# **OKI** Semiconductor

# ISM6258/MSM6258V

#### ADPCM SPEECH PROCESSOR FOR SOLID STATE RECORDER

# TO CUSTOMERS FOR NEW CIRCUIT DESIGN

For a new circuit design, it is recommended to use not the MSM6258, but the MSM6388/MSM6588 as described later.

The MSM6258 has an 8-bit AD converter and does not have a built in low pass filter. On the other hand, the MSM6388/MSM6588 has a 12-bit AD converter and includes a low pass

filter. Therefore, the MSM6388/MSM6588 can realize a high quality voice.

In addition, the same control as a CPU interface of the MSM6258 can be performed by using the EPLAY/EREC command of the MSM6388 and the EXT command of the MSM6588.

#### **GENERAL DESCRIPTION**

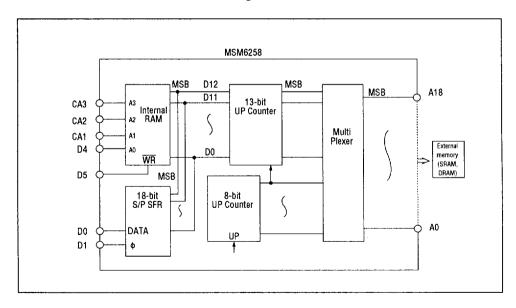

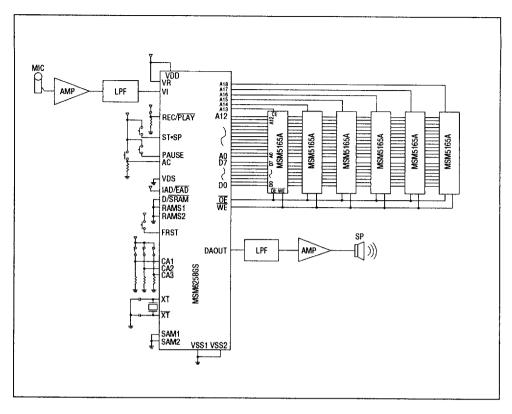

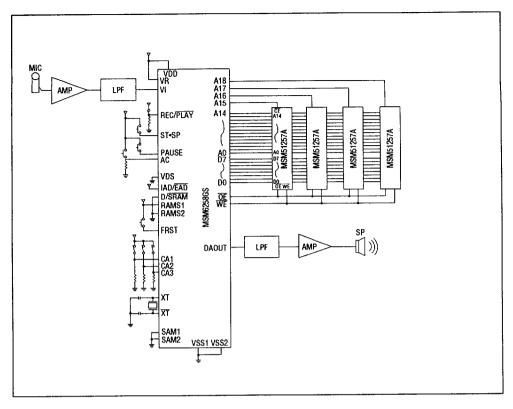

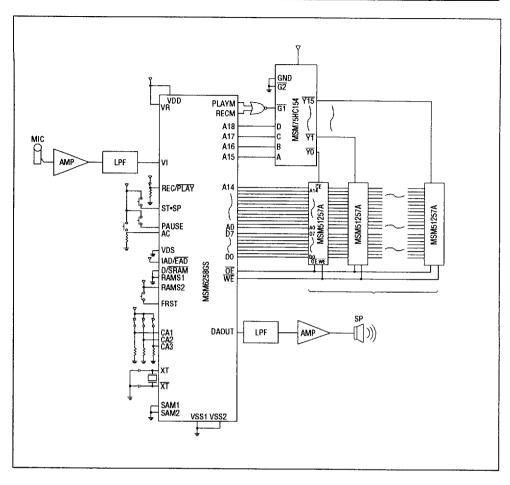

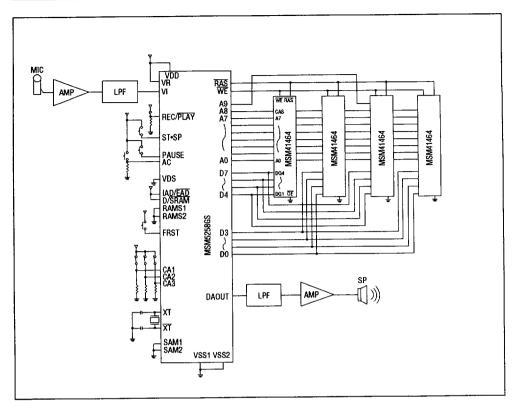

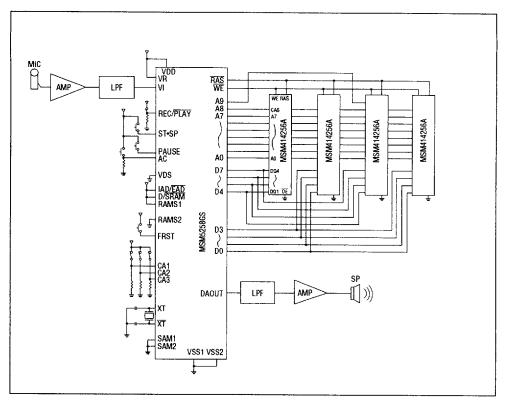

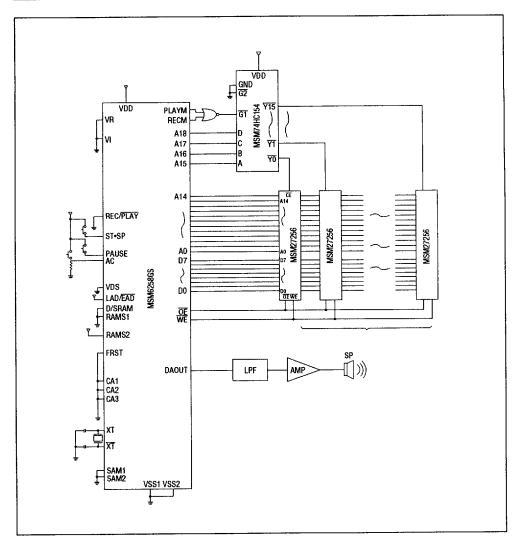

The MSM6258 is a complex and highly integrated ADPCM speech processor, implemented in CMOS technology for low power consumption. The integrated A/D and D/A converters make the chip more self-contained, relieving the need for external conversion circuitry. The device comprises internally. A DRAM controller permitting the use of DRAMs alternatively to SRAMs and ROMs to store speech data. In other words, less periphery, thus less system vulnerability a voice detection circuit and phrase select provision are successfully added features for increased performance.

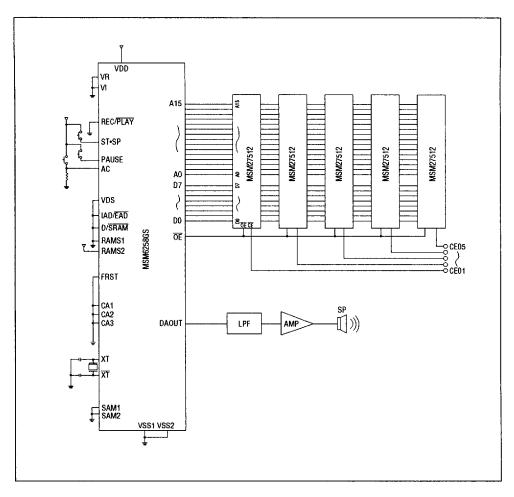

The ADPCM analysis and synthesis block is identical to the popular OKI MSM5218, that is, the bit overflow protection is included in for improved reproduction quality. The device is offered in two basic versions one of which comes in two package types. One is the version designed to be interfaced with an 8-bit CPU like the OKI MSM80C85 or MSM80C51 microcontroller, and comes in a 40-pin flat package; the other operates as a stand-alone solution that includes 19-pin programmable output lines for memory addressing and chip select in a 60-pin flat package or in a 68-pin

PLCC, respectively, to permit full surface mount implementation.

MSM6258 accepts 4 to 8MHz master clocks, out of which two sets of sampling frequencies can be derived. Additionally, the ADPCM bit number is pin-selectable between 3 or 4 bits per sample. When using 256k or 1Mb DRAMs, the maximum I/O time is approximately 17 minutes at a bit-rate of 16kbps, while 256k SRAMs offer a little more than a minute of speech, both in their maximum memory configurations. At the higher bit-rates, 21.2 and 32 kbps, the I/O times are reduced proportionally.

In the case of DRAMs, the OKI MSC2304 (2-Megabit, module) or MSC2305 (4-Megabit module) are recommendable for space and cost saving benefits and in the interest of simplified handling. In the external mode, the built-in 8-bit ADC is looped so that a separate ADC can be connected to MSM6258, the accuracy of which may be between 8 to 12-bit for 'recording' speech. When the playback mode is set, the internal 10-bit DAC will be disabled to permit the connection of an external DAC of 10 to 12-bit of resolution.

#### **FEATURES**

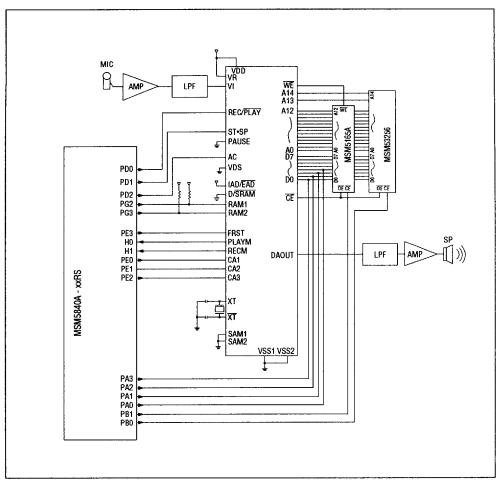

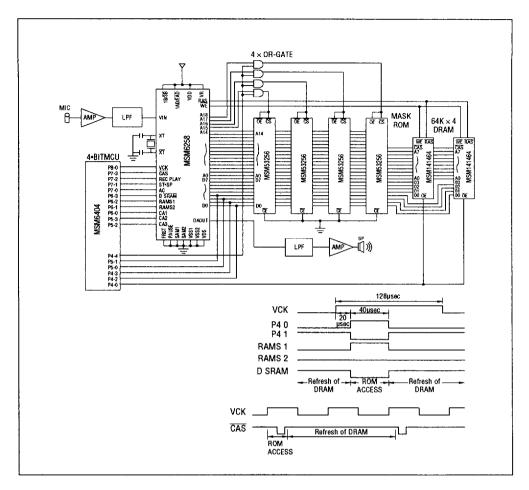

#### 1. STAND-ALONE VERSION

- Switch or microcomputer interface is possible

- Straight ADPCM (3-bit/4-bit)

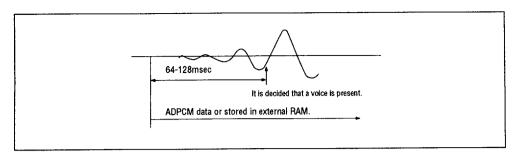

- Built-in voice detection circuit

- Built-in DRAM refresh circuit

- SRAM/DRAM can be directly connected.

Maximum 16 M-bit (with 256K or 1M DRAM used)

- Sampling frequency selection 3.9, 5.2, 7.8kHz (for original oscillation frequency of 4.0 MHz) 4.0, 5.3, 8.0kHz (for original oscillation frequency of 4.096 MHz) 7.8, 10.4, 15.6kHz (for original oscillation frequency of 8.0 MHz)

- Maximum number for words recorded: 7-word

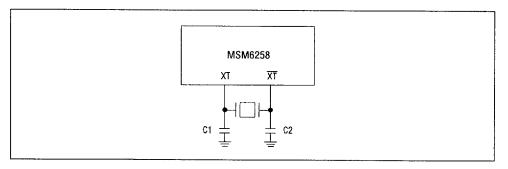

- Original oscillation frequency: 4~8 MHz

- Built-in AD converter: 8-bit

- Built-in DA converter: 10-bit (voltage type of class A)

- Operable with a single power supply

- 60-pin plastic QFP (QFP60-P-1519-

- 60-pin V plastic QFP (QFP60-P-1519-VK)

- 68-pin plastic QFJ (PLCC) (QFJ68-P-S950)

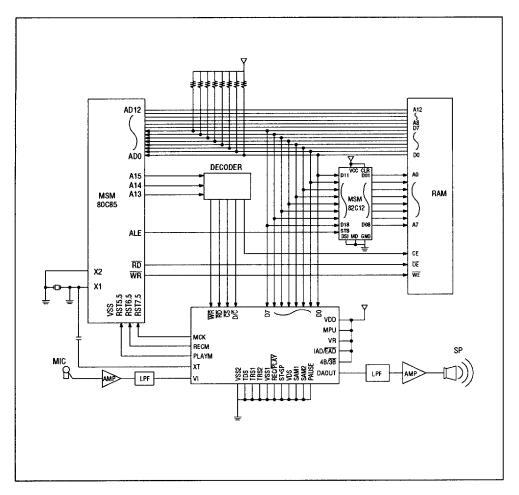

#### 2. CPU INTERFACE VERSION

- Command/status can be input and output through the data bus.

- Straight ADPCM (3-bit/4-bit)

- Sampling frequency selection

3.9, 5.2, 7.8kHz (for original oscillation frequency of 4.0 MHz)

4.0, 5.3, 8.0kHz (for original oscillation frequency of 4.096 MHz)

7.8, 10.4, 15.6kHz (for original oscillation frequency of 8.0 MHz)

- Maximum number for words recorded: 7-word

- Original oscillation frequency: 4~8 MHz

- Built-in AD converter: 8-bit

- Built-in DA converter: 10-bit (voltage type of class A)

- Operable with a single power supply

- 40-pin plastic DIP (DIP40-P-600)

- 44-pin plastic QFP (QFP44-P-910-K)

- 44-pin-V plastic QFP (QFP44-P-910-V1K)

- 44-pin plastic QFJ (PLCC) (QFJ44-P-S650)

**=** 6724240 0016620 418 **==**

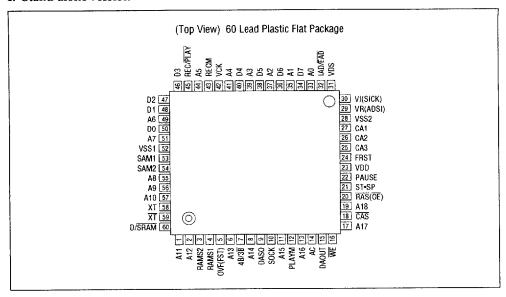

#### PIN CONFIGURATION

#### 1. Stand-alone version

Note 1: Applicable to the MSM6258GS-K, GS-VK.

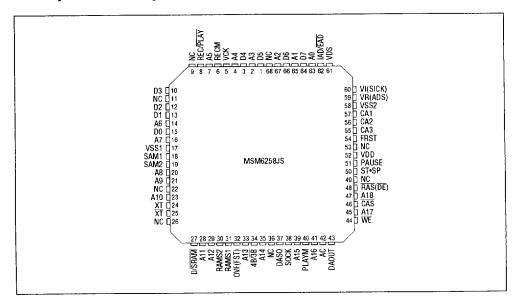

#### 68-lead plastic leaded chip carrier

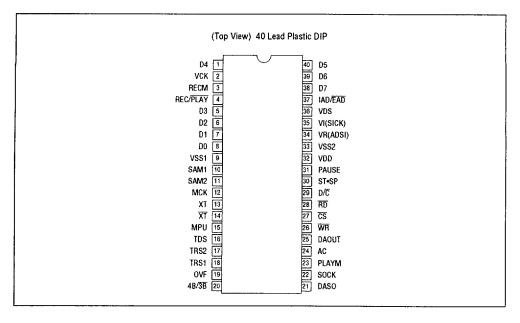

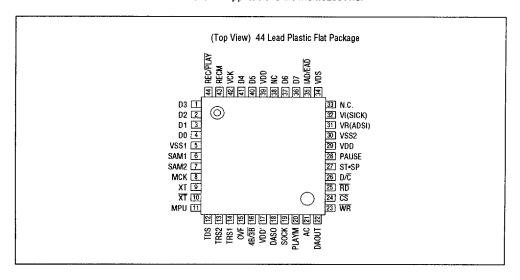

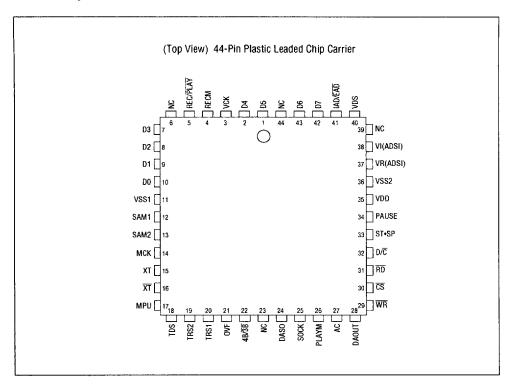

#### 2. CPU interface verison

Note 1: Applicable to the MSM6258VRS.

Note 1: Applicable to the MSM6258VGS-K & GS-V1K

Note 2: VDD' connected to VDD Pin

# **■** 6724240 0016622 290 **■**

#### MSM6258VJS

Note 1: Applicable to the MSM6258VJS.

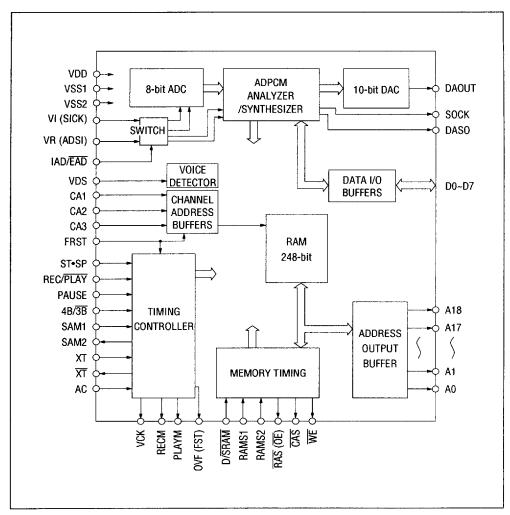

#### **FUNCTIONAL BLOCK DIAGRAM**

#### 1. Stand-alone version

**■** 6724240 0016624 063 **■**

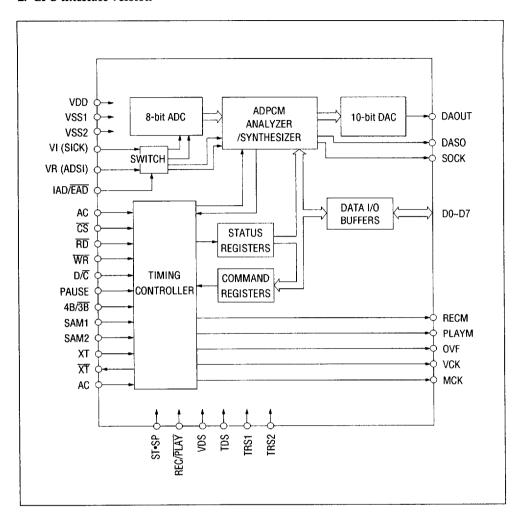

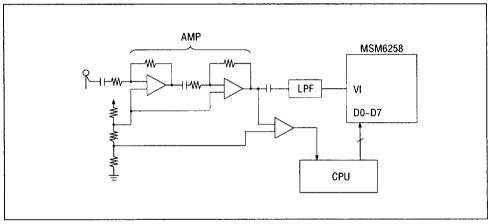

#### 2. CPU interface version

### **ABSOLUTE MAXIMUM RATINGS**

#### STAND-ALONE & MPU interface version

| Parameter            | Symbol           | Conditions            | Value              | Unit |

|----------------------|------------------|-----------------------|--------------------|------|

| Power supply voltage | VDD              | T <sub>a</sub> = 25°C | <b>−0.3</b> ~ +7.0 | ٧    |

| Input voltage        | V <sub>IN</sub>  | T <sub>a</sub> = 25°C | -0.3 ~ VDD +0.3    | ٧    |

| Storage temperature  | T <sub>stg</sub> | _                     | −55 ~ +150         | °C   |

Note:

Permanent device damage may occur it ABSOLUTE MAXIMUM RATINGS are exceeded Functional operation should be restricted to the conditions as recommended. Exposure to ABSOLUTE MAXIMUM RATINGS for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Conditions                               | Value     | Unit |

|-----------------------|-----------------|------------------------------------------|-----------|------|

| Power supply voltage  | VDD             | V <sub>SS1</sub> = V <sub>SS2</sub> = 0V | +3 ~ +6.0 | V    |

| Ambient range         | T <sub>OP</sub> | _                                        | -40 ~ +85 | °C   |

| Oscillation frequency | Fosc            | _                                        | 4.0 ~ 8.0 | MHz  |

6724240 0016626 936 📟

#### DC CHARACTERISTICS

(VDD = 5V/10%, Ta = -40 to +85°C) STAND-ALONE VERSION (VDD = 5V/10%, Ta = -40 to +70°C) CPU I/F VERSION

| Parameter                | Symbol           | Conditions                       | Min.             | Тур. | Max.            | Unit |

|--------------------------|------------------|----------------------------------|------------------|------|-----------------|------|

| Operating current        | I <sub>DD</sub>  | F <sub>osc</sub> = 4.0MHz        | -                |      | 4               | mA   |

| Stand by current         | I <sub>DS</sub>  | With SRAM, AC=H                  | _                | -    | 10              | μА   |

| H input voltage          | V <sub>IH1</sub> | -                                | 3.6              | -    | -               | V    |

| H input voltage (Note 1) | V <sub>IH2</sub> | -                                | $0.8 \times VDD$ | ı    | -               | ٧    |

| L input voltage          | V <sub>IL</sub>  | <del>-</del>                     | -                | -    | 0.8             | ٧    |

| H output voltage         | V <sub>oH</sub>  | IOH = -40μA                      | 4.2              | -    | _               | V    |

| L output voltage         | V <sub>oL</sub>  | IOL = 2mA                        | _                |      | 0.45            | V    |

| H input current          | I <sub>1H1</sub> | Without pull down VIH=VDD        | -                | _    | 10              | μΑ   |

| H input current (Note 2) | I <sub>IH2</sub> | With pull down VIL=0V            | 20               | _    | 400             | μA   |

| L input current          | l <sub>iL</sub>  | V <sub>IL</sub> =V <sub>SS</sub> | -10              | -    | 10              | μΑ   |

| Output leakage current   | I <sub>LO</sub>  | 0V < V0 < VDD                    | -10              | -    | 10              | μА   |

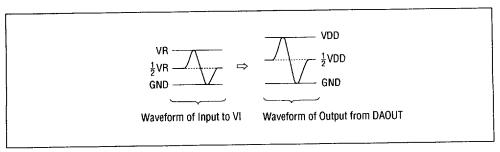

| DA-output relative error | VDAE             | No-load                          | _                | _    | 40              | m۷   |

| AD conversion precision  | V <sub>ADE</sub> | VSS1=VSS2=0V VR=VDD              | _                | _    | 40              | mV   |

| DA output impedance      | R <sub>DA</sub>  | <del>-</del>                     | 12               | 17   | 22              | kΩ   |

| VR input impedance       | R <sub>ve</sub>  |                                  | -                | 35   | _               | kΩ   |

| VR input voltage         | V <sub>VR</sub>  | <del>-</del>                     | 0.9 × VDD        | _    | VDD             | ٧    |

| VI input voltage         | V <sub>vi</sub>  | <del></del>                      | 0                | -    | V <sub>VR</sub> | V    |

| VI input impedance       | R <sub>vi</sub>  | -                                | 10               |      | _               | kΩ   |

S/N = (n-1) × 6

n = ADC bit number

Note 1: Applies to XT

Note 2: Applies to ST•SP and PAUSE and MPU, FRST, VDS (only CPU I/F version)

#### **AC CHARACTERISTICS**

#### 1. Stand-Alone Version

VDD = 4.5 - 5.5V,  $Ta = -40 - 85^{\circ}C$ fosc = 4.096 MHz, fs = 8.0 kHz

| Item                                                                              | Symbol               | Min.             | Тур. | Max. | Unit |    |

|-----------------------------------------------------------------------------------|----------------------|------------------|------|------|------|----|

| AC pulse width                                                                    |                      | t <sub>ACP</sub> | 2.0  | -    | _    | μѕ |

| PAUSE pulse width                                                                 | t <sub>pap</sub>     | 2.0              | _    | -    | μS   |    |

| FRST pulse width                                                                  |                      | t <sub>FRP</sub> | 2.0  | -    | -    | μs |

| ST•SP pulse width (1) (STOP pulse width whe ="L", and REC/PLAY="H")               | n D SRAM<br>(Note 2) | t <sub>spp</sub> | 66   |      | -    | ms |

| ST-SP pulse width(2)<br>(STOP pulse width excepting (1) above)                    |                      | t <sub>stp</sub> | 2.0  | _    | -    | μs |

| Time from entry of start pulse to rise of RECM DRAM is selected                   | when (Note 1)        | t <sub>DRR</sub> | . 1  | 16.3 |      | ms |

| Time from starting of oscillation to rise of REC SRAM is selected                 | M when               | t <sub>srr</sub> | 56.2 | -    | 70   | ms |

| Time from starting of oscillation to initial chang<br>DAOUT when SRAM is selected | ge of<br>(Note 1)    | t <sub>xDs</sub> |      | 40   | -    | ms |

| Time from entry of STOP pulse to fall of RECM                                     | (Note 1)             | t <sub>srf</sub> | 0    | _    | 66   | ms |

| Time for DAOUT to change from GND to 1/2 VI                                       | DD (Note 1)          | t <sub>DAR</sub> | -    | 16   | _    | ms |

| Time from entry of STOP pulse to change of DAOUT to GND (Note 1)                  | REC/PLAY "H"         | t <sub>dal</sub> | 0    | 50   | 100  | ms |

| change of DACO1 to divid (Note 1)                                                 | REC/PLAY "L"         | t <sub>daf</sub> | 0    | 16   | 32   | ms |

| Time from setting of PLAYM to "L" to entry of r<br>pulse                          | estart<br>(Note 1)   | t <sub>PRS</sub> | 52   | -    | _    | ms |

| Time from entry of START pulse to rise of PLA                                     | YM<br>(Note 1)       | t <sub>spr</sub> | 0    | _    | 4    | μs |

| Time from entry of STOP pulse to fall of PLAY!                                    | t <sub>spf</sub>     | 0                | _    | 4    | μs   |    |

| Time from setting of REC/PLAY, CA1 - CA3 to START pulse                           | t <sub>src</sub>     | 2                | -    | -    | μs   |    |

| Time from completion of entry of STOP pulse to of REC/PLAY, CA1 - CA3             | o change             | t <sub>spc</sub> | 2    | -    | -    | μs |

(Note 1)

Proportionate to fosc (Raising fosc shortens the time.)

(Note 2)

Proportionate to fs (Raising fs shortens the time.)

### **=** 6724240 0016628 709 **=**

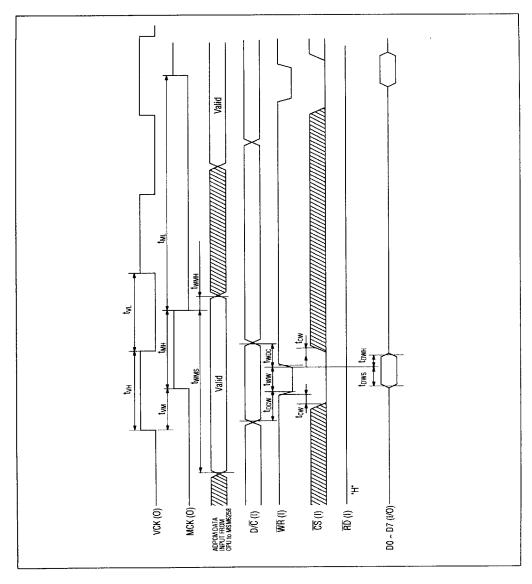

#### 2. CPU Interface Version

VDD = 4.5 - 5.5V,  $Ta = -40 - 85^{\circ}C$  fosc = 4.096 MHz, fs = 8.0 kHz

| Item                                                 |          | Symbol           | Min. | Тур.  | Max.         | Unit |

|------------------------------------------------------|----------|------------------|------|-------|--------------|------|

| Time during which the level of VCK remains "H"       | (Note 1) | t <sub>vH</sub>  | -    | 62.5  | -            | μs   |

| Time during which the level of VCK remains "L"       | (Note 1) | t <sub>vL</sub>  | -    | 62.5  | _            | μs   |

| Time during which the level of MCK remains "H"       | (Note 2) | t <sub>MH</sub>  | -    | 39.1  | -            | μs   |

| Time during which the level of MCK remains "L"       | (Note 3) | t <sub>ML</sub>  | _    | 210.9 | -            | μs   |

| Time from rise of VCK to rise of MCK                 | (Note 2) | t <sub>vm</sub>  | -    | 19.5  | -            | μS   |

| Setup time for fall of MCK during ADPCM data reading | (Note 2) | t <sub>rms</sub> | 15   | -     | -            | μS   |

| Hold time for fall of MCK during ADPCM data reading  | (Note 2) | t <sub>rmh</sub> | 55   | ı     | _            | μs   |

| Setup time for fall of MCK during ADPCM data writing | (Note 2) | t <sub>wms</sub> | 70   | -     | _            | μs   |

| Hold time for fall of MCK during ADPCM data writing  | (Note 2) | t <sub>wm</sub>  | 2    | _     | _            | μS   |

| RD pulse width                                       |          | t <sub>rr</sub>  | 250  | -     | -            | ns   |

| D/C setup time for fall of RD                        |          | t <sub>DCR</sub> | 50   | -     | _            | ns   |

| D/C hold time for rise of RD                         |          | t <sub>rdc</sub> | 100  | -     | -            | ns   |

| CS setup hold time for RD                            |          | t <sub>cr</sub>  | 0    | -     | -            | ns   |

| Data establishment time from fall of RD              |          | t <sub>DRE</sub> | -    | -     | 200          | ns   |

| Data float time from rise of RD                      |          | t <sub>drf</sub> | 10   | _     | 200          | ns   |

| WR pulse width                                       |          | t <sub>ww</sub>  | 250  | -     | _            | ns   |

| D/C setup time for fall of WR                        |          | t <sub>ocw</sub> | 50   | -     | <del>-</del> | ns   |

| D/C hold time for rise of WR                         |          | t <sub>woc</sub> | 100  | -     | -            | ns   |

| CS setup hold time for WR                            |          | t <sub>cw</sub>  | 0    | -     | -            | ns   |

| Data setup time for rise of WR                       |          | t <sub>ows</sub> | 100  | -     | -            | ns   |

| Data hold time for rise of WR                        |          | t <sub>own</sub> | 30   | -     | -            | ns   |

| Time from fall of AC to entry of start command       | (Note 2) | t <sub>AS</sub>  | 16.0 | -     | -            | ms   |

| Setup time for entry of start command in rise of VCK | (Note 2) | t <sub>wvs</sub> | 4    | -     | 120          | μs   |

| Hold time for entry of stop command in rise of VCK   | (Note 2) | t <sub>wvP</sub> | 4    | -     | 120          | μS   |

| Item                                                         | Syr            | nbol | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|----------------|------|------|------|------|------|

| Time from fall of VCK to rise of RECK                        | t              | VRR  | 0.0  | _    | 2.0  | μS   |

| Time from fall of VCK to fall of RECM                        | t              | VRF  | 0.0  | _    | 2.0  | μs   |

| Time from fall of AC to time when DAOUT is set to 1/2 VDD (N | lote 2)        | DAR  | _    | 15.6 | _    | ms   |

| Time from entry of start command to rise of PLAYM            | t              | WPR  | 0.0  | _    | 4.0  | μs   |

| Time from entry of stop command to fall of PLAYM             | lote 2) t      | WPF  | 0.0  | -    | 2.0  | μs   |

| Time from entry of stop command to entry of start command (N | tote 1)        | SPT  | 260  | _    | -    | μs   |

| Duty cycle for input of original oscillation clock to XT     | f <sub>D</sub> | OUTY | 40   | 50   | 60   | %    |

(Note 1)

Proportionate to fs (Raising fs extends the time.)

(Note 2)

Proportionate to fosc (Raising fosc shortens the time.)

(Note 3)

Equivalent to two times the sampling period minus  $t_{\mathrm{MH}}$

**-** 6724240 0016630 367 **-**

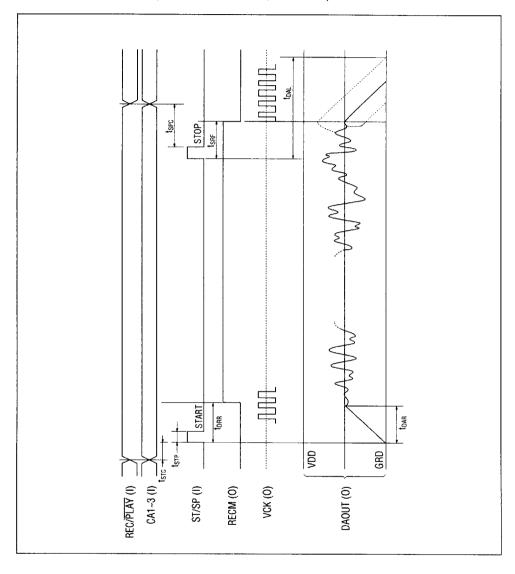

#### **TIMING CHART**

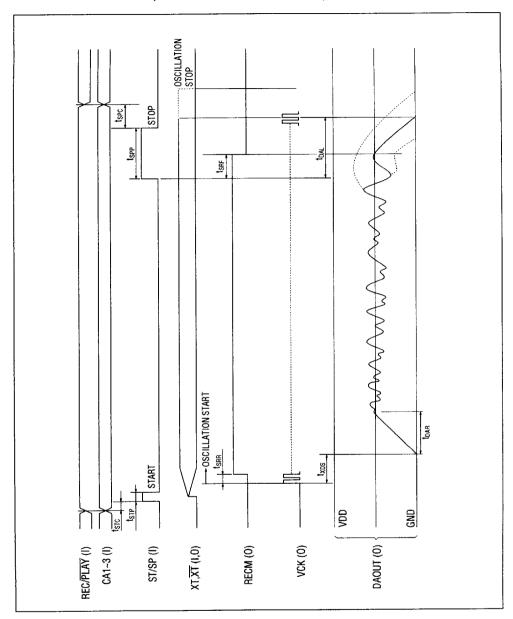

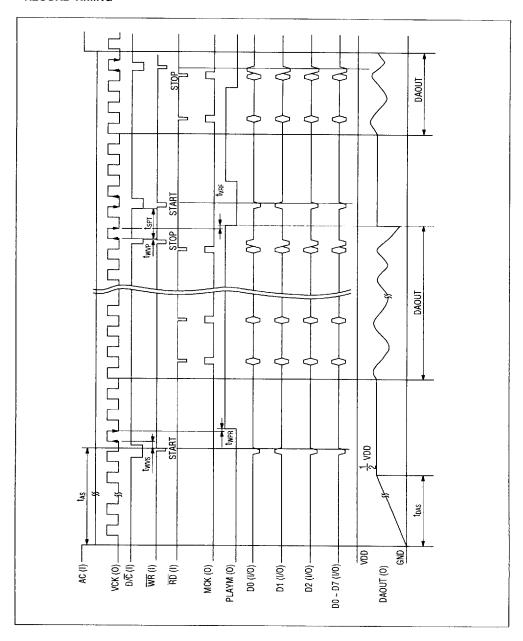

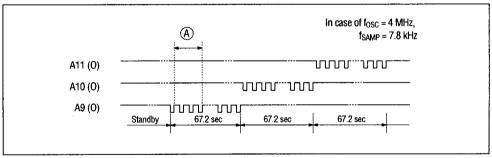

- 1. Stand-Alone Version

- RECORD TIMING (with DRAM selected, VDS = "L")

Note If VDS = "H", RECM outputs 2 Hz clock during detection of voice.

• **RECORD TIMING** (with SRAM selected, VDS = "L")

Note If VDS = "H", RECM outputs 2 Hz clock during detection of voice.

# **■** 6724240 0016632 13T **■**

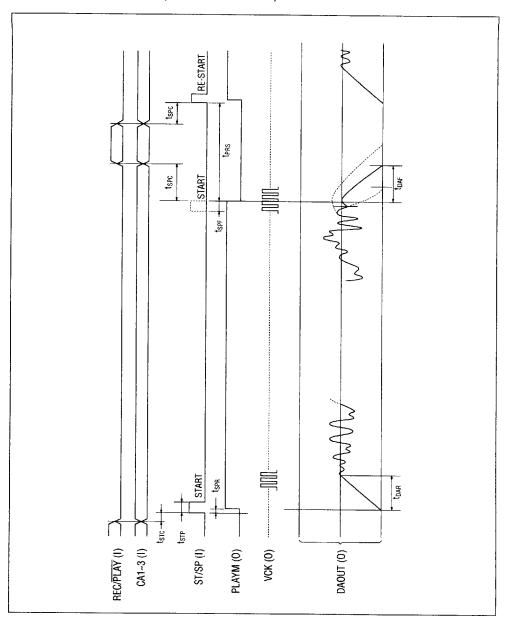

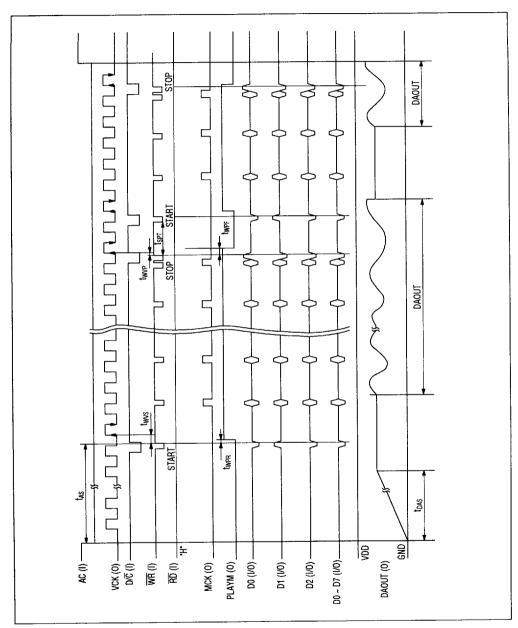

PLAYBACK TIMING (with DRAM selected)

Note tDAF = 16 msec when DAOUT signal level is 1/2 VDD, tDAF = 32 msec when DAOUT signal level is VDD.

## **6**724240 0016633 076 **11**

• PLAYBACK TIMING (with SRAM selected)

■ 6724240 0016634 TO2 ■■

448

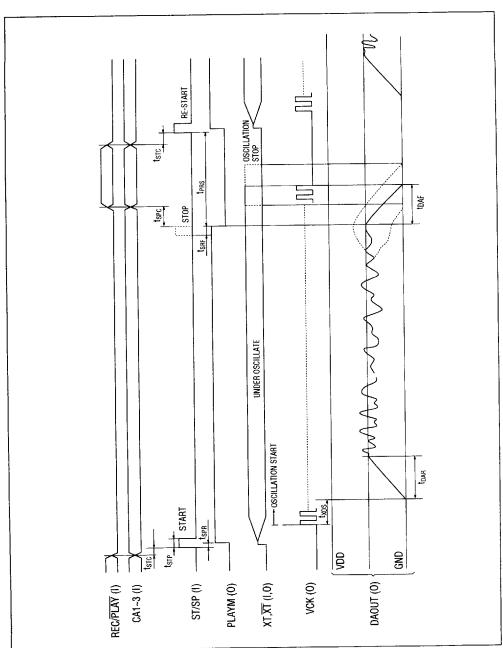

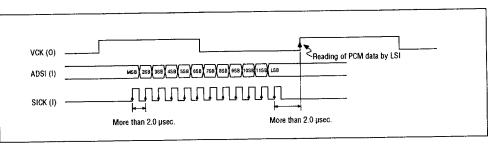

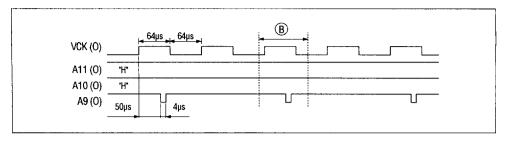

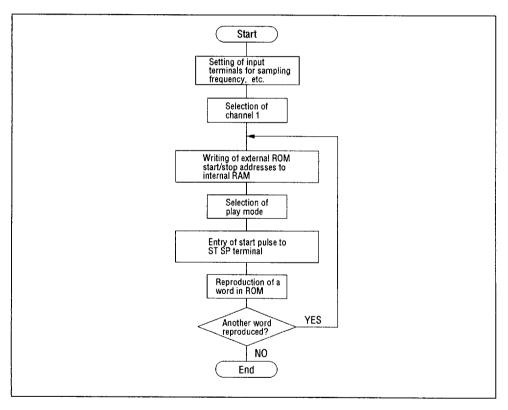

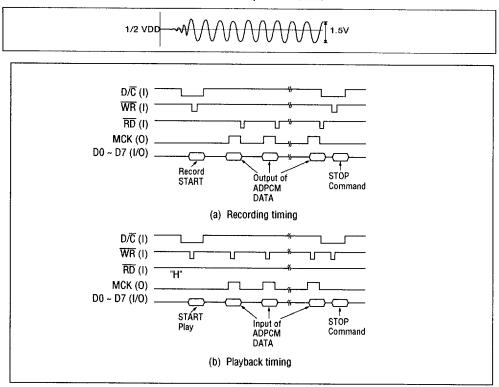

#### 2. CPU INTERFACE VERSION

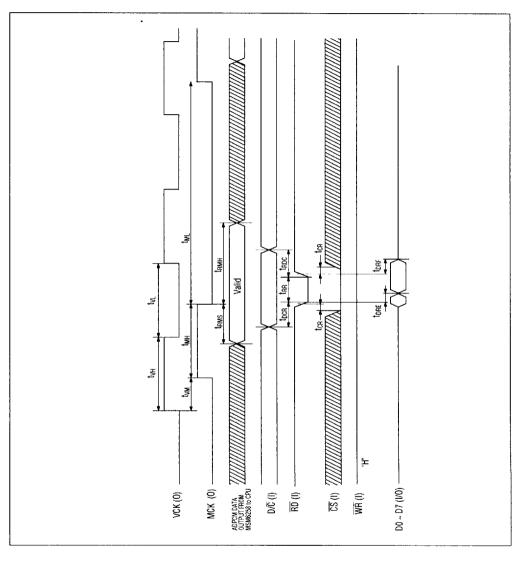

- READ TIMING (with record or status output)

- READ TIMING (with record or status output)

Note Use the above valid section to reference ADPCM data output from the MSM6258 to CPU. Status reading may be performed anywhere.

### **■** 6724240 0016635 949 **■**

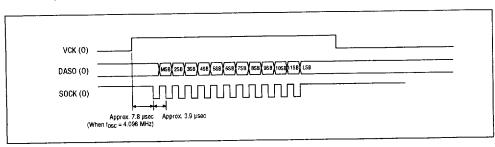

- WRITE TIMING (with playback or command input)

- WRITE TIMING (with playback or command input)

Note Use the above valid section to reference ADPCM data input from CPU to the MSM6258. Command write may be performed anywhere.

# **■** 6724240 0016636 **88**5 **■**

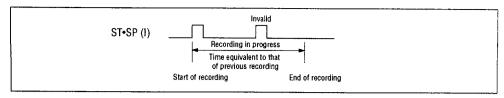

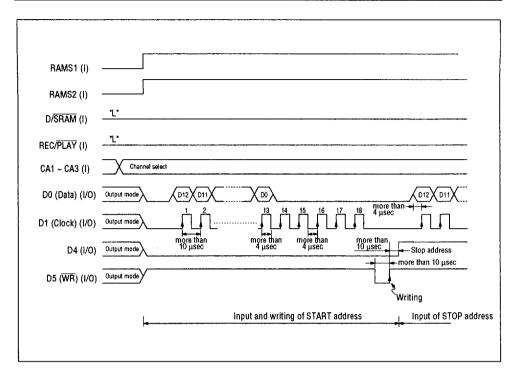

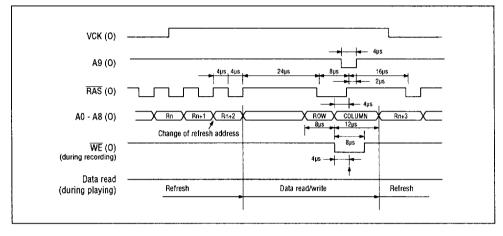

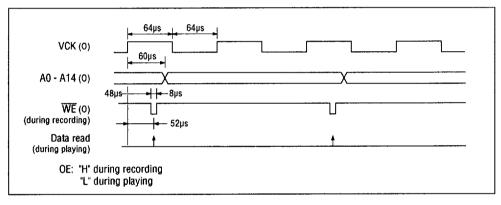

#### RECORD TIMING

#### • RECORD TIMING

## **-** 6724240 0016637 711 **-**

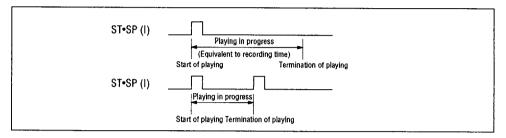

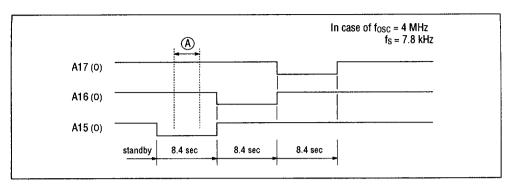

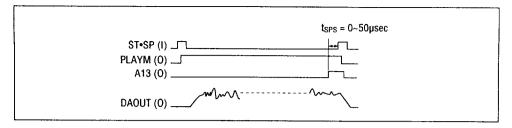

#### PLAYBACK TIMING

#### • PLAYBACK TIMING

# **-** 6724240 0016638 658 **-**

#### **DESCRIPTION OF TERMINALS**

#### 1. Stand-Alone Version

| Pin Name                              | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                                   |     | Power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VSS1                                  | -   | Digital GND pin                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS2                                  | -   | Analog GND pin                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AC (All Clear)                        | _   | If the level of this pin is set to "H", the internal circuitry is set to the initial state. So, the output level of DAOUT is set to GND, the flag for each channel is reset to inhibit reproduction in channel 1 through channel 7; and oscillation is stopped if SRAM has been selected.  The built-in power-on resetting circuit causes the level of this pin to go "H". For assurance, it is recommended to connect an external power-on resetting circuit. |

| REC/PLAY                              | _   | Selects recording or playing. If the level of this pin is set to "H", record mode is invoked. Do not change the input level of this pin during recording or playing.                                                                                                                                                                                                                                                                                           |

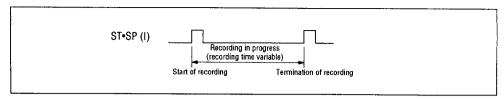

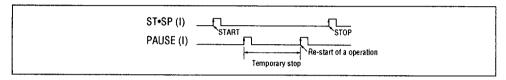

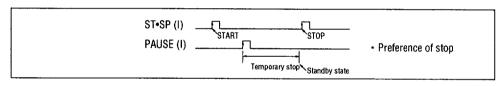

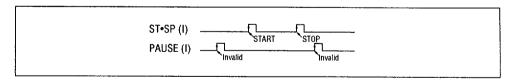

| ST•SP                                 | ı   | Enables entry of pulses to start and terminate recording or playing. It is internally pulled down. A chatter prevention circuit is provided.                                                                                                                                                                                                                                                                                                                   |

| PAUSE                                 | -   | When momentarily connected to VDD, the record or playback operation is temporarily suspended. It is internally pulled down.                                                                                                                                                                                                                                                                                                                                    |

| PLAYM<br>(PLAY MONITOR)               | 0   | Its output level is set to "H" during vocalization in play mode. Its output level is set to "L" during standby and record mode.                                                                                                                                                                                                                                                                                                                                |

| RECM<br>(REC MONITOR)                 | 0   | Outputs "L", "H", and "2 Hz clock output" depending on the state of the LSI. In play or standby mode, its output level is set to "L".  During recording, the level of this pin is set to "H". It outputs 2 Hz clock during detection of voice, and during pause.                                                                                                                                                                                               |

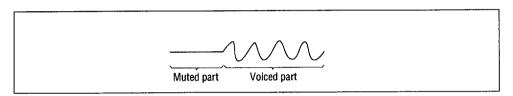

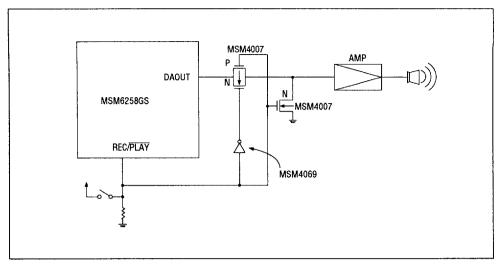

| DAOUT                                 | 0   | Voice output pin. Voice is output during recording and playing. For reference, a muting circuit, which inhibits the output of voice during recording, is given in Figure 34.  In standby mode, its level is set to GND level to make the power consumption of the speaker driving transistor null. At this time, pop noise is eliminated internally.                                                                                                           |

| CA1~CA3                               | 1   | Specifies channels for recorded phrases or phrases to be reproduced. Up to eight channels can be specified. Do not change the input level of this pin during recording or playing.                                                                                                                                                                                                                                                                             |

| OVF(FST)<br>Overflow<br>(Flag Status) | 0   | Outputs the flag status ("H" level if the selected channel has already been used for recording) for the selected channel in standby mode.  Outputs "H" level pulses if the voice signal exceeds approximately 80% of the dynamic range in record or play mode.                                                                                                                                                                                                 |

6724240 0016639 594 📟

| Pin Name                        | 1/0        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

|---------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| FRST<br>(FLAG RESET)            | 1          | Setting the level of this pin to "H" resets the flag for the selected channel to inhibit reproduction in that channel.  The signal from this pin is valid only in standby mode. Do not set the level to "H" during recording or playing. A pull down resistor is used.                                                                                                                                                                                                     |                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| VDS<br>(Voice Detect<br>Select) | ı          | In record mode, when VDS="H", this input determines whether the silence preceding the voice input is silence or voice and if voice then recording is started. This is called a "Voice Triggered Starting Circuit".                                                                                                                                                                                                                                                         |                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| SAM1<br>SAM2                    | I          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Selects a sampling frequency. If the original oscillation frequency is 4.096 MHz, a sampling frequency is select shown below: |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

|                                 |            | SAM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | L                                                                                                                             |                                    | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Н                                             |

|                                 |            | SAM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | L                                                                                                                             |                                    | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Н                                             |

|                                 |            | fs                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.0k                                                                                                                          | Hz 5                               | .3kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.0kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | inhibited                                     |

| 4B/3B                           | 1          | Selects bit leng                                                                                                                                                                                                                                                                                                                                                                                                                                                           | th for ADPC                                                                                                                   | M. "H" stand                       | ds for 4-bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t, and "L" stand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ds for 3-bit.                                 |

| D0~D7                           | 1/0        | This bi-directional data bus conveys the ADPCM-coded data to and from the memory One byte consists of two nibbles in the 4-bit ADPCM data format. In the case of 3-bit data format, two nibbles are presented, but the LSB of each is always externally pulled-down. The MSB of every nibble indicates whether the input waveform is ascending (MSB=0) or descending (MSB=1). Do to D7 output or input a pair of ADPCM nibbles during every sampling period, which is VCK. |                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

|                                 |            | ADPUN HIDDIES                                                                                                                                                                                                                                                                                                                                                                                                                                                              | during ever                                                                                                                   | y samping                          | period, wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nich is VCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | or input a pair of                            |