A15-6010-02a

# Preliminary

February 1, 2008

© Copyright International Business Machines Corporation 2006, 2008

All Rights Reserved Printed in the United States of America February 2008.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both. IBM PowerPC

ibm.com PowerPC Architecture IBM Logo

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM System and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com®

The IBM Semiconductor solutions home page can be found at ibm.com/chips

A15-6010-02a February 1, 2008

# Contents

| List of Figures                                                       | 17   |

|-----------------------------------------------------------------------|------|

| List of Tables                                                        | 21   |

| 1. Overview                                                           | 27   |

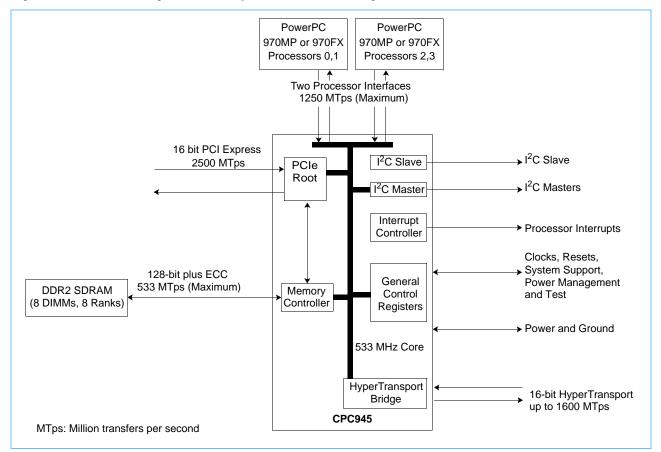

| 1.1 Introduction                                                      | 27   |

| 1.2 Features                                                          | 27   |

| 1.3 Block Diagrams                                                    |      |

| 2. Functional Description                                             | 29   |

| 2.1 External Interfaces                                               |      |

| 2.1.1 Processor Interconnect (PI)                                     | . 29 |

| 2.1.2 SDRAM Interface                                                 | . 30 |

| 2.1.3 PCI Express Interface                                           |      |

| 2.1.4 HyperTransport Host Bridge                                      |      |

| 2.1.5 DRAM I2C Master Interface                                       |      |

| 2.1.6 I2C Slave Configuration Register Interface                      |      |

| 2.1.7 Interrupt Controller                                            |      |

| 2.2 Implementation                                                    |      |

| 2.2.1 CPC945 Clocking                                                 |      |

| 2.2.1.1 Processor Interconnect Clock                                  |      |

| 2.2.1.2 DDRClk                                                        |      |

| 2.2.1.3 PCI Express Clocking                                          |      |

| 2.2.1.4 HyperTransport Clock<br>2.2.1.5 Power Manager Clock           |      |

| 2.2.1.5 Power Manager Clock                                           |      |

| 2.2.3 CPC945 Core Interface (API Interface)                           |      |

| 2.2.4 PCI Express and HyperTransport Bus Interfaces                   |      |

| 2.2.4.1 PCI Express and HyperTransport Transactions                   |      |

| 2.2.4.2 Processor Interconnect to PCI Express Transaction Mapping     |      |

| 2.2.4.3 Processor Interconnect to HyperTransport Transaction Mapping  |      |

| 2.2.4.4 PCIe/HT-to-Processor Interconnect Virtual Transaction Mapping | 33   |

| 2.2.4.5 PCIe Transaction Ordering                                     |      |

| 2.2.4.6 Data Consistency/Memory Coherence                             |      |

| 2.2.4.7 Endianess                                                     |      |

| 2.2.5 Exceptions                                                      | 36   |

| 2.2.5.1 Invalid Addresses                                             | . 36 |

| 2.2.5.2 Invalid Burst Transactions                                    | . 36 |

| 2.2.5.3 Invalid Transaction Types                                     | 36   |

| 2.2.6 Interrupts                                                      | . 37 |

| 3. CPC945 Core Interface (API Interface)                              | 39   |

| 3.1 CPC945 Core Interface Overview                                    | . 39 |

| 3.1.1 General Description of the Request Interfaces                   |      |

| 3.1.1.1 CRRAI / CWRAI – Coherent Read/Write Request Address Interface | . 42 |

| 3.1.1.2 NCRAI – Non-Coherent Request Address Interface                | . 42 |

| 3.1.1.3 TRAI / TWAI – Target Read/Write Address Interface                 | 42       |

|---------------------------------------------------------------------------|----------|

| 3.1.1.4 TAI – Target Address Interface                                    |          |

| 3.1.2 General Description of the Data Interfaces                          |          |

| 3.1.2.1 WDI – Write Data Interface                                        | 44       |

| 3.1.2.2 RDI – Read Data Interface                                         | 44       |

| 3.1.2.3 MWDI – Memory Write Data Interface                                | 44       |

| 3.1.2.4 MRDI – Memory Read Data Interface                                 | 44       |

| 3.1.2.5 AMRDI – API from Memory Read Data Interface                       | 44       |

| 3.1.2.6 MWDBI – Memory Write Data Buffer Interface                        | 44       |

| 3.2 Illustration of Requests and Dataflow within PI                       | 45       |

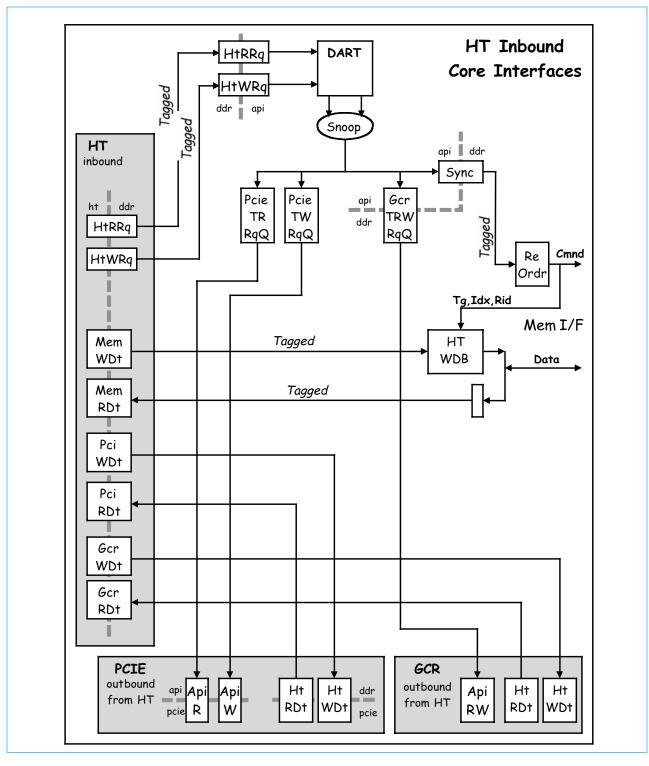

| 3.2.1 HT Inbound Request                                                  | 45       |

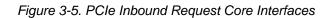

| 3.2.2 PCIe Inbound Request                                                | 47       |

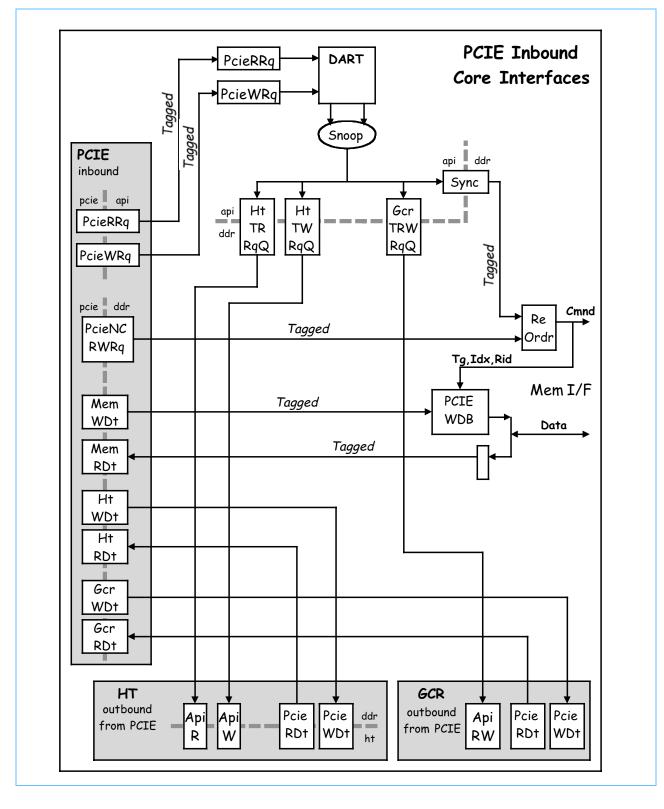

| 3.2.3 PI Target Requests                                                  | 49       |

| 3.3 PI Bus Timing Parameters                                              | 51       |

| 3.4 DMA Address Relocation Table (DART)                                   | 53       |

| 3.4.1 DART Format in Main Memory                                          |          |

| 3.4.2 DART Translation Process                                            | 55       |

| 3.4.3 DART TLB Format                                                     | 57       |

| 3.4.4 DART TLB Translation                                                | 60       |

| 3.5 Processor Interconnect Interface Microarchitecture                    | 61       |

| 3.5.1 System Overview                                                     | 61       |

| 3.5.2 Apilf Operation                                                     | 61       |

| 3.5.2.1 Commands from Processor                                           |          |

| 3.5.2.2 Resources                                                         | 69       |

| 3.5.2.3 Resource Descriptions                                             |          |

| 3.5.3 Ordering of Operations                                              |          |

| 3.5.3.1 Processor Commands                                                | 73       |

| 4. Processor Interconnect Bus                                             | . 77     |

| 4.1 Processor Interface Alignment Procedure                               |          |

| 4.1.1 Determining PI Bus Parameters                                       |          |

| 4.1.2 Error Register Information                                          |          |

| 4.1.3 Additional Debug Information                                        |          |

| 4.1.4 API Programming Procedure                                           |          |

| 4.1.5 Configuring for Single PI Port Usage                                |          |

| 4.1.6 Internal versus External APSync                                     |          |

| 4.2 Processor Interface Endian Order                                      |          |

| 4.3 Processor Interface Balanced Encoding                                 |          |

| 4.4 Bus Snoops and Coherency                                              |          |

| 4.5 Processor Interface Slave Transactions                                |          |

| 4.6 Processor Interface Master Transactions                               |          |

| 4.7 TEA, DERR, Checkstop                                                  |          |

|                                                                           | <u> </u> |

| 4.7.1 I ransfer Error Acknowledge                                         |          |

| 4.7.1 Transfer Error Acknowledge<br>4.7.2 Data Error Signal and Checkstop | 93       |

| •                                                                         | 93<br>93 |

| 5. | PCI Express                                                              |     |

|----|--------------------------------------------------------------------------|-----|

|    | 5.1 Introduction                                                         |     |

|    | 5.1.1 PCIe Registers                                                     | 97  |

|    | 5.1.2 Addressing                                                         | 97  |

|    | 5.1.3 DART                                                               | 97  |

|    | 5.1.4 PCIe Bus I/O Space                                                 | 97  |

|    | 5.1.5 CPC945 PCIe Bus Address Decoding                                   | 97  |

|    | 5.2 PCI Express Concepts                                                 | 98  |

|    | 5.2.1 Transmit Layer Packet                                              |     |

|    | 5.2.2 PI Versus TL Data Formatting Differences                           |     |

|    | 5.2.3 Error Checking                                                     | 106 |

|    | 5.2.4 Message Decode                                                     | 108 |

|    | 5.3 Configuration Register Access                                        |     |

|    | 5.3.1 Indirect Method                                                    |     |

|    | 5.3.2 Limited Direct Access Method                                       |     |

|    | 5.3.3 Direct Access Method                                               |     |

|    | 5.3.4 SBus Direct Configuration Access Method                            |     |

|    | 5.3.5 I2C Direct Configuration Access Method                             | 113 |

| _  |                                                                          |     |

| 6. | HyperTransport                                                           |     |

|    | 6.1 Overview                                                             |     |

|    | 6.2 Initializing HyperTransport Core in the CPC945                       |     |

|    | 6.2.1 Programming the HyperTransport core                                |     |

|    | 6.2.1.1 HT1 Address Mask Register (0xF8070200)                           |     |

|    | 6.2.1.2 Link Config/Control Register (0xF8070110)                        |     |

|    | 6.2.1.3 LinkFreqCap/LinkError/Link Freq/RevisionID Register (0xF8070120) |     |

|    | 6.2.1.4 Error Handling/Enumeration Scratchpad Register (0xF807140)       |     |

|    | 6.2.1.5 Example of Programming Sequence                                  |     |

|    | 6.3 DART                                                                 |     |

|    | 6.4 HyperTransport Read Size Restriction                                 |     |

|    | 6.5 HyperTransport Address Space                                         |     |

|    | 6.6 HyperTransport Bus Address Decoding                                  |     |

|    | 6.7 HyperTransport Address Mapping                                       | 119 |

|    | 6.7.1 Downstream Requests                                                |     |

|    | 6.7.2 Upstream Requests                                                  | 121 |

|    | 6.8 Reset                                                                | 122 |

|    | 6.9 Exceptions to HT Specification 1.04                                  | 123 |

|    | 6.9.1 Bridge Control Register                                            | 123 |

|    | 6.9.2 Updating the PLL                                                   | 123 |

|    | 6.9.3 Ordering through CPC945's Primary Interface                        | 124 |

|    | 6.9.4 HyperTransport SERR#                                               | 125 |

|    | 6.10 HyperTransport Registers                                            | 127 |

| 7  | DDP2 Momery Controller                                                   | 400 |

| 1. | DDR2 Memory Controller<br>7.1 Feature Summary                            |     |

|    | •                                                                        |     |

|    | 7.2 Memory Controller Basics                                             |     |

|    | 7.3 Memory Configurations                                                |     |

| 7.4 Supported Memories                           | 132 |

|--------------------------------------------------|-----|

| 7.4.1 Sizes                                      | 132 |

| 7.4.2 Speeds                                     | 132 |

| 7.4.3 DDR2 Features                              | 133 |

| 7.4.4 DIMMs                                      | 133 |

| 7.5 Clocks                                       | 134 |

| 7.6 Data Transfers                               | 134 |

| 7.7 Operational States                           |     |

| 7.7.1 Power On Reset                             |     |

| 7.7.2 Memory Controller Bring-up Summary         |     |

| 7.7.3 Normal Operation                           |     |

| 7.7.3.1 Page Access                              |     |

| 7.7.3.2 Power Management During Normal Operation |     |

| 7.7.4 Self Refresh                               |     |

| 7.7.4.1 Self Refresh Entry                       |     |

| 7.7.4.2 Self Refresh Exit from Chip Sleep        |     |

| 7.7.4.3 Self Refresh Exit from Chip Power On     |     |

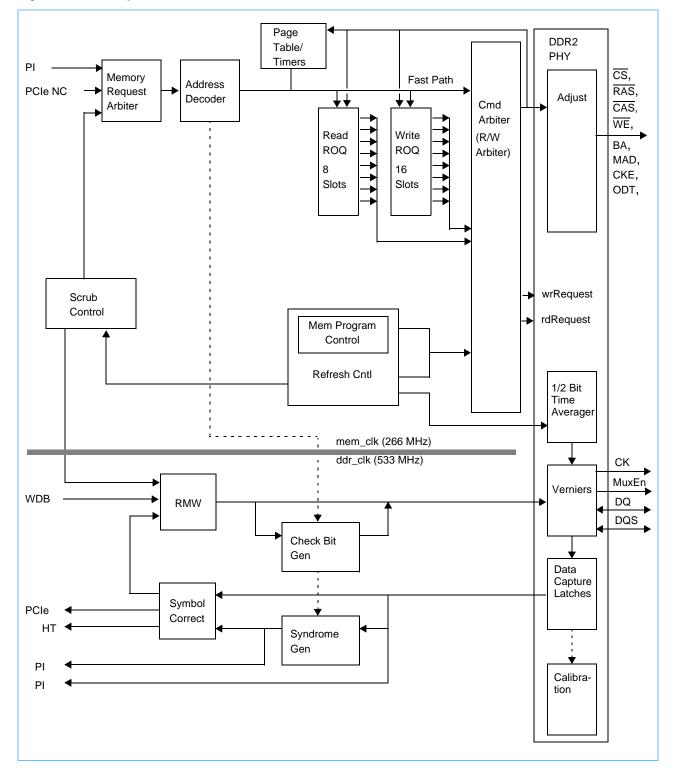

| 7.8 Internal Operation Overview                  |     |

| 7.8.1 Control                                    |     |

| 7.8.2 Data                                       |     |

| 7.8.2.1 Read-Modify-Writes                       |     |

| 7.8.3 DDR2 PHY                                   |     |

| 7.9 Memory Programming Control                   |     |

| 7.9.1 MemInitReg Execution                       |     |

| 7.9.2 Looping                                    |     |

| 7.9.3 Termination                                |     |

| 7.9.4 First Use                                  |     |

| 7.9.5 Auto Refresh                               |     |

| 7.9.6 SDRAM Commands                             |     |

| 7.10 Memory Device Initialization                |     |

| 7.10.1 MRS Settings                              |     |

| 7.10.2 EMRS Settings                             |     |

| 7.11 MRS Register                                |     |

| 5                                                |     |

| 7.12 Refresh                                     |     |

| 7.13 Memory Request Arbiter                      |     |

| 7.14 Address Decode                              |     |

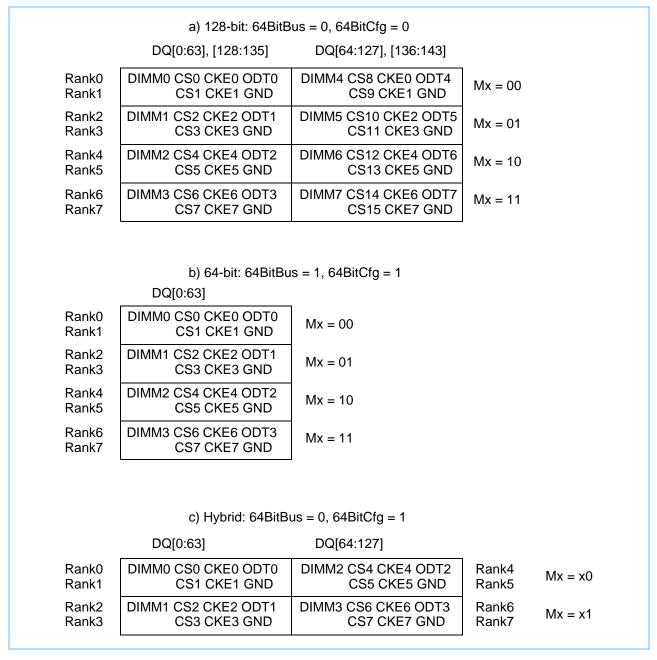

| 7.14.1 64/128 Cfg/Bus                            |     |

| 7.14.2 DIMMs/DIMM pairs                          |     |

| 7.14.3 Installed DIMMs                           |     |

| 7.14.4 Single-Sided/Double-Sided                 |     |

| 7.14.5 Chip Size and Organization                |     |

| 7.14.6 Page Policy                               |     |

| 7.14.7 Interleave Mode                           |     |

| 7.14.8 Chip Select Mode                          |     |

| 7.14.9 Start Address, Add 2G/Sub 2G              |     |

| 7.14.10 DIMM Configuration Algorithm             |     |

| 7.14.11 DIMM Configuration Examples              |     |

| 7.14.11.1 Example 1                              |     |

| 7.14.11.2 Example 2                              | 100 |

| 7.14.11.3 Example 3                                      |     |

|----------------------------------------------------------|-----|

| 7.14.11.4 Example 4                                      | 168 |

| 7.14.12 Address Mapping                                  |     |

| 7.14.13 Address Mapping Exceptions                       |     |

| 7.15 Timing Parameters                                   | 175 |

| 7.15.1 Data Bus Delay Greater than tCK                   | 175 |

| 7.15.2 Restrictions                                      | 176 |

| 7.15.3 Timing Parameter Examples                         | 176 |

| 7.16 Page Table/Timers                                   | 180 |

| 7.17 Reorder Queues                                      | 180 |

| 7.17.1 Queue Sizes                                       | 180 |

| 7.17.2 Queue Filling                                     | 181 |

| 7.17.3 Queue Entries                                     | 181 |

| 7.17.4 Queue Page Policy                                 |     |

|                                                          |     |

| 7.17.6 Queue Write Conflicts                             | 184 |

| 7.17.7 Queue Write High Watermarks                       | 184 |

| 7.17.8 Queue Grant Mode                                  | 185 |

| 7.18 Command Arbiter                                     | 186 |

| 7.18.1 Queue to Queue Arbitration                        |     |

| 7.18.2 Fast Path                                         | 188 |

| 7.18.3 Intra Queue Arbitration                           | 189 |

| 7.18.4 RW Arbitration Mode                               | 189 |

| 7.18.5 Two Cycle Addressing                              | 190 |

| 7.18.6 Multiple Commands                                 |     |

| 7.18.6.1 RMW                                             | 190 |

| 7.18.6.2 128 Byte Transfers                              | 191 |

| 7.18.7 Enforced Ordering                                 | 191 |

| 7.19 ECC                                                 | 191 |

| 7.19.1 ECC Introduction                                  | 191 |

| 7.19.2 Writes                                            | 194 |

| 7.19.3 Reads                                             | 195 |

| 7.19.4 Partial Writes                                    | 195 |

| 7.19.5 Syndrome Decode                                   | 196 |

| 7.19.5.1 Nibble in Error                                 | 196 |

| 7.19.5.2 Bits in Error                                   | 203 |

| 7.19.5.3 Single Bit Errors                               |     |

| 7.19.5.4 Address Parity and Special Uncorrectable Errors | 205 |

| 7.19.5.5 Syndrome Decode Summary                         | 205 |

| 7.19.6 Error Logging                                     | 205 |

| 7.19.7 Error Reporting                                   | 206 |

| 7.19.8 Error Injection                                   | 207 |

| 7.19.9 Byte Lane Substitution                            | 207 |

| 7.20 Scrub                                               | 208 |

| 7.20.1 General                                           | 208 |

| 7.20.2 Scrub Arbitration                                 | 208 |

| 7.20.3 Scrub Addresses                                   | 208 |

| 7.20.4 Immediate with Fill Mode                          |     |

| 7.20.5 Background Mode                                   | 210 |

| 7.20.6 Immediate Mode                                    | 210 |

| 7.21 External Connections Overview                      | 211 |

|---------------------------------------------------------|-----|

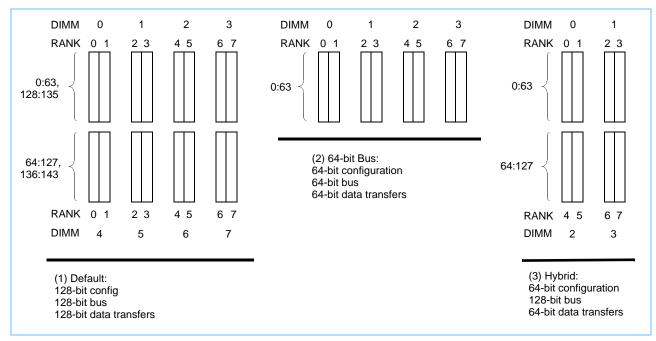

| 7.21.1 Bus Configurations                               | 212 |

| 7.21.2 External Data Multiplexers                       |     |

| 7.21.3 Unused I/O                                       | 213 |

| 7.22 DDR2 PHY                                           | 213 |

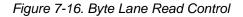

| 7.22.1 Byte Lanes                                       | 213 |

| 7.22.2 Clusters                                         | 214 |

| 7.22.3 Relationship to Board Wiring                     | 214 |

| 7.22.4 Bus Driving                                      | 215 |

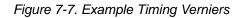

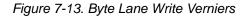

| 7.22.5 Verniers                                         |     |

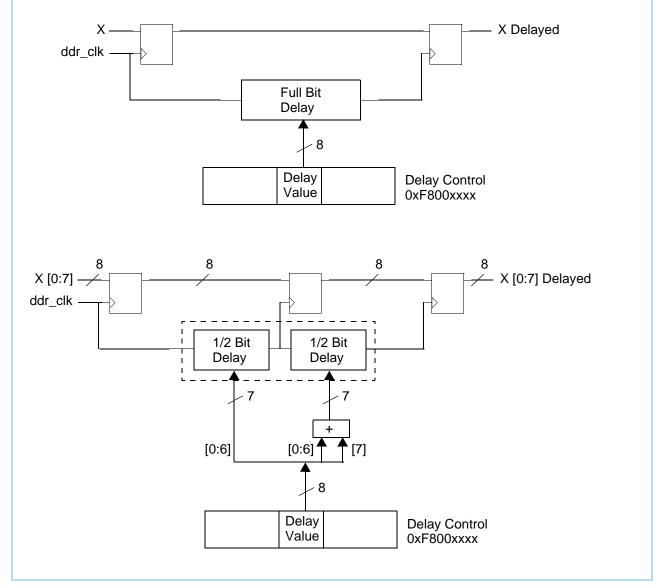

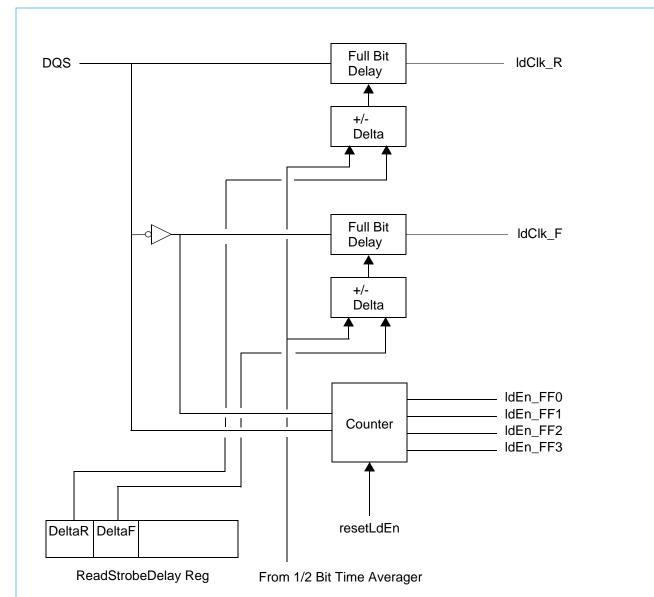

| 7.22.6 1/2 Bit Time Averager                            |     |

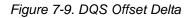

| 7.22.7 DQS 1/2 Bit Time Offset                          | 218 |

| 7.23 I/O Pad Control                                    | 220 |

| 7.23.1 I/O Pad Bit Settings                             |     |

| 7.23.2 Relationship to Memory Chip Settings             | 222 |

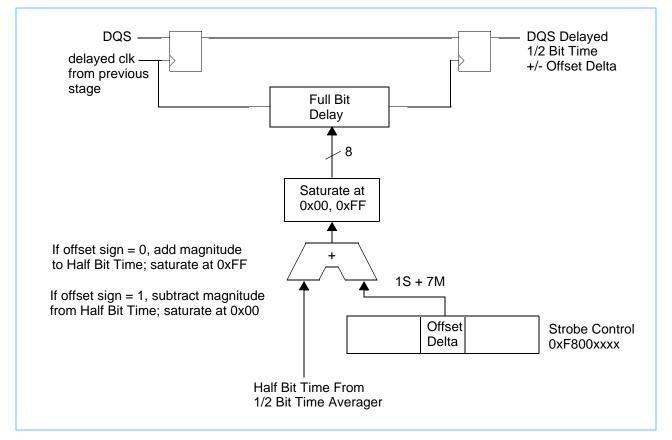

| 7.24 Memory Clocks                                      | 222 |

| 7.25 Memory Control Signals                             | 223 |

| 7.25.1 Adjustable Cycle Delay                           | 223 |

| 7.25.2 Command                                          | 224 |

| 7.25.3 Address                                          | 224 |

| 7.25.4 Chip Select                                      | 224 |

| 7.25.5 CKE - Clock Enables                              | 224 |

| 7.25.6 Dynamic CKE                                      | 225 |

| 7.25.7 ODT - On Die Termination                         |     |

| 7.25.7.1 ODT Operation                                  |     |

| 7.25.7.2 ODT Timing                                     |     |

| 7.25.7.3 Other ODT Considerations                       |     |

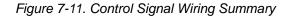

| 7.25.8 Control Signal Summary                           |     |

| 7.26 Data Timing Coarse Controls                        | 229 |

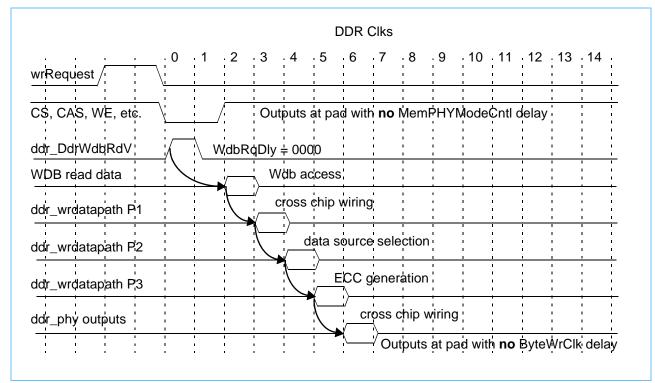

| 7.27 Write Data Timing                                  | 229 |

| 7.27.1 Write Coarse Timing                              |     |

| 7.27.2 Write Vernier Timing                             | 230 |

| 7.28 Read Data Timing                                   |     |

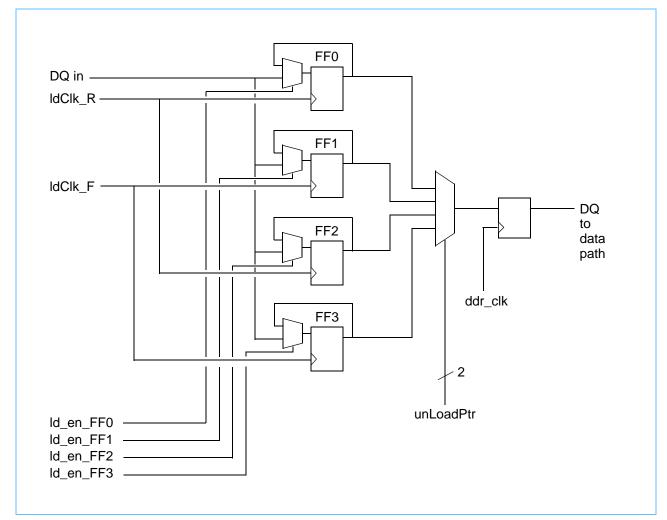

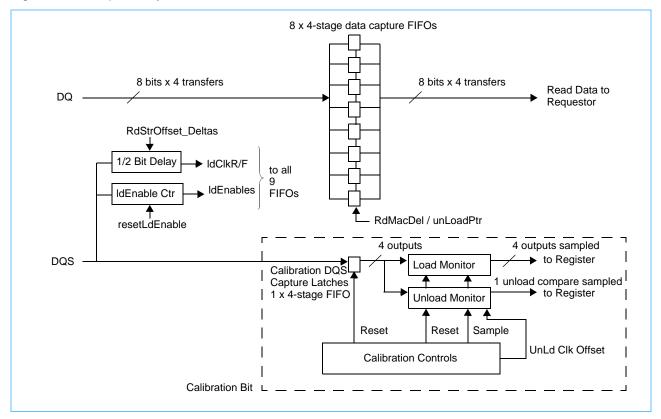

| 7.28.1 Read Timing Overview                             | 233 |

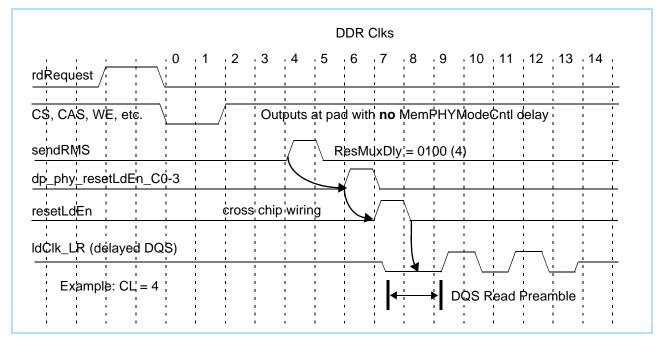

| 7.28.2 Read ResetLdEn Timing                            | 236 |

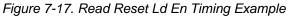

| 7.28.3 Read Unload Timing                               | 238 |

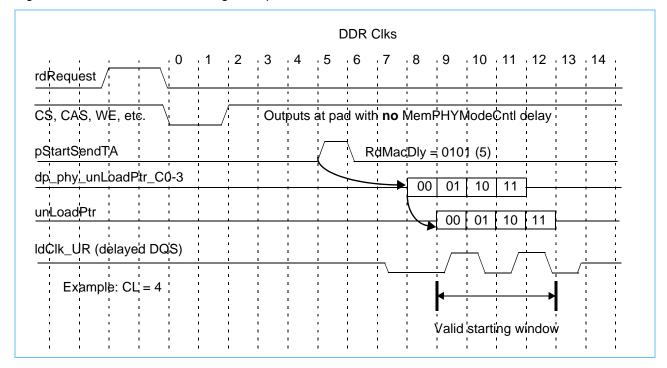

| 7.29 Output Enable Timing                               | 240 |

| 7.29.1 OE Coarse Timing                                 | 240 |

| 7.29.2 OE Vernier Timing                                | 241 |

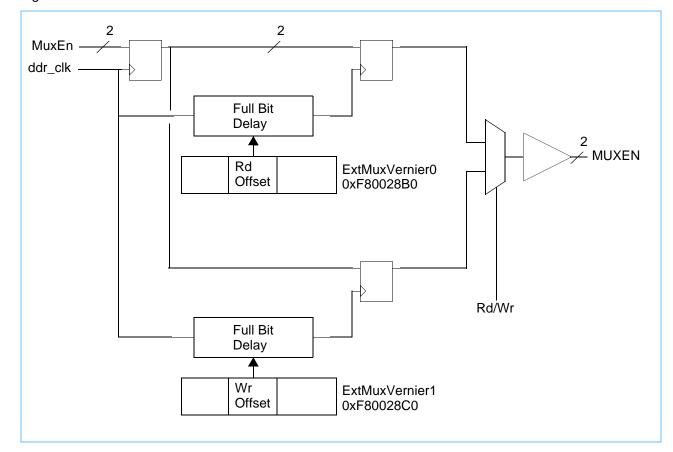

| 7.30 External Multiplexer Timing                        | 242 |

| 7.30.1 ExtMux Coarse Timing                             | 242 |

| 7.30.2 ExtMux Vernier Timing                            | 244 |

| 7.31 DDR2 PHY Calibration Logic                         | 245 |

| 7.31.1 Calibration Logic Overview                       |     |

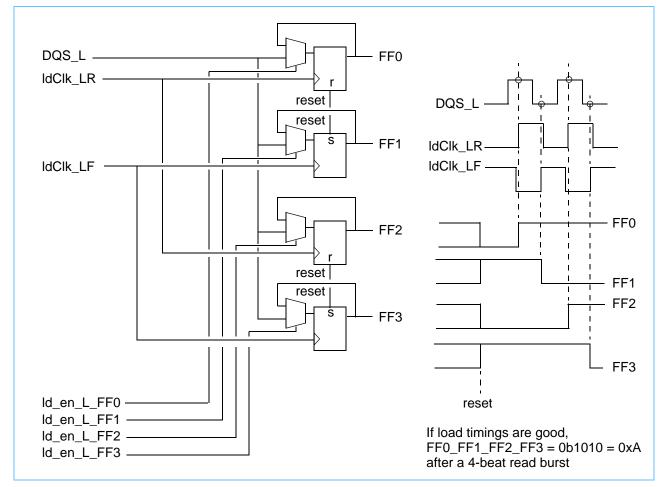

| 7.31.2 Calibration Bit DQS Capture Latches              |     |

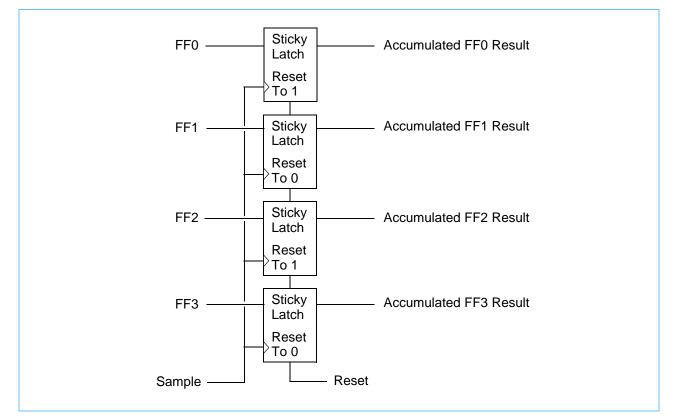

| 7.31.3 Calibration Load Monitor                         |     |

| 7.31.3.1 Summary of Load Calibration in Pulsed Mode     | 252 |

| 7.31.3.2 Summary of Load Calibration in Continuous Mode | 252 |

| 7.31.4 ResetLdEnable                                    |     |

|    | 7.31.5 Calibration Unload Monitor                                                        | 254 |

|----|------------------------------------------------------------------------------------------|-----|

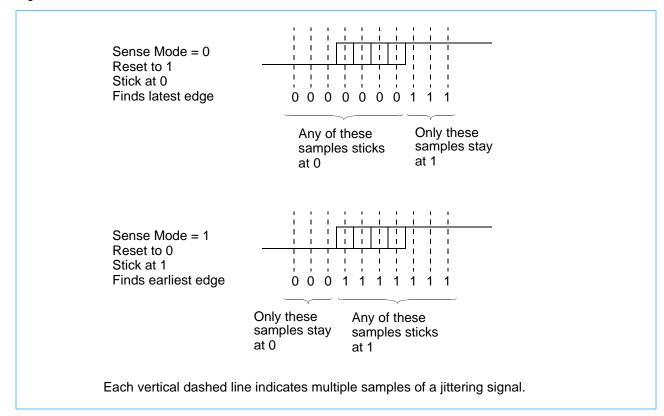

|    | 7.31.6 Jitter Considerations                                                             | 258 |

|    | 7.31.7 Calibration Setup                                                                 | 260 |

|    | 7.31.8 Single Step Mode                                                                  | 261 |

|    | 7.31.8.1 Single Step Use Summary                                                         | 261 |

|    | 7.31.9 Autocalibration Mode                                                              | 262 |

|    | 7.31.9.1 Autocal Overview                                                                | 262 |

|    | 7.31.9.2 Bytelane Selection                                                              | 262 |

|    | 7.31.9.3 Calibration Mode Selection                                                      |     |

|    | 7.31.9.4 Generated Vernier Control Values                                                | 263 |

|    | 7.31.9.5 FSM Pass/Fail Determination                                                     | 264 |

|    | 7.31.9.6 Control and Delay Measurement                                                   | 265 |

|    | 7.31.9.7 Autocalibration Use Summary                                                     | 265 |

| 8. | I2C Interfaces                                                                           | 267 |

| •- | 8.1 Overview                                                                             |     |

|    | 8.2 I2C Slave Interface                                                                  |     |

|    | 8.2.1 I2C Slave Interface Transactions                                                   |     |

|    | 8.2.1.1 Control Register transaction types                                               |     |

|    | 8.2.1.2 I2C Transactions to any Physical Memory Location                                 |     |

|    | 8.3 I2C Master Interface                                                                 |     |

|    |                                                                                          |     |

|    | 8.3.1 Overview                                                                           |     |

|    | 8.3.2 I2C Master Control Registers                                                       |     |

|    | 8.3.2.1 MODE Register Usage                                                              |     |

|    | 8.3.2.2 CNTRL Register Usage                                                             |     |

|    | 8.3.2.3 STATUS Register Usage                                                            |     |

|    | 8.3.2.4 ISR & IER Register Usage<br>8.3.2.5 ADDR, SUBADDR, & DATA Register Usage         |     |

|    |                                                                                          |     |

|    | 8.3.2.6 REV Register<br>8.3.2.7 RISETIMECNT Register                                     |     |

|    | 8.3.2.8 BITTIMECNT Register                                                              |     |

|    |                                                                                          | 211 |

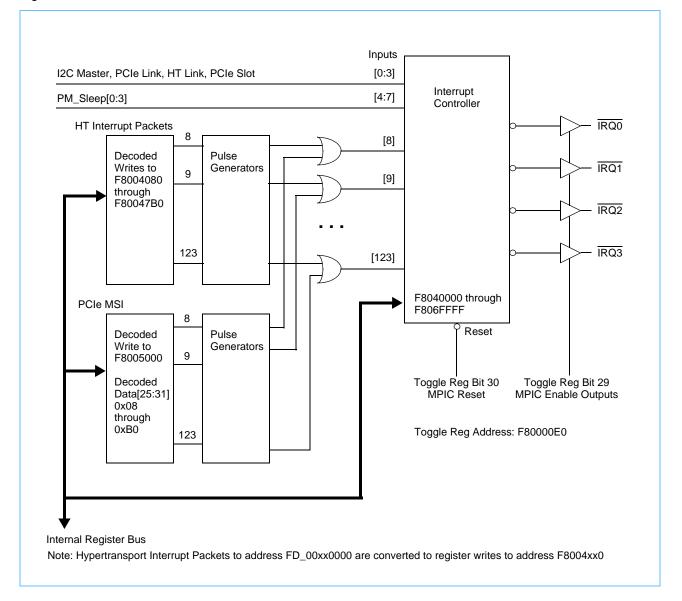

| 9. | MPIC                                                                                     | 279 |

|    | 9.1 Feature Summary                                                                      | 279 |

|    | 9.2 MPIC Organization                                                                    | 280 |

|    | 9.3 Interrupt Inputs                                                                     | 281 |

|    | 9.3.1 Interrupt 0, I2C Master                                                            |     |

|    | 9.3.2 Interrupt 1, PCIe Link Error                                                       |     |

|    | 9.3.3 Interrupt 2, HT Link                                                               |     |

|    | 9.3.4 Interrupt 3, PCIe Slot                                                             |     |

|    | 9.3.5 Interrupts 4:7, PM_Sleep[0:3]                                                      |     |

|    | 9.3.6 Interrupts 8:123, HT Posted Write Interrupts, and PCIe Message Signaled Interrupts |     |

|    | 9.3.6.1 HT Posted Write Interrupts                                                       | 282 |

|    | 9.3.6.2 PCIe Message Signaled Interrupts                                                 |     |

|    | 9.3.6.3 Merging of HT and PCIe Interrupts                                                |     |

|    | 9.3.6.4 Generating Interrupts with Register Writes                                       | 283 |

|    | 9.3.7 Interrupt Input Summary                                                            |     |

|    | 9.4 Interrupt Outputs                                                                    | 285 |

|    | 9.5 Interrupt Controller                                                                 |     |

|    |                                                                                          |     |

| 9.5.1 Global Reset/Enable                                                    | 285 |

|------------------------------------------------------------------------------|-----|

| 9.5.1.1 Toggle Register, MPICReset Bit                                       |     |

| 9.5.1.2 MPIC Global Configuration Register, Reset Controller Bit             |     |

| 9.5.1.3 MPIC Global Configuration Register, 8259 Pass Through Enable bit     |     |

| 9.5.2 Global Enable Summary                                                  |     |

| 9.5.3 Registers                                                              |     |

| 9.5.3.1 OpenPIC                                                              |     |

| 9.5.3.2 OpenPIC Compliance                                                   |     |

| 9.5.3.3 Deviations from the OpenPIC Specification                            |     |

| 9.5.4 Interrupt Setup                                                        |     |

| 9.5.4.1 Mask Bits                                                            |     |

| 9.5.4.2 Sense Bits                                                           |     |

| 9.5.4.3 Vectors                                                              |     |

| 9.5.4.4 Priorities                                                           |     |

| 9.5.5 Changing the Interrupt Setup                                           |     |

| 9.5.6 Interrupt Sequence                                                     |     |

| 9.5.7 Nesting of Interrupt Events                                            |     |

| 9.5.8 Spurious Interrupts                                                    |     |

| 9.5.9 Delivery Modes                                                         |     |

| 9.5.9.1 Directed Mode                                                        |     |

| 9.5.9.2 Distributed Mode                                                     |     |

| 9.5.9.3 Exactly Once Delivery                                                |     |

| 9.5.10 Processor Identification                                              |     |

| 9.5.11 I/O Interrupts                                                        |     |

| 9.5.12 Interprocessor Interrupts<br>9.5.12.1 IPI Priority Level Restrictions |     |

|                                                                              |     |

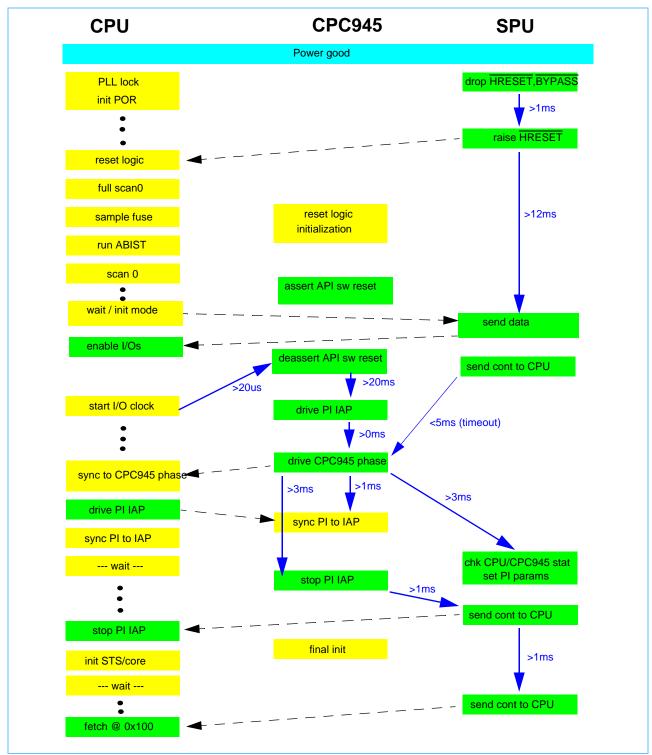

| 10. System Initialization Sequence                                           | 297 |

| 10.1 Introduction                                                            |     |

| 10.2 Power Sequencing                                                        |     |

| 10.3 Power-On Reset                                                          |     |

| 10.3.1 Hardware Reset Sequence                                               |     |

| 10.3.2 CPC945 Initialization                                                 |     |

| 10.3.3 CPC945 Initialization                                                 |     |

|                                                                              |     |

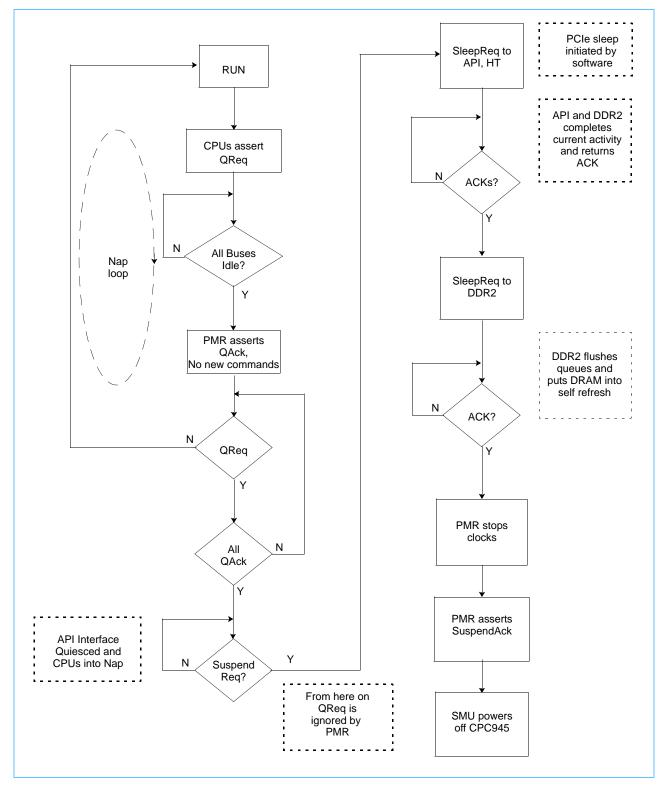

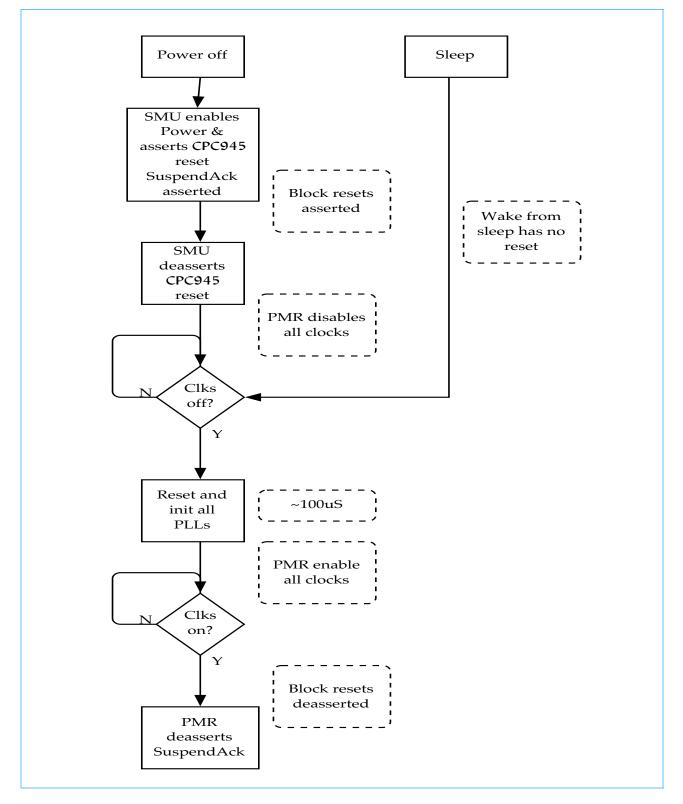

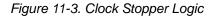

| 11. Power Management and Clocks                                              | 303 |

| 11.1 Introduction                                                            |     |

| 11.2 System Power Management                                                 |     |

| 11.2.1 CPC945 and Processor State Definitions                                |     |

| 11.2.2 CPC945 Top Level Power Manager                                        |     |

| 11.2.3 PLLs                                                                  |     |

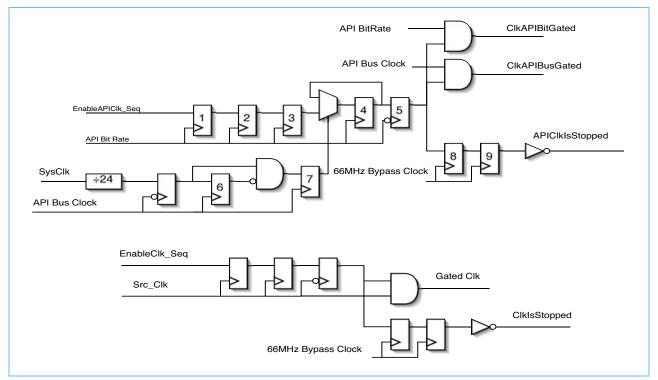

| 11.2.4 Clock Stoppers                                                        |     |

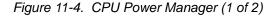

| 11.3 CPU Power Management                                                    |     |

| 11.3.1 CPU Power Management                                                  |     |

| 11.3.2 Processor Interconnect Power Manager                                  |     |

| 11.3.2.1 PLL1                                                                |     |

| 11.3.3 DDR2 Power Management (PLL2)                                          |     |

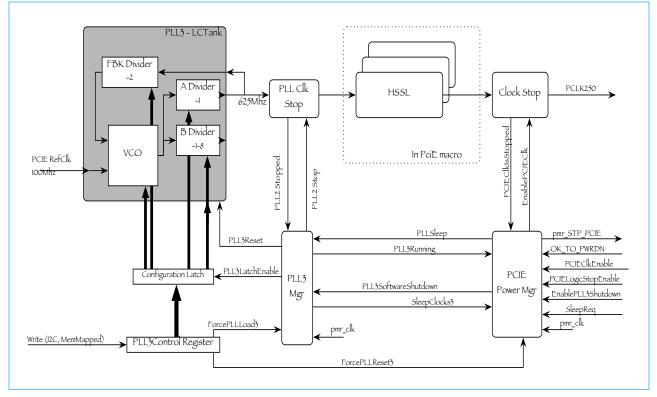

| 11.3.4 PCI Express Power Management                                          |     |

|                                                                              |     |

| 11.3.4.1 PLL3                                                                |     |

| <b>CPC945</b> | Bridge | and | Memory | Controller |

|---------------|--------|-----|--------|------------|

|               |        |     |        |            |

|     | 11.3.5 HyperTransport Power Management                                    | 314 |

|-----|---------------------------------------------------------------------------|-----|

|     | 11.3.5.1 LDTReq and LDTStop Generation                                    | 314 |

|     | 11.3.5.2 HyperTransport Power Manager                                     | 315 |

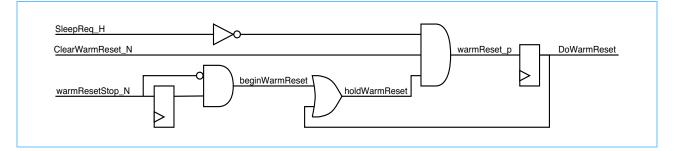

|     | 11.3.5.3 PLL4                                                             | 315 |

|     | 11.4 Power Tuning                                                         | 316 |

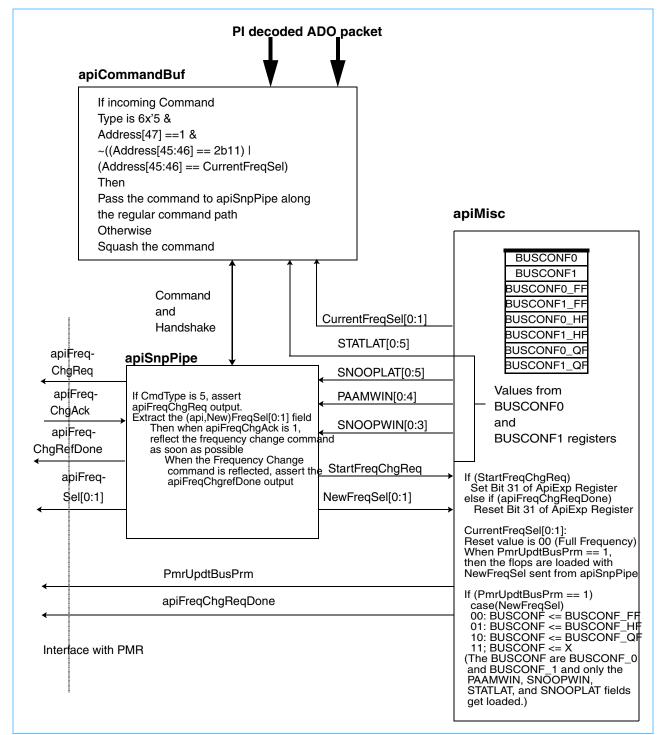

|     | 11.5 PI Frequency Change Operation                                        | 319 |

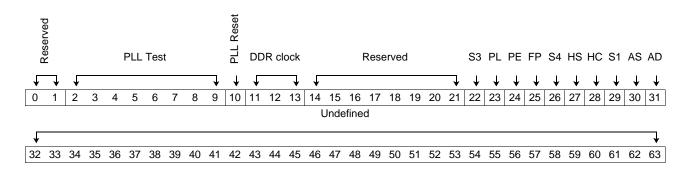

|     | 11.6 PLL Programming                                                      | 322 |

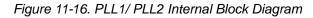

|     | 11.6.1 PLL1 and PLL2                                                      |     |

|     | 11.6.2 PLL3                                                               | 324 |

|     | 11.6.3 PLL4                                                               | 325 |

| 12  | Programmer's Interface                                                    | 327 |

| 12. | 12.1 Memory Map                                                           |     |

|     |                                                                           |     |

|     | 12.2 Memory-Like Space                                                    |     |

|     | 12.2.1 DRAM<br>12.2.2 Noncoherent DRAM Access                             |     |

|     | 12.2.3 ROM                                                                |     |

|     | 12.2.3 ROM                                                                |     |

|     | 12.2.5 PCI Express Configuration Space                                    |     |

|     |                                                                           |     |

|     | 12.3 Control Register Memory Map                                          |     |

|     | 12.4 CPC945 Control Registers                                             |     |

|     | 12.4.1 CPC945 Revision Register<br>12.4.2 Who Am I Bus Master ID Register |     |

|     | 12.4.2 Who Am r bus Master ID Register                                    |     |

|     | 12.4.4 Hardware Initialization State Register                             |     |

|     | 12.4.5 CPC945 Toggle Register                                             |     |

|     | 12.5 Clocks and Power Management Registers                                |     |

|     | 12.5.1 Clock Control Register                                             |     |

|     | 12.5.2 System Power Management Register                                   |     |

|     | 12.5.3 CPU Power Management Register                                      |     |

|     | 12.5.4 CPU Quiesce Timing Register                                        |     |

|     | 12.5.5 HyperTransport Power Management Register                           |     |

|     | 12.5.6 PLL1 Control Register                                              |     |

|     | 12.5.7 PLL2 Control Register                                              |     |

|     | 12.5.8 PLL3 Control Register                                              | 352 |

|     | 12.5.9 PLL4 Control Register                                              | 355 |

|     | 12.5.10 PLL/Clock Visibility and Test                                     | 358 |

|     | 12.6 MPIC Registers                                                       | 359 |

|     | 12.6.1 MPIC Feature Reporting Register                                    | 360 |

|     | 12.6.2 MPIC Global Configuration Register 0                               | 361 |

|     | 12.6.3 MPIC Vendor ID Register                                            |     |

|     | 12.6.4 MPIC Processor Initialization Register                             |     |

|     | 12.6.5 MPIC IPI (0,1,2,3) Vector/Priority Registers                       |     |

|     | 12.6.6 MPIC Spurious Vector Register                                      |     |

|     | 12.6.7 MPIC Interrupt Source 0-123 Vector/Priority Registers              |     |

|     | 12.6.8 MPIC Interrupt Source 0-123 Destination Registers                  |     |

|     | 12.6.9 MPIC CPU(0-3) IPI(0-3) Dispatch Command Registers                  |     |

|     | 12.6.10 MPIC CPU(0-3) Current Task Priority Registers                     |     |

|     | 12.6.11 MPIC CPU(0-3) Interrupt Acknowledge Registers                     | 368 |

| 12.6.12 MPIC CPU(0-3) End-of-Interrupt Registers                      | 369   |

|-----------------------------------------------------------------------|-------|

| 12.7 PI Physical Interface Registers                                  |       |

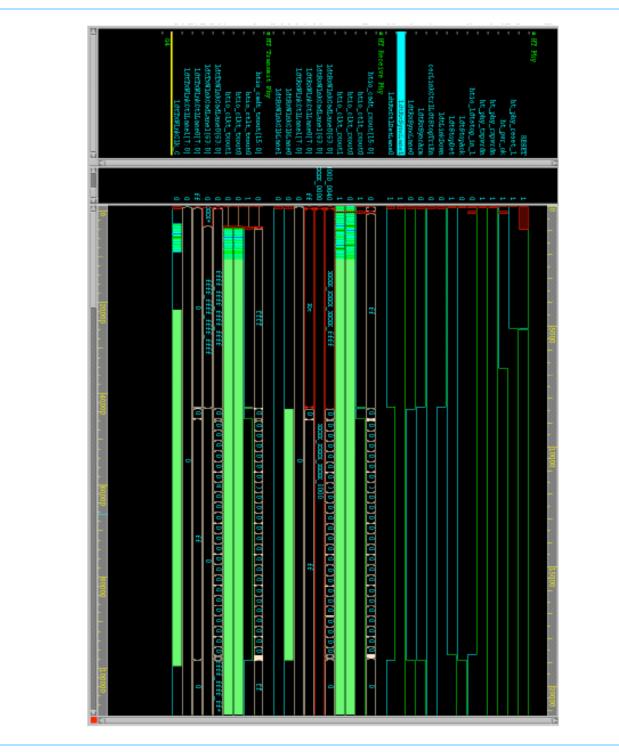

| 12.7.1 APIPhy Command and Status Register Bus                         | 370   |

| 12.7.2 PI Physical Interface Registers                                |       |

| 12.7.3 APIPhy Configuration Registers                                 | . 375 |

| 12.7.3.1 APIPhy Driver IAP Pattern Mask (APIPhyDRVIAPPATMASK)         | 375   |

| 12.7.3.2 APIPhy Receiver IAP Pattern Mask (APIPhyRCVIAPPATMASK)       |       |

| 12.7.4 APIPhy Configuration 0 Register (APIPhyCONFIGREG0)             |       |

| 12.7.4.1 APIPhy Configuration 1 Register (APIPhyCONFIGREG1)           |       |

| 12.7.4.2 APIPhy Shorts Test Configuration Register (APIPhySTR)        | 381   |

| 12.7.4.3 APIPhy Status 0 Register (APIPhySTAT0)                       |       |

| 12.7.4.4 APIPhy Receiver Mode and Command Register (APIPhyRcvModeCmd) |       |

| 12.7.4.5 APIPhy Receiver IAP State Register (APIPhyRIAPSTATE)         |       |

| 12.7.4.6 APIPhy Data Error 0 Register (DATAERROR0)                    |       |

| 12.7.4.7 APIPhy Data Error 1 Register (DATAERROR1)                    | 389   |

| 12.7.4.8 APIPhy Data Error 2 Register (DATAERROR2)                    | 390   |

| 12.7.4.9 APIPhy Data Error 3 Register (APIPhyDATAERROR3)              | 391   |

| 12.7.4.10 APIPhy Data Error 4 Register (APIPhyDATAERROR4)             |       |

| 12.7.4.11 APIPhy Data Error 5 Register (APIPhyDATAERROR5)             |       |

| 12.7.4.12 APIPhy I/O Control Register (APIPhyIOCTRL)                  | 394   |

| 12.7.4.13 APIPhy PMR I/O Control Register (APIPhyPMRIOCTRL)           | 396   |

| 12.7.5 Related Registers                                              | 397   |

| 12.7.5.1 Bus Encode Disable                                           | 397   |

| 12.8 DRAM I2C Master Controller Registers                             | . 398 |

| 12.8.1 I2C Controller MODE Register                                   |       |

| 12.8.2 I2C Controller CNTRL Register                                  | 400   |

| 12.8.3 I2C Controller STATUS Register                                 |       |

| 12.8.4 I2C Controller Interrupt Status (ISR) Register                 |       |

| 12.8.5 I2C Controller Interrupt Enable (IER) Register                 | 403   |

| 12.8.6 I2C Controller ADDR Register                                   | 404   |

| 12.8.7 I2C Controller SUBADDR Register                                | 404   |

| 12.8.8 I2C Controller Data Transmit/Receive Register                  | 405   |

| 12.8.9 I2C Controller Revision Register                               | . 405 |

| 12.8.10 I2C Controller RISETIMECNT Register                           | . 406 |

| 12.8.11 I2C Controller BITTIMECNT Register                            | 407   |

| 12.9 Advanced Processor Interconnect Registers                        | 408   |

| 12.9.1 API Proc Command Slot Configuration Register (APIProcCmd)      |       |

| 12.9.2 API I/O Pending Queue Configuration Register (APIIOPnd)        | 411   |

| 12.9.3 API Command Arbitration Register (APICmdArb)                   | 412   |

| 12.9.4 API Target Request Queue Configuration Register (APITRqCfg)    | 414   |

| 12.9.5 API Target Response Queue Configuration Register (APITRspCfg)  | 415   |

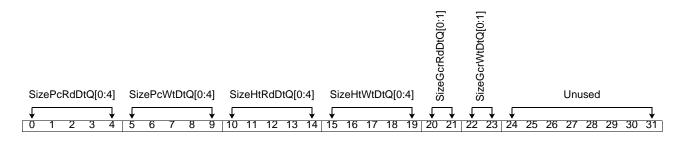

| 12.9.6 API Target Data Queue Configuration Register (APIDtQCfg)       | 416   |

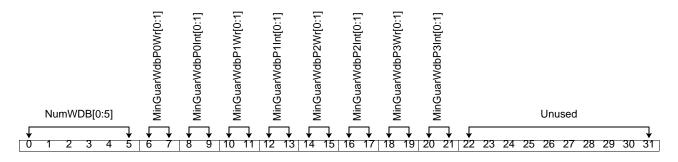

| 12.9.7 API Write Data Buffer (WDB) Configuration Register (APIWdbCfg) | 417   |

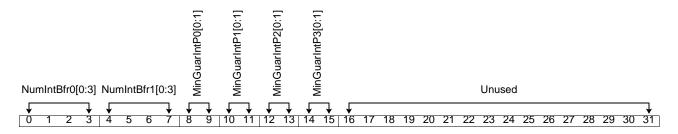

| 12.9.8 API Intervention Buffer Configuration Register (APIIntCfg)     | 418   |

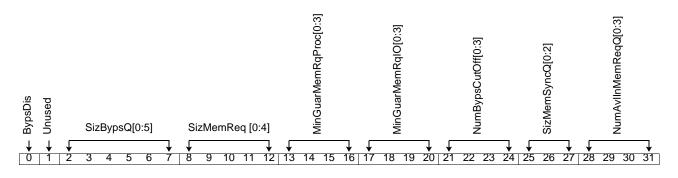

| 12.9.9 API Memory Request Configuration Register (APIMemReqCfg)       | 419   |

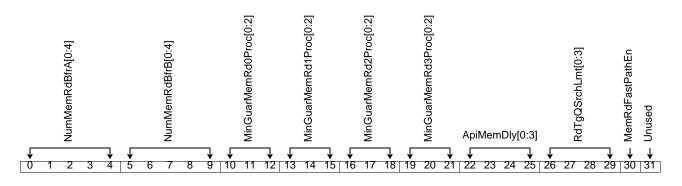

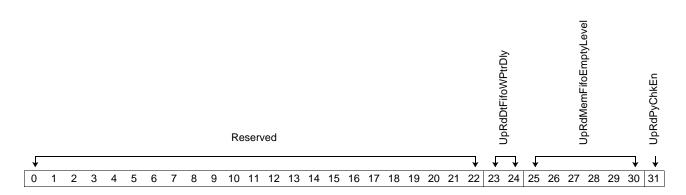

| 12.9.10 API Memory Read Configuration Register (APIMemRdCfg)          | 421   |

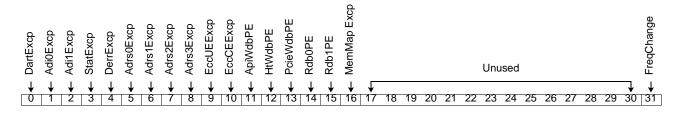

| 12.9.11 API Exception Register (APIExcp)                              |       |

| 12.9.12 API Exception Mask 0 Register (APIMask0)                      | 424   |

| 12.9.13 API Exception Mask 1 Register (APIMask1)                      |       |

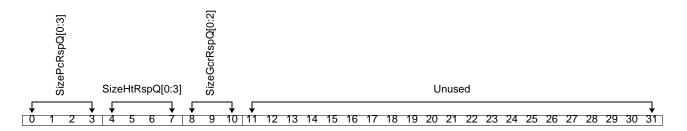

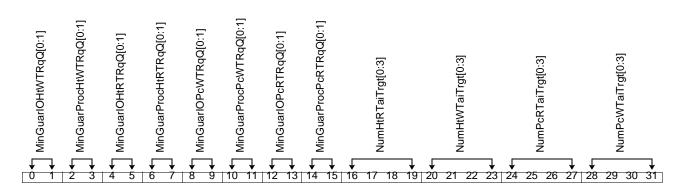

| 12.9.14 API Target Request Queues Guarantees Register (APITRqGuar)    | 427   |

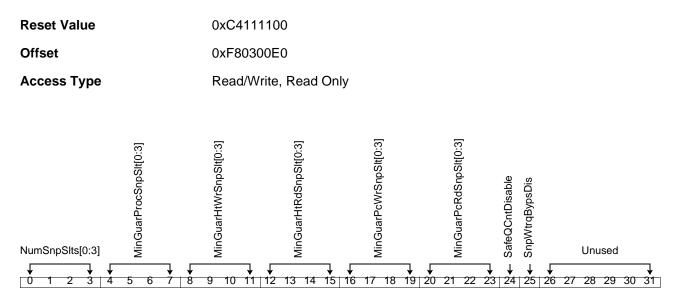

| 12.9.15 API Snoop Slot Configuration Register (APISnpSltCfg)             |              |

|--------------------------------------------------------------------------|--------------|

| 12.9.16 API Bus Configuration Registers                                  |              |

| 12.9.16.1 PI PAAM Window (APIPaamWin)                                    | . 430        |

| 12.9.16.2 API Snoop Window (APISnoopWin)                                 | . 431        |

| 12.9.16.3 I/O Snoop Window (APIIOSnoopWin)                               | . 432        |

| 12.9.16.4 API Handshake Status Latency (APIStatLat)                      | . 433        |

| 12.9.16.5 API Snoop Latency Values (APISnoopLat)                         | . 434        |

| 12.9.17 PSRO Register (PSRO)                                             | . 435        |

| 12.9.18 PI System Command Registers                                      | . 436        |

| 12.9.18.1 System Command Control [0:1] Registers (SysCmdCntl[0:1])       | . 437        |

| 12.9.18.2 System Command Status Register (SysCmdStat)                    |              |

| 12.9.18.3 System Command Data0 Register (SysCmdDt0)                      |              |

| 12.9.18.4 System Command Data1 Register (SysCmdDt1)                      |              |

| 12.9.18.5 System Command Data2 Register (SysCmdDt2)                      |              |

| 12.9.18.6 System Command Data3 Register (SysCmdDt3)                      |              |

| 12.9.19 DART Control Register (DARTCNTL)                                 |              |

| 12.9.20 DART Base Register (DARTBASE)                                    |              |

| 12.9.21 DART Size Register (DARTSIZE)                                    |              |

| 12.9.22 DART Exception Status Register (DARTEXCP)                        |              |

| 12.9.23 Entry in DART TLB Tag Array Register (DARTTAG)                   |              |

| 12.9.24 Entry in DART TLB Data Array Register (DARTDATA)                 |              |

| 12.10 Memory Control Registers                                           |              |

| 12.10 Memory Control Registers                                           |              |

| 12.10.1 1 RAS Command Timer0 Register (RASTimer0)                        |              |

| 12.10.1.2 RAS Command Timer Register (RASTimer0)                         |              |

| 12.10.1.2 CAS Command Timer Register (CASTimer0)                         | . 451<br>152 |

| 12.10.1.4 CAS Command Timer1 Register (CASTimer0)                        |              |

| 12.10.1.4 GAG Command Timer (Register (CAG Timer))                       |              |

| 12.10.2 Memory Programming Control Register (MemProgCntl)                |              |

| 12.10.4 Mode Register Set (MRS) Register (MRSRegCntl) and Extended Mode  | . 450        |

| Register Set Register (EMRSRegCntl)                                      | 157          |

| 12.10.5 Memory Mapping Exception Registers                               |              |

| 12.10.5.1 Memory Mapping Exception Address Register (MemMapExcpAd)       |              |

| 12.10.5.1 Memory Mapping Exception Address Register (MeminapExcpAd)      |              |

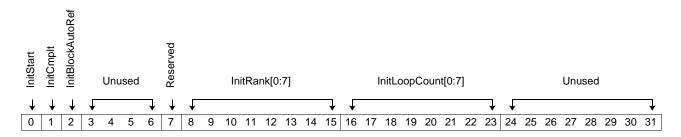

| 12.10.5.2 Memory Initialization Registers [0:15] (MemInitReg[0:15])      |              |

|                                                                          | 100          |

| 12.10.7 DIMM Configuration Registers                                     |              |

|                                                                          |              |

| 12.10.9 Memory User Configuration Register (UsrCnfg)                     |              |

| 12.10.10 Memory Read Request Queue Configuration Register (MemRdQCnfg)   |              |

| 12.10.11 Memory Write Request Queue Configuration Register (MemWrtQCnfg) |              |

| 12.10.12 Memory Reorder Queue Arbitration Register (MemQArb)             |              |

| 12.10.13 Memory R/W Arbitration Register (MemRWArb)                      |              |

| 12.10.14 Memory Bus Configuration Register (MemBusConfig)                |              |

| 12.10.15 Memory Bus Configuration Register 2                             |              |

| 12.10.16 ODT Control Register (ODTCntl)                                  |              |

| 12.10.17 Memory Scrub Control Register (MSCR)                            |              |

| 12.10.18 Memory Scrub Range Start Register (MSRSR)                       |              |

| 12.10.19 Memory Scrub Range End Register (MSRER)                         |              |

| 12.10.20 Memory Scrub Pattern Register (MSPR)                            |              |

| 12.10.21 Memory Check Control Register (MCCR)                            | . 479        |

|                                                                          |              |

| 12.10.22 Memory Error Address Registers                            | 480 |

|--------------------------------------------------------------------|-----|

| 12.10.22.1 MEAR0 Register (MEAR0)                                  | 480 |

| 12.10.22.2 MEAR1 Register (MEAR1)                                  | 481 |

| 12.10.23 Memory Error Syndrome Register (MESR)                     |     |

| 12.10.24 Memory Mode Control Register (MemModeCntl)                | 483 |

| 12.10.25 Mem PHY Mode Control Register (MemPhyModeCntl)            | 485 |

| 12.10.26 I/O Pad Control Register (IOPadCntl)                      | 487 |

| 12.10.27 Write Strobe Control Registers (ByteWrClkDelay)           | 489 |

| 12.10.28 Read Data Strobe Control Registers (ReadStrobeDelay)      | 491 |

| 12.10.29 CK Control Registers (CKDelay)                            | 493 |

| 12.10.30 Reset LdEn Offset Delay Registers (RstLdEnVerniersCn)     | 494 |

| 12.10.31 External Data Multiplexer Delay Registers (ExtMuxVernier) |     |

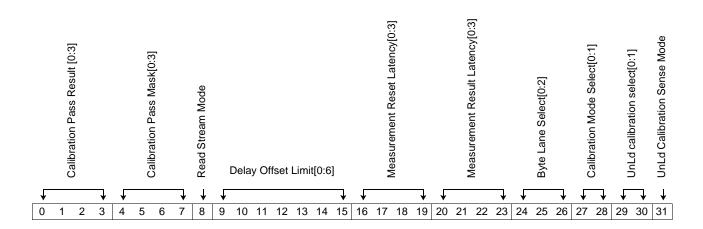

| 12.10.32 Calibration Control and Delay Measurement Registers       |     |

| 12.10.32.1 Half Bit Time Measurement Results                       | 497 |

| 12.10.33 Calibration Configuration Registers                       | 499 |

| 12.10.34 Calibration Read Margin Result Registers                  | 502 |

| 12.11 PCI Express Registers                                        | 505 |

| 12.11.1 PCIe Configuration Registers                               | 505 |

| 12.11.1.1 PCI 2.3 Configuration Space Header                       | 507 |

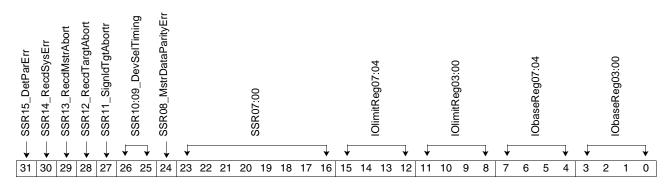

| 12.11.1.2 PCI Power Management Capability Structure                | 520 |

| 12.11.1.3 PCI Express Capability Structure                         | 524 |

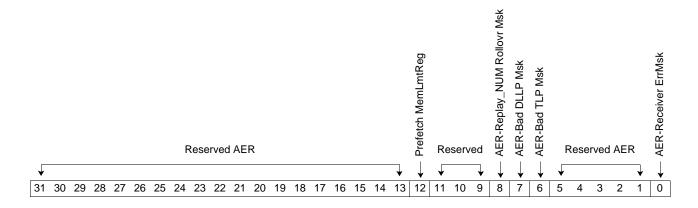

| 12.11.1.4 Advanced Error Reporting Extended Capability Structure   | 538 |

| 12.11.2 XBus PCI Express Configuration Registers                   | 551 |

| 12.11.2.1 Legacy Interrupt Control Register                        | 553 |

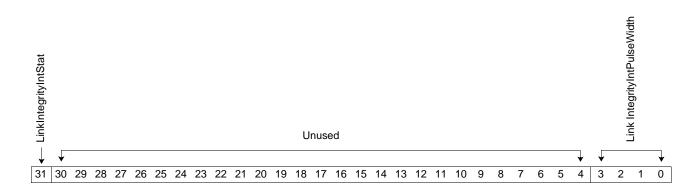

| 12.11.2.2 Link Integrity Interrupt Control Register                | 554 |

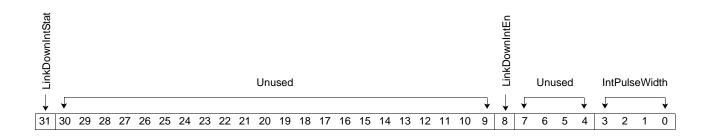

| 12.11.2.3 Link Down Interrupt Control Register                     | 555 |

| 12.11.2.4 PCI Express 0 Address Mask Register                      |     |

| 12.11.2.5 Memory Read Completion Time-Out Register                 | 558 |

| 12.11.2.6 I/O Completion Time-Out Register                         | 558 |

| 12.11.2.7 Configuration Completion Time-Out Register               |     |

| 12.11.2.8 Local Completion Time-Out Register                       |     |

| 12.11.2.9 Maximum Advertised Posted Credits Register               |     |

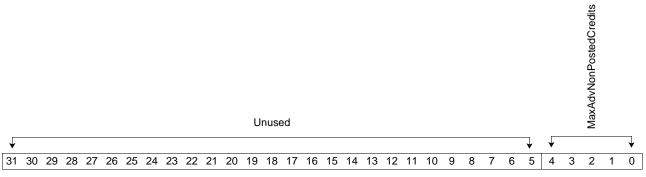

| 12.11.2.10 Maximum Advertised Nonposted Credits Register           |     |

| 12.11.2.11 Number of Reserved Posted Credits Register              |     |

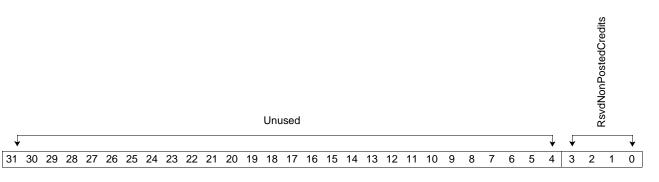

| 12.11.2.12 Number of Reserved Nonposted Credits Register           |     |

| 12.11.2.13 Maximum Available Tags Register                         |     |

| 12.11.2.14 Completion Arbiter Priority Register                    | 565 |

| 12.11.2.15 Version Number Register                                 |     |

| 12.11.2.16 L1 Power Mode Request Response Register                 |     |

| 12.11.2.17 Interrupt Filter Register (UNUSED)                      |     |

| 12.11.2.18 Last NAK'd Write Address Register                       |     |

| 12.11.2.19 Transmission Error Count Register                       |     |

| 12.11.2.20 Dispatch Read Mode Register                             |     |

| 12.11.2.21 No Snoop Request Mode Register                          |     |

| 12.11.2.22 Direct Access Mode Register                             |     |

| 12.11.2.23 L23 Message Time-Out Register                           |     |

| 12.11.2.24 Invalid Transaction Register                            |     |

| 12.11.2.25 Configuration 4 Or 8 Register                           |     |

| 12.11.2.26 Unlock Protected Register                               |     |

| 12.11.2.27 Coherent Memory Write Tag Delay Register (UNUSED)       | 576 |

|    | 12.11.2.28 Block Transactions During Configuration Reads Register                 |     |

|----|-----------------------------------------------------------------------------------|-----|

|    | 12.11.2.29 CRC Error Count Register                                               |     |

|    | 12.11.2.30 Unsupported Request Or Completer Abort Register                        | 578 |

|    | 12.11.2.31 Enable Transaction Error Acknowledge On Unsupported Request            |     |

|    | Completion Register                                                               | 579 |

|    | 12.11.2.32 Enable Transaction Error Acknowledge On Completer Abort                |     |

|    | Completion Register                                                               | 580 |

|    | 12.11.2.33 Enable Transaction Error Acknowledge On Configuration Retry            |     |

|    | Time-Out Register                                                                 |     |

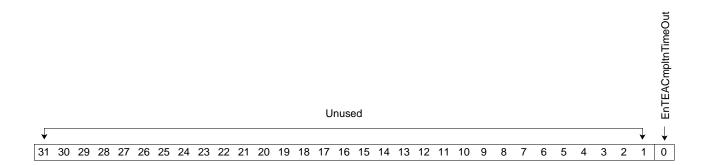

|    | 12.11.2.34 Enable Transaction Error Acknowledge On Completion Time-Out Register   | 582 |

|    | 12.11.2.35 Set PCIE04 Received Completer Abort On Completer Abort Register        | 583 |

| 12 | 2.11.3 PCI Express GCR Registers                                                  | 584 |

|    | 12.11.3.1 CORE_X: PI Core Interface Parameters Register                           | 586 |

|    | 12.11.3.2 BEACON: Beacon Support Register                                         |     |

|    | 12.11.3.3 LOOPBACK: Loopback Control and Status Register                          |     |

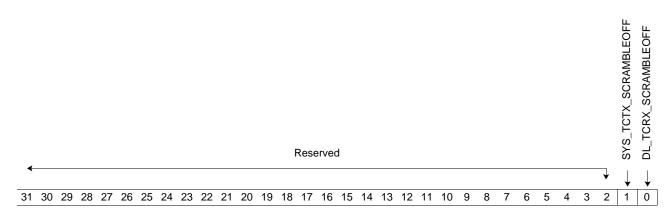

|    | 12.11.3.4 SCRAMBLE: Data Scrambling Configuration Register                        |     |

|    | 12.11.3.5 SLOT: Slot Management Register                                          |     |

|    | 12.11.3.6 POWER: Power Management Register                                        |     |

|    | 12.11.3.7 VC_STAT: Virtual Channel Status Register                                |     |

|    | 12.11.3.8 AL_CFG: Application Layer Configuration Register                        |     |

|    | 12.11.3.9 IO_CFG: I/O Configuration Register                                      |     |

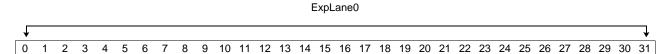

|    | 12.11.3.10 RX_LANE: I/O Receive Configuration Register                            |     |

|    | 12.11.3.11 I/O_LANEn: I/O Status and Control Register for Lane n                  |     |

|    | (n ranges from 015)                                                               | 595 |

|    | 12.11.3.12 DIAG_IBCPL: Diagnostic Register for Application Layer Inbound          |     |

|    | Completion (IbCpl)                                                                | 597 |

|    | 12.11.3.13 DIAG_IBCMGR: Diagnostic Register for Application Layer Inbound         |     |

|    | Completion Manager (IbCMgr)                                                       | 598 |

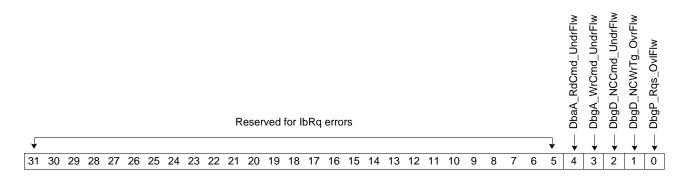

|    | 12.11.3.14 DIAG_IBRQ: Diagnostic Register for Application Layer Inbound           |     |

|    | Request (IbRq)                                                                    | 599 |

|    | 12.11.3.15 DIAG_IBTLIF: Diagnostic Register for Application Layer Inbound         |     |

|    | TL Interface (IbTLIf)                                                             | 600 |

|    | 12.11.3.16 DIAG_IBWD: Diagnostic Register for Application Layer Inbound           |     |

|    | Request (IbWD)                                                                    | 601 |

|    | 12.11.3.17 DIAG_OBCPL: Diagnostic Register for Application Layer Outbound         |     |

|    | Completion (ObCpl)                                                                | 603 |

|    | 12.11.3.18 DIAG_OBMSG: Diagnostic Register for Application Layer Outbound Message |     |

|    | (ObMsg)                                                                           | 604 |

|    | 12.11.3.19 DIAG_OBNP: Diagnostic Register for AL Outbound Nonposted (ObNP)        |     |

|    | 12.11.3.20 DIAG_OBP: Diagnostic Register for Application Layer Outbound           |     |

|    | Posted (ObP)                                                                      | 606 |

|    | 12.11.3.21 DIAG_OBTLIF: Diagnostic Register for Application Layer Outbound        |     |

|    | Posted (ObTLIf)                                                                   | 607 |

|    | 12.11.3.22 MASK_MPIC_IBCPL: MPIC Masking for DIAG_IBCPL                           |     |

|    | 12.11.3.23 MASK_MPIC_IBCMGR: MPIC Masking for DIAG_IBCMGR                         |     |

|    | 12.11.3.24 MASK_MPIC_IBRQ: MPIC Masking for DIAG_IBRQ                             |     |

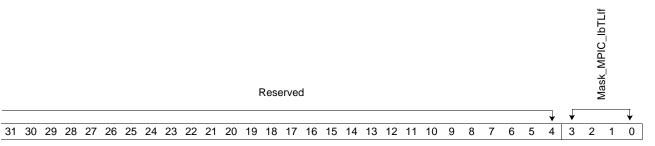

|    | 12.11.3.25 MASK_MPIC_IBTLIF: MPIC Masking for DIAG_IBTLIF                         |     |

|    | 12.11.3.26 MASK_MPIC_IBWD: MPIC Masking for DIAG_IBWD                             |     |

|    | 12.11.3.27 MASK_MPIC_OBCPL: MPIC Masking for DIAG_OBCPL                           |     |

|    | 12.11.3.28 MASK_MPIC_OBNP: MPIC Masking for DIAG_OBNP                             |     |

|    |                                                                                   |     |

| 12.11.3.29 MASK_MPIC_OBP: MPIC Masking for DIAG_OBP                                 |       |

|-------------------------------------------------------------------------------------|-------|

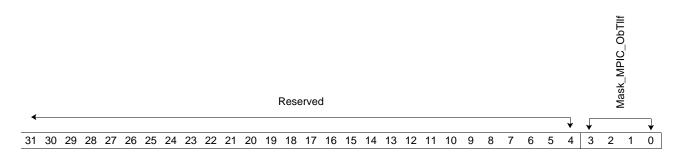

| 12.11.3.30 MASK_MPIC_OBTLIF: MPIC Masking for DIAG_OBTLIF                           |       |

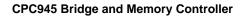

| 12.12 HyperTransport Registers (HT1)                                                | 614   |

| 12.12.1 HT Device ID/Vendor ID Register (Device ID/Vendor ID)                       |       |

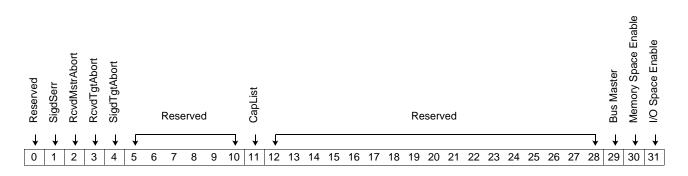

| 12.12.2 Status/Command Register (Status/Command)                                    |       |

| 12.12.3 Class Code/Revision Register (Class Code/Revision ID)                       |       |

| 12.12.4 BIST/Header Type Register (BIST/Header Type)                                |       |

| 12.12.5 Capabilities Pointer Register (Capability1)                                 |       |

| 12.12.6 Interrupt Line Register (IntrLine)                                          |       |

| 12.12.7 Command/Pointer/Capability ID Register (HTCapability00)                     | 625   |

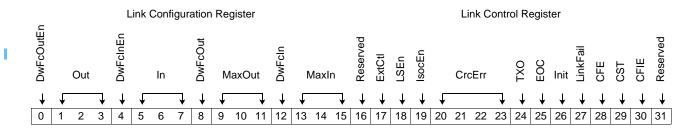

| 12.12.8 Link Config/Link Control Register (HTCapability04)                          |       |

| 12.12.9 LinkFreqCap/Link Error/Link Freq/ Revision ID Register                      | 628   |

| 12.12.10 Feature Capability Register (Feature)                                      | 629   |

| 12.12.11 Error Handling/Enumeration Scratchpad Register (ErrCtrl/Enum)              | 630   |

| 12.12.12 HT Address Mask Register                                                   | 632   |

| 12.12.13 HT1/PI Interface Control Register                                          |       |

| 12.12.14 Memory Read Delay for Memory Read Data Interface (HtMemDly)                | 633   |

| 12.12.15 Write TA delay for Write Data Interface (WrTADly)                          |       |

| 12.12.16 HTG Configuration (HTGCFG)                                                 | 635   |

| 12.12.17 Bridge Control Register (BrCtrl)                                           |       |

| 12.12.18 TxCtl/Rx Data Buffer Allocation Register (TxCtl/RxDataBufAlloc)            | 638   |

| 12.12.19 Maximum Transmit Buffer Counters Register (TxBufCountMax)                  | 639   |

| 12.12.20 Diagnostic CRC Registers (DiagRxCrc)                                       |       |

| 12.12.21 Receive and Transmit Synchronization FIFOs (Sri[Rx/Tx]Numerator)           | 641   |

| 12.12.21.1 SriRxNumeratorLower: Receive Synchronization FIFO Register               |       |

| Description (Bits [0:31])                                                           |       |

| 12.12.22 Receive and Transmit Synchronization Override Values Register (SriOveride) | 643   |

| 12.12.23 Control bits for the HT PHY (HtPHYCtl)                                     | 644   |

| 13. References                                                                      | . 645 |

| 14. Glossary                                                                        | . 647 |

|                                                                                     |       |

| Revision Log                                                                        | . 653 |

# List of Figures

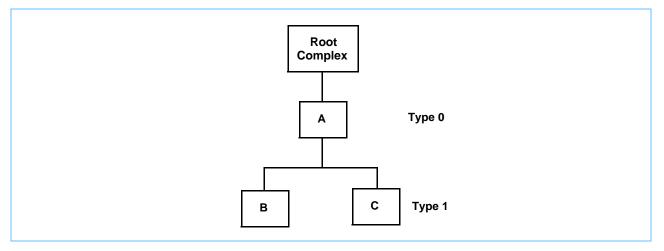

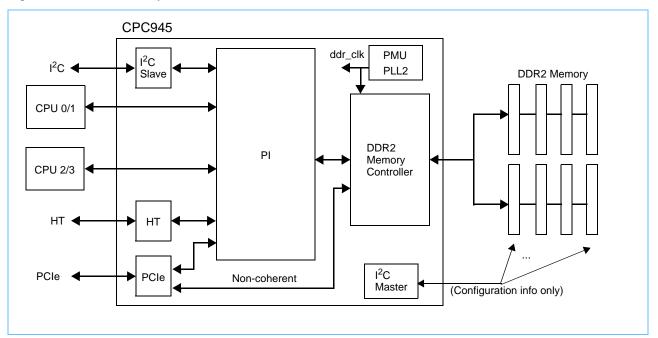

| Figure 1-1.  | CPC945 Bridge and Memory Controller Block Diagram                               | 28  |  |

|--------------|---------------------------------------------------------------------------------|-----|--|

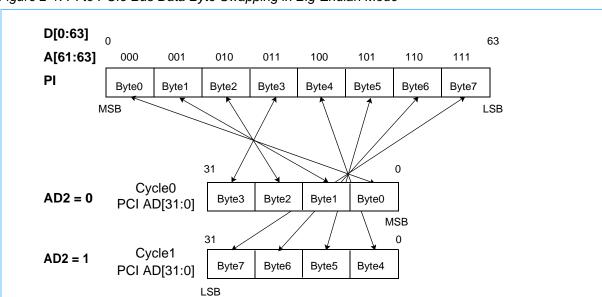

| Figure 2-1.  | PI to PCIe Bus Data Byte Swapping in Big-Endian Mode                            | 35  |  |

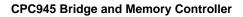

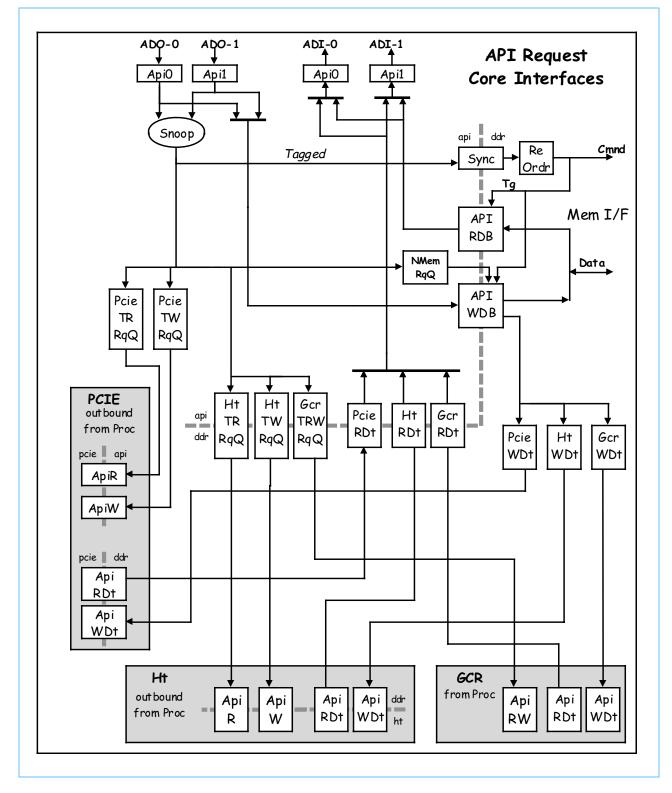

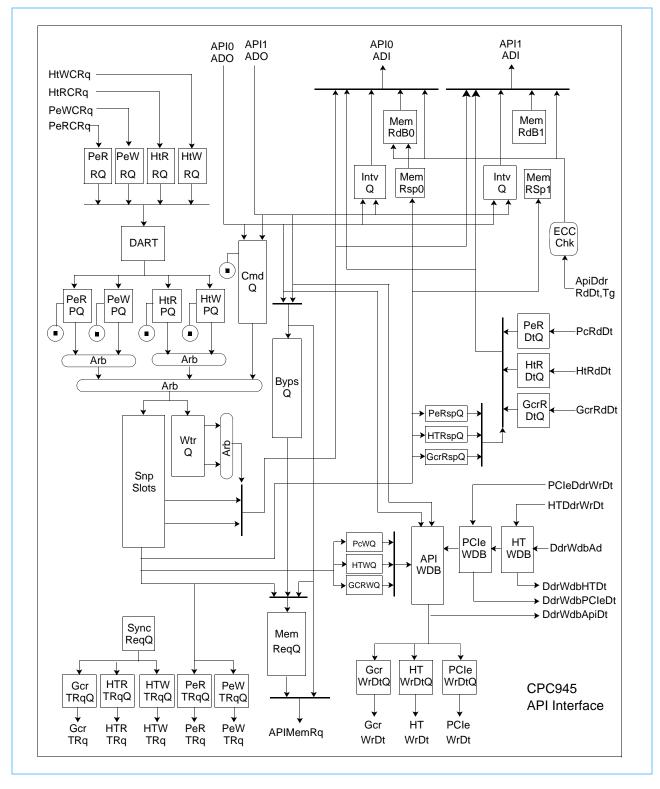

| Figure 3-1.  | CPC945 Core Interface Block Diagram                                             | 40  |  |

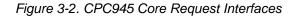

| Figure 3-2.  | CPC945 Core Request Interfaces                                                  | 41  |  |

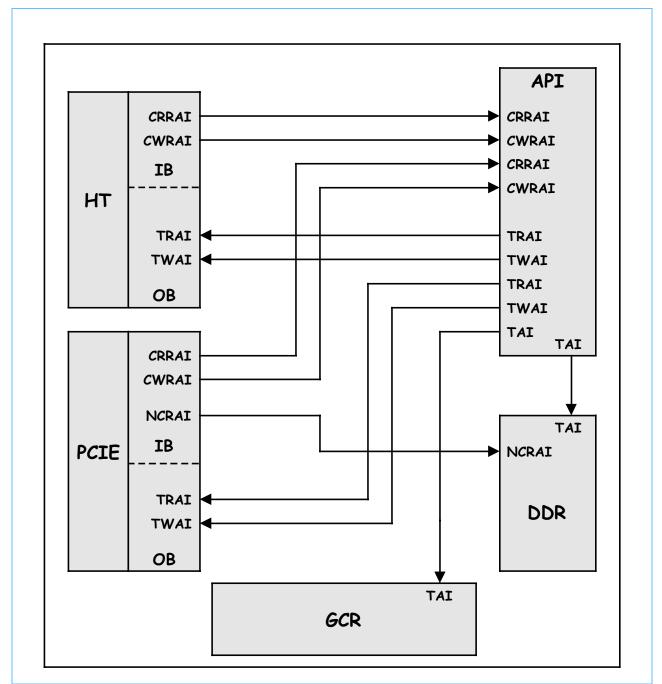

| Figure 3-3.  | CPC945 Core Data Interfaces                                                     | 43  |  |

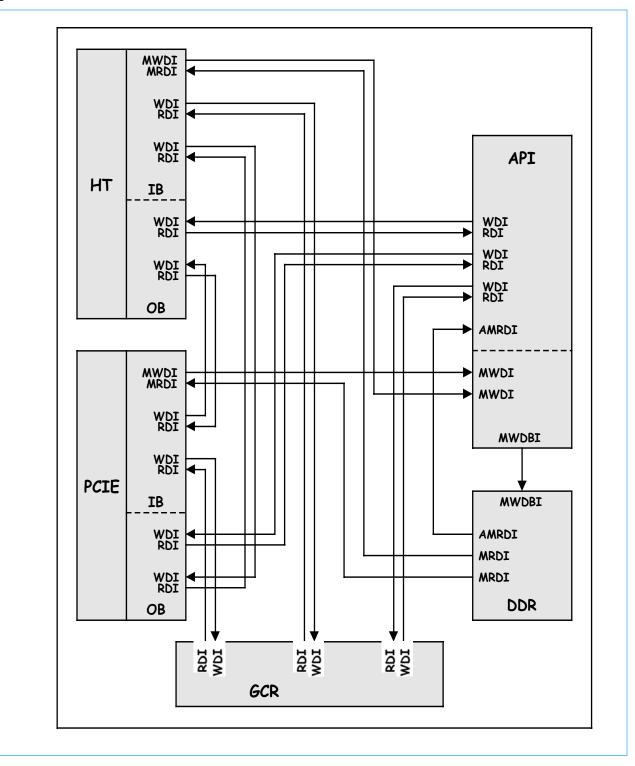

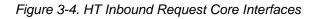

| Figure 3-4.  | HT Inbound Request Core Interfaces                                              | 46  |  |

| Figure 3-5.  | PCIe Inbound Request Core Interfaces                                            | 48  |  |

| Figure 3-6.  | PI Target Request Interfaces                                                    | 50  |  |

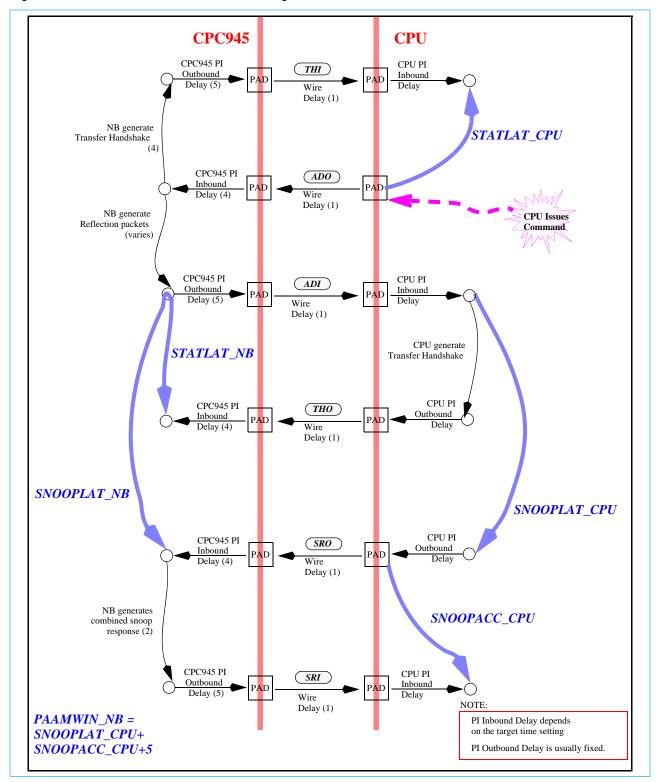

| Figure 3-7.  | Processor and CPC945 Bus Timing Parameters                                      | 52  |  |

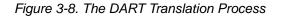

| Figure 3-8.  | The DART Translation Process                                                    | 55  |  |

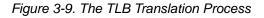

| Figure 3-9.  | The TLB Translation Process                                                     | 58  |  |

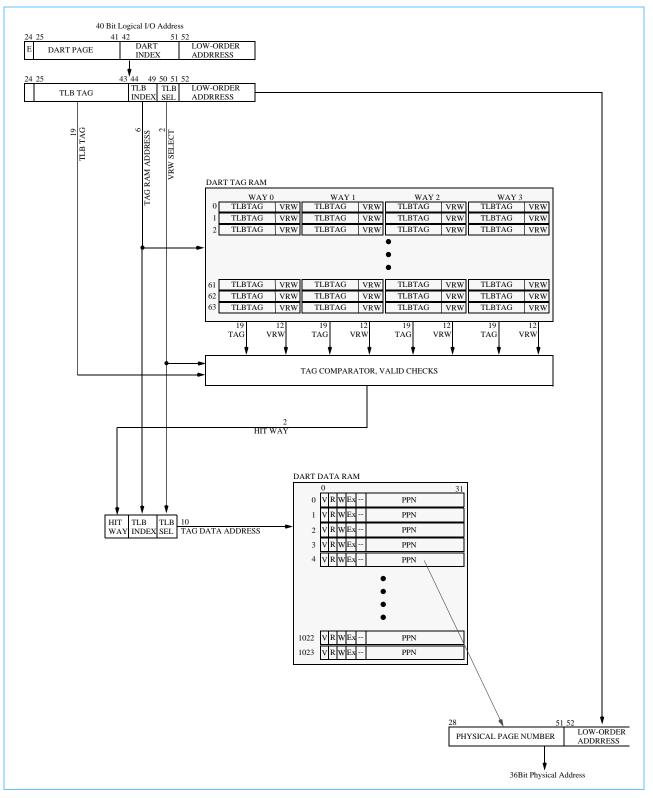

| Figure 3-10. | CPC945 Processor Interface Environment                                          | 61  |  |

| Figure 3-11. | CPC945 PI Unit                                                                  | 62  |  |

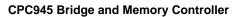

| Figure 4-1.  | Two Processors Connected to the CPC945                                          | 77  |  |

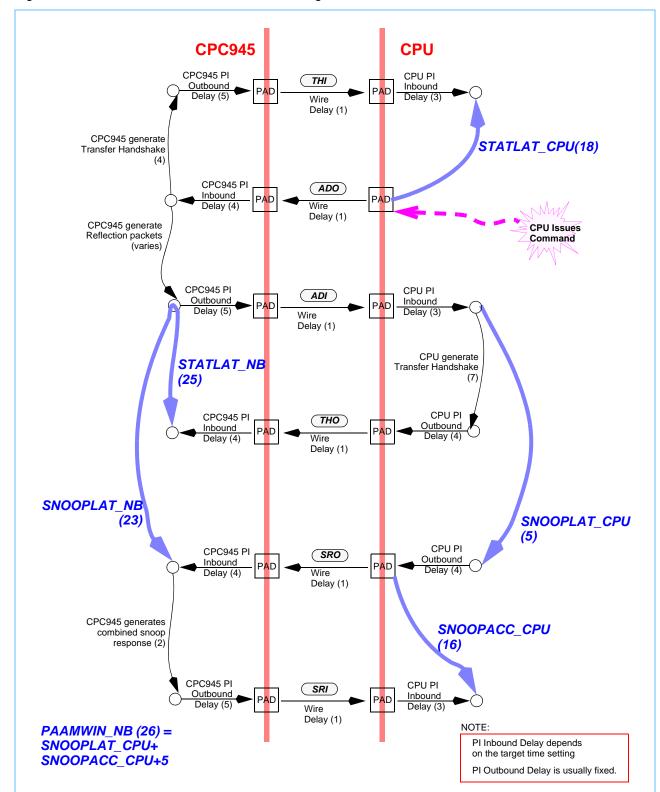

| Figure 4-2.  | Processor and CPC945 Interface Timing Parameters                                | 81  |  |

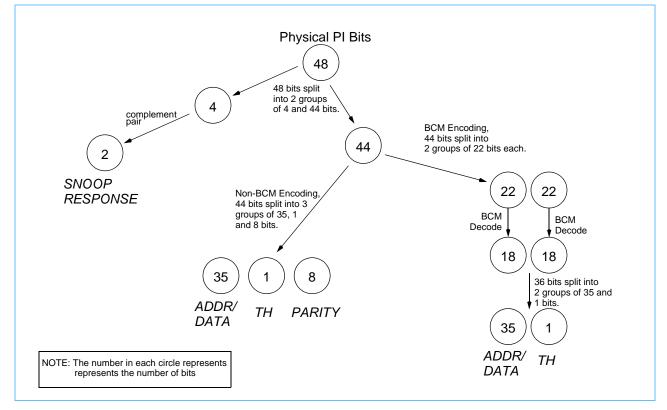

| Figure 4-3.  | Physical PI Bits to Logical PI Bits Mapping                                     | 90  |  |

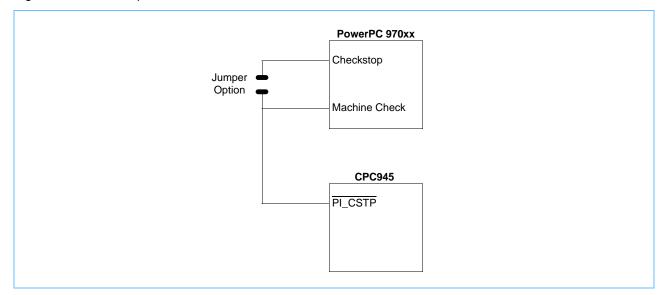

| Figure 4-4.  | Checkstop Connections                                                           | 93  |  |

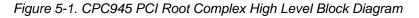

| Figure 5-1.  | CPC945 PCI Root Complex High Level Block Diagram                                | 95  |  |

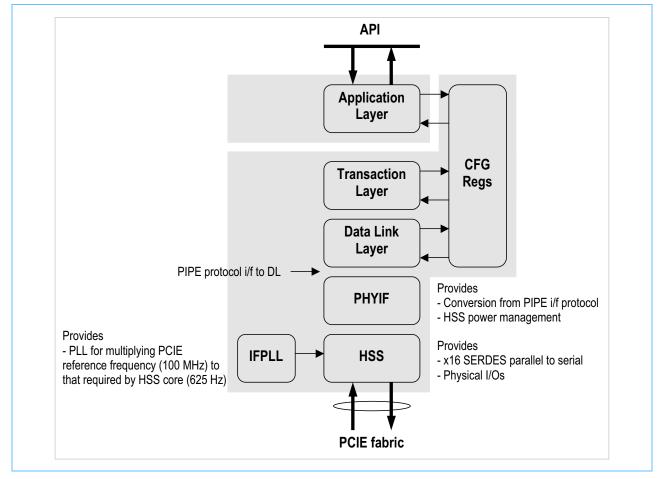

| Figure 5-2.  | TLP Header for Requests with 32 Bit Addressing (3 DWord Header)                 | 98  |  |

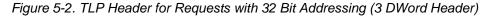

| Figure 5-3.  | TLP Header for Configuration Requests (reads and writes)                        | 98  |  |

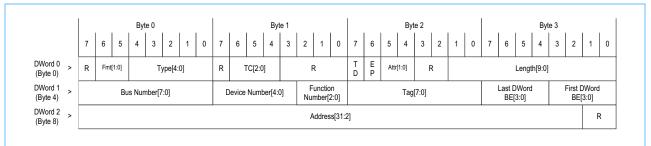

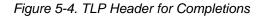

| Figure 5-4.  | TLP Header for Completions                                                      | 99  |  |

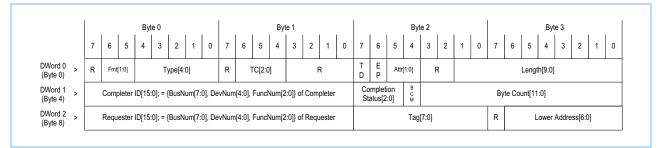

| Figure 5-5.  | TLP Header for Messages                                                         | 99  |  |

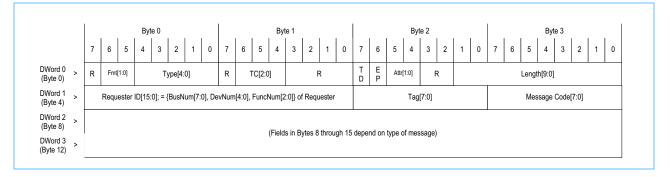

| Figure 5-6.  | PI Data Bit and Byte Ordering                                                   | 103 |  |

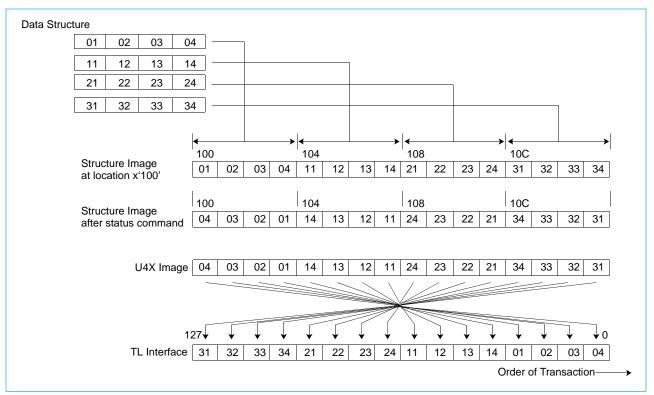

| Figure 5-7.  | System Memory to TL Interface Data Formatting Changes                           | 104 |  |

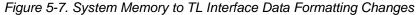

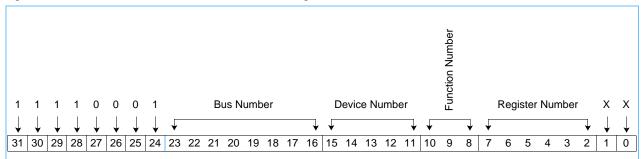

| Figure 5-8.  | Configuration Address Register Formatted For A Type 0 Configuration Transaction | 110 |  |

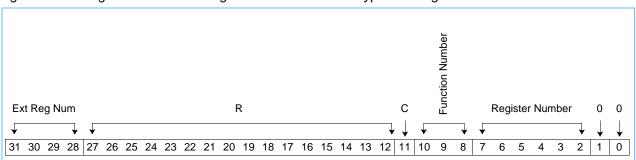

| Figure 5-9.  | Configuration Address Register Formatted For A Type 1 Configuration Transaction | 110 |  |

| Figure 5-10. | Transmission Type By Target                                                     | 111 |  |

| Figure 5-11. | Address Field For Limited Direct Configuration Transactions                     | 112 |  |

| Figure 6-1.  | Initialization Sequence                                                         | 116 |  |

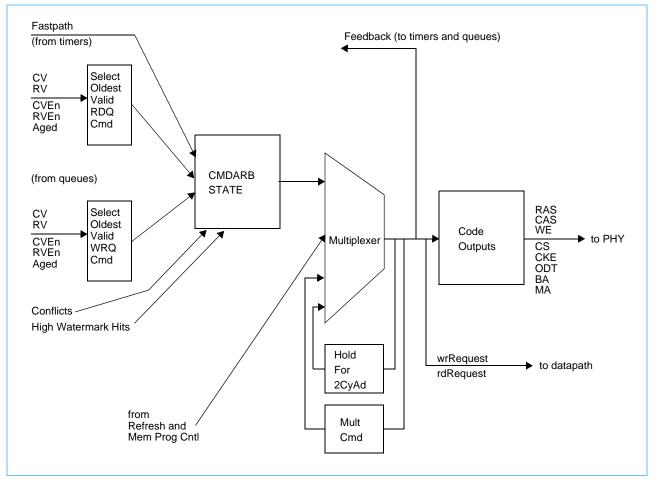

| Figure 7-1.  | DDR2 Memory Controller                                                          |     |  |

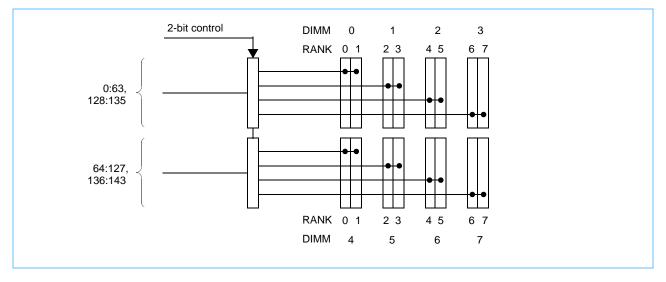

| Figure 7-2.  | External Memory Configurations                                                  | 131 |  |

| Figure 7-3.  | Memory Controller Internals                                                     | 142 |  |

| Figure 7-4.  | Chip Select and Interleave Mode Addressing                                      | 160 |  |

| Figure 7-5.  | Command Arbiter Flow                                                            | 187 |  |

| Figure 7-6.  | External Multiplexers                                                           | 213 |  |

| Figure 7-7.  | Example Timing Verniers                                                         | 217 |  |

| Figure 7-8.  | 1/2 Bit Time Averager                                                           | 218 |  |

| Figure 7-9.  | DQS Offset Delta                                                                | 219 |  |

| Figure 7-10.  | CK Timing Adjustment                                  | 223 |

|---------------|-------------------------------------------------------|-----|

| Figure 7-11.  | Control Signal Wiring Summary                         | 228 |

| Figure 7-12.  | Write Data Timing Example                             | 230 |

| Figure 7-13.  | Byte Lane Write Verniers                              | 232 |

| Figure 7-14.  | Read Data Capture FIFO                                | 233 |

| Figure 7-15.  | Read DQS                                              | 234 |

| Figure 7-16.  | Byte Lane Read Control                                | 237 |

| Figure 7-17.  | Read Reset Ld En Timing Example                       | 238 |

| Figure 7-18.  | Read UnloadPtr Timing Example                         | 239 |

| Figure 7-19.  | RdOEOffDly Timing Example                             | 240 |

| Figure 7-20.  | DQ and DQS Tri-state Timing Example                   | 241 |

| Figure 7-21.  | External multiplexer Basic Timing                     | 242 |

| Figure 7-22.  | External multiplexer Read Timing Example              | 243 |

| Figure 7-23.  | Cluster MuxEn Verniers                                | 244 |

| Figure 7-24.  | Simplified Byte lane with Calibration Bit             | 245 |

| Figure 7-25.  | Calibration Bit DQS Capture FIFO                      | 249 |

| Figure 7-26.  | Calibration Load Monitor                              | 251 |

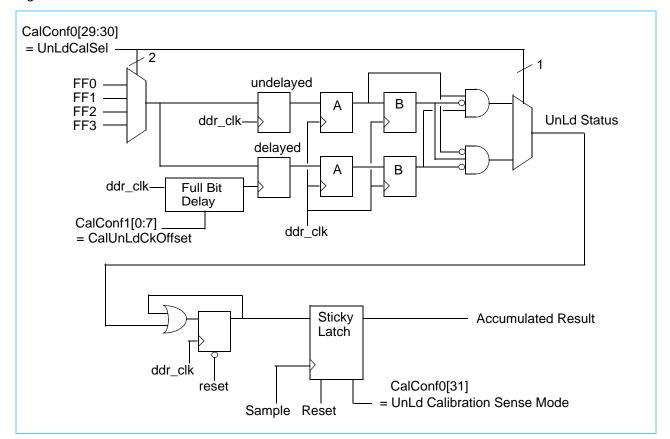

| Figure 7-27.  | Calibration Unload Monitor                            | 254 |

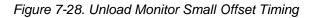

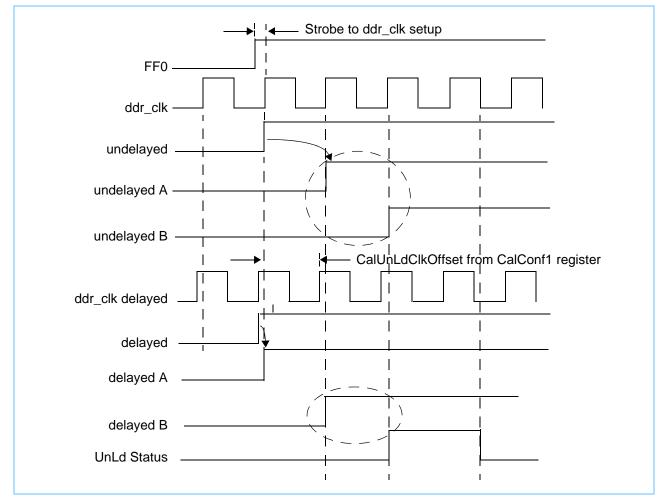

| Figure 7-28.  | Unload Monitor Small Offset Timing                    | 256 |

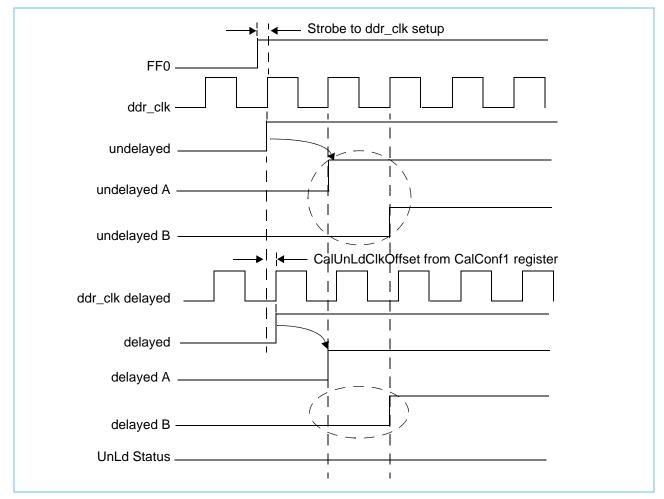

| Figure 7-29.  | Unload Monitor Large Offset Timing                    | 257 |

| Figure 7-30.  | UnLd Calibration Sense Mode                           | 259 |

| Figure 9-1.   | MPIC                                                  |     |

| Figure 10-1.  | CPC945 Power On Reset Procedure                       |     |

| Figure 11-1.  | Run to Sleep Transition                               |     |

| Figure 11-2.  | Wake Sequence                                         |     |

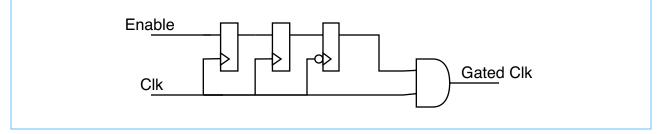

| Figure 11-3.  | Clock Stopper Logic                                   |     |

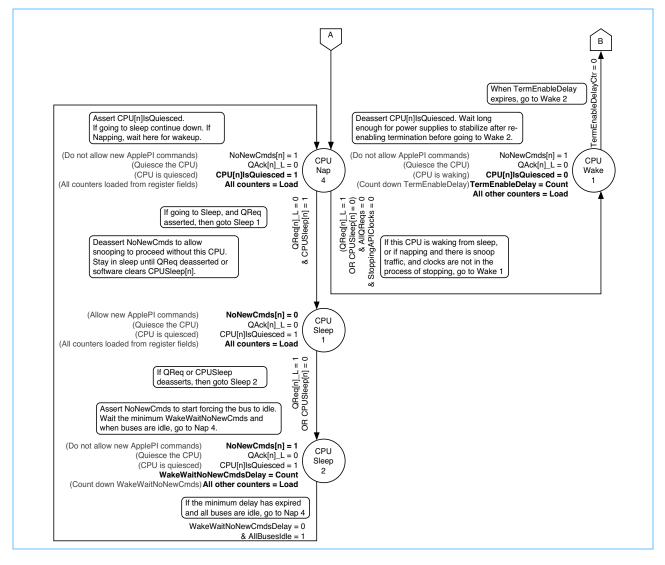

| Figure 11-4.  | CPU Power Manager (1 of 2)                            |     |

| Figure 11-5.  | CPU Power Manager (2 of 2)                            |     |

| Figure 11-6.  | PLL1 Clock Stopper                                    | 311 |

| Figure 11-7.  | PLL3                                                  | 313 |

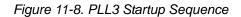

| Figure 11-8.  | PLL3 Startup Sequence                                 | 314 |

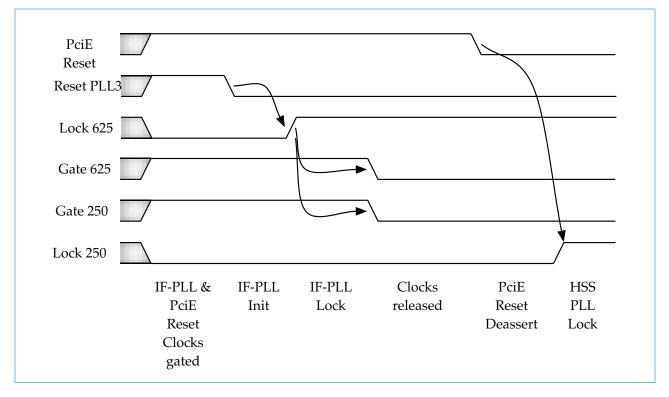

| Figure 11-9.  | HT Warm Reset                                         | 315 |

| Figure 11-10. | . PLL4                                                | 316 |

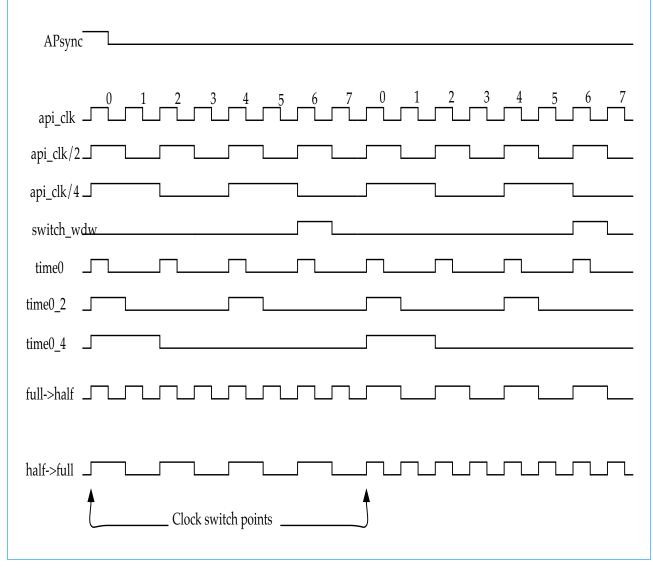

| Figure 11-11  | . Power Tuning Sequence                               | 317 |

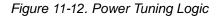

| Figure 11-12. | . Power Tuning Logic                                  | 318 |

| Figure 11-13. | . Power Tuning Timing                                 | 319 |

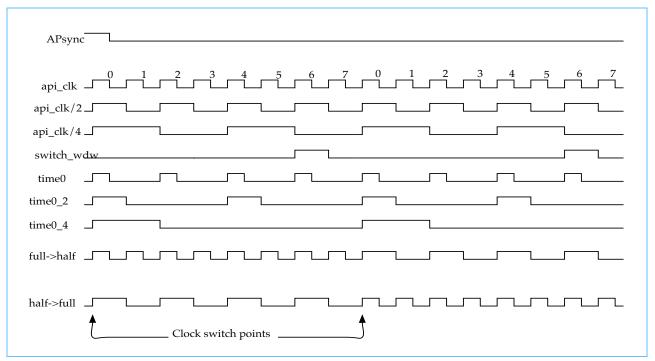

| Figure 11-14  | . Timing Diagram for Frequency Change Operation in PI |     |

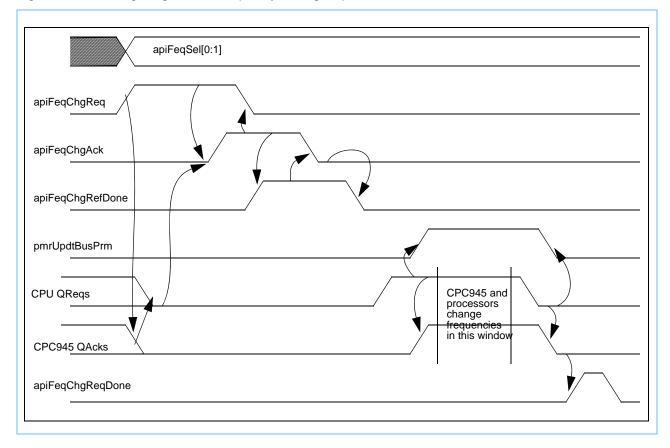

| Figure 11-15  | Block Diagram for a Frequency Change Operation in PI  | 321 |

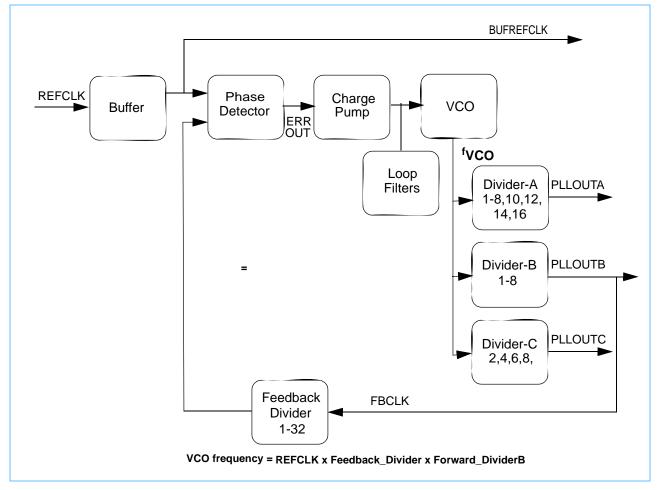

| Figure 11-16  | . PLL1/ PLL2 Internal Block Diagram                   |     |

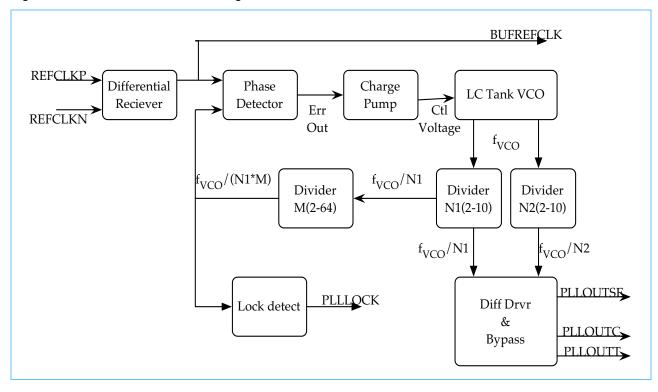

| Figure 11-17. PLL 3 Internal Block Diagram | 324 |

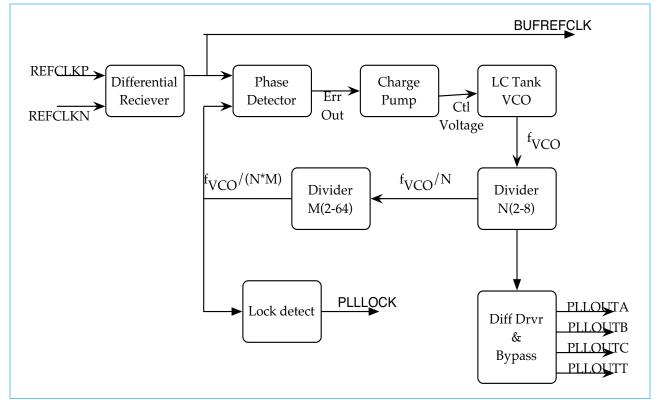

|--------------------------------------------|-----|

| Figure 11-18. PLL 4 Internal Block Diagram | 325 |

| Figure 12-1. PCIe XBus Configuration Space | 330 |

CPC945 Bridge and Memory Controller

# List of Tables

| Table 2-1.  | PI to PCIe Bus address mapping in Big-Endian Mode for Memory Space       | 35  |  |  |

|-------------|--------------------------------------------------------------------------|-----|--|--|

| Table 2-2.  | PI to PCIe Bus Address Mapping in Big-Endian Mode for I/O Space          | 35  |  |  |

| Table 3-1.  | DART Mapping Range                                                       | 53  |  |  |

| Table 3-2.  | Format of a DART Entry in Main Memory                                    | 54  |  |  |

| Table 3-3.  | LPN Address to access the DART TLB                                       |     |  |  |

| Table 3-4.  | Format of a DART Tag Entry in TLB (cache)                                | 59  |  |  |

| Table 3-5.  | Format of DART Data Entry in TLB (cache)                                 |     |  |  |

| Table 3-6.  | Response to Bus Operations from the Processor                            | 63  |  |  |

| Table 3-7.  | Operations (I/O Commands) from Other Agents                              |     |  |  |

| Table 3-8.  | Resources Required for Reflecting                                        | 73  |  |  |

| Table 4-1.  | Big-Endian Processor Interface to Little-Endian PCIe Bus Address Mapping |     |  |  |

| Table 4-2.  | CPC945 Responses to PI Transfer Types                                    | 91  |  |  |

| Table 5-1.  | TLP Header Fields                                                        |     |  |  |

| Table 5-2.  | CPC945 Advertised PCIe Credits                                           | 102 |  |  |

| Table 5-3.  | Supported PCIe Outbound Request Types                                    | 104 |  |  |

| Table 5-4.  | Ordering Rules for PCIe AL Outbound Requests                             | 105 |  |  |

| Table 5-5.  | Physical Layer Errors                                                    | 106 |  |  |

| Table 5-6.  | Data Link Layer Errors                                                   | 106 |  |  |

| Table 5-7.  | 5-7. Transaction Layer Errors                                            |     |  |  |

| Table 5-8.  | PCI Express Stack Errors Addressed by Application Layer                  | 107 |  |  |

| Table 5-9.  | Allowed Inbound TLPs Types and Destinations                              | 108 |  |  |

| Table 5-10. | Message Decode                                                           | 108 |  |  |

| Table 5-11. | Configuration Access Registers                                           | 109 |  |  |

| Table 7-1.  | Supported Memory Sizes                                                   | 132 |  |  |

| Table 7-2.  | Memory Bandwidths (Peak)                                                 | 132 |  |  |

| Table 7-3.  | SDRAM Commands (Simplified)                                              | 150 |  |  |

| Table 7-4.  | Example DDR2 SDRAM Initialization Sequence                               | 151 |  |  |

| Table 7-5.  | 64-Bit Configuration and 64-Bit Bus Settings                             | 156 |  |  |

| Table 7-6.  |                                                                          |     |  |  |

| Table 7-7.  | 7-7. DIMM Configuration Example 1 - DIMM Characteristics                 |     |  |  |

| Table 7-8.  | DIMM Configuration Example 1 - Sorted Group List                         | 165 |  |  |

| Table 7-9.  | DIMM Configuration Example 1 - Register Fields                           | 165 |  |  |

| Table 7-10. | DIMM Configuration Example 1 - Register Values                           | 165 |  |  |

| Table 7-11. | DIMM Configuration Example 2 - DIMM Characteristics                      | 166 |  |  |

| Table 7-12. | DIMM Configuration Example 2 - Sorted Group List                         | 166 |  |  |

| Table 7-13. | DIMM Configuration Example 2 - Register Fields                           | 166 |  |  |

| Table 7-14. | DIMM Configuration Example 2 - Register Values                           | 166 |  |  |

| Table 7-15. | DIMM Configuration Example 3 - DIMM Characteristics                      | 167 |  |  |

| Table 7-16. | DIMM Configuration Example 3 - Sorted Group List167                                      |

|-------------|------------------------------------------------------------------------------------------|

| Table 7-17. | DIMM Configuration Example 3 - Register Fields167                                        |

| Table 7-18. | DIMM Configuration Example 3 - Register Values167                                        |

| Table 7-19. | DIMM Configuration Example 4 - DIMM Characteristics168                                   |

| Table 7-20. | DIMM Configuration Example 4 - Sorted Group List168                                      |

| Table 7-21. | DIMM Configuration Example 4 - Register Fields168                                        |

| Table 7-22. | DIMM Configuration Example 4 - Register Values168                                        |

| Table 7-23. | Memory Mapping for Bank Interleaving at SDRAM Page Boundary (128-bit Configuration) 171  |

| Table 7-24. | Memory Mapping for Bank Interleaving at Cache Line Boundary (128-bit Configuration) 172  |

| Table 7-25. | Memory Mapping for Bank Interleaving at SDRAM Page Boundary (64-bit Configuration) .173  |

| Table 7-26. | Memory Mapping for Bank Interleaving at Cache Line Boundary (64-bit Configuration)174    |

| Table 7-27. | tRCD, tRP and tRC176                                                                     |

| Table 7-28. | tRTP, tWR and tRRD177                                                                    |

| Table 7-29. | tRTP+tRP, tWR + tRP177                                                                   |

| Table 7-30. | Example Timing Parameters178                                                             |

| Table 7-31. | RASTimer0/1 Register Values                                                              |

| Table 7-32. | CASTimer0/1 Register Values                                                              |

| Table 7-33. | Hamming Matrix                                                                           |

| Table 7-34. | Hamming Matrix Continued193                                                              |

| Table 7-35. | Check Bit Summary                                                                        |

| Table 7-36. | MemBusConfig Width Settings212                                                           |

| Table 7-37. | DQS Bit Numbering                                                                        |

| Table 8-1.  | Twenty-two Bit I <sup>2</sup> C System Command Request Definition                        |

| Table 8-2.  | I <sup>2</sup> C Write Transaction (Includes Number of Bits Transmitted for Each Action) |

| Table 8-3.  | Bit Sequence on the I <sup>2</sup> C Bus for a Control Register Write Transaction        |

| Table 8-4.  | Bit Sequence on the I <sup>2</sup> C Bus for a Control Register Read Transaction         |

| Table 8-5.  | Byte Sequence on the I <sup>2</sup> C Bus for Writing the SysCmdCntl1 Register           |

| Table 8-6.  | Byte Sequence on the I <sup>2</sup> C Bus for Writing the SysCmdCntl0 Register           |

| Table 9-1.  | Interrupt Input Summary                                                                  |

| Table 9-2.  | Register Summary                                                                         |

| Table 10-1. | CPC945 System Support Signal Pins                                                        |

| Table 11-1. | CPC945 and Processor Power Management State Definitions                                  |

| Table 11-2. | PLL1 and PLL2 Tune Bit Settings, 1 of 2                                                  |

| Table 11-3. | PLL1 and PLL2 Tune Bit Settings, 2 of 2                                                  |

| Table 12-1. | 36-bit Extended Memory Map                                                               |

| Table 12-2. | Control Register Memory Map                                                              |

| Table 12-3. | CPC945 Control Register Addresses                                                        |

| Table 12-4. | PMR Address Space                                                                        |

| Table 12-5. | PLL1 Clock Settings                                                                      |