# COS/MOS 4-Word by 8-Bit Random-Access NDRO Memory

Binary Addressing

Direct Word-Line Addressing

CD4036AD, CD4036AK CD4039AD, CD4039AK

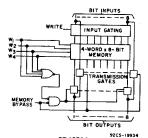

RCA type CD4036A is a single monolithic integrated circuit containing a 4-word x 8-bit Random Access NDRO Memory. Inputs include 8 INPUT-BIT lines, CHIP INHIBIT, WRITE, READ INHIBIT, MEMORY BYPASS, and 2 ADDRESS inputs. 8 OUTPUT-BIT lines are provided.

All input and output lines utilize standard COS/MOS inverter configurations and hence can be directly interfaced with COS/MOS logic devices.

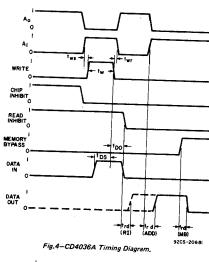

CHIP INHIBIT allows memory word expansion by WIRE-ORing of multiple CD4036A packages at either the 8-bit input and/or output lines (See Fig.15). With CHIP INHIBIT "high", both READ and WRITE operations are inhibited on the CD4036A. With CHIP INHIBIT "low", information can be written into and/or read continuously from one of the four words selected by the binary code on the two address lines. With CHIP INHIBIT "low", a "high" WRITE signal and a "low" READ INHIBIT signal activate WRITE and READ operations, respectively, at the addressed word location (See Fig.4).

The MEMORY BYPASS signal, when "high", allows shunting of information from the 8 INPUT-BIT lines directly to the 8

OUTPUT-BIT lines without disturbing the state of the 4 words. During the bypass operation input information may also be written into a selected word location, provided the CHIP INHIBIT is "low" and the WRITE is "high". The READ operation is deactivated during the BYPASS operation because information is fed directly from the 8 INPUT-BIT lines to the 8 OUTPUT-BIT lines.

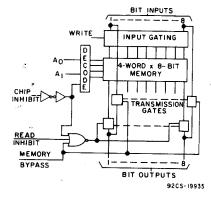

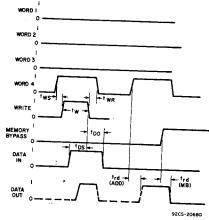

RCA type CD4039A is identical to the CD4036A with the exception that individual address-line inputs have been provided for each memory word in place of the binary ADDRESS, CHIP INHIBIT, and READ INHIBIT inputs. When Wire-Oring multiple CD4039A packages for memory word expansion, an individual CD4039A is selected by addressing one of its word locations. The READ operation is activated whenever a word location is addressed (via a "high" signal—see Fig.5).

These devices will be supplied in two different 24-lead ceramic packages; the CD4036AK and CD4039AK in the flat-pack, and the CD4036AD and CD4039AD in the dual-in-line package.

### MAXIMUM RATINGS, Absolute-Maximum Values:

| Storage Temperature Range            | -65 to +150                     | oC. |

|--------------------------------------|---------------------------------|-----|

| Operating Temperature Range          | -55 to +125                     | oC  |

| DC Supply Voltage Range              |                                 | •   |

| (V <sub>DD</sub> - V <sub>SS</sub> ) | -0.5 to +15                     | V   |

| Device Dissipation (Per Pkg.)        | 200                             | mW  |

| All Inputs                           | $v_{SS} \leq v_I {\leq} v_{DD}$ |     |

| Recommended DC Supply Voltage        |         |     |

|--------------------------------------|---------|-----|

| (V <sub>DD</sub> - V <sub>SS</sub> ) | 3 to 15 | V   |

| Lead Temperature (During soldering)  |         |     |

| At distance 1/16 ±1/32 inch          |         |     |

| (1.59 ±0.79 mm) from case            |         |     |

| for 10 seconds max                   | 265     | oC. |

|                                      |         |     |

|                                         | SYMBOL          |              | LIMITS             |          |                                          |                  |      |        |       |       |       | CHARAC-<br>TERISTIC<br>CURVES |       |                    |          |   |

|-----------------------------------------|-----------------|--------------|--------------------|----------|------------------------------------------|------------------|------|--------|-------|-------|-------|-------------------------------|-------|--------------------|----------|---|

| CHARACTERISTIC                          |                 | . co         | TEST<br>CONDITIONS |          | CD4036AD, CD4036AK<br>CD4039AD, CD4039AK |                  |      |        |       |       |       |                               | UNITS |                    |          |   |

|                                         |                 |              | Vo                 | $V_{DD}$ | -                                        | -55°C 25°C       |      |        | 125°C |       |       |                               | 1     | & TEST<br>CIRCUITS |          |   |

|                                         | ļ               | ــــ         | Volts              | Volts    | Min.                                     | Тур.             | Max. | Min.   | Тур.  | Max.  | Min.  | Тур.                          | Max.  | 1                  | Fig. No. |   |

| Quiescent Device                        | ار              |              |                    | 5        |                                          | <u> </u>         | 5    |        | 0,5   | 5     | _     |                               | 300   | μА                 | 44.40    |   |

|                                         |                 | -            | <u> </u>           | 10       |                                          |                  | 10   |        | 1     | 10    | -     | _                             | 600   | μΛ                 | 11, 12   |   |

| Quiescent Device<br>Dissipation/Package | PD              |              | <u> </u>           | 5        | -                                        | <u> </u>         | 25   |        | 2,5   | 25    |       | _                             | 1500  | μW                 |          |   |

| Output Voltage:                         |                 |              |                    | 10       |                                          | <del>  -</del> _ | 100  |        | 10    | 100   | _     |                               | 6000  | μ.,                |          |   |

| Low-Level                               | VOL             |              | <u> </u>           | 5        |                                          | <u> </u>         | 0.01 | -      | 0     | 0.01  |       |                               | 0.05  | l v l              |          |   |

|                                         | ·               | <del></del>  |                    | 10       |                                          | <del> -</del>    | 0.01 |        | 0     | 0.01  |       |                               | 0.05  |                    |          |   |

| High-Level                              | ۷он             |              |                    | 5        | 4.99                                     | ~                |      | 4.99   | 5     |       | 4.95  |                               | _     | v .                | _        |   |

|                                         |                 | -            |                    | 10       | 9.99                                     |                  | -    | 9.99   | 10    |       | 9.95  |                               |       |                    |          |   |

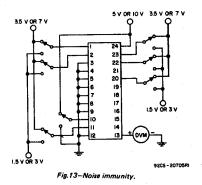

| Noise Immunity                          | v <sub>NL</sub> |              | 0.8                | 5        | 1.5                                      | -                | -    | 1.5    | 2.25  | -     | 1.4   |                               |       |                    |          |   |

| (All inputs except<br>bit inputs when   |                 |              | 1,0                | 10       | 3                                        | -                | _    | 3      | 4.5   | _     | 2.9   | -                             | -     |                    |          |   |

| in memory by-                           |                 |              | 4.2                | 5        | 1.4                                      |                  | -    | 1.5    | 2.25  | _     | 1.5   | _                             |       | V                  | 13       |   |

| pass mode.)                             |                 |              | 9.0                | 10       | 2.9                                      | -                | -    | 3      | 4.5   | -     | 3     | -                             | -     |                    |          |   |

| Output Drive Current:<br>N-Channel      |                 | Nor-         | 0.5                | 5        | 0,12                                     | -                | -    | 0.10   | 0.20  | _     | 0.07  | _                             | _     |                    |          |   |

| 14-Channel                              |                 | mal<br>Read  | 0.5                | 10       | 0.30                                     | - :              | _    | 0.25   | 0.50  | -     | 0.17  | _                             |       | mA                 | 6        |   |

| P-Channel                               | IDP             | Modes        | 4.5                | 5        | -0.12                                    | -                |      | -0.10  | -0.20 | _     | -0,07 | _                             |       | mA                 |          |   |

|                                         |                 |              | _                  | 9.5      | 10                                       | -0.30            |      | _      | -0.25 | -0.50 |       | 0.17                          | _     | _                  | mA       | 7 |

| Output Drive Current:<br>A-Channel      | 0               | InN Mem-     | 0.5                | 5        | 0.04                                     | -                | -    | 0.03   | 0.06  | _     | 0.02  | -                             | _     | mA                 | -        |   |

|                                         |                 | ory<br>By-   | 0.5                | 10       | 0.09                                     | -                | -    | 0.075  | 0.15  |       | 0.05  | _                             |       |                    |          |   |

| P-Channel                               |                 | pass<br>Mode | 4.5                | 5        | -0.04                                    | -                | -    | 0.03   | 0.06  | _     | -0.02 | _                             | _     | mA                 |          |   |

|                                         |                 | +            | 9.5                | 10       | -0.09                                    | _                | _    | -0.075 | -0.15 |       | 0.05  | _                             | _     |                    | -        |   |

| Input Current                           | łį              |              | - [                | -        | _                                        |                  | _    | -      | 10    | _     | _     | _                             | _     | ρA                 |          |   |

<sup>&</sup>lt;sup>+</sup>Bit inputs driven from low-impedance driver.

#### Special Features:

- COS/MOS logic compatibility at all input and output terminals

- Memory bit expansion

- Memory word expansion via Wire-OR capability at the 8 INPUT-BIT and 8 OUTPUT-BIT lines

- Memory bypass capability for all bits

- Buffering on all outputs

- CD4036A- on-chip binary address decoding, separate READ INHIBIT and WRITE controls

- Access Time-200 ns(Typ) at V<sub>DD</sub>=10 V

- CD4039A-Direct word-line addressing

#### Applications:

Digital equipment where low power dissipation and/or high noise immunity are primary design requirements.

- Channel Preset Memory in digital frequency-synthesizer circuits

- General-purpose and scratch-pad memory in COS/MOS and other low-power systems.

CD4039A

Fig.1 - CD4036A - Logic block diagram.

| Write<br>(Pin 2) | Read<br>Inhibit<br>(Pin 21) | Memory<br>Bypass<br>(Pin 11) | Chip<br>Inhibit<br>(Pin 22) | Operating Mode                                                                               |  |  |  |  |  |  |

|------------------|-----------------------------|------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| X                | ×                           | Ľ                            | н                           | Chip Inhibited (Outputs float)                                                               |  |  |  |  |  |  |

| ×                | ×                           | н                            | Н                           | Input/Output Shunted to output;<br>No Reading from Memory;                                   |  |  |  |  |  |  |

| Ľ                | ×                           | H                            | L                           | Information in Memory<br>Undisturbed                                                         |  |  |  |  |  |  |

| н                | ×                           | Ξ                            | L                           | Input/Output Shunted to output;<br>No Reading from Memory;<br>Write Data into Addressed Word |  |  |  |  |  |  |

| L                | Ļ                           | L                            | L                           | Read Data from Addressed Word<br>Write Deactivated                                           |  |  |  |  |  |  |

| L                | н                           | L,                           | L                           | Read/Write Deactivated (Outputs float)                                                       |  |  |  |  |  |  |

| н                | L                           | i,                           | L                           | Read from Memory while .<br>Writing Data into<br>Addressed Word                              |  |  |  |  |  |  |

| н                | Н                           | L                            | L                           | Write Data into Addressed Word<br>Read Deactivated (outputs float)                           |  |  |  |  |  |  |

Fig.2 - Operating-mode truth table.

| A1<br>Pin 1 | A0<br>Pin 23 | Addressed<br>Word |

|-------------|--------------|-------------------|

| ٦           | ٦            | Word 1            |

| L           | н            | Word 2            |

| н           | L            | Word 3            |

| н.          | н            | Word 4            |

L = Low-Level Voltage,

H = High-Level Voltage

Fig.3 - Address truth table.

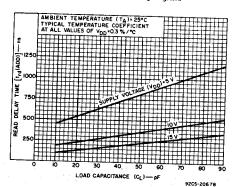

# DYNAMIC ELECTRICAL CHARACTERISTICS at $T_{\mbox{\scriptsize A}}$ = 25°C and $C_{\mbox{\scriptsize L}}$ = 15 pF Typical Temperature Coefficient for all values of VDD = 0.3%/°C

|                                    | T               |                                                                               |                          |                  |                    |                                                  |              |                     |

|------------------------------------|-----------------|-------------------------------------------------------------------------------|--------------------------|------------------|--------------------|--------------------------------------------------|--------------|---------------------|

| CHARACTERISTICS                    | SYMBOLS         | TEST<br>CONDITIONS                                                            |                          | CD40<br>CD40     | 36AD, 0<br>39AD, 0 | D4036AK<br>D4039AK                               | UNITS        | CHARAC-<br>TERISTIC |

| Read Delay Time:                   |                 |                                                                               | V <sub>D</sub> E<br>Volt |                  | Тур.               | Max.                                             | ONTS         | & TEST<br>CIRCUITS  |

| (Access time)<br>Read Inhibit (RI) |                 | OUTPUT TIED                                                                   | <u>5</u>                 | <del>  -</del> - | 375<br>150         | 750<br>300                                       | ns           | 4,5                 |

| Chip Inhibit (CI)                  | ]               | THROUGH 100 kΩ TO VSS FOR DATA OUTPUT "HIGH" AND TO VDD FOR DATA OUTPUT "LOW" | 5                        | +                | 500                | <del>                                     </del> | Note 4       |                     |

| Memory Bypass                      | <sup>t</sup> rd |                                                                               | 10                       | ΙΞ               | 200                | 1000<br>400                                      | ns<br>Note 4 | 4,5                 |

| (MB)                               |                 |                                                                               | 10                       | =                | 375<br>150         | 750<br>300                                       | ns           | 4.5                 |

| Address <sup>1</sup> (ADD)         |                 |                                                                               | 10                       | =                | 500<br>200         | 1000                                             | ns           | 4,5,8               |

| Write Set-up Time2                 | tws             |                                                                               | 5                        | 250              | 125                | 400                                              |              |                     |

| Write Removal Time3                | tWR             |                                                                               | 10<br>5                  | 100              | <u>50</u>          | <u> </u>                                         | ns           | 4,5                 |

| Write Pulse Duration               |                 |                                                                               | 10<br>5                  | 0<br>150         | 0                  |                                                  | ns           | 4,5                 |

|                                    | - tw            |                                                                               | 10                       | 60               | 75<br>30           |                                                  | ns           | 4,5                 |

| Data Set-up Time5                  | <sup>t</sup> DS |                                                                               | 5<br>10                  | ╧┼               | 0                  | 0*                                               | ns           | 4,5                 |

| Data Overlap Time6                 | tDO             |                                                                               | 5<br>10                  | 100 <sup>●</sup> | 50                 | ===                                              | ns           |                     |

| Output Transition Time             | THL,<br>TLH     |                                                                               | 5                        | -                | 20<br>200          | 400                                              |              | 4,5                 |

| Input Capacitance                  | CI              | Any Input                                                                     | 10                       |                  | 100                | 200                                              | ns           | 9                   |

|                                    |                 |                                                                               |                          |                  |                    |                                                  | pF           | - 1                 |

- For CD4036A only, remove 100-k $\Omega$  test condition and write all 1's in word one, and all 0's in word two, or vice-versa. Delay from change of ADDRESS or CHIP-INHIBIT signals to application of WRITE pulse.

- Delay from removal of WRITE pulse to change of ADDRESS or CHIP-INHIBIT signals.

- Values for CD4036AD & 4036AK only.

- The time that DATA signal must be present before the WRITE pulse removal.

- Max, indicates satisfactory operation if  $t_{\mbox{DS}}$  equals or exceeds this value.

- The time that DATA signal must remain present after the WHITE pulse removal.

- Min. indicates satisfactory operation if tDO equals or exceeds this value.

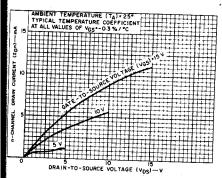

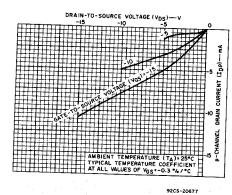

92CS-20676 Fig.6—Typical n-channel drain characteristics.

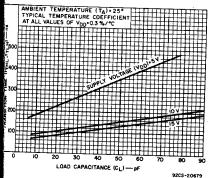

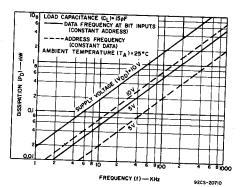

Fig.9-Typical transition time vs. CL.

Fig.7-Typical p-channel drain characteristics.

Fig. 10-Typical power dissipation vs. frequency

Fig.5-CD4039A Timing Diagram.

Fig.8-Typical read delay time vs. CL.

#### TEST CIRCUITS

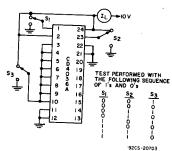

Fig.11-Quiescent current (CD4036A)

### TEST CIRCUITS (Cont'd)

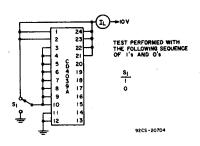

Fig.12-Quiescent current (CD4039A).

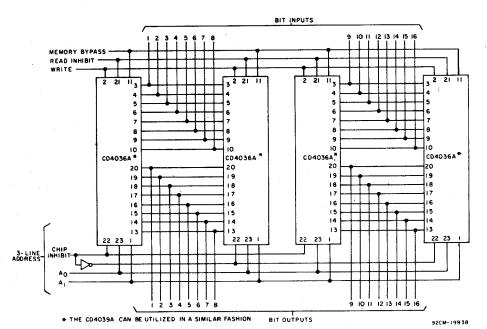

+ The CD4036A CAN BE UTILIZED IN A SIMILAR FASHION.

SEE APP, NOTE ICAN-8498 - "DESIGN OF FIXED AND PROGRAMMABLE COUNTERS USING THE RCA CD4018A COS/MOS PRESETTABLE DIVIDE-BY-"N' COUNTER" AND ICAN-8716, "LOW POWER DIGITAL FREQUENCY SYNTHESIZERS UTILIZING COSMOS ICS".

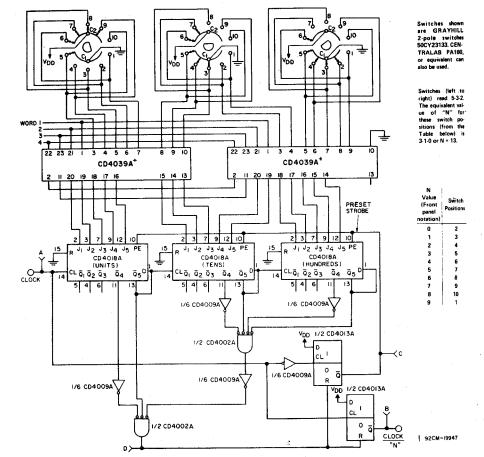

Fig.14—Three-decade programmable - N counter with 4-channel preset memory settings for frequency synthesizers.

The divide-by-N counter system shown in Fig.14 is programmable from 2 to 999. Four counter-preset words, selected by means of the rotary switches, can be stored in the CD4039A devices and can be read into each CD4018A by

simply addressing the proper word. Note that the CD4029A (see Bulletin File No. 503) Presettable Up/Down Counter with BCD decade counting can also be used to perform the basic counting function.

a) RE

CHIP

ADDRE

DATA C

DATA (

CHIP SELEC

ADDRES

READ/W

Fig.15—General-purpose memory storage — 8 words x 16 bits (RAM or ROM).