# Extending the Boundary Limits of High Voltage IGBTs and Diodes to above 8kV

M. Rahimo, A. Kopta, S. Eicher, N. Kaminski, F. Bauer, U. Schlapbach, S. Linder

ISPSD, June 2002, Santa Fe, USA

Copyright © [2002] IEEE. Reprinted from the International Symposium on Power Semiconductor Devices and ICs.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of ABB Switzerland Ltd, Semiconductors's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to <u>pubs-permissions@ieee.org</u>.

# Extending the Boundary Limits of High Voltage IGBTs and Diodes to above 8kV

M. Rahimo<sup>1</sup>, A. Kopta<sup>1</sup>, S. Eicher<sup>1</sup>, N. Kaminski<sup>1</sup>, F. Bauer<sup>2</sup>, U. Schlapbach<sup>1</sup>, S. Linder<sup>1</sup>

<sup>1</sup>ABB Switzerland Ltd Semiconductors, Fabrikstrasse 3, CH - 5600 Lenzburg, Switzerland Phone: +41 58 586 1201; Fax: +41 58 586 1309; email: <u>munaf.rahimo@ch.abb.com</u> <sup>2</sup>ABB Corporate Research Ltd., CH - 5405 Baden-Dattwil, Switzerland

**Abstract** - In this paper, we demonstrate for the first time, a planar high voltage IGBT and freewheeling diode chip set with a blocking capability exceeding 8000V. The main aim is to show that a high performance IGBT can be achieved at this voltage level by implementing the "Soft-Punch-Through" (SPT) concept. Details of the IGBT and diode design and performance are presented. This includes, experimental results for the static and dynamic characteristics under normal and SOA conditions, detailed trade-off curves for a number of design parameters, and cosmic ray induced failure results for the IGBT and diode.

## Introduction

Today, MOS-Bipolar Transistors such as the IGBT present interesting characteristics combining both MOS and bipolar structures with very desirable features for power system designers - mainly the high input impedance allowing comparatively small gate drivers, the short circuit withstand capability and robust turn-off performance. Therefore, IGBTs are continuously becoming very attractive alongside the pace of the advancement of semiconductor technologies for power applications. In addition, the progress achieved in high power silicon diodes lends a helping and reassuring hand on that way.

In recent years, high voltage IGBTs and diodes have been developed with blocking capabilities exceeding 4.5kV [1][2]. These devices were mainly targeted for use in traction systems, industrial applications, and HVDC converters. Also, new emerging high voltage markets such as pulse power applications are looking more likely to exploit the benefits of high voltage IGBTs. Therefore, the development trend continues towards even higher blocking capabilities in order to reduce the number of series connected devices for achieving simpler system designs with better performance. Previously, a high voltage IGBT and diode chip set rated 5.5kV was successfully demonstrated for 2.8kV DC link applications [3]. Also, a 6.5kV IGBT chip was presented featuring good conduction and switching performance, while capable of blocking voltages above 7kV [4]. In addition, a 6.5kV IGBT module was introduced recently [5] with an IGBT chip featuring field stop technology.

In this paper, we continue to follow the development trend by demonstrating the first ever HV-planar IGBT and diode chip set with excellent electrical properties and the capability of blocking voltages above 8kV. We also, intend to show that a HV-IGBT with excellent electrical characteristics can be achieved using standard planar technology combined with the "Soft-Punch-Through" (SPT) concept [6].

# IGBT and Diode design and structure

The blocking requirements of high voltage devices have usually determined the silicon wafer material specifications, i.e. the thickness and resistivity. For a given blocking voltage, the designer had a limited freedom in the choice of these two parameters. Therefore, for the same blocking voltage class, two design options were made available, termed as punchthrough (PT) and non-punch-through (NPT) devices. In order to reduce the overall losses of high voltage devices, a punchthrough design becomes more desirable with a reduced base region thickness compared to an NPT structure. However, with the need for higher resistivity starting material to achieve higher blocking voltages, combined with low cosmic ray failure rates [7], a PT design becomes less applicable due to hard punch through during device turn-off. This has led to the development of a new design concept termed "Soft Punch Through".

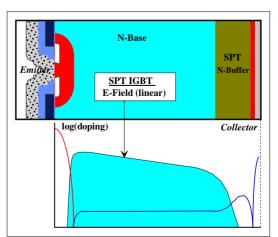

The SPT concept is based on using a low doped n-buffer profile at the anode side of the IGBT as shown in figure (1). Hence, despite the much thinner base region, the dynamic electrical properties of the SPT-IGBT are almost comparable with those of a thicker NPT-IGBT.

Fig. 1: SPT IGBT doping profile and electric field distribution

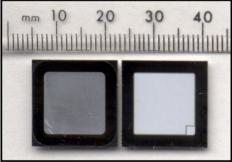

The Soft-Punch-Through feature is especially applied with respect to the softness of the current curves during switching transients, hence, the term "Soft" in SPT originates from this fact. Other major benefits of the SPT concept resulting from a substantially thinner wafer thickness is the reduction of both on-state voltage and turn-off losses. A 17.5mm x 17.5mm IGBT and diode chip set were manufactured. The IGBT design was based on the SPT concept providing an optimized total device thickness of less than 700 $\mu$ m, which is remarkable for the intended chip voltage class. The resistivity of the starting material was chosen, taking into account minimising the cosmic ray induced failure rate. Initial measurments for both the IGBT and diode were obtained showing that a target failure rate of 2 FIT/cm<sup>2</sup> at 4200V is met.

For the HV-IGBT, two buffer designs which differ in their depth and surface concentration values were evaluated. Design (A) employs an SPT buffer region having a deep and low surface concentration doping profile. Design (B) features a shallower buffer region with higher surface concentration, approaching that of a PT design. In addition, different anode concepts and lifetime control methods were also investigated. The IGBT emitter (cathode) design is based on a standard planar technology with small cell features for providing strong plasma enhancement at the emitter side. The emitter layout features a proprietary Mini-Stripe design which combines the advantages of both cell and stripe designs in terms of providing low on-state losses, high avalanche ruggedness and short circuit controllability.

The new HV-diode silicon was based on the same thin silicon specification used in the IGBT chip to achieve a low forward voltage drop. Also, an adjusted buffer region was implemented to provide soft recovery performance. A strong P-anode was employed in order to achieve a high dynamic avalanche capability. Very low switching losses accompanied with soft recovery characteristics were achieved using a combination of local and homogenous lifetime control methods. A top view of the new IGBT and diode chip set is shown in figure (2).

Fig. 2: New (>8kV) IGBT and Diode Chip Set

By implementing reliable and effective junction termination techniques with SIPOS passivation, the new IGBT and diode have stable breakdown voltage characteristics. The diode termination is also designed to eliminate any possible drawbacks in terms of device ruggedness due to high fields and current crowding at the anode periphery during reverse recovery. The termination designs were also optimized to provide less termination area in order to utilize more active region for conduction.

#### **Static Performance**

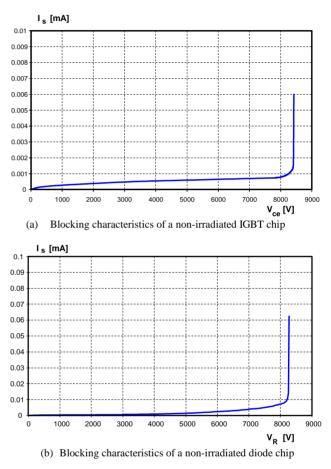

Figure (3) shows the IGBT (a) and Diode (b) reverse blocking characteristics at room temperature. The IGBT and diode show breakdown voltages of 8400V and 8200V respectively at room temperature. The chips were also tested at higher temperatures  $125^{\circ}C$  with leakage currents below 5mA at 7500V.

Fig. 3: Blocking characteristics of non-irradiated IGBT chip (a) and Diode chip (b) at room temperature.

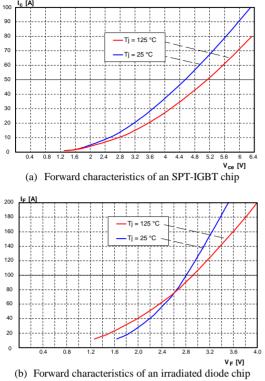

Figure (4) shows the IGBT (a) and Diode forward characteristics at room temperature and 125°C. The curves plotted are for the SPT-IGBT and irradiated diode chips. Figure (4.a) shows the forward characteristics of the SPT-IGBT. Due to the large reduction in the base region thickness and the optimized cell design, the new SPT-IGBT achieves low conduction losses with a typical on-state voltage of 4.5V at 25°C and 5.1V at 125°C at a nominal current of 50A (35A/cm<sup>2</sup>). It is also clear that the curves exhibit a positive temperature coefficient even at very low current levels. The irradiated diode forward characteristics are shown in figure (4.b).

The diode also exhibits a positive temperature coefficient above 75A with a typical forward voltage of 2.8V at  $25^{\circ}C$  and 2.9V at  $125^{\circ}C$  at a nominal current of  $100A (70A/cm^2)$ .

A positive temperature coefficient during on-state for both the IGBT and diode will ensure excellent current sharing of the paralleled die operating in high current modules.

Fig. 4: 25 °C and 125 °C forward I-V characteristics of an SPT- IGBT chip (a) and irradiated Diode chip (b).

## **Switching Performance**

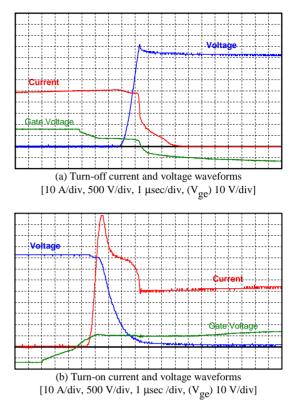

The dynamic performance of the new chip set was evaluated in an inductive load chopper circuit. Figure (5) shows the switching characteristics of the SPT-IGBT during (a) turn-off and (b) turn-on at 125°C. The tests were carried out at a nominal current of 50A and a DC rail voltage of 4200V. The turn-off current of the SPT IGBT is very smooth with a short tail. This behaviour is due to the SPT buffer layer in front of the anode and the thin wafer specification. Since less plasma needs to be extracted due to the presence of a weak anode, the tail phase of the current during turn-off is short and therefore turn-off losses are kept low. Therefore, a perfect balance is achieved resulting in low losses, short tail current, and low EMI levels. Figure (5.b) shows the switching waveforms during turn-on. The IGBT and diode were designed for low turn-on switching losses thanks to an optimized design for the new diode. The turn-off losses of the IGBT were approximately 0.28J while the turn-on losses were in the order of 0.65J.

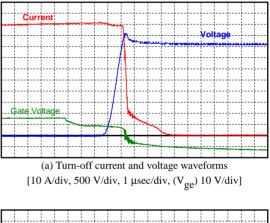

Figure (6) shows the switching characteristics of the SPT-IGBT and diode during (a) turn-off and (b) turn-on at twice the nominal current of 100A at  $125^{\circ}$ C. Rugged performance is demonstrated for both the IGBT and diode. The SPT-IGBT maintains its soft punch through features during turn-off even at high current levels while the turn-on waveforms show soft recovery characteristics for the diode at a di/dt current ramp of 130 A/µsec.

Fig. 5: IGBT switching characteristics at nominal current. ( $V_{cc}$ =4200V,  $I_c$ =50A,  $V_{ge}$ =15V,  $R_G$ =100 $\Omega$ ,  $L_s$ =400nH, @125<sup>o</sup>C)

Fig. 6: IGBT switching characteristics. At 2 x nominal current ( $V_{cc}$ =4200V,  $I_c$ =100A,  $V_{ge}$ =15V,  $R_G$ =100 $\Omega$ ,  $L_s$ =400nH, @125<sup>0</sup>C)

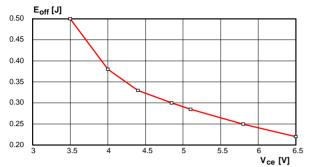

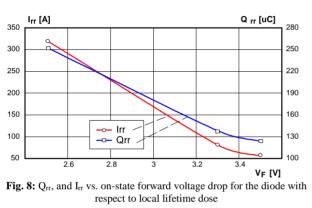

Detailed trade-off curves for on-state vs. switching parameters for both the IGBT and diode are shown in figures (7) and (8) respectively.

Fig. 7: Turn-off losses vs. on-state losses for the SPT-IGBT with respect to anode injection efficiency  $(V_{cc}=4200V, I_c=50A, R_G=100\Omega, @125^{0}C)$

$(V_{cc}=4200V, I_{c}=50A, di/dt=250 A/\mu sec , R_{G}=100\Omega, @125^{0}C)$

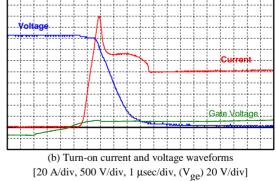

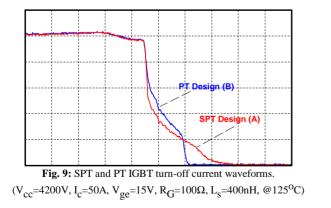

A PT-IGBT was also manufactured for comparison with the SPT-IGBT design with the same silicon thickness. The PT-IGBT required local lifetime control using He<sup>++</sup> near the buffer region due to the high anode efficiency necessary for the PT design. The He<sup>++</sup> dose was adjusted to obtain the similar on-state and turn-off losses to those for the SPT design. Turn-off current waveforms were obtained for both SPT and PT designs as shown in figure (9).

The PT-IGBT current waveform shows clearly a sharp drop during current fall time due to hard punch through. This can lead to an inhomogeneous current flow in the IGBT and degraded turn-off capability and possible voltage spikes in the circuit. The SPT-IGBT current waveform however shows a soft current fall with a short tail until the IGBT is non-conducting.

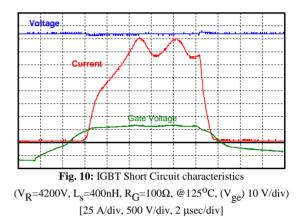

The waveforms in figure (10), show the SPT-IGBT in short circuit mode at a DC rail voltage of 4200V at 125°C. The current waveform shows a maximum short circuit current of approximately 3.5 times nominal current.

#### Conclusion

We demonstrate for the first time a high performance IGBT and Diode chip set with blocking capabilities above 8000V. The "Soft-Punch-Through" SPT-IGBT and diode show excellent static and dynamic characteristics with respect to stable blocking behaviour, low on-state and switching losses, wide SOA and low cosmic ray failure rate. Experimental comparisons between SPT and PT designs for the IGBT were also presented and discussed, outlining the superior performance of the SPT concept when applied at this voltage level IGBTs.

#### References

- F. Bauer et al, "Design Considerations and Characteristics of Rugged Punch-through (PT) IGBTs with 4.5 kV Blocking Capability", Proc. ISPSD96, p.327, 1996

- [2] K. Yoshikawa et al, "A Study on Wide RBSOA of 4.5kV Power Pack IGBT", Proc. ISPSD'2001, p.117, 2001.

- [3] F. Bauer et al, "A High Voltage IGBT and Diode Chip Set designed for the 2.8kV DC Link Level with Short Circuit Capability extending to the Maximum Blocking Voltage", Proc. ISPSD'2000, p.29, 2000.

- [4] T. Wikstroem et al, "Experimental Study on Plasma Engineering in 6500 V IGBTs", Proc. ISPSD'2000, p.37, 2000.

- [5] J. Bauer et al, "6.5kV-Modules using IGBTs with Field Stop Technology", Proc. ISPSD'2001, p.121, 2001.

- [6] M. Rahimo et al, "Novel Soft-Punch-Through (SPT) 1700V IGBT Sets Benchmark on Technology Curve", Proc. PCIM'2001, p. 393, 2001.

- [7] H.R. Zeller, "Cosmic Ray Induced Failures in High Power Semiconductor Devices", Solid-St. Electronics, Vol. 38, p. 2041, 1995