Universal 2-Channel Time-to-Digital Converter

21st February 2011 Document-No.: DB\_GP21\_e V1.1

Published by acam-messelectronic gmbh <sup>©</sup> acam-messelectronic gmbh 2011

#### **Disclaimer / Notes**

The information provided by this preliminary datasheet is believed to be close to the final product. However, it is theoretical and no responsibility is assumed by acam for its use, nor for any infringements of patents or other rights of third parties that may result from its use. The information is subject to change without notice and is provided "as is" without warranty of any kind (expressed or implied). Picostrain is a registered trademark of acam. All other brand and product names in this document are trademarks or service marks of their respective owners.

#### Support

For a complete listing of direct sales, distributors and sales representatives visit the acam website at:

http://www.acam.de/company/distributors

For technical support you can contact the acam support team in the headquarter in Germany or the Distributor in your country. The contact details of acam in Germany are: sales@acam.de or by phone +49-7244-74190.

## **Table of Contents**

| 1 Overview                             |                                | 1-1 |

|----------------------------------------|--------------------------------|-----|

|                                        | 2.1 Electrical Characteristics | 2-1 |

|                                        | 2.2 Converter Specification    | 2-2 |

| 2 Characteristics &                    | 2.2 Timings                    | 2-3 |

| Specifications                         | 2.3 Pin Description            | 2-0 |

|                                        | 2.4 Package Drawings           | 2-  |

|                                        | 2.5 Power Supply               | 2-8 |

|                                        |                                |     |

|                                        | 3.1 Configuration registers    | 3-1 |

|                                        | 3.2 Read registers             | 3-1 |

| <b>3 Registers &amp; Communication</b> | 3.3 EEPROM                     | 3-1 |

|                                        | 3.4 SPI-interface              | 3-1 |

|                                        |                                |     |

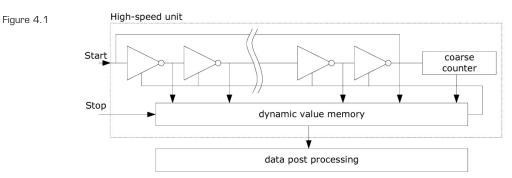

|                                        | 4.1 TDC - Measure Mode 1       | 4-  |

| 4 Converter Frontend                   | 4.2 TDC - Measure Mode 2       | 4-  |

|                                        | 4.3 Analog Input Section       | 4-1 |

|                                        | 4.4 Temperature Measurement    | 4-1 |

|                                        |                                |     |

|                                        | 5.1 Oscillator                 | 5-  |

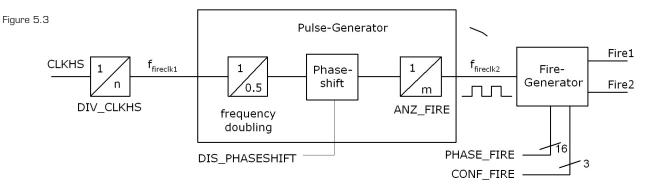

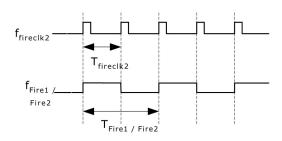

| <b>5 Details and Special Functions</b> | 5.2 Fire-pulse Generator       | 5   |

| J Decails and Special Functions        | 5.3 Fast Initialization        | 5   |

|                                        | 5.4 Noise Unit                 | 5   |

| 6 Applications                         |                                | 6-  |

|                                        |                                | 7-  |

| 7 Miscellaneous                        |                                |     |

# TDC-GP21

## 1 Overview

## 1.1 Features

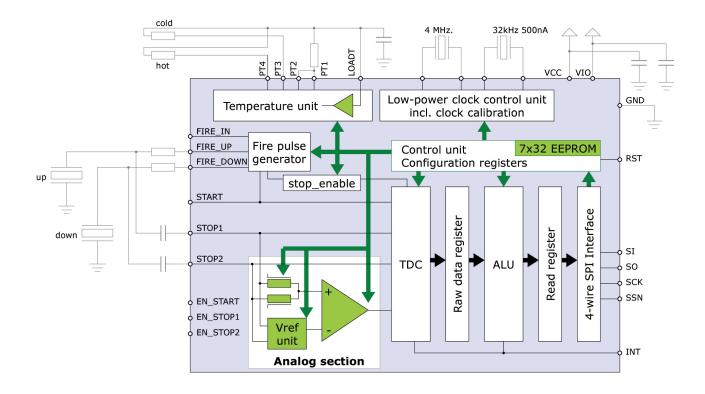

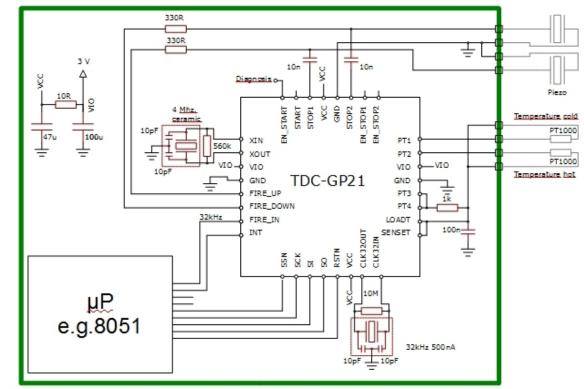

TDC-GP21 is next generation's upgrade for TDC-GP2. It offers pin-to-pin and functional compatibility, several feature improvements and an extended functionality. Analog elements like a chopper stabilized comparator and analog switches simplify external circuits in a significant manner. In parallel, measurement quality is improved and operating current is reduced. The firepulse generator is extended, a new low-power 32 kHz oscillator driver is implemented and the temperature measuring unit is further improved. All in all, the TDC-GP21 is perfectly suited to design ultra-compact and low-cost ultrasonic flow meters and heat meters. If the integrated analog elements of the TDC-GP21 are used, the avarage operating current of a typical heatmeter application can be reduced to 2.2  $\mu$ A

#### Measure Mode 2

- 1 channel with typ. 90 ps resolution

- Double resolution mode with 45 ps, Quad resolution mode with 22 ps resolution

- Measurement range 500 ns to 4 ms

- 2 x CLKHS pulse-pair resolution with 3-fold multihit capability

- Each of the 3 events can be assigned to an adjustable measuring window with 10 ns resolution

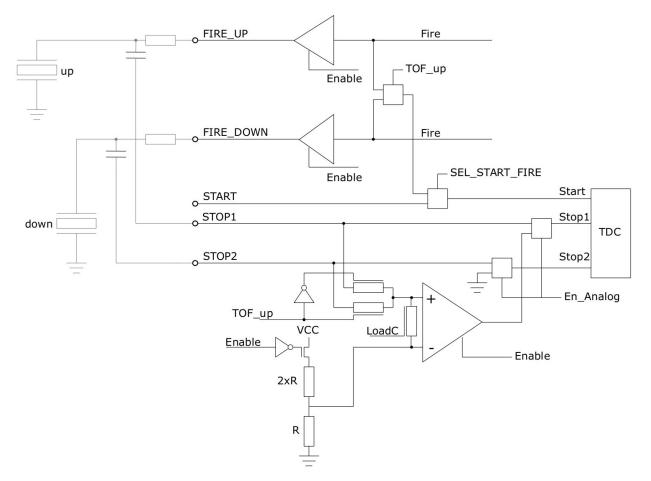

### Analog Input Circuit

- Chopper-stabilized low-offset comparator

- 2 analog switches for input selection

- External circuit is reduced to 2 resistors and 2 capacitors

### **Special Functions**

- Fire pulse generator, up to 127 pulses

- Trigger to rising and/or falling edge

- Precise stop enable by windowing

- Low-power 32 kHz oscillator (500 nA)

- Clock calibration unit

- 7x32 Bit EEPROM

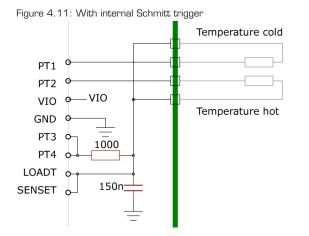

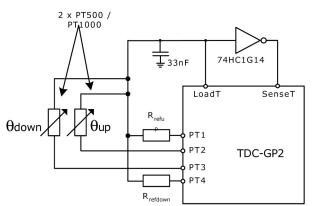

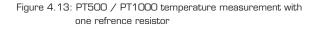

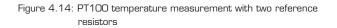

#### **Temperature Measurement Unit**

- 2 or 4 sensors

- PT500/PT1000 or higher

- Schmitt trigger integrated

- Very high resolution: 16-Bit eff. with external Schmitt-trigger (0.004 °C resolution for platinum sensors), 17.5-Bit eff. with integrated low noise Schmitt-trigger (0.0015 °C resolution for platinum sensors)

- Ultra low current (0.08 µA when measuring every 30 seconds)

#### Measure Mode 1

- 2 channels with typ. 90 ps resolution

- 1-channel double resolution with typ. 45 ps

- Range 3.5 ns (O ns) to 2.5 μs

- 20 ns pulse-pair resolution, 4-fold multihit

- Up to 1 million measurements per second im measure mode 1

#### General

- 4-wire SPI interface

- 1 MHz continuous data rate max.

- I/O voltage 2.5 V to 3.6 V

- Core voltage 2.5 V to 3.6 V

- Temperature range 40 °C to +85 °C

- QFN 32 package

## TDC-GP21

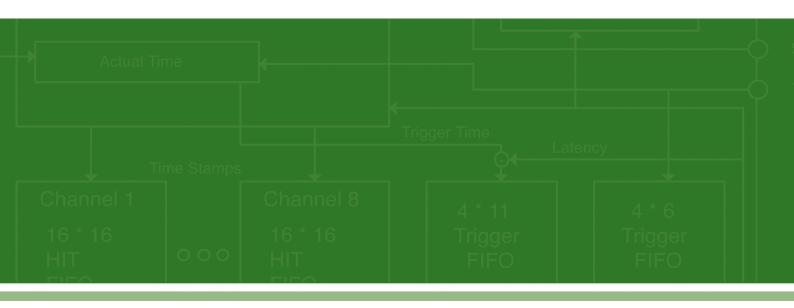

## 1.2 Blockdiagram

## 2 Characteristics & Specifications

## 2.1 Electrical Characteristics

## **Absolute Maximum Ratings**

Supply voltage

| Vcc vs. GND                | - 0.3 to 4.0       | V  |

|----------------------------|--------------------|----|

| Vio vs. GND                | - 0.3 to 4.0       | V  |

| Vin                        | - 0.5 to Vcc + 0.5 | V  |

| Storage temperature (Tstg) | - 55 to 150        | °C |

| ESD rating (HBM), each pin | > 2                | kV |

| Junction temperature (Tj)  | max.125            | °C |

### **Recommended Operating Conditions**

| Symbol | Parameter                    | Conditions                  | Min | Тур | Max | Unit |

|--------|------------------------------|-----------------------------|-----|-----|-----|------|

| Vcc    | Core supply voltage*         | Vio > Vcc                   | 2.5 |     | 3.6 | V    |

| Vio    | I/O supply voltage           |                             | 2.5 |     | 3.6 | V    |

| tri    | Normal input rising time     |                             |     |     | 200 | ns   |

| tfa    | Normal input falling time    |                             |     |     | 200 | ns   |

| tri    | Schmitt trigger rising time  |                             |     |     | 5   | ms   |

| tfa    | Schmitt trigger falling time |                             |     |     | 5   | ms   |

| Та     | Ambient temperature          | Tj must not exceed<br>125°C | -40 |     | 125 | °C   |

\*including the oscillator pins XIN, XOUT, Clk32In, Clk32Out

## DC Characteristics (Vio = Vcc = 3.0 V, Tj = -40 to +85°C)

| Symbol | Parameter                             | Conditions                                    | Min    | Тур               | Max    | Unit           |

|--------|---------------------------------------|-----------------------------------------------|--------|-------------------|--------|----------------|

| 132    | Current 32 kHz                        | lcc + lio, only 32kHz oscil-<br>lator running |        | 1.0               |        | μA             |

| lhs    | Current 4 Mhz oscillator              | 3.6V<br>3.0V<br>off                           |        | 200<br>130<br>< 1 |        | μΑ<br>μΑ<br>nA |

| ltmu   | Current time measuring unit           | only during active time<br>measurement        |        | 4                 |        | mA             |

| lddq   | Quiescent current                     | all clocks off, @ 85 °C                       |        | < 0.1             |        | μA             |

| II     | Input leakage current                 |                                               |        |                   |        | μA             |

| Voh    | High level output voltage             | loh= tbd mA Vio=Min.                          | 0.8Vio |                   |        | V              |

| Vol    | Low level output voltage              | lol = tbd mA, Vio=Min                         |        |                   | 0.2Vio | V              |

| Vih    | High level input voltage              | LVTTL Level, Vio = Max.                       | O.7Vio |                   |        | V              |

| Vil    | Low level input voltage               | LVTTL Level, Vio = Min.                       |        |                   | 0.3Vio | V              |

| Vth    | High level Schmitt trigger<br>voltage |                                               | 0.7Vio |                   |        | V              |

| Symbol | Parameter                            | Conditions | Min | Тур  | Max    | Unit |

|--------|--------------------------------------|------------|-----|------|--------|------|

| Vtl    | Low level Schmitt trigger<br>voltage |            |     |      | 0.3Vio | V    |

| Vh     | Schmitt trigger hysteresis           |            |     | 0.28 |        | V    |

## **Terminal Capacitance**

| Symbol | Terminal       | Condition               | Rated Value |        |      | Unit |

|--------|----------------|-------------------------|-------------|--------|------|------|

|        |                |                         | Min.        | Тур.   | Max. |      |

| Ci     | Digital input  | measured @ Vcc = Vio,   |             | 7      |      | рF   |

| Co     | Digital output | f = 1 MHz,<br>Ta = 25°C |             |        |      |      |

| Cio    | Bidirectional  |                         |             | 9      |      |      |

|        | PT ports       |                         |             | t.b.d. |      |      |

|        | Analog in      |                         |             | t.b.d. |      |      |

## **Analog Frontend**

| Symbol | Terminal                                                  | Condition | Rated Value |      |      | Unit |

|--------|-----------------------------------------------------------|-----------|-------------|------|------|------|

|        |                                                           |           | Min.        | Тур. | Max. |      |

|        | Comparator input offset volta-<br>ge (chopper stabilized) |           |             | < 1  | 2    | mV   |

|        | Rdson Analog switch                                       |           |             | 200  |      | Ohm  |

## 2.2 Converter Specification

## Time Mesuring Unit

| Symbol         | Terminal                        | Condition                                               | Rated Va | ue       |        | Unit |

|----------------|---------------------------------|---------------------------------------------------------|----------|----------|--------|------|

|                |                                 |                                                         | Min.     | Тур.     | Max.   |      |

| LSB            | Resolution (BIN-Size)           | Measure Mode 1 & 2:<br>DOUBLE_RES = 0<br>DOUBLE_RES = 1 |          | 90<br>45 |        | ps   |

|                |                                 | Measure mode 2:<br>GUAD_RES = 1                         |          | 22       |        | ps   |

| σ              | Standard deviation              | Measure Mode 1 & 2:<br>DOUBLE_RES = 0<br>DOUBLE_RES = 1 |          | t.b.d    |        | ps   |

|                |                                 | Measure mode 2:<br>QUAD_RES = 1                         |          | t.b.d    |        | ps   |

| t <sub>m</sub> | Measuring range                 | Measure mode 1                                          | 3.5 ns   |          | 2.4 µs |      |

|                |                                 | Measure mode 2                                          | 500 ns   |          | 4 ms   |      |

| INL            | Integral Non-linearity          |                                                         |          | < 0.1    |        | LSB  |

| DNL            | Differential Non-linea-<br>rity |                                                         |          | < 0.8    |        | LSB  |

### Temperature Measuring Unit<sup>1</sup>

| Symbol | Terminal                           |       | Internal Scl | nmitt-Trigger | external Sch | nmitt-Trigger <sup>2</sup> | Unit   |

|--------|------------------------------------|-------|--------------|---------------|--------------|----------------------------|--------|

|        |                                    |       | PT500        | PT1000        | PT500        | PT1000                     |        |

|        | Resolution RMS                     |       | 17.5         | 17.5          | 16.0         | 16.0                       | Bit    |

|        | SNR                                |       | 105          | 105           | 96           | 96                         | dB     |

|        | Absolute Gain <sup>3</sup>         |       | 0.9912       | 0.9931        | 0.9960       | 0.9979                     |        |

|        |                                    | 3.6 V | 0.9923       | 0.9940        | 0.9962       | 0.9980                     |        |

|        | Absolute Gain vs. Vio <sup>3</sup> | 3.0 V | 0.9912       | 0.9931        | 0.9960       | 0.9979                     |        |

|        |                                    | 2.5 V | 0.9895       | 0.9915        | 0.9956       | 0.9979                     |        |

|        | Gain-Drift vs. Vio                 |       | 0,25         | 0.23          | 0.06         | 0.04                       | %/V    |

|        | max. Gain Error<br>(@ d⊖ = 100 K)  |       | 0,05%        | 0,05%         | 0,02%        | < 0.01%                    |        |

|        | Gain-Drift vs. Temp                |       | 0.022        | 0.017         | 0.012        | 0.0082                     | %/10 K |

|        | Gain-Drift vs. Vio                 |       |              |               | 0,08         |                            | %/V    |

|        | Initial Zero Offset                |       | < 20         | <10           | < 20         | < 10                       | mК     |

|        | Offset Drift vs. Temp              |       | < 0.05       | < 0.03        | < 0,012      | < 0.0082                   | mK∕ ℃  |

|        | PSRR                               |       |              |               | >100         |                            | dB     |

$^1$  All values measured at Vio = Vcc = 3.0 V, Cload = 100 nF for PT1000 and 200 nF for PT500 (COG-type)  $^2$  measured with external 74AHC14 Schmitt-trigger  $^3$  compared to an ideal gain of 1

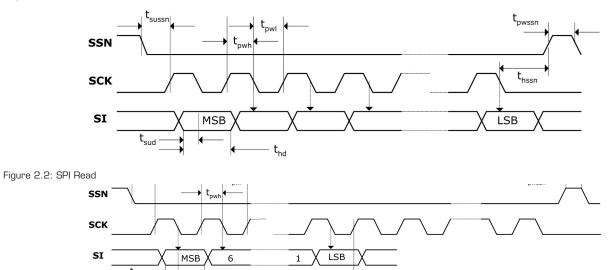

#### 2.3 Timings

At Vcc = 3.0 V  $\pm$  0.3 V, ambient temperature -40 °C to +85 °C unless otherwise specified

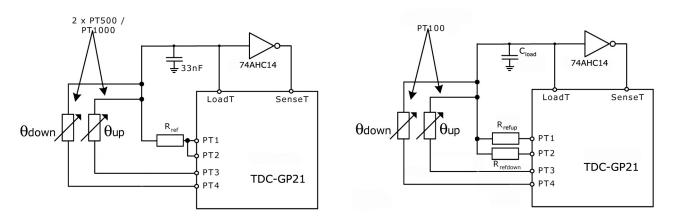

### Oscillator

| Symbol | Parameter                                        | Min. | Тур.   | Max. | Unit |

|--------|--------------------------------------------------|------|--------|------|------|

| Clk32  | 32 kHz reference oscillator                      |      | 32,768 |      | kHz  |

| t32st  | 32 kHz oscillator start-up time after power-up   |      | 3      |      | s    |

| CIkHS  | High-speed reference oscillator                  | 2    | 4      | 8    | MHz  |

| toszst | Oscillator start-up time with ceramic resonator  |      | 100    |      | μs   |

| toszst | Oscillator start-up time with crystal oscillator |      | 3      |      | ms   |

LSB

1

DATA

### **Serial Interface**

| Symbol | Parameter              | Max. @ Vio = |       | Unit |

|--------|------------------------|--------------|-------|------|

|        |                        | 2.5 V        | 3.3 V |      |

| fclk   | Serial clock frequency | 15           | 20    | MHz  |

| Symbol | Parameter                              | Max. @ Vi | Max. @ Vio = |    |  |

|--------|----------------------------------------|-----------|--------------|----|--|

|        |                                        | 2.5 V     | 3.3 V        |    |  |

| tpwh   | Serial clock, pulse width high         | 30        | 25           | ns |  |

| tpwl   | Serial clock, pulse width low          | 30        | 25           | ns |  |

| tsussn | SSN enable to valid latch clock        | 40        | 10           | ns |  |

| tpwssn | SSN pulse width between write cycles   | 50        | 40           | ns |  |

| thssn  | SSN hold time after SCLK falling       | 40        | 25           | ns |  |

| tsud   | Data set-up time prior to SCLK falling | 5         | 5            | ns |  |

| thd    | Data hold time before SCLK falling     | 5         | 5            | ns |  |

| Symbol | Parameter Max. @ Vio =                 |           | Unit         |    |  |

|        |                                        | 2.5 V     | 3.3 V        |    |  |

| tvd    | Data valid after SCLK rising           | 20        | 16           | ns |  |

## Serial Interface (SPI compatible, Clock Phase Bit =1, Clock Polarity Bit =0):

– t<sub>hd</sub>

OPCODE

Figure 2.1: SPI Write

so

MSB

MSB-1

${\rm t}_{\rm vd}$

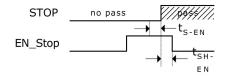

## **Disable Timings**

Figure 2.3:

| Spec   | Description       | Min (ns)  | Max (ns) |

|--------|-------------------|-----------|----------|

| tS-EN  | Enable Setup Time | t.b.d. ns | -        |

| tSH-EN | Enable Hold Time  | t.b.d. ns | -        |

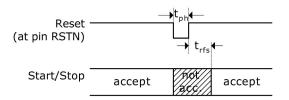

## **Reset Timings**

Figure 2.4:

| Spec | Description                                                    | Min (ns)  | Max (ns) |

|------|----------------------------------------------------------------|-----------|----------|

| tph  | Reset pulse width                                              | t.b.d. ns | -        |

| trfs | Time after rising edge of reset pulse before hits are accepted | t.b.d. µs | -        |

Note: After power-on reset it is necessary to wait minimum 500 us to settle the analog part.

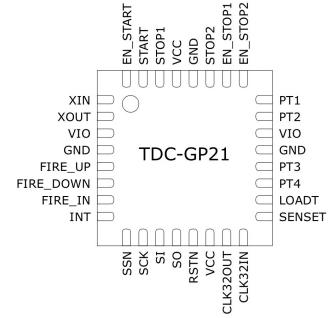

**Pin Description**

2.4

| No. | Name      | Description                          | Buffer type     | Value      | lf not<br>used |

|-----|-----------|--------------------------------------|-----------------|------------|----------------|

| 1   | XIN       | Oscillator driver in                 |                 |            | GND            |

| 2   | XOUT      | Oscillator driver out                |                 |            |                |

| 3   | VIO       | I/O – supply voltage                 |                 |            |                |

| 4   | GND       | Ground                               |                 |            |                |

| 5   | FIRE_UP   | Fire pulse generator output 1        | 48 mA           |            |                |

| 6   | FIRE_DOWN | Fire pulse generator output 2        | 48 mA           |            |                |

| 7   | FIRE_IN   | Signal input for quasi "Sing Around" |                 |            | GND            |

| 8   | INTN      | Interrupt flag                       | 4 mA            | LOW active |                |

| 9   | SSN       | Slave select                         |                 | LOW active |                |

| 10  | SCK       | Clock serial interface               |                 |            |                |

| 11  | SI        | Data input serial interface          |                 |            |                |

| 12  | SO        | Data output serial interface         | 4 mA tristate   |            |                |

| 13  | RSTN      | Reset input                          |                 | LOW active |                |

| 14  | VCC       | Core supply voltage                  |                 |            |                |

| 15  | CLK32OUT  | Output 32 kHz clock generator        |                 |            | n. c.          |

| 16  | CLK32IN   | Input 32 kHz clock generator         |                 |            | GND            |

| 17  | SENSET    | Sense input temperature measurement  | Schmitt trigger |            | GND            |

| 18  | LOADT     | Load output temperature measurement  | 24 mA           |            | n.c.           |

## TDC-GP21

| No. | Name     | Description                    | Buffer type           | Value       | lf not<br>used |

|-----|----------|--------------------------------|-----------------------|-------------|----------------|

| 19  | PT4*     | Port 4 temperature measurement | > 96 mA open<br>drain |             |                |

| 20  | PT3*     | Port 3 temperature measurement | > 96 mA open<br>drain |             |                |

| 21  | GND      | Ground                         |                       |             |                |

| 22  | VIO      | I/O – supply voltage           |                       |             |                |

| 23  | PT2*     | Port 2 temperature measurement | > 96 mA open<br>drain |             |                |

| 24  | PT1*     | Port 1 temperature measurement | > 96 mA open<br>drain |             |                |

| 25  | EN_STOP2 | Enable pin stop input 2        |                       | HIGH active | Vio            |

| 26  | EN_STOP1 | Enable pin stop input 1        |                       | HIGH active | Vio            |

| 27  | STOP2    | Stop input 2                   |                       |             | GND            |

| 28  | GND      | Ground                         |                       |             |                |

| 29  | VCC      | Core supply voltage            |                       |             |                |

| 30  | STOP1    | Stop input 1                   |                       |             | GND            |

| 31  | START    | Start input                    |                       |             |                |

| 32  | EN_START | Enable pin start input         |                       | HIGH active | Vio            |

\*  ${\rm R}_{_{\rm DSON}}$  temperature ports: typ. 1.8  $\Omega$  @ 3.0 V

## 2.5 Package Drawings

Suitable socket: Plastronics 32QN50S15050D

| Symbol | Dimension i | n Millimeters | 6    |                                                     |

|--------|-------------|---------------|------|-----------------------------------------------------|

|        | Min.        | Nom.          | Max. |                                                     |

| D      | -           | 5             | -    |                                                     |

| E      | -           | 5             | -    |                                                     |

| А      | -           | -             | 1    |                                                     |

| A1     | 0           | -             | -    |                                                     |

| b      | 0.17        | -             | 0.3  |                                                     |

| е      | -           | 0.5           | -    |                                                     |

| L      | 0.3         | -             | 0.5  |                                                     |

| G      |             | 3.24          |      | Caution: Center pad is internally connected to GND. |

### Thermal resistance

Roughly 40 K/W at 0 m/s air flow, 37 K/W at 1 m/s air flow, 35 K/W at 2m/s air flow (values just for reference).

# TDC-GP21

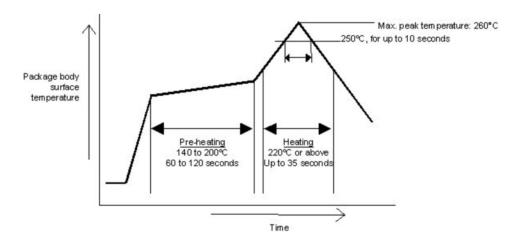

#### Soldering Temperature Profile

The temperature profile for infrared reflow furnace (in which the temperature is the resin's surface temperature) should be maintained within the range described below.

#### Maximum temperature

The maximum temperature requirement for the resin surface, given 260°C as the peak temperature of the package body's surface, is that the resin surface temperature must not exceed 250°C for more than 10 seconds. This temperature should be kept as low as possible to reduce the load caused by thermal stress on the package, which is why soldering for short periods only is recommended. In addition to using a suitable temperature profile, we also recommend that you check carefully to confirm good soldering results.

## 2.6 Power Supply

#### Supply voltage

TDC-GP21 is a high end mixed analog/digital device. To reach full performance of the chip a good power supply is mandantory. It should be high capacitive and of low inductance.

The TDC-GP21 provides two pairs of power supply terminals:

- Vio I/O supply voltage

- Vcc Core supply voltage

All ground pins should be connected to a ground plane on the printed circuit board. Vio and Vcc should be provided by a battery or fixed linear voltage regulator. Do not use switched regulators to avoid disturbances caused by the I/O supply.

The measurement quality of a time-to-digital converter depends on a good power supply. The chip sees mainly pulsed current and therefore a sufficient bypassing is mandatory:

| Vcc | 47 µF  | (minmum 22 µF)  |

|-----|--------|-----------------|

| Vio | 100 µF | (minimum 22 µF) |

The supply voltage should be provided through analog regulators. We strongly recommend not to use switch mode power supplies.

#### **Current consumption**

The current consumption is the sum from different parties (all data for Vio = Vcc = 3.0V):

| <br>ddq          | < 5 nA typ.@3.0V, 25°C                   | Quiescent current, no 32 kHz oscillator running                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>32</sub>  | typ. 1.Ο μΑ                              | Standby current with active 32 kHz oscillator (GP21 waiting for command).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| l <sub>hs</sub>  | typ. 130 µA/s<br>* (active runtime)      | Current into the high speed oscillator at 3.0 V Vio.<br>Example: In ultrasonic flow-meters the high-speed oscillator is<br>on for about 2ms only. The average current consumption is<br>130 $\mu$ A/s * 2 ms = 0.26 $\mu$ A                                                                                                                                                                                                                                                                                                                                                                                                                           |

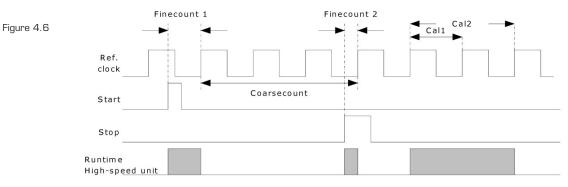

| I <sub>tmu</sub> | typ. 4 mA/s<br>* (active measuring time) | Current into the time measuring unit, In measurement range 1<br>the time measuring unit is active for the start-stop time inter<br>val plus the calibration time interval of 2 periods of the refe<br>rence clock per measurement.<br>In measurement range 2 the time measuring unit is on for<br>average 4 periods of the reference clock per measurement,<br>two for the time measurement and two for calibration.<br>Example: With 10 measurements per second in measurement<br>range 2 and a 4 MHz reference clock the time measuring unit<br>is active for only about 10 $\mu$ s.<br>The average current is 4 mA/s * 10 $\mu$ s = 0.040 $\mu$ A. |

| l <sub>alu</sub> | typ. 7 nA per calculation                | Current into ALU during data proccessing including<br>a calibration calculation.<br>Example: At 1000 measurements per second with 3 stops per<br>start the ALU average current is 7 nA * $3000 = 21 \mu$ A.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# TDC-GP21

I<sub>T</sub> typ. 2.5 μAs \* measure rate The current for a full temperature measurement is typ.2.5 μAs. In heat-meters the temperature is measured typically once every 30 seconds. The average current is about 0.085 μA

I<sub>ana</sub> typ. 0.8 mA Current consuption of the integrated analog part of TDC-GP21during a Time-of-flight (ToF) measurement. The analog part is active for a duration of 250 μs + ToF.

In a typical ultrasonic heat meater application, the flow is measured twice per second. The temperature is measured every 30 seconds. With TDC-GP21 the current consumption of the complete flow and temperature measuring unit, including the analog part, the transducers and PT sensors, is as low as  $2.2 \ \mu$ A typically.

TDC-GP21

## **3 Registers & Communication**

## 3.1 Configuration registers

The TDC-GP21 has 6 configuration registers with 32 bit. The upper 24 bit are used for configuration and are write only. They are used to setup the TDC-GP21 operating mode. The lowest 8 bit can be used e.g. as an ID and can be read back. As the read/write operations start with the MSB communication will be compatible with TDC-GP2.

For communication test please write to register 1 and read back the highest 8 bit from address 5. **Note:**

The write registers of TDC-GP21 are fully upwards compatible with TDC-GP2. A given configuration of TDC-GP2 can directly be used one-to-one in TDC-GP21. The TDC-GP21 than works as a TDC-GP2. The add-on functionality can be selected in register 6 and reg1 Bits 7:0 which are not used in GP2. For proper work of TDC-GP21, a power-up reset via pin or SPI command is necessary after the power-up of the circuit.

| Parameter      | Old name (TDC-GP2) | Register | Bits          | Default<br>value | New or<br>modified |

|----------------|--------------------|----------|---------------|------------------|--------------------|

| ANZ_FAKE       | No_Fake            | 0        | 15            | 0                |                    |

| ANZ_FIRE       | Fire#              | 6<br>0   | 28-31<br>8-10 | 2                | ×                  |

| ANZ_PER_CALRES | CALRES#            | 6        | 22,23         | 0                |                    |

| ANZ_PORT       | PORT#              | 0        | 17            | 1                |                    |

| CALIBRATE      | calibrate          | 0        | 13            | 1                |                    |

| Conf Fire      | CONF_FIRE          | 5        | 28-31         | 0                |                    |

| CURR32K        |                    | 1        | 15            | 1                | ×                  |

| CYCLE_TEMP     |                    | 6        | 18,19         | 0                | ×                  |

| CYCLE_TOF      |                    | 6        | 16,17         | 0                | ×                  |

| DELVAL1        | DELVAL1            | 2 8-23   |               | 0                |                    |

| DELVAL2        | DELVAL2            | 3        | 8-23          | 0                |                    |

| DELVAL3        | DELVAL3            | 4        | 8-23          | 0                |                    |

| DIS_PHASSHIFT  | Dis_PhaseNoise     | 5        | 27            | 0                |                    |

| DIV_CLKHS      | ClkHSDiv           | 0        | 20,21         | 0                |                    |

| DIV_FIRE       | DIV_FIRE           | 0        | 24-27         | 2                |                    |

| DOUBLE_RES     |                    | 6        | 12            | 0                | ×                  |

| EN_ANALOG      |                    | 6        | 31            | 0                | ×                  |

| EN_ERR_VAL     | EN_ERR_VAL         | 3        | 29            | 0                |                    |

| EN_Fast_Init   | EN_FAST_INIT       | 1        | 23            | 0                |                    |

| EN_INT         | EN_INT             | 2<br>6   | 29-31<br>21   | 1                | ×                  |

| EN_STARTNOISE  | EN_STARTNOISE      | 5        | 28            | 0                |                    |

### 3.1.1 Alphanumeric listing of configuration parameters

# TDC-GP21

| Parameter      | Old name (TDC-GP2) | Register | Bits        | Default<br>value | New or<br>modified |

|----------------|--------------------|----------|-------------|------------------|--------------------|

| FIREO_DEF      |                    | 6        | 14          | 0                | ×                  |

| HIT1           | HIT1               | 1        | 24-27       | 5                |                    |

| HIT2           | HIT2               | 1        | 28-31       | 5                |                    |

| Hitin1         | HITIN1             | 1        | 16-18       | 0                |                    |

| Hitin2         | HITIN2             | 1        | 19-21       | 0                |                    |

| HZ6O           |                    | 6        | 15          | 0                | ×                  |

| IDO            |                    | 0        | 0-7         | 0                | ×                  |

| ID1            |                    | 1        | 0-7         | 0                | ×                  |

| ID2            |                    | 2        | 0-7         | 0                | ×                  |

| ID3            |                    | 3        | 0-7         | 0                | ×                  |

| ID4            |                    | 4        | 0-7         | 0                | ×                  |

| ID5            |                    | 5        | 0-7         | 0                | ×                  |

| ID6            |                    | 6        | 0-7         | 0                | ×                  |

| MESSB2         | MRange2            | 0        | 11          | 1                |                    |

| NEG_START      | NEG_START          | 0        | 8           | 1                |                    |

| NEG_STOP_TEMP  |                    | 6        | 30          | 0                | ×                  |

| NEG_STOP1      | NEG_STOP1          | 0        | 9           | 1                |                    |

| NEG_STOP2      | NEG_STOP2          | 0        | 10          | 1                |                    |

| NO_CAL_AUTO    | DisAutoCal         | 0        | 12          | 0                |                    |

| PHFIRE         | Phase_Fire         | 5        | 8-23        | 0                |                    |

| QUAD_RES       |                    | 6        | 13          | 0                | ×                  |

| REPEAT_FIRE    | REPEAT_FIRE        | 5        | 24-26       | 0                |                    |

| RFEDGE1        | RFEDGE1            | 2        | 27          | 0                |                    |

| RFEDGE2        | RFEDGE2            | 2        | 28          | 0                |                    |

| SEL_ECLK_TMP   | SelClkT            | 0        | 14          | 1                |                    |

| SEL_START_FIRE |                    | 1        | 14          | 0                | ×                  |

| SEL_TIMO_MB2   | SEL_TIMO_MR2       | 3        | 27,28       | 3                |                    |

| SEL_TST01      |                    | 1        | 8-10        | 0                | ×                  |

| SEL_TSTO2      |                    | 1        | 11-13       | 0                | ×                  |

| START_CLKHS    | START_CIKHS        | 0<br>6   | 18,19<br>20 | 1                | ×                  |

| TCYCLE         | TCycle             | 0        | 16          | 0                |                    |

| TEMP_PORTDIR   |                    | 6        | 11          | 0                | ×                  |

| TW2            |                    | 6        | 22,23       | 0                | ×                  |

## 3.1.2 List of configuration registers

| Bit number $\rightarrow$    | 15 | 14 | 13   | 12 | 11 | 10 | 9    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------------|----|----|------|----|----|----|------|---|---|---|---|---|---|---|---|---|

| parameter $\rightarrow$     |    |    | para | m1 |    |    | k.d. |   |   |   |   |   |   |   |   |   |

| Default value $\rightarrow$ |    |    |      |    |    |    | 1    | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

k.d. = keep default values

## Register O (address O):

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IDO<br>O |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0        |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |

| J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |

| CALLE OFFICE OFFICE OF A STATE OF A STATE OF A STATE OF A STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |

| off of the second secon |          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |

| AND PER CALIFIES IN CITATION OF TO TO TO THE AND CALL AND |          |  |  |  |  |  |  |  |  |

| Parameter<br>(Old GP2 name) | Description                                                                                                                                                                                                                                                                         | Settings                                                                                                                                                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANZ_FIRE<br>(FIRE#)         | Sets number of pulses generated by fire<br>pulse generator. Additional 3 bits are set in<br>register 6.<br>For values ANZ_FIRE > 15 the phase setting<br>(PHFIRE) can not be used.                                                                                                  | 0 = off<br>1 = 1 pulse<br>2 = 2 pulses<br><br>127 = 127 pulses                                                                                                               |

| DIV_FIRE                    | Sets predivider for internal clock signal of fire<br>pulse generator                                                                                                                                                                                                                | O = not permitted1 = divided by 2<br>2 = divided by 3<br>3.= divided by 4<br><br>15 = divided by 16                                                                          |

| ANZ_PER_CALRES<br>(CALRES#) | Sets number of periods used for calibrating the ceramic resonator                                                                                                                                                                                                                   | 0 = 2 periods = 61.035 μs<br>1 = 4 periods = 122.07 μs<br>2 = 8 periods = 244.14 μs<br>3 = 16 periods = 488.281 μs                                                           |

| DIV_CLKHS<br>(ClkHSDiv)     | Sets predivider for CLKHS                                                                                                                                                                                                                                                           | O = divided by 1<br>1 = divided by 2<br>2 = divided by 4<br>3 = divided by 4                                                                                                 |

| START_CLKHS[1:0]            | Defines the time interval the chip waits after<br>switching on the oscillator before making a<br>measurement.<br><b>Note</b> :<br>The highest bit to adjust START_CLKS is loca-<br>ted in register 6, bit 20. This has to be set to<br>1 for settling times of 2.44 ms and 5.14 ms. | 0 = Oscillator off<br>1 = Oscillator continuously on<br>2 = settling time 480 μs<br>3 = settling time 1.46 ms<br>4 = settling time 2.44 ms<br>5 to 7 = settling time 5.14 ms |

| ANZ_PORT<br>(PORT#)         | Sets number of ports used for temperature measurement                                                                                                                                                                                                                               | O = 2 temperature ports (PT1 and PT2)<br>1 = 4 temperature ports                                                                                                             |

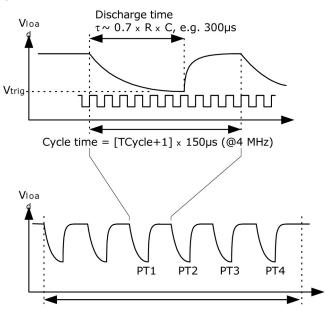

| TCYCLE                      | Sets cycle time for temperature measure-<br>ment                                                                                                                                                                                                                                    | O = 128 μs cycle time @ 4 MHz<br>1 = 512 μs cycle time @ 4 MHz (recom-<br>mended)                                                                                            |

| ANZ_FAKE<br>(FAKE#)         | Number of dummy cycles at the beginning of a tempera-ture measurement                                                                                                                                                                                                               | 0 = 2 Fake measurements<br>1 = 7 Fake measurements                                                                                                                           |

| SEL_ECLK_TMP<br>(SelClkT)   | Select reference signal for internal cycle clock<br>for tem-perature measurement | O = use 32.768 kHz as cycle clock<br>1 = use 128 * CLKHS as period for cycle<br>clock (32µs with 4 MHZ high speed clock<br>signal ) |

|-----------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| CALIBRATE                   | Enables/disables calibration calculation in the ALU                              | O = calibration off (allowed only in<br>mode 1)<br>1 = calibration on (recommended)                                                 |

| NO_CAL_AUTO<br>(DisAutoCal) | Enables/disables auto-calibration run in the TDC                                 | O = auto-calibration after measurement<br>1 = auto-calibration disabled                                                             |

| MESSB2<br>(MRange2)         | Switch to measurement range 2                                                    | 0 = measurement range 1<br>1 = measurement range 2                                                                                  |

| NEG_STOP2                   | Negation stop 2 input                                                            | 0 = non-inverted input signal – rising edge<br>1 = inverted input signal – falling edge                                             |

| NEG_STOP1                   | Negation stop 1 input                                                            | O = non-inverted input signal – rising edge<br>1 = inverted input signal – falling edge                                             |

| NEG_START                   | Negation start input                                                             | O = non-inverted input signal – rising edge<br>1 = inverted input signal – falling edge                                             |

| IDO                         | Free bits, e.g. to be used as identification or version number                   |                                                                                                                                     |

## Register 1 (address 1):

| 31 | 30                        | 29 | 28 | 27 | 26 | 25 | 24 | 23    | 22 | 21 | 20    | 19 | 18    | 17 | 16   | 15   | 14  | 13  | 12   | 11 | 10  | 9 | 8 | 7-0 |

|----|---------------------------|----|----|----|----|----|----|-------|----|----|-------|----|-------|----|------|------|-----|-----|------|----|-----|---|---|-----|

|    | HIT2 HIT1                 |    |    |    |    |    | F  | IITIN | 2  | F  | IITIN | 1  |       |    | SEL  | _TS1 | ro2 | SEL | _TST | 01 | ID1 |   |   |     |

| 0  | 0 1 0 1 0 1 0 1 0 1 0 0 0 |    |    |    |    |    |    |       |    | 0  | 0     | 0  | 0     | 1  | 0    | 0    | 0   | 0   | 0    | 0  | 0   | 0 |   |     |

|    |                           |    |    |    |    |    |    |       |    |    |       |    |       |    | Ţ    | Ţ    |     |     |      |    |     |   |   |     |

|    |                           |    |    |    |    |    |    |       |    |    |       |    |       | ot |      |      |     |     |      |    |     |   |   |     |

|    | ENTREST MILL & d.         |    |    |    |    |    |    |       |    |    |       |    |       | Ŕ  | 8°°  | S.   |     |     |      |    |     |   |   |     |

|    | A CARACTER STATE          |    |    |    |    |    |    |       |    |    |       |    |       | Ċ, | 832H |      |     |     |      |    |     |   |   |     |

|    | ×                         |    |    |    |    |    |    |       |    |    |       |    | cft)~ | /  |      |      |     |     |      |    |     |   |   |     |

|    |                           | 1  |    |    |    |    |    |       |    |    |       |    | 1     |    |      |      |     |     |      |    |     |   |   |     |

| Parameter | Description                                                                                                  | Settings                                                                                                                                                                                                                                                                                                                                                    |                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| HIT2      | Defines operator for ALU data post-proces-<br>sing<br>Measure mode 1: HIT1-HIT2<br>Measure mode 2: HIT2-HIT1 | $\begin{array}{l} \mbox{MRange1:} \\ \mbox{O} = Start \\ \mbox{1} = 1. Stop Ch1 \\ \mbox{2} = 2. Stop Ch1 \\ \mbox{3} = 3. Stop Ch1 \\ \mbox{4} = 4. Stop Ch1 \\ \mbox{5} = no action \\ \mbox{6} = Cal1 Ch1 \\ \mbox{7} = Cal2 Ch1 \\ \mbox{9} = 1. Stop Ch2 \\ \mbox{A} = 2. Stop Ch2 \\ \mbox{B} = 3. Stop Ch2 \\ \mbox{C} = 4. Stop Ch2 \\ \end{array}$ | MRange2:<br>2 = 1. Stop Ch1<br>3 = 2. Stop Ch1<br>4 = 3. Stop Ch1 |

| HIT1           | Defines operator for ALU data post-proces-<br>sing<br>MRange1: HIT1-HIT2<br>MRange2: HIT2-HIT1                                                                                            | MRange1:       MRange2:         0 = Start       1 = Start         1 = 1. Stop Ch1       2 = 2. Stop Ch1         3 = 3. Stop Ch1       4 = 4. Stop Ch1         5 = no action       6 = Cal1 Ch1         7 = Cal2 Ch1       9 = 1. Stop Ch2         A = 2. Stop Ch2       B = 3. Stop Ch2         C = 4. Stop Ch2       6 = Cal2 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_FAST_INIT   | Enables fast init operation                                                                                                                                                               | O = Fast init mode disabled<br>1 = Fast init mode enabled                                                                                                                                                                                                                                                                      |

| HITIN2         | Number of expected hits on channel 2                                                                                                                                                      | O = stop channel 2 disabled<br>1 = 1 hit<br>2 = 2 hits<br>3 = 3 hits<br>4 = 4 hits<br>5 to 7 = not permitted                                                                                                                                                                                                                   |

| HITIN1         | Number of expected hits on channel 1                                                                                                                                                      | O = stop channel 1 disabled<br>1 = 1 hit<br>2 = 2 hits<br>3 = 3 hits<br>4 = 4 hits<br>5 to 7 = not permitted                                                                                                                                                                                                                   |

| CURR32K        | Low current option for 32 kHz oscillator.<br>Basically there is no need to use high current<br>option (1). Low current (O) also guarantees<br>oscillation.                                | 0 = low current (recommended)<br>1 = high current (GP2 compatibility)                                                                                                                                                                                                                                                          |

| SEL_START_FIRE | Firepulse is used as TDC start. The START input is disabled.                                                                                                                              | 0 = TDC-GP2 behaviour<br>1 = Use FIRE as Start                                                                                                                                                                                                                                                                                 |

| SEL_TSTO2      | Defines functionality of EN_START pin. Besi-<br>des the GP2 functionality this pin can act as<br>output for various signals. If SEL_TSTOP2 > 0<br>then EN_START = HIGH internally.        | O = GP2 functionality, Fire_in input for sing<br>around<br>5 = TOF_UP =1 when TOF_UP measure-<br>ment is active<br>7 = 4 kHz (32 kHz/8) clock output                                                                                                                                                                           |

| SEL_TSTO1      | Defines functionality of FIRE_IN pin. Besides<br>the GP2 functionality this üin can act as out-<br>put for various signals. If SEL_TSTO1 >1 the<br>FIRE_IN iscoonected to GND internally. | O = GP2 functionality, Fire_in input for sing<br>around<br>5 = EN_STOP by DELVAL output<br>6 = Output signal of the integrated com-<br>parator<br>7 = 32 kHz clock output                                                                                                                                                      |

| ID1            | Free bits, e.g. to be used as identification or version number                                                                                                                            |                                                                                                                                                                                                                                                                                                                                |

## Register 2 (address 2):

| 31 | 30   | 29   | 28  | 27 | 26 | 25      | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12  | 11 | 10 | 9 | 8 | 7-0 |

|----|------|------|-----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|---|---|-----|

| E  | N_IN | Т    |     |    |    | DELVAL1 |    |    |    |    |    |    |    |    |    |    |    |    | ID2 |    |    |   |   |     |

| 0  | 0    | 1    | 0   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0 | 0 | 0   |

|    | PH   | DGE2 | DGE |    |    |         |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |   |   |     |

| Parameter | Description                                                                                                                                         | Settings                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_INT    | Activates interrupt sources wired by OR.<br>Additional bit in register 6 (see there, too)                                                           | Bit 31 = Timeout interrupt enable<br>Bit 30 = End Hits interrupt enable<br>Bit 29 = ALU interrupt enable<br>Reg6, BIT21 = End of EEPROM action |

| RFEDGE2   | Edge sensitivity channel 1                                                                                                                          | O = rising or falling edge<br>1 = rising and falling edge                                                                                      |

| RFEDGE1   | Edge sensitivity channel 1                                                                                                                          | O = rising or falling edge<br>1 = rising and falling edge                                                                                      |

| DELVAL1   | Delay value for internal stop enable unit, hit 1<br>channel 1. Fixed point number with 14 inte-<br>ger and 5 fractional digits in multiples of Tref | DELVAL1 = 0 to 16383.96875                                                                                                                     |

| ID2       | Free bits, e.g. to be used as identification or version number                                                                                      |                                                                                                                                                |

## Register 3 (address 3):

|       |       |      |                |    | ,  | -  |    |    |    |    |    |    |    |      |    |    |    |    |    |    |    |   |   |     |

|-------|-------|------|----------------|----|----|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|---|---|-----|

| 31    | 30    | 29   | 28             | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-0 |

| k.    | d.    |      |                |    |    |    |    |    |    |    |    |    | DE | ELVA | L2 |    |    |    |    |    |    |   |   | ID3 |

| Ο     |       |      |                |    |    |    |    |    |    | 0  |    |    |    |      |    |    |    |    |    |    |    |   |   |     |

| EN FR | R.VAL | MO M | 6 <sup>2</sup> | ļ  |    |    |    |    |    |    |    |    |    |      |    |    |    |    |    |    |    |   |   |     |

| Parameter    | Description                                                                                                                                         | Settings                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| EN_ERR_VAL   | Timeout forces ALU to write OxFFFFFFFF into the output register                                                                                     | O = disabled<br>1 = enabled                                            |

| SEL_TIMO_MB2 | Select predivider for timeout in measurement<br>range 2                                                                                             | Ο = 64 μs<br>1 = 256 μs<br>2 = 1024 μs<br>3 = 4096 μs<br>@ 4 MHz ClkHS |

| DELVAL2      | Delay value for internal stop enable unit, hit 2<br>channel 1. Fixed point number with 14 inte-<br>ger and 5 fractional digits in multiples of Tref | DELVAL1 = 0 to 16383.96875                                             |

| ID3          | Free bits, e.g. to be used as identification or version number                                                                                      |                                                                        |

## Register 4 (address 5):

| 31 | 30           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18  | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-0 |

|----|--------------|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|---|---|-----|

|    | k.d. DELVAL3 |    |    |    |    |    |    |    |    |    |    |    | ID4 |    |    |    |    |    |    |    |    |   |   |     |

| 0  | 0            | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0   |

| Parameter | Description                                                                                                                                         | Settings                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| DELVAL3   | Delay value for internal stop enable unit, hit 3<br>channel 1. Fixed point number with 14 inte-<br>ger and 5 fractional digits in multiples of Tref | DELVAL1 = 0 to 16383.96875 |

| ID4       | Free bits, e.g. to be used as identification or version number                                                                                      |                            |

## Register 5 (address 5):

|     | 31     | 30       | 29   | 28    | 27     | 26   | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-0 |

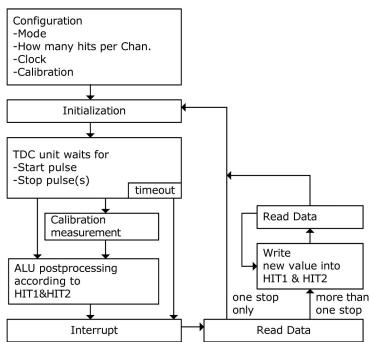

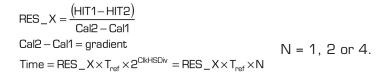

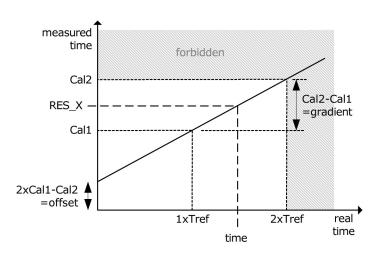

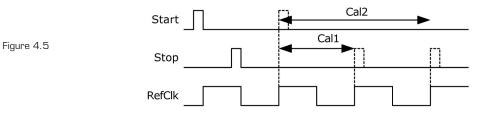

|-----|--------|----------|------|-------|--------|------|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|---|---|-----|