Adesto Field Application

http://www.adestotech.com/

#### **Content:**

- Differences Highlight require NO software change

- Features Highlight for AT45DB321E

- Features not recommended for new design

- AT45DB321E Command Set Summary

- Program / Erase Time comparison

- Feature description

- 2-byte Status Register

- Enter and exit Ultra-Deep Power Down

- Freeze Sector Lockdown

- Buffer and Page size reconfiguration

- Software Reset

- Low Power Read Mode

- Program / Erase Suspend and Resume

# AT45DB321E Differences Highlight — Items require Software Change

#### Conversion from AT45DB321D to AT45DB321E

- ✓ Command: No change

- ✓ Product ID: No change

- ✓ Page Program Time: No Change

- ✓ Erase Time: No Change

- ✓ Status Register: No change

AT45DB321E is designed to replace the AT45DB321D in the 8 pin packages. While it maintains the fine granular structure, it also introduces a few new features.

- ✓ Improved Deep Power Down mode 5µA (typical)

- ✓ Ultra-Deep Power Down mode 400nA

- ✓ Low Power Read mode

- ✓ User configurable and re-configurable page size (512bytes or 528bytes)

- ✓ Program / Erase Suspend and Resume

- ✓ New max operating clock frequency at 104MHz (command 1Bh)

- ✓ Wider operating voltage range: 2.3V 3.6V

- ✓ Allows Software Reset

- ✓ Now with 5 Bytes Device ID

#### AT45DB321D

- Single 2.5V 3.6V or 2.7V 3.6V supply

- RapidS<sup>™</sup> serial interface: 66MHz maximum clock frequency

- SPI compatible modes 0 and 3

- User configurable page size

- 512 bytes per page

- 528 bytes per page

- Page size can be factory preconfigured for 512 bytes

- Page program operation

- Intelligent programming operation

- 8,192 pages (512/528 bytes/page) main memory

- Flexible erase options

- Page erase (512 bytes)

- Block erase (4KB)

- Sector erase (64KB)

- Chip erase (32Mb)

- Two SRAM data buffers (512/528 bytes)

- Allows receiving data while reprogramming the flash array

- Continuous read capability through entire array

- Ideal for code shadowing applications

- Low power dissipation

- 7mA active read current ,typical

- 25µA standby current, typical

- 15µA deep power down, typical

#### AT45DB321E

Single 2.3V - 3.6V supply

- Supports SPI modes 0 and 3

- Supports RapidS<sup>™</sup> operation

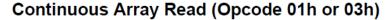

- Continuous read capability through entire array

- Up to 85MHz

- Low-power read option up to 10MHz

- Clock-to-output time (t<sub>v</sub>) of 6ns maximum

- User configurable page size

- 512 bytes per page

- 528 bytes per page (default)

- Page size can be factory pre-configured for 512 bytes

- Two fully independent SRAM data buffers (512/528 bytes)

- Flexible programming options

- Byte/Page Program (1 to 512/528 bytes) directly into main memory

- Buffer Write

- Buffer to Main Memory Page Program

- Flexible erase options

- Page Erase (512/528 bytes)

- Block Erase (4KB)

- Sector Erase (64KB)

- Chip Erase (32-Mbits)

- Program and Erase Suspend/Resume

- Advanced hardware and software data protection features

- Individual sector protection

- Individual sector lockdown to make any sector permanently read-only

- Low-power dissipation

- 500nA Ultra-Deep Power-Down current (typical)

- 3µA Deep Power-Down current (typical)

- 25µA Standby current (typical)

- 11mA Active Read current (typical)

New

New

New

New

# AT45DB321E Features not recommended for new design

#### These commands are supported, but recommended not to use in new design

| Commands                                                                 | AT45DB321D | AT45DB321E |

|--------------------------------------------------------------------------|------------|------------|

| Continuous Array Read (Legacy Command – Not Recommended for New Designs) | E8H        | E8h        |

| Buffer 1 Read                                                            | 54H        | 54H        |

| Buffer 2 Read                                                            | 56H        | 56H        |

| Main Memory Page Read                                                    | 52H        | 52H        |

| Continuous Array Read                                                    | 68H        | 68H        |

| Status Register Read                                                     | 57H        | 57H        |

# **AT45DB321E Command Set Comparison**

| Commands                                                                 | AT45DB321D         | AT45DB321E            |

|--------------------------------------------------------------------------|--------------------|-----------------------|

| Buffer 1 Read (High Frequency)                                           | D4H                | D4h                   |

| Buffer 1 Read (Low Frequency)                                            | D1H                | D1h                   |

| Buffer 2 Read (High Frequency)                                           | D6H                | D6h                   |

| Buffer 2 Read (Low Frequency)                                            | D3H                | D3h                   |

| Continuous Array Read (High Frequency)                                   | OBH                | 0Bh                   |

| Continuous Array Read (High Frequency)                                   |                    | 1Bh <b>←</b>          |

| Continuous Array Read (Legacy Command – Not Recommended for New Designs) | E8H                | E8h                   |

| Continuous Array Read (Low Frequency)                                    | 03H                | 03h                   |

| Continuous Array Read (Low Power Mode)                                   |                    | 01h                   |

| Main Memory Page Read                                                    | D2H                | D2h                   |

| Block Erase                                                              | 50H                | 50h                   |

| Buffer 1 to Main Memory Page Program with Built-In Erase                 | 83H                | 83h                   |

| Buffer 1 to Main Memory Page Program without Built-In Erase              | 88H                | 88h                   |

| Buffer 1 Write                                                           | 84H                | 84h                   |

| Buffer 2 to Main Memory Page Program with Built-In Erase                 | 86H                | 86h                   |

| Buffer 2 to Main Memory Page Program without Built-In Erase              | 89H                | 89h                   |

| Buffer 2 Write                                                           | 87H                | 87h                   |

| Chip Erase                                                               | C7H, 94H, 80H, 9AH | C7h + 94h + 80h + 9Ah |

| Main Memory Byte/Page Program through Buffer 1 without Built-In Erase    |                    | 02h                   |

| Main Memory Page Program through Buffer 1 with Built-In Erase            | 82H                | 82h                   |

| Main Memory Page Program through Buffer 2 with Built-In Erase            | 85H                | 85h                   |

| Page Erase                                                               | 81H                | 81h                   |

| Program/Erase Resume                                                     |                    | D0h                   |

| Program/Erase Suspend                                                    |                    | B0h                   |

| Sector Erase                                                             | 7CH                | 7Ch                   |

# **AT45DB321E Command Set Comparison**

| Commands AT45DB321E                                     | AT45DB321E                        |

|---------------------------------------------------------|-----------------------------------|

| Enable Sector Protection 3DH + 2AH + 7                  | 'FH + A9H   3Dh + 2Ah + 7Fh + A9h |

| Disable Sector Protection 3DH + 2AH + 7                 | 'FH + 9AH   3Dh + 2Ah + 7Fh + 9Ah |

| Erase Sector Protection Register 3DH + 2AH + 7          | 7FH + CFH   3Dh + 2Ah + 7Fh + CFh |

| Program Sector Protection Register 3DH + 2AH + 7        | 7FH + FCH   3Dh + 2Ah + 7Fh + FCh |

| Read Sector Protection Register 32H                     | 32h                               |

| Sector Lockdown 3DH + 2AH + 7                           | 7FH + 30H   3Dh + 2Ah + 7Fh + 30h |

| Read Sector Lockdown Register 35H                       | 35h                               |

| Freeze Sector Lockdown                                  | 34h + 55h + AAh + 40h             |

| Program Security Register 9BH + 00H + 00                | 0H + 00H   9Bh + 00h + 00h + 00h  |

| Read Security Register 77H                              | 77h                               |

| Main Memory Page to Buffer 1 Transfer 53H               | 53h                               |

| Main Memory Page to Buffer 2 Transfer 55H               | 55h                               |

| Main Memory Page to Buffer 1 Compare 60H                | 60h                               |

| Main Memory Page to Buffer 2 Compare 61H                | 61h                               |

| Auto Page Rewrite through Buffer 1 58H                  | 58h                               |

| Auto Page Rewrite through Buffer 2 59H                  | 59h                               |

| Deep Power-Down B9H                                     | B9h                               |

| Resume from Deep Power-Down ABH                         | ABh                               |

| Ultra-Deep Power-Down                                   | 79h                               |

| Status Register Read D7H                                | D7h                               |

| Configure "Power of 2" (Binary) Page Size 3Dh + 2Ah + 8 | 0h + A6h   3Dh + 2Ah + 80h + A6h  |

| Configure Standard DataFlash Page Size                  | 3Dh + 2Ah + 80h + A7h             |

| Software Reset                                          | F0h + 00h + 00h + 00h             |

# **AT45DB321E Command Set Comparison**

#### **AT45DB321E New 5-byte Manufacturer ID**

| Commands                                                           | AT45DB321D | AT45DB321E   |

|--------------------------------------------------------------------|------------|--------------|

| Manufacturer and Device ID Read                                    | 9FH        | 9Fh          |

| Manufacturer ID                                                    | 1Fh        | 1Fh          |

| Device ID (Byte 1)                                                 | 27h        | 27h          |

| Device ID (Byte 2)                                                 | 00h        | 00h          |

| [Optional to Read] Extended Device Information (EDI) String Length | 00h        | 01h <b>←</b> |

| [Optional to Read] EDI Byte 1                                      |            | 00h          |

# AT45DB321D and AT45DB321E - Program / Erase Time

|                 | AT45DB321D                                       | AT45DB321D<br>(2.5V Version) |     | AT45DB321D |     |     |     |      |

|-----------------|--------------------------------------------------|------------------------------|-----|------------|-----|-----|-----|------|

| Symbol          | Parameter                                        | Min                          | Тур | Max        | Min | Тур | Max | Unit |

| t <sub>EP</sub> | Page erase and programming time (512-/528-bytes) |                              | 17  | 40         |     | 17  | 40  | ms   |

| t <sub>P</sub>  | Page programming time (512/528 bytes)            |                              | 3   | 6          |     | 3   | 6   | ms   |

| t <sub>PE</sub> | Page erase time (512/528 bytes)                  |                              | 15  | 35         |     | 15  | 35  | ms   |

| t <sub>BE</sub> | Block erase time (4,096/4,224 bytes)             |                              | 45  | 100        |     | 45  | 100 | ms   |

| t <sub>SE</sub> | Sector erase time (131,072/135,168 bytes)        |                              | 1.6 | 5          |     | 1.6 | 5   | s    |

| t <sub>CE</sub> | Chip erase time                                  |                              | TBD | TBD        |     | TBD | TBD | S    |

| Symbol          | Parameter AT45DB321E                            | Min | Тур | Max | Units |

|-----------------|-------------------------------------------------|-----|-----|-----|-------|

| t <sub>EP</sub> | Page Erase and Programming Time (512/528 bytes) |     | 17  | 35  | ms    |

| t <sub>P</sub>  | Page Programming Time                           |     | 3   | 4   | ms    |

| t <sub>BP</sub> | Byte Programming Time                           |     | 8   |     | μs    |

| t <sub>PE</sub> | Page Erase Time                                 |     | 12  | 35  | ms    |

| t <sub>BE</sub> | Block Erase Time                                |     | 45  | 100 | ms    |

| t <sub>SE</sub> | Sector Erase Time                               |     | 0.7 | 1.4 | S     |

| t <sub>CE</sub> | Chip Erase Time                                 |     | 45  | 80  | s     |

## AT45DB321E – New 2-byte Status Register

#### Status Register Read

The 2-byte Status Register can be used to determine the device's ready/busy status, page size, a Main Memory Page to Buffer Compare operation result, the sector protection status, Freeze Sector Lockdown status, erase/program error status, Program/Erase Suspend status, and the device density. The Status Register can be read at any time, including during an internally self-timed program or erase operation.

To read the Status Register, the  $\overline{\text{CS}}$  pin must first be asserted and then the opcode D7h must be clocked into the device. After the opcode has been clocked in, the device will begin outputting Status Register data on the SO pin during every subsequent clock cycle. After the second byte of the Status Register has been clocked out, the sequence will repeat itself, starting again with the first byte of the Status Register, as long as the  $\overline{\text{CS}}$  pin remains asserted and the clock pin is being pulsed. The data in the Status Register is constantly being updated, so each repeating sequence may output new data. The RDY/BUSY status is available for both bytes of the Status Register and is updated for each byte.

Deasserting the  $\overline{CS}$  pin will terminate the Status Register Read operation and put the SO pin into a high-impedance state. The  $\overline{CS}$  pin can be deasserted at any time and does not require that a full byte of data be read.

Bit Name Description Type<sup>(1)</sup> Device is busy with an internal operati RDY/BUS Device is busy with an internal operation. Ready/Busy Status RDY/BUSY Ready/Busy Status Device is ready. Device is ready. RES Reserved for Future Use R Reserved for future use. 6 Main memory page data matches buffer data Compare Result Erase or program operation was successfu Main memory page data does not match buffer data. **EPE** Erase/Program Error R Erase or program error detected 1101 Sector protection is disabled. RES Reserved for Future Use Reserved for future use. PROTECT Sector Protection Status Sector protection is enabled. Sector Lockdown command is disabled. 3 SLE Sector Lockdown Enabled R Device is configured for standard DataFlash page size (528 bytes). Sector Lockdown command is enabled. PAGE SIZE Page Size Configuration Device is configured for "power of 2" binary page size (512 bytes). No program operation has been suspended while using Buffer 2. Program Suspend Status R PS2 (Buffer 2) R = Readable only A sector is program suspended while using Buffer 2. No program operation has been suspended while using Buffer 1. Program Suspend Status PS1 R (Buffer 1) A sector is program suspended while using Buffer 1. No change on the first byte No sectors are erase suspended. ES Erase Suspend R A sector is erase suspended.

Table 9-2. Status Register Format – Byte 2

Note: 1. R = Readable only

## AT45DB321E - Ultra-Deep Power Down

# New

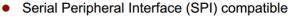

#### **Ultra-Deep Power-Down**

The Ultra-Deep Power-Down mode allows the device to consume far less power compared to the standby and Deep Power-Down modes by shutting down additional internal circuitry. Since almost all active circuitry is shutdown in this mode to conserve power, the contents of the SRAM buffers cannot be maintained. Therefore, any data stored in the SRAM buffers will be lost once the device enters the Ultra-Deep Power-Down mode.

When the device is in the Ultra-Deep Power-Down mode, all commands including the Status Register Read and Resume from Deep Power-Down commands will be ignored. Since all commands will be ignored, the mode can be used as an extra protection mechanism against program and erase operations.

Entering the Ultra-Deep Power-Down mode is accomplished by simply asserting the  $\overline{CS}$  pin, clocking in the opcode 79h, and then deasserting the  $\overline{CS}$  pin. Any additional data clocked into the device after the opcode will be ignored. When the  $\overline{CS}$  pin is deasserted, the device will enter the Ultra-Deep Power-Down mode within the maximum time of  $t_{\text{FUDPD}}$ .

The complete opcode must be clocked in before the  $\overline{CS}$  pin is deasserted, and the  $\overline{CS}$  pin must be deasserted on an even byte boundary (multiples of eight bits); otherwise, the device will abort the operation and return to the standby mode once the  $\overline{CS}$  pin is deasserted. In addition, the device will default to the standby mode after a power cycle.

The Ultra-Deep Power-Down command will be ignored if an internally self-timed operation such as a program or erase cycle is in progress. The Ultra-Deep Power-Down command must be reissued after the internally self-timed operation has been completed in order for the device to enter the Ultra-Deep Power-Down mode.

Figure 10-3. Ultra-Deep Power-Down

Market Leading

Ultra-Deep Power Down

- 400nA (typ)

- 1µA (max)

## AT45DB321E - Exit Ultra-Deep Power Down

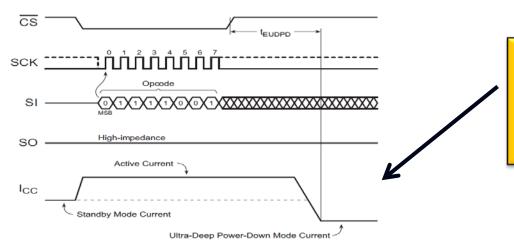

#### **Exit Ultra-Deep Power-Down**

To exit from the Ultra-Deep Power-Down mode, the  $\overline{\text{CS}}$  pin must simply be pulsed by asserting the  $\overline{\text{CS}}$  pin, waiting the minimum necessary  $t_{\text{CSLU}}$  time, and then deasserting the  $\overline{\text{CS}}$  pin again. To facilitate simple software development, a dummy byte opcode can also be entered while the  $\overline{\text{CS}}$  pin is being pulsed just as in a normal operation like the Program Suspend operation; the dummy byte opcode is simply ignored by the device in this case. After the  $\overline{\text{CS}}$  pin has been deasserted, the device will exit from the Ultra-Deep Power-Down mode and return to the standby mode within a maximum time of  $t_{\text{XUDPD}}$ . If the  $\overline{\text{CS}}$  pin is reasserted before the  $t_{\text{XUDPD}}$  time has elapsed in an attempt to start a new operation, then that operation will be ignored and nothing will be performed. The system must wait for the device to return to the standby mode before normal command operations such as Continuous Array Read can be resumed.

Since the contents of the SRAM buffers cannot be maintained while in the Ultra-Deep Power-Down mode, the SRAM buffers will contain undefined data when the device returns to the standby mode.

Figure 10-4. Exit Ultra-Deep Power-Down

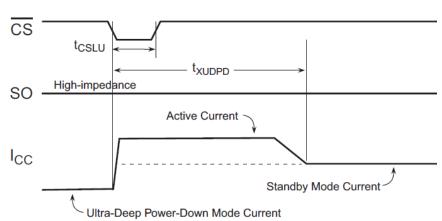

#### AT45DB321E – Freeze Sector Lockdown

#### Freeze Sector Lockdown

The Sector Lockdown command can be permanently disabled, and the current sector lockdown state can be permanently frozen so that no additional sectors can be locked down aside from those already locked down. Any attempts to issue the Sector Lockdown command after the Sector Lockdown State has been frozen will be ignored.

To issue the Freeze Sector Lockdown command, the  $\overline{\text{CS}}$  pin must be asserted and the opcode sequence of 34h, 55h, AAh, and 40h must be clocked into the device. Any additional data clocked into the device will be ignored. When the  $\overline{\text{CS}}$  pin is deasserted, the current sector lockdown state will be permanently frozen within a time of  $t_{\text{LOCK}}$ . In addition, the SLE bit in the Status Register will be permanently reset to a Logic 0 to indicate that the Sector Lockdown command is permanently disabled.

# AT45DB321E – page size re-configuration

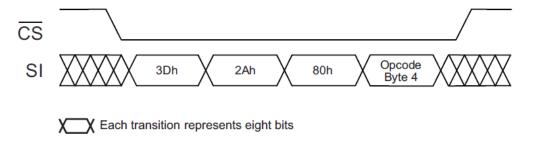

Table 11-1. Buffer and Page Size Configuration Commands

| Command                                   | Byte 1 | Byte 2 | Byte 3 | Byte 4 |

|-------------------------------------------|--------|--------|--------|--------|

| "Power of 2" binary page size (512 bytes) | 3Dh    | 2Ah    | 80h    | A6h    |

| DataFlash page size (528 bytes)           | 3Dh    | 2Ah    | 80h    | A7h    |

Figure 11-1. Buffer and Page Size Configuration

User can reconfigure as needed

#### AT45DB321E – Software Reset

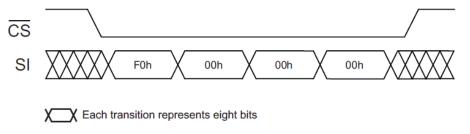

#### **Software Reset**

In some applications, it may be necessary to prematurely terminate a program or erase cycle early rather than wait the hundreds of microseconds or milliseconds necessary for the program or erase operation to complete normally. The Software Reset command allows a program or erase operation in progress to be ended abruptly and returns the device to an idle state.

To perform a Software Reset, the  $\overline{\text{CS}}$  pin must be asserted and a 4-byte command sequence of F0h, 00h, 00h, and 00h must be clocked into the device. Any additional data clocked into the device after the last byte will be ignored. When the  $\overline{\text{CS}}$  pin is deasserted, the program or erase operation currently in progress will be terminated within a time  $t_{\text{SWRST}}$ . Since the program or erase operation may not complete before the device is reset, the contents of the page being programmed or erased cannot be guaranteed to be valid.

The Software Reset command has no effect on the states of the Sector Protection Register, the Sector Lockdown Register, or the buffer and page size configuration. The PS2, PS1, and ES bits of the Status Register, however, will be reset back to their default states. If a Software Reset operation is performed while a sector is erase suspended, the suspend operation will abort and the contents of the page or block being erased in the suspended sector will be left in an undefined state. If a Software Reset is performed while a sector is program suspended, the suspend operation will abort and the contents of the page that was being programmed and subsequently suspended will be undefined. The remaining pages in the sector will retain their previous contents.

The complete 4-byte opcode must be clocked into the device before the  $\overline{CS}$  pin is deasserted, and the  $\overline{CS}$  pin must be deasserted on a byte boundary (multiples of eight bits); otherwise, no reset operation will be performed.

#### AT45DB321E – Low Power Read Mode

#### **Lower Read Current:**

Command 01h:

6mA typ at 1MHz 7mA typ at 15MHz

# AT45DB321E – Program / Erase Suspend - Resume

#### Program/Erase Suspend

In some code and data storage applications, it may not be possible for the system to wait the milliseconds required for the Flash memory to complete a program or erase cycle. The Program/Erase Suspend command allows a program or erase operation in progress to a particular 128KB sector of the main memory array to be suspended so that other device operations can be performed.

Example:

By suspending an erase operation to a particular sector, the system can perform functions such as a program or read operation within a different 128KB sector. Other device operations, such as Read Status Register, can also be performed while a program or erase operation is suspended.

#### Program/Erase Resume

The Program/Erase Resume command allows a suspended program or erase operation to be resumed and continue where it left off.

Note: Please refer to datasheet for the detail

# **DataFlash DataSheets and Samples**

DataFlash® Datasheet:

http://www.adestotech.com/products/serial-flash/dataflash

DataFlash® Sample Request:

http://www.adestotech.com/sample-ordering-information