## **BTA26**

## **Triac Series**

| Parameter                                  | Symbol                              | Value       | Unit | Test condition                               |

|--------------------------------------------|-------------------------------------|-------------|------|----------------------------------------------|

| peak repetitive off-stage voltage          | V <sub>drm</sub> , V <sub>rrm</sub> | 600         | V    | I <sub>D</sub> =0.1mA, I <sub>R</sub> =0.1mA |

| on-state RMS current                       | I <sub>T</sub> (RMS)                | 25          | А    | all conduction angles                        |

| NON repetitive surge peak on-state current | I <sub>TSM</sub>                    | 250         | А    | Tp=10ms, Tj=25 ⁰C                            |

| critical rate of rise on-state current     | dl/dt                               | 50          | A/μs | I <sub>TM</sub> =20A, I <sub>G</sub> =50mA   |

| peak gate current                          | I <sub>GM</sub>                     | 4           | А    | tp=20μs                                      |

| average gate power dissipation             | P <sub>G</sub> (AV)                 | 1           | W    |                                              |

| storage temperature range                  | Tstg                                | -40 to +150 | °C   |                                              |

| operating junction temperature range       | Tj                                  | 125         | °C   |                                              |

## Electrical characteristics (Tj=25°C) unless otherwise specified

| Parameter                               | Symbol           | Value            | Unit | Test condition                                  |

|-----------------------------------------|------------------|------------------|------|-------------------------------------------------|

| gate trigger current                    | I <sub>GT</sub>  | <u>&lt;</u> 50   | mA   | T2+G+ V <sub>D</sub> =12V, I <sub>T</sub> =0.1A |

|                                         |                  | <u>&lt;</u> 50   | mA   | T2+G- V <sub>D</sub> =12V, I <sub>T</sub> =0.1A |

|                                         |                  | <u>&lt;</u> 50   | mA   | T2-G- V <sub>D</sub> =12V, I <sub>T</sub> =0.1A |

|                                         |                  | <u>&lt;</u> 100  | mA   | T2-G+ V <sub>D</sub> =12V, I <sub>T</sub> =0.1A |

| gate trigger voltage                    | V <sub>GT</sub>  | <u>&lt;</u> 1.30 | V    | V <sub>D</sub> =12V, I <sub>T</sub> =0.1A       |

| hold current                            | Ι <sub>Η</sub>   | <u>&lt;</u> 50   | mA   | V <sub>D</sub> =12V, I <sub>T</sub> =0.1A       |

| critical rate of rise off-state voltage | dv/dt            | <u>&gt;</u> 200  | V/µs | V <sub>D</sub> =67%V <sub>DRM</sub>             |

| on-state voltage                        | V <sub>TM</sub>  | <u>&lt;</u> 1.55 | V    | I <sub>T</sub> =35A                             |

| off-state leakage current               | I <sub>DRM</sub> | <u>&lt;</u> 3.00 | mA   | V <sub>D</sub> =V <sub>DRM</sub> ; Tj=125°C     |

| thermal resistance                      | Rth(j-a)         | 50               | °C/W |                                                 |

|                                         | Rth(j-c) AC      | 1.20             |      | Insulated                                       |

## Disclaimer

The product information and the selection guides facilitate selection of the CDIL's Discrete Semiconductor Device(s) best suited for application in you product(s) as per your requirement. It is recommended that you completely review our Data Sheet(s) so as to confirm that the Device(s) meet functionality parameters for your application. The information furnished in the Data Sheet and on the CDIL Web Site/CD are believed to be accurate and reliable. CDIL however, does not assume responsibility for inaccuracies or incomplete information. Furthermore, CDIL does not assume liability whatsoever, arising out o the application or use of any CDIL product; neither does it convey any license under its patent rights nor rights of others. These products are not designed for use in life saving/support appliances or systems. CDIL customers selling these products (either as individual Discrete Semiconductor Devices or incorporated in their end products), in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damage resulting from such sale(s).

CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.

CDIL is a registered Trademark of Continental Device India Limited C-120 Naraina Industrial Area, New Delhi 110 028, India. Telephone + 91-11-2579 6150, 4141 1112 Fax + 91-11-2579 5290, 4141 1119 email@cdil.com www.cdilsemi.com

BTA26 Rev 1 021209E

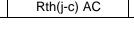

TOP 3

PACKAGE TO-P3

ALL DIMENSIONS ARE IN mm

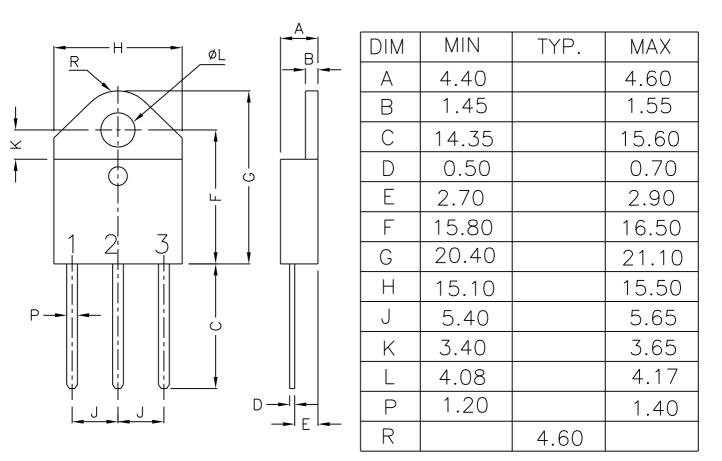

PIN CONFIGURATION

- 1. MAIN TERMINAL 1

- 2. MAIN TERMINAL 2

- 3. GATE