# DEVICE ENGINEERING INCORPORATED

385 East Alamo Drive Chandler, AZ 85225 Phone: (480) 303-0822 Fax: (480) 303-0824 E-mail: admin@deiaz.com

# 700 SERIES 20V BIPOLAR ARRAY FAMILY

## FEATURES

- 20V bipolar analog array family of 9 base chips

- Metal mask customization to stock base wafers yields fast design turnaround

- Small chip size and enhanced complexity, due to advanced, small geometry process

- NPN current gain typically 200, f<sub>T</sub> of 800MHz

- Large NPN with 200 mA of current handling capability

- PNP current gain between 40 and 90,  $f_T$  of 15MHz

- Wide selection of package options

- Design library for low cost tools: SIMetrix, PSPICE, and ICED

- "Kit parts" available for bread-boarding

- Design Manual with dozens of reference function circuits and tutorials

- Turn-key design and layout services available

#### DESCRIPTION

The 700 Series is a semi-custom 20V Bipolar analog and mixed-signal ASIC (Application Specific Integrated Circuit). Customers design their proprietary ASIC's using low-cost commercially available SPICE simulator, layout editor, and free design library. The design manual and library contain dozens of reference design function circuits including comparators, amplifiers, voltage references and regulators, logic gates, and timers.

DEI delivers fast turnaround by applying the customer designed metal interconnect pattern to a stock Series 700 wafer. Once the design is production ready, DEI provides production fabrication and test for timely deliveries of high-quality, fully-tested, proprietary Integrated Circuits.

| Obin Osniss                  | 740 | 744  | 740  | = 40 |      | =0.4 |      | 700   |       |

|------------------------------|-----|------|------|------|------|------|------|-------|-------|

| Chip Series                  | 710 | 711  | 712  | 713  | 723  | 724  | 734  | 736   | 747   |

| Pads                         | 4   | 8    | 17   | 22   | 25   | 30   | 30   | 41    | 48    |

| NPN/PNP Transistors          | 14  | 22   | 27   | 39   | 60   | 80   | 120  | 180   | 280   |

| Schottky NPN Transistors     | 4   | 6    | 10   | 11   | 12   | 16   | 24   | 36    | 56    |

| Large NPN Transistors        | 1   | 1    | 1    | 2    | 3    | 4    | 9    | 5     | 9     |

| Large PNP Transistors        | 0   | 1    | 1    | 2    | 3    | 3    | 6    | 4     | 5     |

| Total Transistors            | 33  | 52   | 66   | 93   | 143  | 183  | 279  | 405   | 630   |

| 750 Ohm Resistors            | 122 | 190  | 210  | 411  | 623  | 895  | 1268 | 1798  | 2487  |

| Total Base Resistance (Ohms) | 91k | 142k | 160k | 310k | 470k | 675k | 950k | 1.35M | 1.87M |

| Base Pinch Resistors         | 2   | 2    | 9    | 9    | 7    | 11   | 8    | 14    | 16    |

| Epi Pinch Resistors          | 1   | 1    | 2    | 2    | 2    | 2    | 2    | 2     | 2     |

| Junction Capacitors          | 1   | 2    | 2    | 4    | 7    | 7    | 9    | 12    | 10    |

| Cross Unders                 | 40  | 60   | 70   | 160  | 200  | 300  | 450  | 650   | 950   |

#### Table 1: 700 Series Base Chip Summary

©2002 Device Engineering Inc

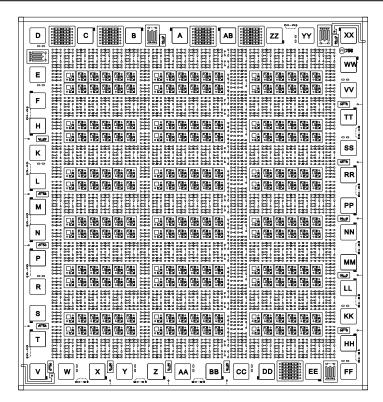

The 700 Series is based on a unique architecture and provides a uniform suite of components with which to implement your design. Each chip provides blocks of 12 transistors, 10 of which are convertible from NPN to PNP, and 2 Schottky NPN transistors positioned at the end of each block. These islands are surrounded by a field of resistors - the high quantity of resistors facilitating easy design.

Islands of transistors are arranged in columns and rows. The number of the chip defines the number of rows and columns; for example, the 712 contains a single column and 2 rows.

Between the bonding pads along the periphery are other devices: large (200mA) NPN transistors, large PNP transistors, pinch (high value) resistors, and junction capacitors. Cross under resistors are provided throughout the structure of the entire chip to ease routing.

There are nine chips in this series forming a smooth progression in size, each being approximately 30% larger in area. The specification of the chips in the 700 Series is shown below. Use this as a guide to determine which device is suitable for the application you have in mind. More information is available in the Design Manual at http://www.deiaz.com/700\_series.htm.

Main Features of the 700 Series

- All devices use an advanced, small geometry (4 micron metal) process resulting in small chip size and enhanced complexity.

- Each of the small transistors can be either NPN or PNP. In the NPN mode the transistor has three separate emitters and two bases, allowing the simple creation of current ratios and multiple use of a single device. The same transistor can also be configured as a single or dual, lateral PNP transistor, ideal for current mirrors and pull up functions.

- The NPN device offers current gain of typically 200 and an f<sub>T</sub> of 800MHz. Each of the three emitters can carry up to 8mA. The PNP lateral device has a gain between 40 and 90 and f<sub>T</sub> of 15MHz. In the Periphery of the chip, the large NPN provides up to 200mA of drive current.

- Components such as resistors and small transistors have identical size and orientation providing optimum matching.

- The main resistor component on the chips is a single value, 7500hms base resistor. Connection in series and parallel of the many resistor sections on the array allows creation of almost any value between about 500hms and 100kohms. Matching between any two resistors is 2%, with 1% matching when 10 or more are used for each value.

Figure 1: 736 Array

## **ELECTRICAL DESCRIPTION**

| Table 2: Absolute Maximum Ratings |

|-----------------------------------|

|-----------------------------------|

| PARAMETER                                    | MIN  | MAX  | UNITS |

|----------------------------------------------|------|------|-------|

| Voltages referenced to Vee (Substrate)       |      |      |       |

| Vcc Supply Voltage                           | -0.3 | +20  | V     |

| Operating Temperature                        |      |      |       |

| Plastic Packages                             | -55  | +85  | °C    |

| Ceramic Packages                             | -55  | +125 |       |

| Storage Temperature                          |      |      |       |

| Plastic Packages                             | -65  | +150 | °C    |

| Ceramic Packages                             | -65  | +150 |       |

| Junction Temperature:                        |      |      |       |

| Tjmax                                        |      | +125 | °C    |

| ESD per JEDEC A114-A Human Body Model        |      | 2000 | V     |

| Lead Soldering Temperature (10 sec duration) |      | 280  | °C    |

| Notes:                                       |      | 1    | 1     |

Stresses above absolute maximum ratings may cause permanent damage to the device.

## Table 3: Recommended Operating Conditions

| PARAMETER             | SYMBOL                | CONDITIONS     |

|-----------------------|-----------------------|----------------|

| Supply Voltage        | VCC -V <sub>SUB</sub> | 0.9 to 20V     |

| Operating Temperature | Тор                   |                |

| Plastic               |                       | -55 to +85 °C  |

| Ceramic               |                       | -55 to +125 °C |

| SYMBOL                                     | PARAMETER                                                  | <b>TEST CONDITIONS</b><br>25°C | MIN | MAX       | UNIT |  |

|--------------------------------------------|------------------------------------------------------------|--------------------------------|-----|-----------|------|--|

|                                            | CMALL N                                                    | 1                              |     |           |      |  |

| BV <sub>CEO</sub>                          | C-E breakdown voltage with base open                       | PN TRANSISTORS<br>Ic = 10uA    | 20  |           | V    |  |

| h <sub>FE</sub>                            | Common emitter current gain                                | Ib = 1uA                       | 100 | 350       | v    |  |

| mpE                                        | Common enniter eurrent gam                                 | Vce = 5V                       | 100 | 550       |      |  |

| $V_{BE}$                                   | B-E diode voltage with collector<br>connected to base      | Ibe = 10uA                     |     | 700<br>10 | mV   |  |

| I <sub>CEO</sub>                           | C-E leakage current with base open                         | Vce = 20V                      |     |           | nA   |  |

| BV <sub>EBO</sub>                          | E-B breakdown voltage (Zener voltage)                      | Ieb = 10uA                     | 5.6 | 6.1       | V    |  |

| RC                                         | Resistance between the two collector contacts              |                                |     | 200       | Ω    |  |

|                                            | SMALL P                                                    | NP TRANSISTORS                 |     |           |      |  |

| BV <sub>CEO</sub>                          | C-E breakdown voltage with base open                       | Ic = 10uA                      | 20  |           | V    |  |

| $h_{\text{FE}}$                            | Common emitter current gain                                | Ib = 1uA                       | 50  | 200       | -    |  |

| -                                          |                                                            | Vce = 5V                       |     |           |      |  |

| I <sub>CEO</sub>                           | C-E leakage current with base open                         | Vce = 20V                      |     | 10        | nA   |  |

|                                            | LARGE N                                                    | PN TRANSISTORS                 |     |           |      |  |

| BV <sub>CEO</sub>                          | C-E breakdown voltage with base open                       | Ic = 10uA                      | 20  |           | V    |  |

| $\mathbf{h}_{\mathrm{FE}}$                 | Common emitter current gain                                | Ib = 2mA $Vce = 5V$            | 40  | 150       | -    |  |

| I <sub>CEO</sub>                           | C-E leakage current with base open                         | Vce = 20V                      |     | 50        | nA   |  |

|                                            |                                                            |                                |     |           |      |  |

|                                            |                                                            | NP TRANSISTORS                 |     |           |      |  |

| BV <sub>CEO</sub>                          | C-E breakdown voltage with base open                       | Ic = 10uA                      | 20  |           | V    |  |

| h <sub>FE</sub>                            | Common emitter current gain                                | Ib = 100uA $Vce = 5V$          | 5   |           | -    |  |

| I <sub>CEO</sub>                           | C-E leakage current with base open                         | Vce = 20V                      |     | 20        | nA   |  |

|                                            | BASE                                                       | E RESISTORS                    |     |           |      |  |

| R <sub>B1</sub>                            | Base Resistor                                              |                                | 600 | 900       | Ω    |  |

| $\Delta$ R <sub>B1</sub> - R <sub>B2</sub> | Difference between two identical resistors, close together |                                |     | tbd       | %    |  |

|                                            | SCHO                                                       | TTKY DIODES                    |     |           |      |  |

| V <sub>F</sub>                             | Forward voltage drop                                       | I = 10uA                       | 300 | 400       | mV   |  |

| Ir                                         | Reverse leakage current                                    | Vr = 20V                       |     | 50        | nA   |  |

|                                            | BASE PI                                                    | NCH RESISTORS                  |     |           |      |  |

| I <sub>RBP</sub>                           | Resistor current at forced 5V.                             | $V_{\text{Res}} = 5V$          | 10  | 150       | uA   |  |

|                                            | EPI PIN                                                    | CH RESISTORS                   |     |           |      |  |

| I <sub>REP</sub>                           | Resistor current at forced 20V.                            | $V_{\text{Res}} = 20 V$        | 1   | 8         | uA   |  |

|                                            | METAL I                                                    | INTERCONNECT                   |     |           |      |  |

| R <sub>MET</sub>                           | Metal interconnect resistance                              | 500 Squares                    |     | 40        | Ω    |  |

|                                            | HINCTH                                                     | ON CAPACITORS                  |     |           |      |  |

| BV <sub>JCAP</sub>                         | Junction capacitor break down voltage                      | Icap = 10uA                    | 9   |           | V    |  |

| Ir                                         | Reverse leakage current                                    | V cap = 5V                     | ,   | 50        | nA   |  |

## **DESIGN TOOLS**

#### **Design Manual**

The **700** Series Bipolar Array Design Manual by Array Design Inc. is available for download at http://www.deiaz.com/. This presents a comprehensive survey of bipolar linear IC design and the specifics of designing with the 700 Series array. It is geared for the engineer contemplating his or her first IC design as well a thorough reference for the experienced Bipolar IC design engineer.

The manual covers the basics of the bipolar technology and the IC design process. It includes descriptions and analysis of dozens of circuit building blocks and reference function circuit designs. Finally, there are tutorials on how to load and use the design tools.

#### **Circuit Design Tools**

The 700 Series device model libraries, schematic symbol libraries, and dozens of function circuit blocks are available for download at http://www.deiaz.com/. These are available for two inexpensive, readily available CAE tools for schematic capture / SPICE circuit simulation. SIMetrix<sup>™</sup> is the recommended tool and is available from Catena Software Ltd. at <u>http://www.catena.uk.com/</u> or can be purchased through DEI directly. The industry standard P-SPICE<sup>™</sup> is available from Cadence at <u>http://www.pspice.com./</u>.

#### **Circuit Layout Tools**

The 700 Series device layout patterns are available for download at http://www.deiaz.com/. These include the graphic templates for all array family members. These GDSII stream files can be used for design on any IC layout tool. Full support for LVS (Layout Vs Schematic) and DRC (Design Rule Check) is provided for the widely used and inexpensive ICED tool available from IC Editors, Inc. at <u>http://www.ic-editors.com/</u> and can be purchased through DEI.

## **Bread Board Kit parts**

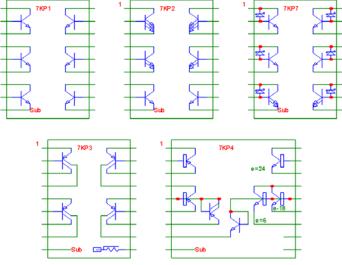

Some designers prefer to breadboard their designs in addition to circuit simulation. This option is supported with a set of kit parts. These are the actual devices on the chips, wired up individually. All kit parts are in 18-pin dual in-line packages. Pin 9 is always the substrate and must be connected to the most negative potential in your circuit.

- 7KP1 contains six identical small NPN transistors with a single emitter connected.

- 7KP2 also contains six small NPN transistors. However, here the upper two transistors have three emitters, the middle ones two and the lower pair one emitter.

- 7KP3 has four small PNP transistors (with each collector brought out separately) and one epi-pinch resistor.

- 7KP4 provides two each of the large NPN and PNP transistors and one each of the small transistors. One of the large NPN transistors has its emitters available in two groups.

- 7KP7 contains six Schottky-clamped NPN transistors (with one of the emitters again permanently connected to the substrate).

Figure 2: 700 Series Kit Parts

## **APPLICATION CIRCUITS**

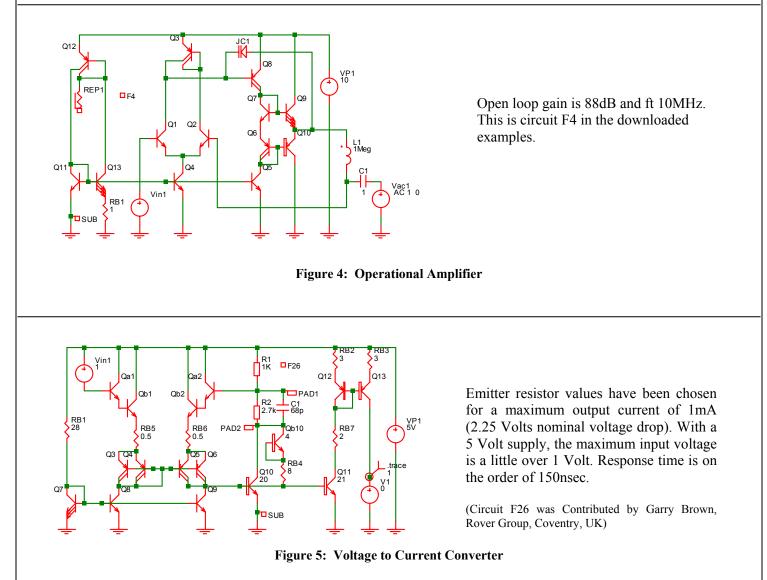

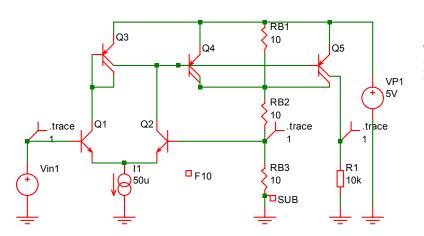

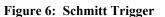

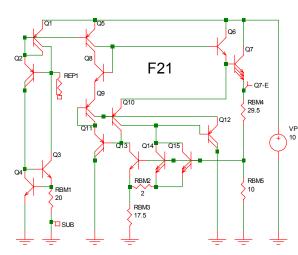

Here are just a few circuits which are thoroughly described in the 700 Series Design Manual and included in the CAE libraries. A listing of available circuits is also available at our website <u>http://www.deiaz.com/700\_series.htm</u> under <u>Circuit Examples</u> and under <u>Design Techniques</u>.

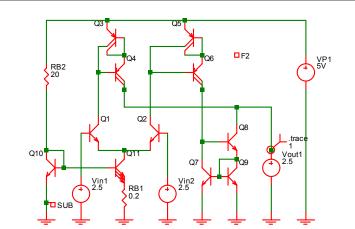

Frequency range is approx. 20MHz (there is some peaking at 9MHz). Change from -55C to 125C is -2dB and the three-sigma variation  $\pm 0.5$ dB. This is circuit F2 in the downloaded examples.

## **APPLICATION CIRCUITS (CON'T)**

The switching points are: Lower: VP x RB3 / (RB1 + RB2 + RB3) Upper: VP x RB3 / (RB2 + RB3)

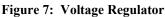

The divider string RB4/RB5 has been set here for 5 Volts, but you can set the ratio for any voltage from 3 to 18 Volts. Output impedance is 0.3 Ohms and the current limits at 90mA at -55C and 120mA at 125C. This is circuit F21 in the downloaded example files.

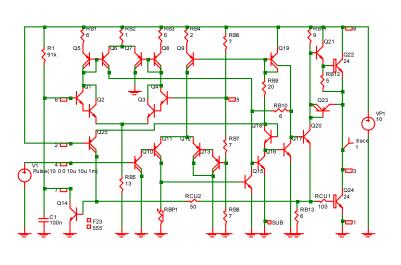

The industry standard 555 timer is available to be implemented into an array. This timer consists of two comparators, a latch, and a discharge transistor. The first comparator is formed by Q1 through Q8 (note that Q1 and Q2, a darlington pair, can fit into the same island – the same can be done with Q3 and Q4). The second comparator is formed by Q10 through Q13. The discharge transistor is Q14, and the rest of the circuit makes up the flip flop and control logic. This is schematic F23 in the downloaded files.

#### Figure 8: 555 Timer

## **PACKAGE OPTIONS**

| Pins                                        | 8 | 14 | 16 | 18 | 20 | 24 | 28 | 40 | 44 | 48 |

|---------------------------------------------|---|----|----|----|----|----|----|----|----|----|

| Plastic                                     |   |    |    |    |    |    |    |    |    |    |

| Dual In-Line (DIP), 300 mil                 | Х | Х  | Х  | Х  | Х  | Х  |    |    |    |    |

| Dual In-Line (DIP), 600 mil                 |   |    |    |    |    | Х  | Х  | X  |    | Х  |

| Small Outline (SOIC), narrow body (150 mil) | Х | Х  | Х  |    |    |    |    |    |    |    |

| Small Outline (SOIC), wide body (300 mil)   |   |    | Х  |    | Х  | Х  | Х  |    |    |    |

| Plastic Leaded Chip Carrier (PLCC)          |   |    |    |    |    |    | Х  |    | Х  |    |

| Ceramic                                     |   |    |    |    |    |    |    |    |    |    |

| Dual In-Line, 300 mil                       | Х |    | Х  |    |    |    |    |    |    |    |

| Dual In-Line, 600 mil                       |   |    |    |    |    | Х  | Х  |    |    |    |

#### Table 5: Standard Package Options (Contact factory for other options)

The 700 Series has been created and is maintained by Array Design Incorporated, San Francisco, CA 94110-5151.

DEI reserves the right to make changes to any products or specifications herein. DEI makes no warranty, representation, or guarantee regarding suitability of its products for any particular purpose.