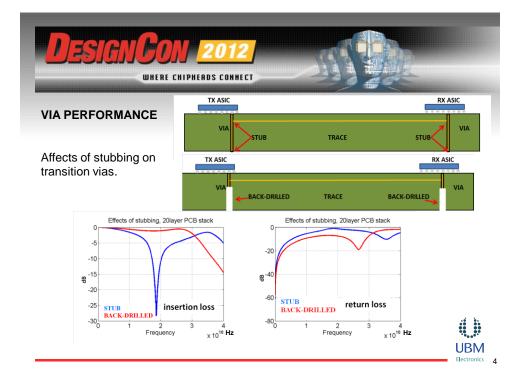

#### **VIA PERFORMANCE**

Impedance mis-match on through vias

#### **VIA PERFORMANCE**

We can summarize via performance within two major categories:

<u>Gross Discontinuities</u>: via stubbing, special pads and other structures causing major resonances.

**Impedance Discontinuities:** pads, stack symmetry, and the number of planes subtly affect impedance.

The primary objective is to make vias seamless and inert in the channel... like the trace it connects.

UBM Electronics 7

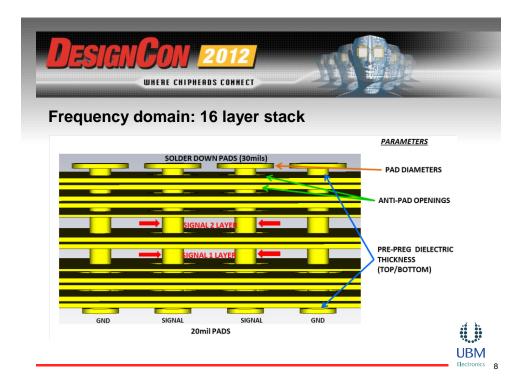

# **Frequency versus Time Domains**

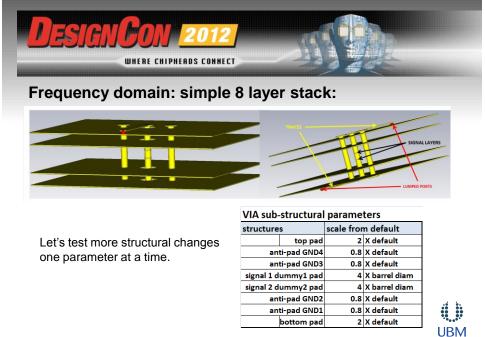

**Exploring Via sub-structures**

Can we use frequency--time or both domains to reveal via sub-structures and their affects so as to help us optimize via performance?

We will explore these domains using a 3D solver.

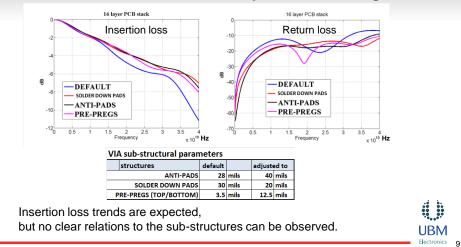

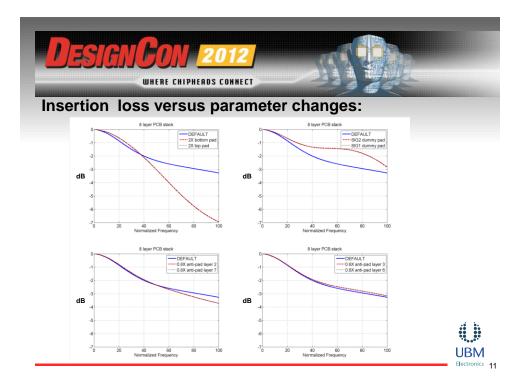

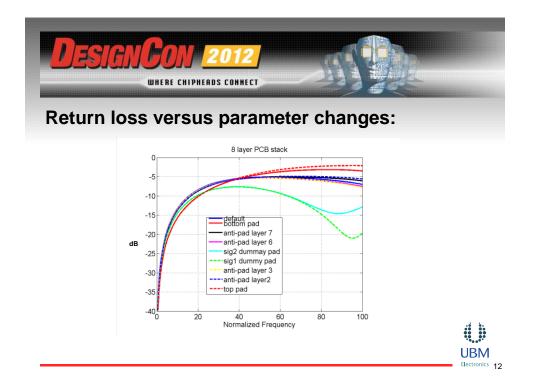

### Insertion and return loss versus parameter changes:

Electronics 10

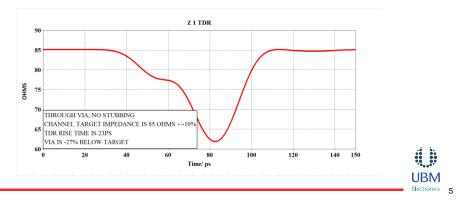

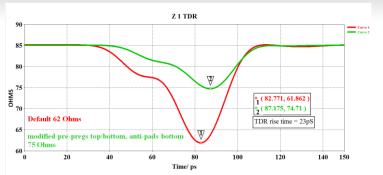

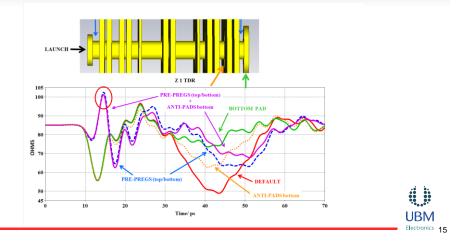

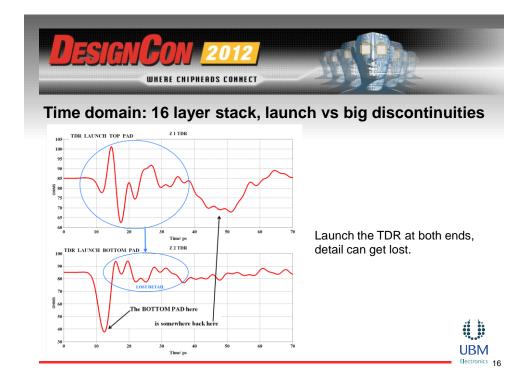

## Time domain: 16 layer stack

Impedance target is 85 ohms, contrasting the default structure against two parameter changes with a Trise of 23ps.

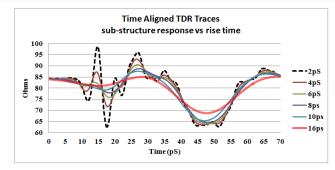

What do we see using faster rise times?

Time domain: 16 layer stack, TDR response vs Trise

Fast Edge Rate TDR (FER) exposes detail. But can we use this?

Time domain: 16 layer stack, 3 parameter changes

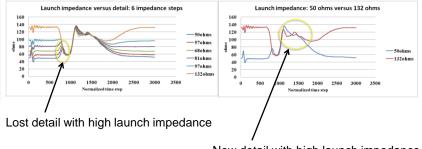

#### Time domain: 8 layer stack, launch impedance also impacts detail

New detail with high launch impedance

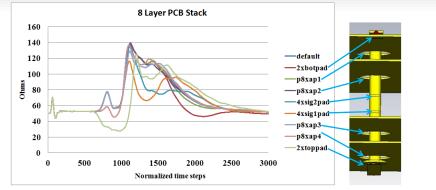

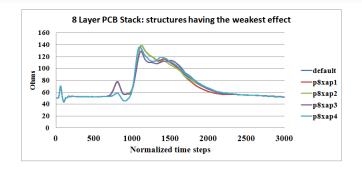

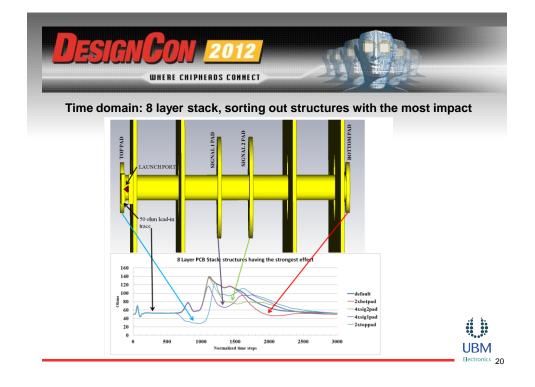

Time domain: 8 layer stack, stepping through 8 parameter changes

A bit messy, let's sort the sub-structures. Our target impedance is 50 ohms.

Time domain: 8 layer stack, sorting out structures with the least impact

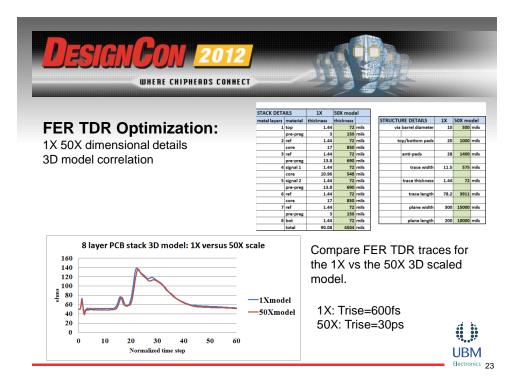

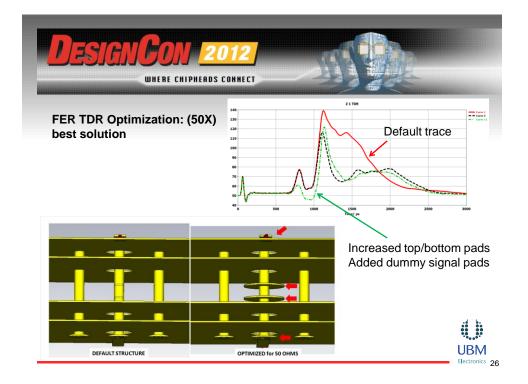

FER TDR Optimization

We need to consider physical measurements using standard TDR equipment. But how are we going to physically generate a 2ps edge rate?

The answer lies in the power of scaling.....

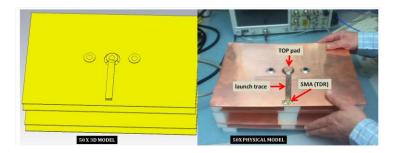

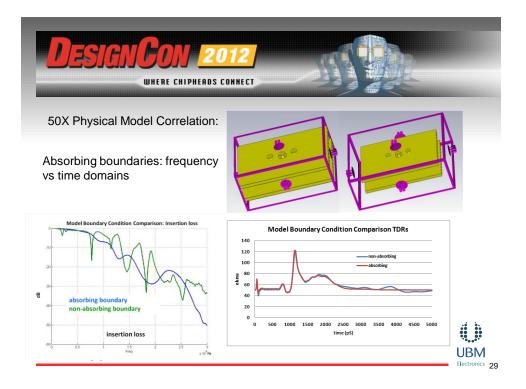

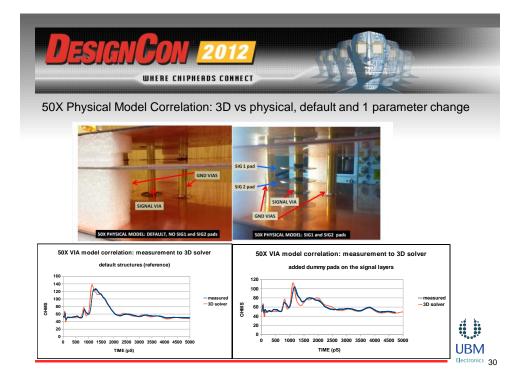

FER TDR Optimization: 50X 3D and Physical models

We will use the simple 8 layer stack for these exercises.

UBM Electronics 21

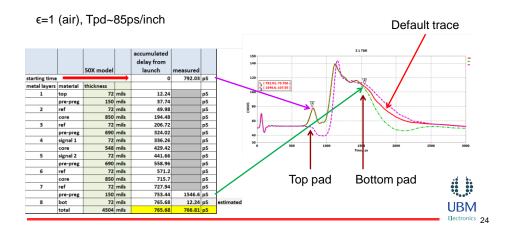

# FER TDR Optimization: (50X) Calibrating the TDR trace

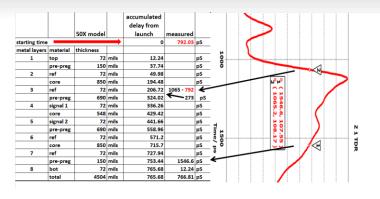

FER TDR Optimization: (50X) locating the large impedance discontinuity

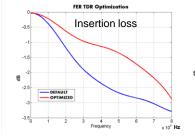

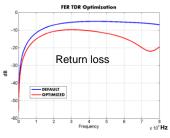

## FER TDR Optimization: (50X) back to the Frequency domain

How well did we do?

~1.2dB improvement @ 400MHz

~5.3db improvement @ 400MHz

Electronics 28

**Conclusions:**

• Frequency domain does not provide substructure detail.

• Time domain using Fast Edge Rate TDR in simulation can reveal significant detail of a via's sub-structure.

• A simple process using this technique was demonstrated.

• The technique has been demonstrated against a 50X physical model.