🔆 Agilent Technologies

Accuracy Improvements of PDN Impedance Measurements in the Low to Middle Frequency Range

Istvan Novak, Sun Microsystems, Burlington, MA Yasuhiro Mori, Agilent Technologies Mike Resso, Agilent Technologies

- Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias and constant AC signal

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

### Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias and constant AC signal

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

# **INTRODUCTION (1/2)**

- Validation of PDN is becoming more critical

- Tighter budgets

- More supply rails with more interaction

- Validation can be better done in the frequency domain

- Supply voltages keep dropping

- Target impedance goes down

- There are multiple challenges in measuring low impedances

# **INTRODUCTION (2/2)**

Challenges in low-impedance measurements

- Except measuring components in fixtures, PDN measurements require cables to reach DUT

- Discontinuities of cable connections to DUT beyond the calibration plane introduce big errors

- Discontinuity error can be reduced by Shunt-through Two-port connection, but it creates a ground loop

- Some PDN components are sensitive to not only DC bias, but also AC bias so that the instrumentation's test signal may alter the result

#### • Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias and constant AC signal

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

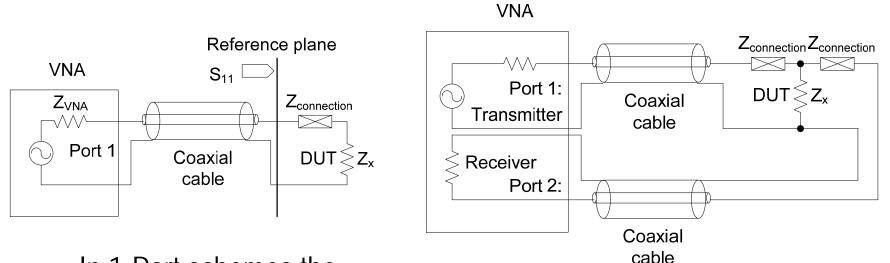

### **THE CABLE-BRAID LOOP ERROR (1)**

#### The problem:

In 1-Port schemes the discontinuity of connection overwhelms the low DUT impedance

In Two-port Shunt-through schemes the effect of discontinuity is largely removed but the two cable braids create a loop.

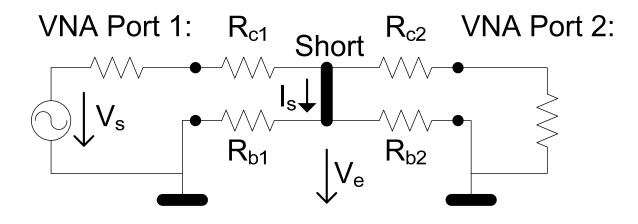

### **THE CABLE-BRAID LOOP ERROR (2)**

The Is test current returning on the braids lifts the lower side of the DUT. Instead of the DUT, we measure the cable braid resistance.

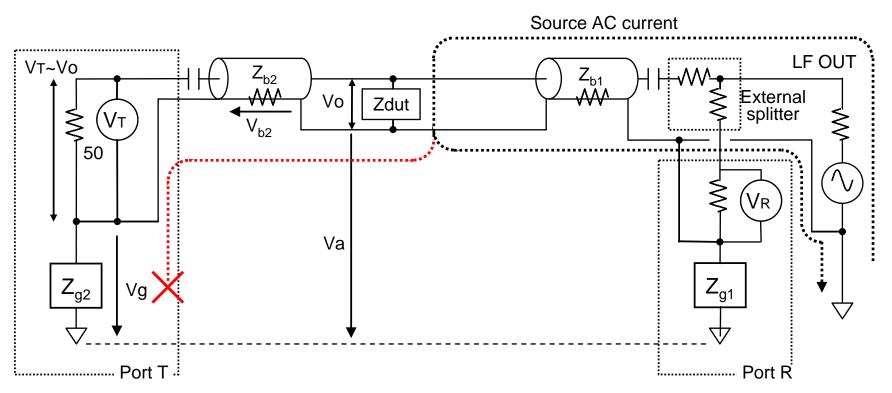

#### REDUCING THE CABLE-BRAID LOOP ERROR

The receivers are floated on  $Z_{g1}$  and  $Z_{g2}$ , which attenuates the error by a factor of  ${\sim}Z_g/Z_b$

DesignCon 2010, Santa Clara, CA. February 4, 2010

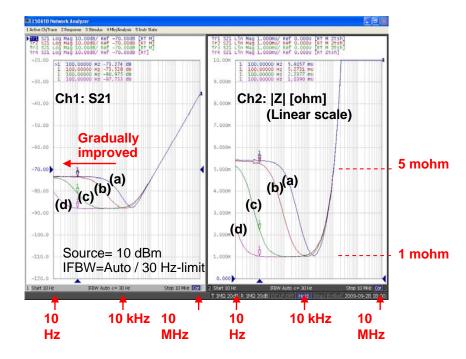

#### REDUCING THE CABLE-BRAID LOOP ERROR

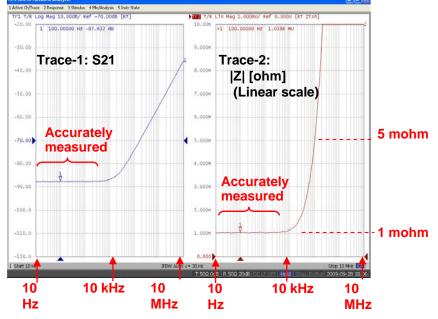

#### S21 and |Z| measurement results with S-parameter test port of E5061B-3L5

- (a) Without core

- (b) A clamp-on-type core is attached to test cable.

- (c) A large toroidal core is attached to test cable.

- (d) Test cable is turned three times around a large toroidal core.

#### S21 and |Z| measurement results with gain-phase test port of E5061B-3L5

Without core or isolation transformer Source=10 dBm (-5 dBm at thru cal) Port-T: ATT=0 dB, Zin=50 ohm, Port-R: ATT=20 dB, Zin=50 ohm

#### • Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias and constant AC signal

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

DesignCon 2010, Santa Clara, CA. February 4, 2010

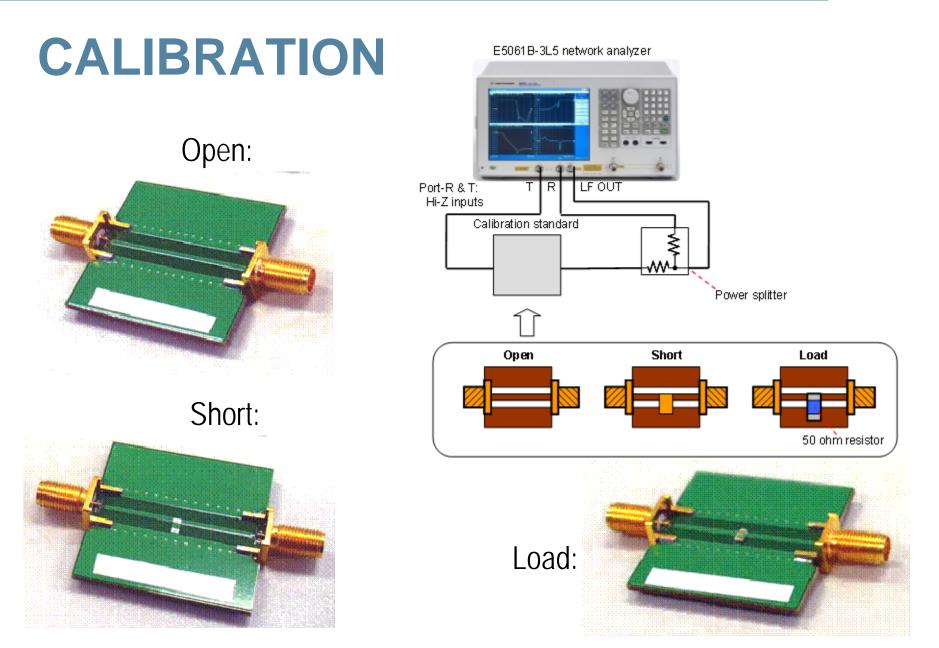

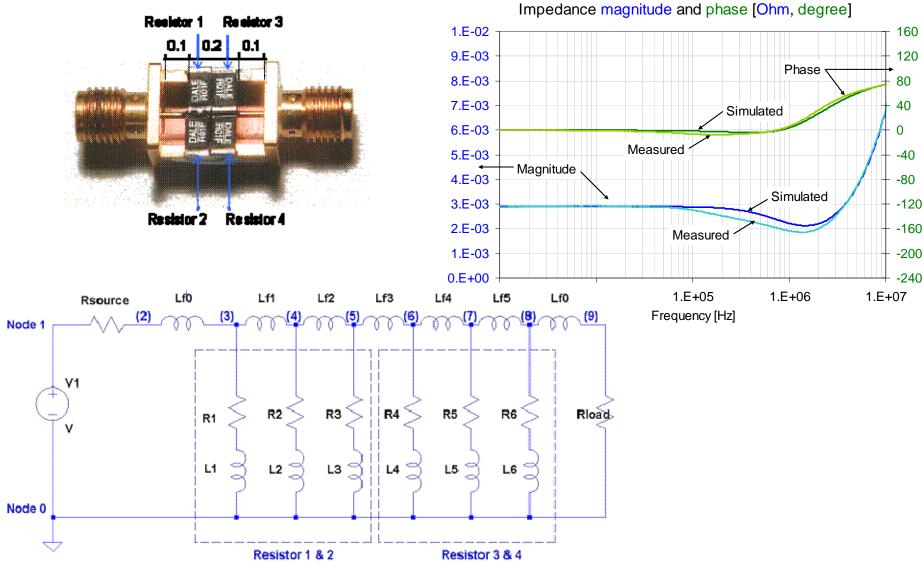

#### HOME-MADE CALIBRATION AND REFERENCE PIECES

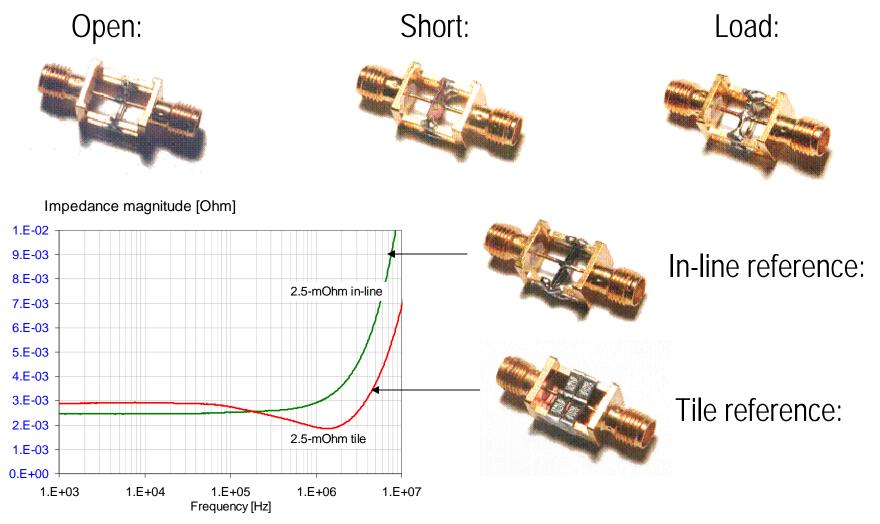

#### **ERROR IN TILE-STYLE REFERENCE PIECE**

DesignCon 2010, Santa Clara, CA. February 4, 2010

- Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias and constant AC signal

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

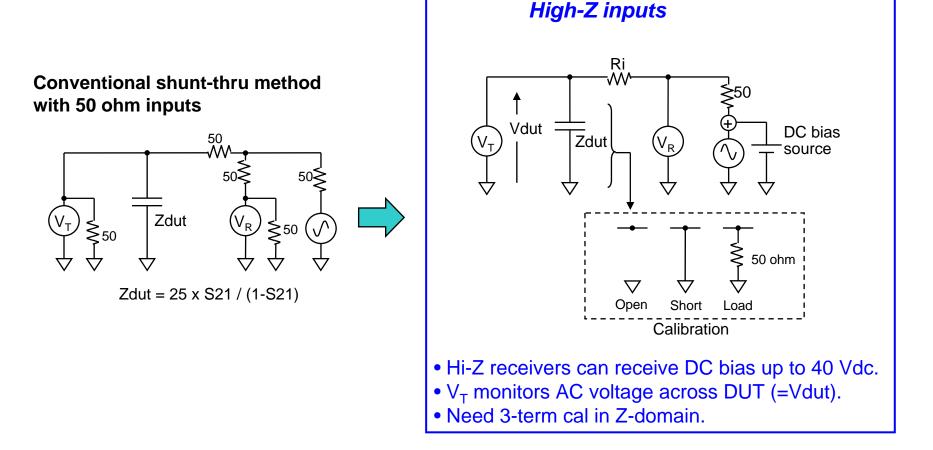

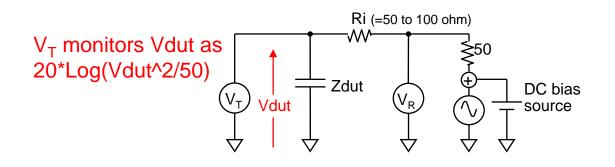

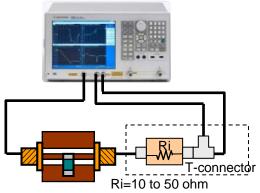

#### MODIFIED SHUNT-THRU METHOD FOR MEASUREMENT WITH DC BIAS & CONSTANT AC

Shunt-thru method with

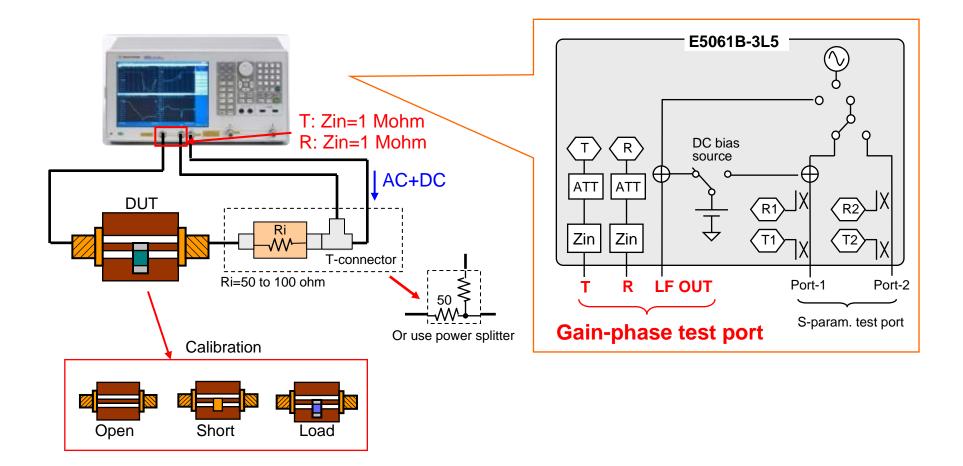

#### MEASUREMENT CONFIGURATION WITH E5061B GAIN-PHASE TEST PORT

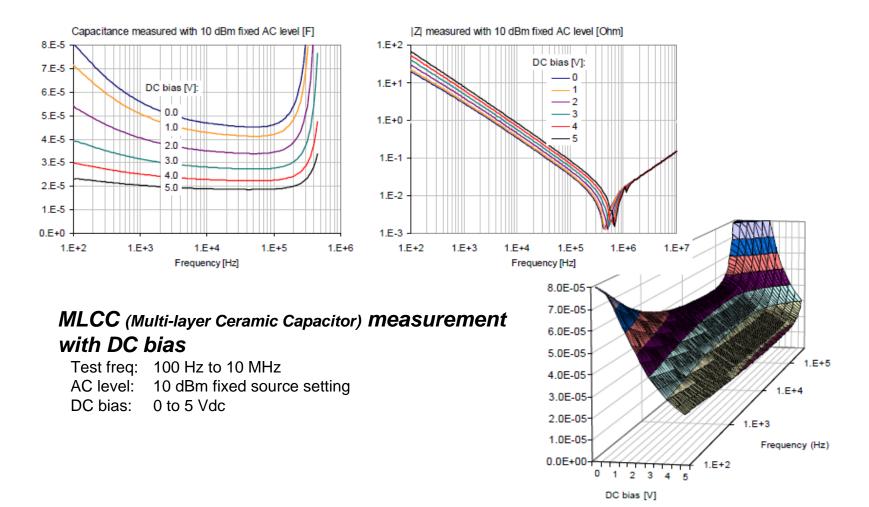

#### **EVALUATING BYPASS CAPACITORS** WITH DC VOLTAGE BIAS

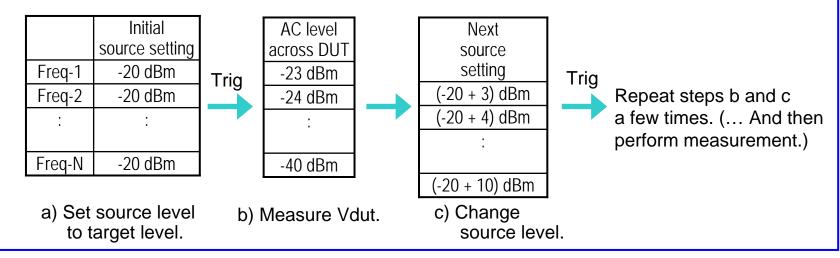

#### **EVALUATING BYPASS CAPACITORS** WITH CONSTANT AC SIGNAL LEVEL (1)

– Pre-measurement for making constant-AC sweep table —

#### **EVALUATING BYPASS CAPACITORS** WITH CONSTANT AC SIGNAL LEVEL (2)

#### (b) Applying constant AC (5 mVrms at DUT) E5061B Network Analyzer Active Ch/Trace 2 Response 3 Stimulus 4 Miz/Analysis 5 Instr State 1 Active Chiltrace 2 Response 3 Structure 4 Mix (Analysis 15 Instr State Tr1 T/R Log Mag 20.00dB/ Ref -20.00dB [F1 2r] Tr1 T/R Log Mag 20.00d8/ Ref -20.00d8 [F1 Zr] -10.000 [F1 2r] 80.00 >1 100.00000 Hz 30.161 dB 60.00 1 2 1.0000000 kHz 10.519 dB 40.00 7 3 10.000000 kHz -9.1416 dB 20.00 4 449.64720 kHz -58.138 dB 100.00000 HZ 32.215 U 1.0000000 kHZ 3.3571 U 10.000000 kHZ 349.07 mU 449.64720 kHZ 1.2391 mU \$0.00 40. 100.00000 Hz 26.620 dB 1.0000000 kHz 9.4750 dB 10.000000 kHz -9.034 dB 398.10717 kHz -51.26 dB 100.00000 Hz 1.0000000 kHz 10.000000 kHz 398.10717 kHz 35.00 2.9768 U 353.41 mU 2.7367 mU 60.00 35.0 Freq Mode Center/Spar 40.00 30.0 -20,000 15.00 List IFBW 20,00 -40.00 10.00 ON 0.000 20.0 -60.00 List Power -80.00 -20.00 15.00 |Z| (ohm) -100.0 ON -10.00 10.00 -40,00 List Delay Cs Real 10.00µU/ Ref 45.00µU [F1 Equ] Tr4 T Log Mag 10.00dB/ Ref -30.00dBr 20.00 -60,00 5.00 85,000 10,00 1.0000000 kHz 47.429 10.000000 kHz 45.628 449.64720 kHz -1.1483 1.0000000 kHz -33.074 dBm 10.000000 kHz -33.076 dBm 449.64720 kHz -70.925 dBm List Time 75.000 -80.0 0.000 0.000 20 Log(|Z|) (dB) OFF 65.00µ -100. Delete 45,0001 -30,000 -120.0 -10.0 35.00µ 25.00µ -40.0 -120.0 A A Tr3 CS Real 10.00µU/ Ref 45.00µU [F1 Equ] Log Mag 10.00d8/ Ref -30.00d8m TC4 T(3) 95.005 20.0 15.00µ -60,00 -70.00 AC level across DUT 5.0000 85.000 10.0 ~80.00 Clour 75.000 0.00 Order Base Segment Table ( =20\*Log (Vdut^2/50) ) Delay Export to CSV File... 65.005 -10.00 Points IFBW Power Span 100 # 55.00p -20.0 106.6700000000 Hz 0.00000000000 H7 20 HZ -28,35 dom Import from CSV File... 113.3400000000 Hz -27.85 d8m 0.00000000000 Hz 20 HZ 45,00ul -30,00 120.0110000000 Hz 0.00000000000 Hz 20 Hz -27.4 dBm -40.00 126,6810000000 Hz 0.00000000000 Hz 30 HZ -26,95 dan Capacitance (F) 133.3520000000 Hz Return 0.00000000000 Hz 30 HZ -26.55 dam 25.00 -50.00 141.2530000000 Hz -26.1 dBm -25.6 dBm 0.00000000000 Hz 30 HZ 150.3970000000 Hz 0.00000000000 Hz 30 Hz 15.005 -60.00 100.00000 Hz 74.834 µU 1.0000000 kHz 53.586 µU 10.000000 kHz 45.090 µU 398.10717 kHz 3.1854 mU 159,5400000000 Hz -25.1 dBm 0.00000000000 Hz 5.000µ -70.0 168,6840000000 HZ 0.00000000000 Hz 30 Hz -24,65 dBm 177.8270000000 Hz 0.00000000000 Hz 30 HZ -24.25 dum 0 5 -5:0000 -80.1 points, 9,5877 sec 2 Start 100 H 0 10 M-tr T 1MQ 20dB R 1MQ 20dB 2009-11-05.0 AC level applied to **Constant-AC sweep** 5 mVrms is constantly DUT is not constant. table created by applied to DUT pre-measurement in this freq range. 201 segments 100 Hz to 10 MHz.

(a) Source level = 10 dBm fixed

DesignCon 2010, Santa Clara, CA. February 4, 2010

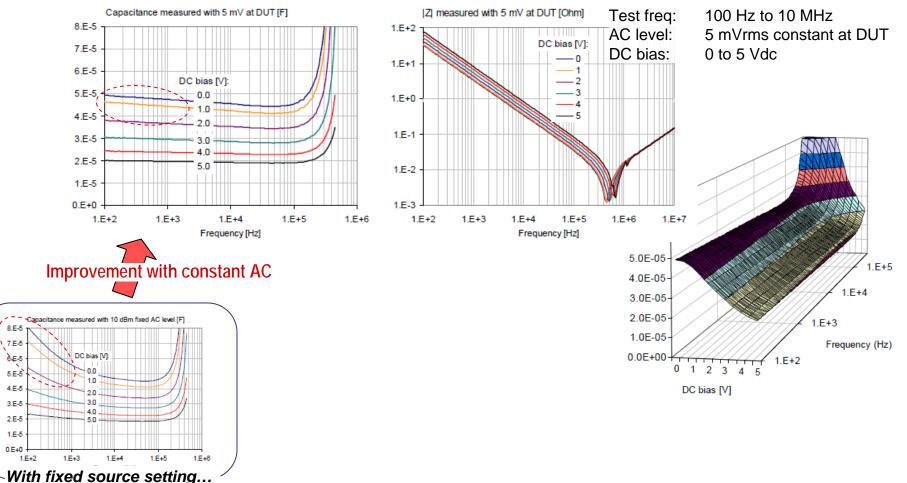

#### **EVALUATING BYPASS CAPACITORS** WITH CONSTANT AC LEVEL AND DC BIAS

#### MLCC measurement with constant AC level and DC bias

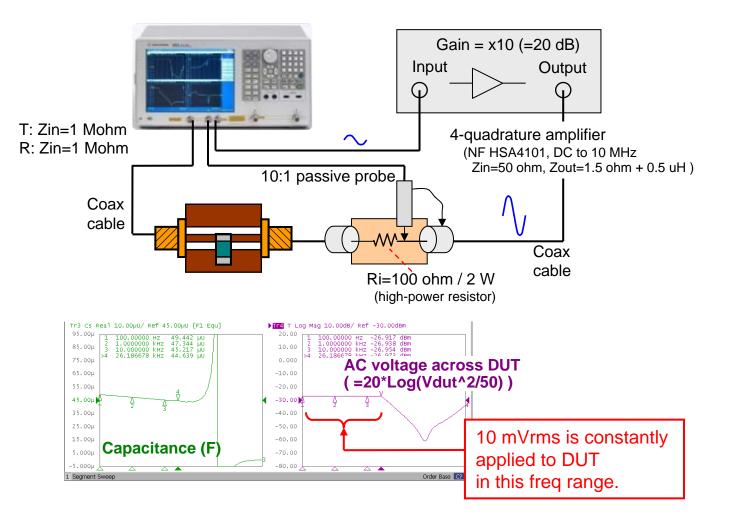

#### **APPLYING HIGHER CONSTANT AC LEVEL**

- Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias

- Evaluating bypass capacitors with constant AC signal level

- Example of MLCC measurement with constant AC level and DC bias

- Applying higher constant AC level

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

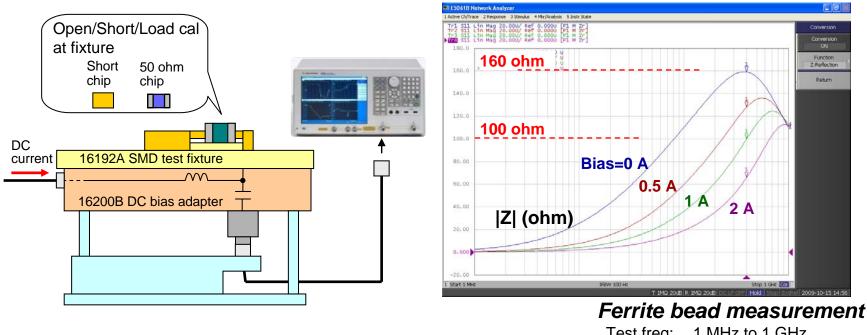

#### **EVALUATING INDUCTORS WITH DC BIAS CURRENT (1)**

#### **1-port reflection method with bias tee** (Test freq: 1 MHz to 1 GHz, DC bias: up to 5 Adc)

Test freq: 1 MHz to 1 GHz DC bias: 0 to 2 Adc

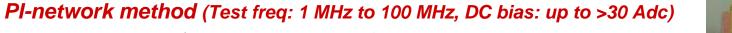

#### **EVALUATING INDUCTORS WITH DC BIAS CURRENT (2)**

- Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias

- Evaluating bypass capacitors with constant AC signal level

- Example of MLCC measurement with constant AC level and DC bias

- Applying higher constant AC level

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

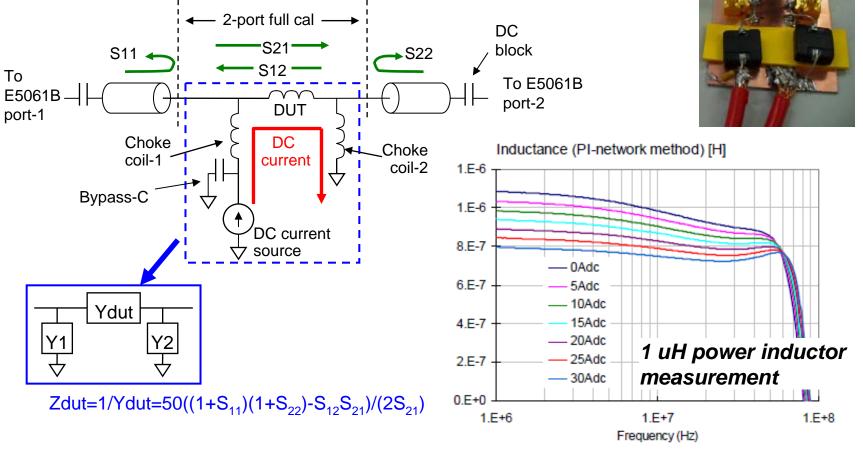

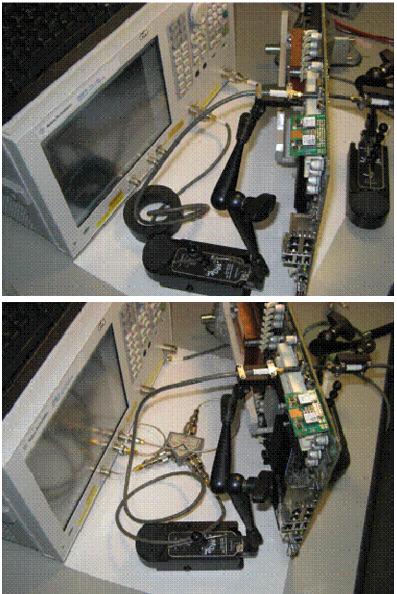

#### **DC-DC CONVERTER MEASUREMENTS (1)**

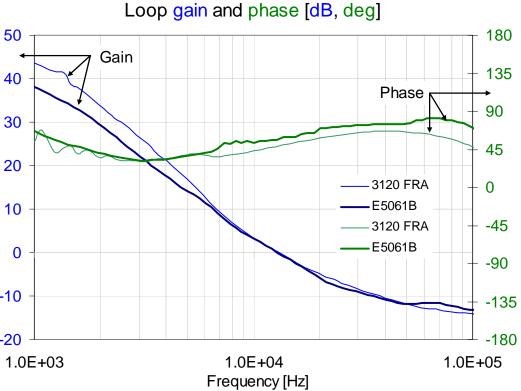

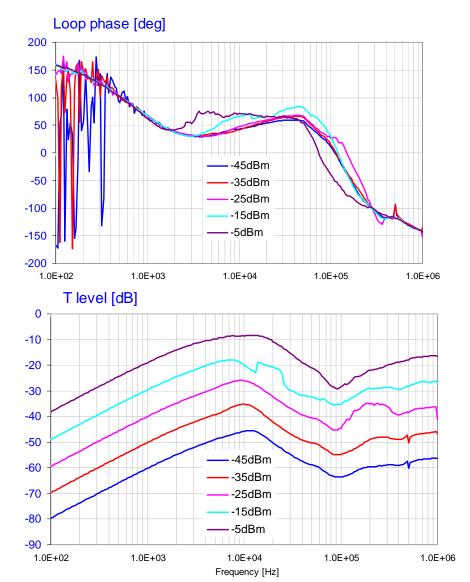

### **DC-DC CONVERTER MEASUREMENTS (2)**

Loop stability measurement of a Linear Technology LTM4617 evaluation module

### **DC-DC CONVERTER MEASUREMENTS (3)**

DesignCon 2010, Santa Clara, CA. February 4, 2010

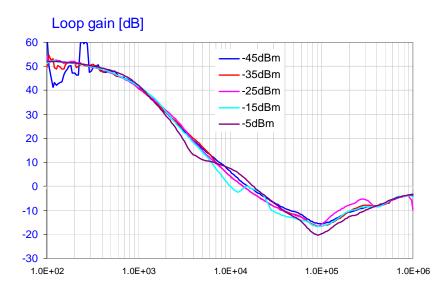

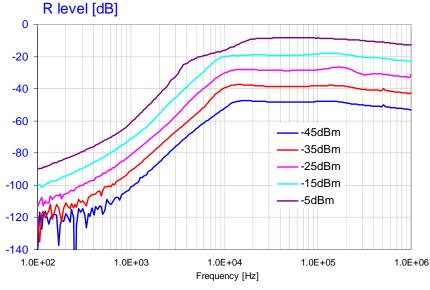

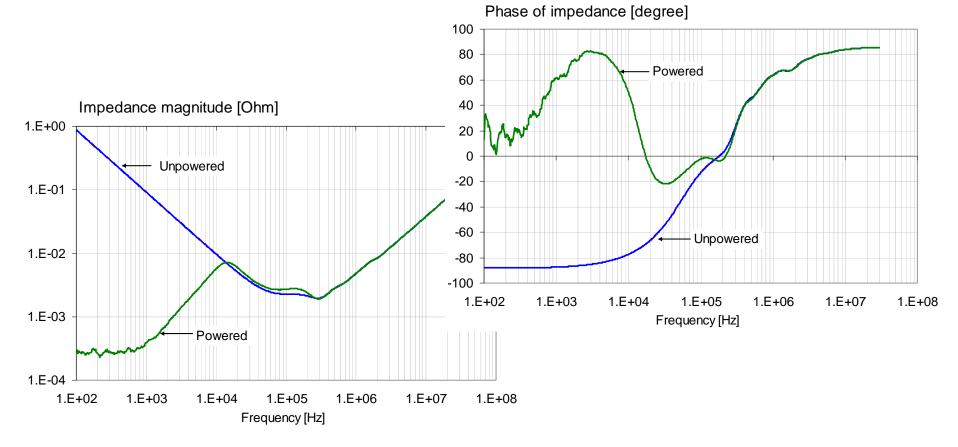

### **DC-DC CONVERTER MEASUREMENTS (4)**

## Output impedance magnitude (on the left) and phase (on the right) of a 15-A 1V DC-DC converter

- Introduction

- Frequency-Domain PDN Measurement Methods

- Handling the cable-braid loop error

- Calibration process and reference pieces

- Evaluating bypass capacitors with DC voltage bias

- Evaluating bypass capacitors with constant AC signal level

- Example of MLCC measurement with constant AC level and DC bias

- Applying higher constant AC level

- Evaluating inductors with DC current bias

- DC-DC converter measurement

- System-level measurements

- Conclusions, acknowledgement

#### **SYSTEM-LEVEL MEASUREMENTS**

Impedance magnitude [Ohm] 1.E+0 1.E-1 1.E-2 1.E-2 1.E-3 1.E-3 1.E-4 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 1.E+09 1.E+10 Frequency [Hz]

DesignCon 2010, Santa Clara, CA. February 4, 2010

### SUMMARY

- Semi-floating ground reference greatly reduces cable-braid error

- MLCCs may exhibit dependence on AC bias as well

- Scripts can help to keep AC level across DUT at user-defined levels

- Gain-phase test port can measure both loop margin and output impedance of DC-DC converters

### ACKNOWLEDGEMENT

The authors wish to express their thanks to Kazuyuki Yagi (Agilent Technologies International Japan) for his valuable comments and suggestions, and to Greg Peters and Shigeki Tanaka (Agilent Technologies) for their support of the project. Special thanks to Steve Ruscak and Natalie Brown (Linear Technology Corporation) for their support and for providing the evaluation module.

### THANK YOU