### VALIDATING SIMULATION MODEL CYCLE TIMES AT SEAGATE TECHNOLOGY

Navdeep S. Grewal Timbur M. Wulf Alvin C. Bruska

Wafer Systems Engineering Seagate Technology One Disc Drive Bloomington, MN 55435, U.S.A.

**KEY WORDS:** Manufacturing Application, Cycle Time Analysis semiconductor Manufacturing, Capacity Planning, Model Validation, and Sensitivity Analysis.

# ABSTRACT

This paper describes the validation of cycle times in a factory simulation model of a new Recording Head Wafer manufacturing facility at Seagate Technology, Minneapolis, MN. The project goals were to determine which factors were causing cycle time deltas between the model and the actual factory, and to add detail to the simulation model to bring cycle times closer to reality. The study found that the most significant contributors to the cycle time delta were number of tools, number of operators, level of operator cross-training, and assumptions about rework, downtime, and equipment dedication.

# 1. INTRODUCTION

A recording head manufacturing facility (fab) is a highly complex manufacturing system in which disc drive read/write heads are fabricated on wafers. Recording head fabs use semiconductor manufacturing processes like microphotolithography, film growth and etching. Today's semiconductor manufacturers face worldwide competition, increasing capital costs and short product life cycles. These issues have combined to make cost effective manufacturing management and shorter fab cycle times important competitive assets. Fab cycle time management also aligns itself to Seagate's Recording Head Operation management's quest to implement Supply Chain Management techniques. Semiconductor manufacturers continuously look at reducing time to market and thereby maintain a competitive market edge. Simulation is an ideal tool for estimating fab cycle times and capacity. The benefits of shorter product cycle times for semiconductor industries have been discussed in detail by many researchers (e.g. Spence and Welter, 1987. Baseman et. al., 1993. Nemoto et. al., 1996). This paper outlines the methods that Seagate used to validate a detailed Jennifer K. Robinson

FabTime Inc. 325M Sharon Park Drive #219 Menlo Park, CA 94025 www.FabTime.com

simulation model and that was used to identify the key factors affecting fab cycle time.

Simulation is ideal for modeling the complex system behavior and other unique attributes of wafer fabs. These attributes include re-entrant process flows, unreliable tools, and elaborate tool dedication schemes. This ability to model complex behavior gives simulation analysis an edge over other type of modeling analysis like queueing models and static spreadsheets (Potti and Mason, 1997). Seagate's Industrial Engineering (I.E.) team uses WWK's Factory Explorer® (FX®) product for simulation. FX® is an integrated software package, capable of cost modeling, capacity analysis, and detailed factory simulation. The software uses an Excel® spreadsheet as the front end for loading data and setting model parameters. FX®'s capacity analysis module calculates the resources required to support the planned schedule while maintaining a maximum userspecified capacity loading on each tool group. This is very helpful in identifying the minimum resource requirements prior to simulation and in creating stable simulation runs. The model can also be loaded with actual tool counts and the pre-simulation capacity analysis used to refine the model.

The wafer fab studied in this project is one of the latest manufacturing facilities commissioned by Seagate. Seagate's I.E. team had developed and applied an integrated static capacity and dynamic simulation analysis methodology for estimating long-term capital equipment needs while achieving targeted cycle times (Grewal *et. al.* 1998). As part of that earlier project, the Seagate I.E. team verified and validated a product ramp phase model. The start up fab model was a simple single product process, low to moderate volume production levels, and no labor constraints. Over time, this model was updated and expanded to account for increased production volumes, additional process flows, express lots, new line yields, etc.

Expansion of a simulation model in this way leads almost inevitably to certain simulation modeling drawbacks, such as getting bogged down with excessive model detail. An increase in model complexity also increases simulation analysis difficulty, especially understanding model behavior

1

and the relationships between model inputs and outputs. See Hood, 1990, Chance *et. al.* 1996, Chance *et. al.* 1999, and Nayani and Mollaghasemi, 1998 for more details on this subject.

When this project commenced, cycle times resulting from the simulation model were significantly shorter than cycle times in the actual factory. This was a problem because it called the validity of the model into question, and made the model less appropriate for planning capital equipment purchases. Therefore, Seagate hired Wright Williams & Kelly to help re-validate the simulation model and to determine which factors were causing cycle time deltas between the model and the actual factory. The project goals were:

- To add detail to the model so that overall model cycle times were within 25% of actual cycle times;

- To add detail to the model so that the list of top cycle time contribution tools from the model matched the list of top cycle time contribution tools in the factory;

- To identify the top factors that contributed to cycle time deltas between the model and reality;

- To identify the insignificant factors for which data is not worth collecting in detail, because they do not significantly affect model cycle time; and

- To prepare a formal verification and validation procedure for subsequent analyses.

# 2. METHODOLOGY

This project consisted of two primary phases of activity – model updating / validation and simulation experiments. The majority of the work consisted of model updating and validation – collecting historical information, entering that information into the model, and comparing the results with actual data. The simulation experiments conducted fell into two categories: experiments to compare the validated model data with the original model data, and experiments to test the sensitivity of the model to other variables.

#### 2.1 Initial Model Verification and Validation

The base simulation model was modified to include up-todate process rework, yield, resource, and average product mix data. Historical equipment downtime data was collected from the maintenance's equipment resource tracking system. The fab loading was then set to the anticipated production volume level over the period of interest. The three main performance measures for verification were: equipment count; equipment utilization by category (e.g. off-line % and busy %) and product cycle time. The base model output reports were analyzed to assess the key system performance measures. Industrial Engineers for the factory performed initial model verification such as checking the model logic, process routes and equipment parameters.

Further, verification was performed by calculating the minimum tool set required by the model with FX®. Then comparing this with the actual toolset. The projected bottlenecks from the model were compared with the known bottlenecks in the factory. For the more heavily loaded tools, the model's capacity usage breakdown (total utilization, busy time, free time, unscheduled down time, etc.) was also compared with actual data from the equipment tracking system. Both the equipment tool count and utilization numbers predicted by the model were quite similar. However, model cycle times, were significantly lower than actual values. Key areas identified for adding model detail were:

- Labor Actual staffing levels, amount of operator cross-training, and verification of work assignments on the floor.

- Product Actual wafer starts by day, actual lot release method, amount of WIP in the system at the start of the analysis, and actual times per step recorded by the manufacturing control system.

- Equipment Batch loading policies, tool/operation dedication strategies, and alternate tools.

- Manufacturing Discipline Batch transfer rules between steps and lot priorities.

# 2.2 Data Validation and Additions to the Model

Specific detail added to the model included the following:

- Actual starts for the past month, as released each day.

- Actual line yields for the past month (instead of planned values).

- Actual tool quantities in place during the past month. The original model was a planning model, and included future tools not qualified for the relevant time period.

- Current process flows. The original model, since it was used for planning, included future process flow changes that had not taken place in the factory. These changes affected which tools were the factory bottlenecks.

- Express lots. The planning model did not include the disruption provided by express lots. They were added for the study.

- Actual operator quantities and work assignments representing two different cross-training assumptions. The previous model had large operator group data but no labor modeling analysis was performed.

- Equipment dedication policies, particularly those leading to a single tool being available to process

© 1999 IEEE. Reprinted, with permission, from Proceedings of the 1999 Winter Simulation Conference, Phoenix, AZ, 2 December 5-8, 1999, 843-849.

certain steps. Other studies have shown such equipment dedication to be a significant cycle time contributor in wafer fabs (Fowler *et. al.* 1997).

• Transport steps between each area, modeled by using a dummy batch tool, with an operator required 100% of the time. For one high traffic density area a dedicated runner was modeled for the transport steps. For all other areas, an operator from the area that the lot was leaving would move it to the next area. Previously, transport steps were not modeled at all. Other studies had shown, however, that the grouping of lots into transport batches can significantly increase cycle time (Domaschke 1998).

### 2.3 Simulation Experiments

Each simulation run was made by pre-loading the model with the actual WIP level of the previous month, and reading in an actual starts file for the next six weeks. All simulations were run for 45 days, with statistics cleared after 15 days (to let the existing WIP clear out). Each experiment was replicated three times. Common random numbers were used to minimize variability across the simulation experiments. All cycle times reported were averaged across the three replications.

# **3. RESULTS**

# 3.1 Number of Operators

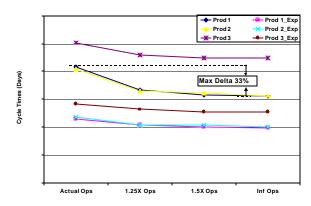

The fab is divided into nine process areas such as Photo, Plating, etc. Fab production provided information on labor deployment within each area. The model was first simulated with the assumption that all operators were cross-trained to run any machine within each area. When the actual number of operators in each group were used, cycle times increased significantly. To quantify this effect, multiple runs were made by increasing the labor force across all the groups by 25% and 50% from the actual number of operators. Figure 1 shows the simulation results with labor being increased from actual number of operators to infinite number of operators (no operator constraint). A significant cycle time reduction was observed when operator count was increased by 25% for all the operator groups. This occurred because the model was slightly unstable with actual number of operators. Labor appears to be one of the most important factors impacting the cycle time for this factory. It was also observed that increasing the number of operators by 50% over the actual quantities yielded only a small additional cycle time reduction, as did running the model without any operator constraints.

Figure 1. Impact of Number of Operators on Model Cycle Time

These results highlight the importance of understanding the impact of operators on factory performance. Work is underway to better understand this behavior and to detail the production support and direct production related work elements for each step.

# 3.2 Level of Operator Cross-Training

Labor modeling was further analyzed by including the operator work assignment for each specific set of tools. In a complex semiconductor-manufacturing environment, level of operator cross-training can have a significant effect on equipment utilization and fab cycle times. At Seagate, although operators were cross-trained to run multiple tools, they frequently were assigned to specific tools and thus were only available for a small number of assigned tools. This process constraint involving tool/operator dedication was analyzed by breaking the operators down into 34 small, specific groups, instead of the previous nine groups.

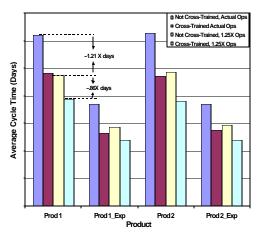

Work assignment details were gathered with production's assistance for each area. The operators were broken down into smaller groups and assigned to service specific tool sets within individual processing areas. A version of the simulation model was prepared with operators assigned to these smaller groups. The number of operators within each group was then increased by 25% to gauge the impact on model cycle times, as illustrated in Figure 2.

Figure 2. Impact of Operator Cross-Training on Model Cycle Time

This chart in Figure 2 shows the average cycle time, by product, for various combinations of the operator groups. The far left bar shows the cycle time with small operator groups (less cross-training), using the actual number within each group. The next bar shows more cross-trained operators, broken into nine groups. The difference in cycle times for the first product was approximately 120% of the theoretical processing time for the first product. The next two bars show the cycle time when the number of operators was increased by 25% in each group. This resulted in an additional cycle time (Robinson, 1998).

The original model did not include operators as a constraint at all. The combined effect of including operator dedication and actual operator quantities was approximately 2X days, where X is the weighted theoretical cycle time across all the processes. Thus operator cross training and number of operators together accounted for a large part of the cycle time difference between the model and reality (Robinson, 1998).

# 3.3 Number of Tools

Number of tools is one of key factors that has a direct impact on model behavior. Running the model with the right tool deployment and qualification information is critical to any simulation analysis. While this seems obvious, it is more difficult in practice than might be expected. When a fab is in a ramp situation, the number of qualified tools changes frequently. Tool specifications and configurations are also in a state of flux due to frequent process changes. This is further compounded by the fact that planners are often using a model designed to reflect the future, when a different set of tools may be available. This was the situation at Seagate when this project commenced. Several tools were modeled as on line when, for example, they were really in qualification or kept on hold by process engineering. Discussions with manufacturing support groups and engineering/ development groups identified a number of anomalies in the simulation model.

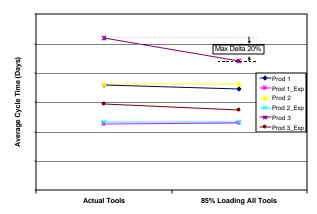

The model was changed to reflect actual tool count and qualification information for the validation time period. In the planning model, because of frequent tool changes, simulation runs had often been made in which FX® would calculate the required number of tools in each group. The assumption used was that each tool group would be loaded to no more than 85% of its maximum possible loading. To better represent the impact of this modeling assumption the simulation results for the updated model were compared against the results of a model using FX®'s estimated tool count (at 85% capacity loading). Figure 3 shows the results of these simulations runs. The cycle time difference was only significant for Product 1, which had a 20% delta. The major cycle time contributor for this product was a batch tool only used by Product 1. It should be noted, however, that at other phases of the ramp, several tools might be loaded at above 85%, in which case an experiment like this would show a much more dramatic effect.

Figure 3. Impact of Actual Vs. Suggested Tools on Model Cycle Time

#### 3.4 Downtime Sensitivity

Recording head manufacturing processes have approximately 400 steps across 100 complex tools with random uptimes. Because the equipment was so new, the initial model was prepared with uptimes either calculated from a small range of data or based on engineering estimates. The model was updated with a new set of MTBF/MTTR, PM and engineering time data gathered from the equipment tracking system database over a longer span of time. The PM and other unscheduled downtimes events are caused by frequent process and equipment specification changes. These parameters accordingly vary from time period to time period.

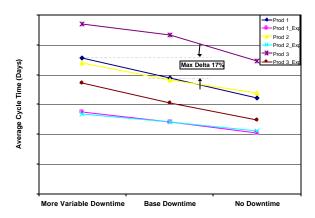

To estimate the impact of downtime variability, an experiment was conducted comparing average cycle time estimates for a model with more variable downtime distributions against the base model and against a model with no downtime. The results are shown in Figure 4. Average cycle times would decrease by approximately 10% if downtime were not modeled at all. They could increase by approximately 7% if more variable downtime distributions were used (e.g. by having downtime events occur half as frequently, but last twice as long). This analysis puts a bound on the maximum change that might be expected in the model from collecting more detailed downtime data.

Figure 4. Impact of Downtime Variability on Model Cycle Times

### 3.5 Rework Sensitivity

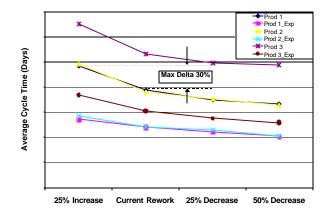

In a semiconductor fab, due to short product life-cycles and increasingly complex processes, maintaining low rework rates is a challenging task. Engineering and manufacturing's mastery of a process is dependent upon the frequency of product turns. Shorter turn-around time means faster learning and process feedback. In a recording head organization, production has a huge rework variance depending upon process maturity. Rework has a significant impact on all product cycle times because of the re-entrant nature of the process. High levels of rework on one product impact others because all processes use the same equipment. This acute sensitivity to rework levels makes this process attribute one of the most critical factors. The impact of this factor was estimated by increasing and decreasing the rework probabilities from the base model assumptions, as shown in Figure 5. Cycle time increased significantly (by up to 30%) when rework probabilities were increased. This indicates that the model is very sensitive to rework assumptions, and implies that more detailed rework data should probably be collected.

Figure 5. Impact of Rework Assumptions on Model Cycle Time

### **3.6 Equipment Dedication**

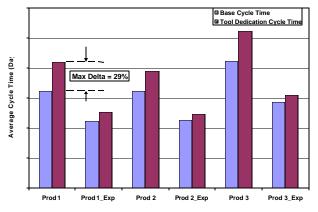

A startup assumption was made that there is no operation/process/tool dedication on the floor. This has changed since these situations arise during the ramping or cutting in of new products. Also, manufacturing operators will dedicate specific tools that produce higher quality for specific operations or steps. This tool/process dedication impedes manufacturing's flexibility to manage WIP and consequently can cause major queue delays and capacity constraints. Although no such major process tool constraints were observed on floor the dedication of certain photo exposure tools for specific operations and products were simulated. Another scenario modeled was operation dedication on large batch vacuum deposition tools that can create WIP bubbles and flow imbalance in the fab. Three scenarios modeled were: Single wafer processing Photo exposure tool/operation dedication, large batch size vacuum deposition tool/operation dedication and a combined model including both the photo exposure tool and the large batch size vacuum tool dedication. The cycle times of all the candidate models were compared against base model without any tool dedication.

Photo exposure tool dedication was modeled by assigning certain operations to specific tools. In the presimulation capacity analysis some of the photo exposure tools became highly loaded (93% Approx.) due to this tool/operation dedication. Also many of the tools in the group were partially loaded. The capacity constraint situation on bottleneck tools was resolved by providing an alternate path through the lower capacity loaded tools. The modeling embellishment on tool dedication of single wafer photo exposure processing tool was significant. The cycle times of the low priority wafers increased on average by 14% (Approx.) across all the products. In comparison the express lot wafers (high-priority lots) were slightly elevated by 4% (Approx.) on average. The modeling analysis of dedication of large batch size vacuum tool proved to be a less significant contributor of cycle time increase.

The photo exposure tool dedication had a greater impact on the wafer fab cycle time because photolithography is one of the most critical process areas since wafer visits these tools multiple times (~25 times approx.), in comparison to the large batch size vacuum deposition tool with 9 visits approx.

The final simulation included combined analysis with the operation dedication for both the Photo Exposure and the large batch size vacuum tool, results are shown in Figure 6. The cycle times increased significantly for regular wafers around 26% approx. average and for priority express lots within range of 8% - 13%. The regular wafers accumulated longer delays due to their lower work priorities and being preempted by the express wafers. This alludes to the effect of manufacturing disciplines on the fab cycle times and system behavior. These results also indicate that the probability of wafer cycle time increasing goes up when several tools are dedicated.

Figure 6: Impact of Tool Dedication on Model Cycle Time.

### **3.7 Less Significant Factors**

Several other sensitivity experiments yielded less significant results. Transport lot size between steps, minimum batch size on a large batch tool, and actual distribution of starts were evaluated. Increasing transport lot size between steps did tend to increase cycle time, but only by a small amount. Increasing the minimum batch size on one of the batch tools increased cycle time for one product by 10%. This cycle time effect is due to increase in queue delay time and was not very large relative to overall cycle times. This may have been because of the small lot sizes used in the Seagate factory. Modelling actual lot releases at the time that they occurred, instead of having releases occur uniformly, increased cycle times only slightly.

### 4. CONCLUSION AND RECOMMENDATIONS

This project was successful in bringing cycle times in the model much closer to actual cycle times during the validation period. When most of the additional detail outlined in Section 2.2 was added, average model cycle times for the main process flow rose to 5% higher than actual cycle times. When small, dedicated operator groups were also added, cycle times became even higher (indicating that some additional effort is required to include more accurate operator data). The top cycle time tools in the resulting model also better matched the industrial engineers' perceptions of top cycle time contributors in the factory.

This study found that the most critical step in validating an on-going model is to make sure that the current assumptions accurately reflect the data that is being validated against. This is no small task when working with a recording head wafer fab in which production is being ramped, and product mix, yields, and rework levels are constantly changing. The Seagate model was particularly sensitive to assumptions about operators, equipment downtime, rework, and equipment dedication. Less obvious in these results, but still believed to be important for this model, was the use of actual, rather than planned, tool quantities.

This study showed in particular the importance of including operators in a model when there is a need for the model to accurately reflect actual cycle time. This is not always the case – many models are used for obtaining relative answers, and do not require that level of detail. However, in Seagate's case, having the model show realistic cycle times was important for gaining the buy-in of the people providing the data. The authors of this study believe that even if operator data is not collected in minute detail, the inclusion of the additional level of resource contention for operators brings cycle times to more realistic levels.

For this Seagate fab, the study identified areas in which it is, and is not, worth collecting more detailed data for future models. The model does not appear to be sensitive to lot transfer size, lot release policy (when the actual starts per day are used, that is), and batching policy. Time will be better spent ensuring that the model has up-to-date operator and tool quantities, and collecting better data concerning rework and equipment dedication policies. Equipment downtime falls somewhere in the middle, and is probably worth continuing to collect in some detail.

One final point is that the majority of the project time was spent collecting data and validating the model. Actually running sensitivity simulation analyses consumed perhaps 20% of the project time. This suggests that in planning other projects, it makes sense to allow as much time as possible for model validation.

# ACKNOWLEDGE MENTS

The authors would like to thank Dr. Frank Chance (Chance Industrial Solutions.), Lydia Purnama (Univ. of Iowa), from Seagate - Eric J Koehler, Orkun Ozturk, Gherense Neguse, Tai N Au, Steven J Hollerung, Daro Diddell and Jeffrey K LaCroix for their help and cooperation.

# REFERENCES

- Baseman, R. J., W. Grey, S. J. Hood, C. A. Kovac, and R. C. Brilla. 1993. Cycle Time Driven Inventory Cost Analysis, *Proceedings of the IBM International Manufacturing Productivity Symposium*, IBM East Fishkill, New York, October 12-15.

- Chance, F., J. K. Robinson, and N. Winter. 1999. Getting To Good Answers: Effective Methods For Validating Complex Models, *Proceedings of the SMOMS Conference*, San Jose, CA.

- Chance, F., J. K. Robinson, and J. W. Fowler. 1996. Supporting Manufacturing with Simulation: Model Design, Development, and Deployment, *Proceedings of the 1996 Winter Simulation Conference*, ed. J.M. Charnes, D. J. Morrice, D. T. Brunner, and J. J. Swain, 114-121.

- Domaschke, J., S. Brown, J. Robinson, and F. Leibl. 1998. Effective Implementation of Cycle Time Reduction Strategies for Semiconductor Back-End Manufacturing, *Proceedings of the 1998 Winter Simulation Conference*, Washington, DC, D. J. Medeiros, E. F. Watson, J. S. Carson, and M. S. Manivannan, eds, 985-992.

- Fowler, J., S. W. Brown, H. Gold, and A. Schoemig. 1997. Measurable Improvements in Cycle-Time-Constrained Capacity, Proceedings of the 1997 IEEE/UCS/SEMI International Symposium on Semiconductor Manufacturing (ISSM).

- Grewal, N. S., A. C. Bruska, T. M. Wulf, and J. K. Robinson. 1998. Integrating Targeted Cycle-Time Reduction Into The Capital Planning Process, *Proceedings of the 1998 Winter Simulation Conference*, Washington, DC, D. J. Medeiros, E. F. Watson, J. S. Carson, and M. S. Manivannan, eds, 1005-1010.

- Hood, S. J. 1990. Detail vs. Simplifying Assumptions for Simulating Semiconductor Manufacturing Lines, Proceedings of the Ninth IEEE International Electronics Manufacturing Technology Symposium, 103-108.

- Nayani, N. and M. Mollaghasemi. 1998. Validation and Verification of the Simulation model of Photolithography Process in Semiconductor Manufacturing, *Proceedings of the 1998 Winter Simulation Conference*, Washington, DC, 1017-1022.

- Nemoto, K., E. Akcali and R. Uzsoy. 1996. Quantifying the Benefits of Cycle Time Reduction in Semiconductor

Wafer Fabrication, *Proceedings of the 1996 IEEE/CPMT International Electronics Manufacturing Technology Symposium*, 130-136.

- Potti, K. and S. J. Mason. 1997. Using Simulation to Improve Semiconductor Manufacturing, Semiconductor International, July, 289-292.

- Robinson, J. K. 1998. Seagate Cycle Time Validation project Report, Seagate and Wright Williams Kelly's internal project report.

- Spence, A. M. and D. J. Welter. 1987. Capacity Planning of a Photolithography Work Cell in a Wafer Manufacturing Line, Proceedings of the IEEE International Conference on Robotics and Automation, Raleigh, NC, 702-708.

# AUTHOR BIOGRAPHIES

**NAVDEEP S. GREWAL** is a Senior Industrial Engineer in the Wafer Systems department at Seagate Technology. He received a B.S. (1991) degree in Industrial Production Engineering from Gulbarga University (India) and an M.S. (1994) from University of Louisville. He is a member of Alpha Pi Mu and I.I.E.

**ALVIN C. BRUSKA** is a Technical Engineering Specialist in the Wafer Systems department at Seagate Technology. Before making a complete circle back to IE, he was a Unit Manager and a Tech Manager at Seagate. Prior to Seagate he was an Industrial Engineer, a Methods Engineer, a supervisor, a Superintendent, a Business Unit Manager and a Plant Manager at Naval Systems Division of FMC Corporation. He holds a B.S. (1968) degree in Mechanical Engineering (Industrial Engineering option) from the University of Minnesota.

**TIMBUR M. WULF** is a Department Manager of Wafer Systems at Seagate Technology. He received his B.S. in Electrical Engineering from Michigan Technological University and his M.B.A. from the College of St. Thomas. He is a member of SEMI.

**JENNIFER K. ROBINSON** is co-founder and chief operating officer of FabTime Inc., a provider of wafer fab cycle time reduction software and services. Previously, she worked as an independent consultant in semiconductor manufacturing. Her clients in that industry have included SEMATECH, Digital Equipment Corporation, Seagate Technology, and Siemens AG. Jennifer holds a B.S. (1989) degree in civil engineering from Duke University and an M.S. (1992) degree in Operations Research from the University of Texas at Austin, and a Ph.D. degree in Industrial Engineering from the University of Massachusetts at Amherst (1998). Her research interests center on factory productivity measurement and improvement..

© 1999 IEEE. Reprinted, with permission, from Proceedings of the 1999 Winter Simulation Conference, Phoenix, AZ, 7 December 5-8, 1999, 843-849.