# Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# **AN-780**

Fairchild Semiconductor Application Note May 1991 Revised February 2004

# Operating ECL from a Single Positive Supply

# Introduction

ECL is normally specified for operation with a negative  $V_{EE}$  power source and a negative  $V_{TT}$  termination supply. This is the optimum operating configuration for ECL but not the only one. Operating ECL from a positive  $V_{CC}$  supply is a practical alternative that is gaining in popularity. Positive referenced ECL, or PECL as it is referred to, has been implemented in various mixed signal ASIC for use in the Video Graphics and Communications fields and is used in clock distribution as well. New single supply translator chips are becoming available to facilitate the interface of PECL logic levels to TTL and back again. Logic designers who strive for maximum speed in a system, now can easily replace sections of TTL logic with ECL and operate in PECL fashion from the common TTL  $V_{CC}$  supply.

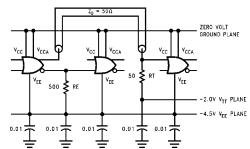

# Standard Negative Supply ECL Operation and Why

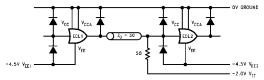

Figure 1 shows F100K logic elements operating in standard negative supply ECL configuration. The most positive potential is the primary voltage reference for ECL operation. Standard ECL input and output levels are therefore negative potentials referenced to the stable passive Ground (0V). The inherent F100K voltage compensation permits stable input and output levels over a broad range of  $V_{\text{EE}}$ 's; i.e., -4.2 to -5.7 VDC for 300 Series F100K. Thus ECL logic operating from a -4.2 V $V_{\text{EE}}$  is compatible to logic operating from a -5.7 V supply assuming both are referenced to a common 0V Ground.

Since ECL logic outputs only source currents that originate from the potential applied to its  $V_{\rm CC}/V_{\rm CCA}$  pins, the use of a OV low impedance and low inductance ground potential is the optimum choice for operation. The use of a continuous copper ground plane as the primary ECL reference is the ideal source for the high frequency transient currents demanded by the logic during switching. Note that despite the ideal nature of a ground plane as the primary ECL reference, when mixing TTL (or other noisy circuitry) into ECL systems, the recommendation is to reference the TTL to a separate ground plane. This is to keep the high transient TTL switching energy out of the primary ECL reference and preserve ECL noise margins.

When F100K ECL output signal interconnection lengths are direct and short enough, transmission line effects may be ignored and then only a RE output biasing resistor is required for logic operation. Please refer to section seven of the "F100K ECL Logic Databook and Design Guide" for a more detailed explanation of transmission line effects and ECL termination techniques. The RE resistor provides

bias to keep the ECL emitter follower output transistor on for both high and low logic states. The RE resistor is normally connected between the ECL output and the most negative potential ( $V_{\rm EE}$ ) thus permitting "single" supply operation.

The  $V_{EE}$  potential will ideally be distributed to the ECL logic from a power plane or bus which has low DC series resistance and low AC impedance. The low AC impedance is essential to supply the transient energy needed during switching. Although the inherent nature of ECL by design is to maintain essentially constant  $I_{EE}$  current even during switching, the charging and discharging of internal and external capacitances and the switching currents in the RE resistors place transient demands on  $V_{EE}$ . The degree to which the user can maintain complementary balance of ECL output loading will greatly influence the nature of the transient  $I_{EE}$  demands.

F100K 300 Series Voltage Levels Specified for Standard Negative V<sub>EE</sub> Supply Operation

| Level           | Min    | Тур    | Max    | Units |

|-----------------|--------|--------|--------|-------|

| V <sub>OH</sub> | -1.025 | -0.955 | -0.87  | VDC   |

| $V_{IH}$        | -1.165 |        | -0.87  | VDC   |

| $V_{BB}$        |        | -1.320 |        | VDC   |

| $V_{IL}$        | -1.83  |        | -1.475 | VDC   |

| V <sub>OL</sub> | -1.83  | -1.705 | -1.62  | VDC   |

$$\begin{split} & \text{Conditions: V}_{CC}/\text{V}_{CCA} = 0.0 \text{ VDC Ground} \\ & \text{V}_{EE} = -4.2 \text{ to } -5.7 \text{ VDC} \\ & \text{RT} = 50\Omega; \text{V}_{TT} = -2.0 \text{ VDC} \end{split}$$

All Levels W.R.T. Ground

FIGURE 1. ECL Standard Operation from a Negative V<sub>EE</sub> Supply

# Standard Negative Supply ECL Operation and Why (Continued)

The usual recommendation for the V $_{\rm EE}$  plane is to bypass every ECL device at its V $_{\rm EE}$  pin with a good RF quality ceramic capacitor. The point at which the RE resistors return to the V $_{\rm EE}$  plane should also be bypassed particularly if it is a single return from a multiple resistor R-PAK. Values from 0.01  $\mu$ F to 0.10  $\mu$ F of the "High K Class II Dielectric" ceramic Z5U grade capacitor are recommended for commercial applications. The lower series inductance inherent in the leadless chip style capacitor is preferred over leaded types for highest frequency performance. The "Mid K Class II Dielectric" ceramic X7R grade capacitor offers acceptable bypass operating characteristics over the broader temperature range of –55°C to +125°C.

Bulk bypassing of the  $V_{EE}$  plane with a 1  $\mu$ F to 10  $\mu$ F is recommended at the point where the  $V_{EE}$  supply connects to the plane. Aluminum or Tantalum Electrolytic capacitors are usually used for bulk bypassing. Miniaturized surface mount Electrolytic capacitors are available for use in high density component applications.

In typical ECL system designs, some inter-connection lengths will exceed the critical values and force the consideration of transmission line effects. The most common high performance and power efficient termination scheme requires the use of a negative 2.0V  $V_{TT}$  termination supply. A single RT resistor in conjunction with the  $V_{TT}$  supply will terminate each output's transmission line in its characteristic impedance and will also provide optimum bias to the ECL output transistor.

The V $_{TT}$  potential will ideally be distributed to the RT terminators from a power plane which has low DC series resistance and low AC impedance. The low AC impedance is essential to supply the transient energy in the termination resistors during switching. Bypassing V $_{TT}$  wherever RT resistors return to the V $_{TT}$  plane is essential to maintaining the low AC impedance of the plane. Capacitor recommendations for bypassing V $_{TT}$  are the same as for V $_{EE}$  above.

The regulation of the  $V_{TT}$  supply is not critical. A variation of  $\pm 5\%$  from nominal causes typically only  $\pm 12$  mV variation in output levels for  $50\Omega$  terminations or  $\pm 7$  mV variation for  $100\Omega$  terminations. Note that in standard ECL configuration, the  $V_{TT}$  supply need only sink current into its negative terminal (single ended  $V_{TT}$  operation with positive terminal grounded).  $V_{TT}$  here will typically be a simple series regulated supply. If the need for single negative supply operation is paramount, a less power efficient Thevenin termination scheme can be used between the  $V_{CC}/V_{CCA}$  and  $V_{EE}$  planes and selective use of series damping in conjunction with RE resistors may also be implemented.

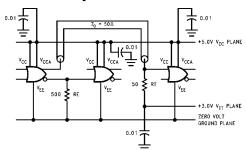

## The PECL Transformation

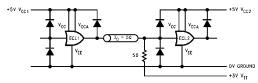

Transforming ECL from negative supply to positive supply operations is conceptually quite easy. Just offset all standard ECL operating potentials by a positive amount equal to an absolute value within the normal  $V_{EE}$  operating range. For F100K 300 Series the normal  $V_{EE}$  range is -4.5 to -5.7 VDC. A 5V offset fits nicely within the range and happens to match the nominal potential for TTL systems. Thus  $V_{EE}$  becomes the 0V ground with  $V_{CC}/V_{CCA}$  offset to +5V and  $V_{TT}$  (if required) offset to +3 VDC. Figure 2 illustrates the transformation (from Figure 1).

F100K 300 Series Voltage Levels Specified for Positive V<sub>CC</sub> Supply [PECL] Operation

| Level           | Min                     | Тур                     | Max                     | Units |

|-----------------|-------------------------|-------------------------|-------------------------|-------|

| V <sub>OH</sub> | V <sub>CC</sub> – 1.025 | V <sub>CC</sub> - 0.955 | V <sub>CC</sub> – 0.87  | VDC   |

| $V_{IH}$        | V <sub>CC</sub> – 1.165 |                         | $V_{CC}-0.87$           | VDC   |

| $V_{BB}$        |                         | V <sub>CC</sub> - 1.320 |                         | VDC   |

| $V_{IL}$        | $V_{CC} - 1.83$         |                         | V <sub>CC</sub> – 1.475 | VDC   |

| $V_{OL}$        | $V_{CC}-1.83$           | V <sub>CC</sub> – 1.705 | V <sub>CC</sub> – 1.62  | VDC   |

Conditions:  $V_{CC}/V_{CCA} = 4.2$  to 5.7 VDC  $V_{EE} = 0.0$ V to Ground RT =  $50\Omega$ ;  $V_{TT} = V_{CC} - 2.0$  VDC All Levels W.R.T. Ground

FIGURE 2. ECL Operation from a Positive V<sub>CC</sub> Supply [PECL]

# **Considerations for PECL Operation**

All the considerations previously discussed for standard operation still apply; i.e., solid isolated and well bypassed reference planes, etc. Some additional considerations apply for PECL operation.

PECL input and output levels are referenced to the active positive  $V_{\rm CC}$  rail that is variable and subject to line and load regulation. PECL level compatibility between sub-systems or systems can be difficult if precise  $V_{\rm CC}$  distribution and accuracy are not maintained throughout. Differential PECL signal transmission and reception between systems may be necessary to ease the  $V_{\rm CC}$  accuracy burden.

This active positive V<sub>CC</sub> potential is the primary reference for PECL levels and the source of PECL switching currents. The distribution of V<sub>CC</sub> to PECL logic is just as important as is the ground distribution to the standard ECL configuration. V<sub>CC</sub> should be delivered from a continuous copper plane with liberal use of high frequency decoupling capacitors at each PECL device's V<sub>CC</sub>/V<sub>CCA</sub> pins.

If TTL or other noisy circuitry is to share the  $V_{CC}$ , a separate powerplane should be provided. TTL switching transients should be isolated from the PECL  $V_{CC}$  plane to preserve PECL noise immunity. Again, differential PECL operation may be warranted for situations where noise control is limited and good common mode noise rejection is required.

The various requirements for output termination and bias previously discussed for standard ECL applies directly to PECL operation. Note that the nominal +3V  $V_{TT}$  supply in PECL mode is required to sink current into its positive ter-

# **Power Supply Sequencing Considerations** (Continued)

minal (single ended  $\dot{V}_{TT}$  operation with negative terminal grounded) from the emitter follower outputs through the RT resistors. A current sinking  $V_{TT}$  supply will be necessary if operated single ended to ground. The  $V_{TT}$  supply should track the  $V_{CC}$  supply keeping a nominal 2V offset to assure optimum biasing of the outputs.

The  $V_{EE}$  for PECL operation is 0V or ground potential and should be distributed from a continuous copper plane in consideration of handling the transients switching currents from the RE bias resistors. Although the PECL  $V_{EE}$  plane will be somewhat tolerant of TTL noise, the recommendation is to isolate TTL transient switching energy in a separate TTL ground plane.

#### **Powerplanes**

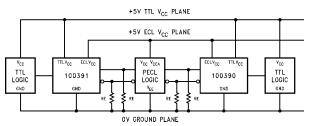

The dedication and organization of powerplanes is essential to successful ECL system design.

Figure 3 illustrates an optimum powerplane implementation for Standard ECL operation on a printed circuit mother board in conjunction with TTL circuitry. Figure 4 shows an optimum powerplane configuration for PECL operation. Note that the dedication and positioning of separate ECL and TTL powerplanes is intended to preserve ECL noise immunity when operating in a mixed signal environment.

| Copper Plane 1 | Signal                      |

|----------------|-----------------------------|

| 2              | TTL 0V Ground               |

| 3              | TTL +5V V <sub>CC</sub>     |

| 4              | Auxiliary GND/Power/Thermal |

| 5              | ECL – 2V V <sub>TT</sub>    |

| 6              | ECL – 4.5V V <sub>EE</sub>  |

| 7              | ECL 0V Ground               |

| 8              | Signal                      |

FIGURE 3. Powerplane Layup for Standard ECL Operation

| Copper Plane 1 | Signal                         |

|----------------|--------------------------------|

| 2              | TTL 0V Ground                  |

| 3              | TTL +5V V <sub>CC</sub>        |

| 4              | Auxiliary GND/Power/Thermal    |

| 5              | ECL + 3V V <sub>TT</sub>       |

| 6              | ECL 0V V <sub>EE</sub> /Ground |

| 7              | ECL + 5V V <sub>CC</sub>       |

| 8              | Signal                         |

FIGURE 4. Powerplane Layup for Positive Referenced ECL

The optimum multiple powerplane approach may not be feasible for some designs. Logic and powerplane partitioning (islands) can be used to control noise when ECL and TTL must share the same powerplane. Figure 5 illustrates the basic concept where areas of a system board are organized by logic type and share the same horizontal powerplane. Low pass filters are usually used to help isolate high frequency signals in sections of the shared plane.

## **Power Supply Sequencing Considerations**

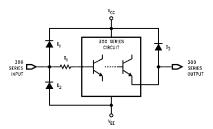

In logic systems where multiple independent power supplies are used, or where two independently powered systems are connected logically, some consideration must be given to supply sequencing. This is particularly true for

ECL/PECL logic due to placement of ESD (Electrostatic Discharge) protection diodes on the inputs and outputs. Figure 6 shows the typical ESD diode placement in a F100K 300 Series device. Figure 7 and Figure 8 illustrate independently powered ECL driver and receiver operating with an independent ground referenced  $V_{TT}$  termination supply.

FIGURE 5. Powerplane and Logic Partitioning

FIGURE 6. F100K 300 Series ESD Diode Circuit

Placement

When the devices (Figure 7) are operated in Standard ECL fashion,  $V_{\text{EE1}}$  may be off while  $V_{\text{EE2}}$  and  $V_{\text{TT}}$  remain on without causing a forward bias potential on any of the ESD diodes. Note that both the true and complement outputs of the ECL1 driver will source logic one current simultaneously to the  $V_{\text{TT}}$  supply when  $V_{\text{EE1}}$  is off while  $V_{\text{TT}}$  remains on. Emitter follower transistors of ECL1 are biased on to a logic high level by the  $V_{\text{TT}}/RT$  even in absence of  $V_{\text{EE1}}.$  The potential for  $V_{\text{TT}}$  current overload exists under these circumstances.

When  $V_{EE2}$  is powered off and  $V_{TT}$  remains on, the low rail input ESD diode of ECL2 (connected to  $V_{EE2}$ ) will forward bias and conduct heavily as  $V_{TT}$  tries to re-power the  $V_{EE2}$  rail. The diode conduction will be limited by the RT resistor and the impedance of the off  $V_{EE2}$  supply in parallel with the ECL2 logic impedance. Although the ESD diode current density rating will typically support this current overstress, the recommendation is to avoid this by insuring that  $V_{EE2}$  and  $V_{TT}$  are ramped together and that  $V_{EE2}$  is never more positive than  $V_{TT}$  by 0.5V.

When the devices (Figure 8) are operated in PECL fashion, there is a very clear forward bias hazard to ESD diodes when supplies are sequenced. If  $V_{CC2}$  is dropped before  $V_{CC1}$ , the positive referenced emitter followers of ECL1 will attempt to re-power up ECL2 through its high rail input ESD diode (connected to  $V_{CC}$ ). The ECL emitter follower outputs are low impedance voltage sources (6 $\Omega$  typical)

# Single Supply Translators—The New Wave Approach (Continued)

and can source an incredible amount of current (greater than 200 mA each output). Thus  $V_{CC2}$  must never be more negative than  $V_{CC1}$  by 1.0V to avoid current overstress.

When  $V_{CC1}$  is powered off and  $V_{TT}$  and  $V_{EE2}$  remain on, the output ESD diode of ECL1 (connected to  $V_{CC1}$ ) will forward bias and conduct heavily as  $V_{TT}$  tries to re-power the  $V_{CC1}$  rail. The diode conduction will be current limited by the RT resistor and the impedance of the off  $V_{CC1}$  supply in parallel with the ECL1 impedance. Although the ESD diode current density rating will typically support this current overstress, the recommendation is to avoid this by insuring that  $V_{TT}$  is never more positive than  $V_{CC1}$  by 0.5V.

If  $V_{CC1}$  and  $V_{CC2}$  are dropped while  $V_{TT}$  remains on, then  $V_{TT}$  tries to re-power both  $V_{CC}$  rails through the output ESD diode of ECL1 and the high rail input ESD diode of ECL2. The forward bias current is limited by the RT resistor and the  $V_{CC1}/V_{CC2}$  supply impedance in parallel with the collective logic impedance. This diode overstress is undesirable and should be avoided by insuring that  $V_{TT}$  is never more positive than  $V_{CC1}$  or  $V_{CC2}$  by more than 0.5V.

If  $V_{TT}$  is dropped before  $V_{CC1}$ , then increased load current can flow through the RT resistor from the emitter follower output of ECL1. Therefore  $V_{TT}$  ramping should be timed with  $V_{CC1}$  and  $V_{CC2}$ .

From the previous discussion, the most critical concern is that no PECL receiver should be powered down if driven directly by a powered up PECL driver without some form of current limiting. The inputs to the receiver must be current limited with external resistors of  $100\Omega$  or greater to be able to survive the overstress caused if  $V_{\rm CC1}$  is ever permitted to be more positive than  $V_{\rm CC2}$  by more than 1.0V. Although the use of current limiting resistors will alter the effective input edge rates and device propagation delays slightly, careful selection and placement of resistors will minimize device performance degradation. Use of surface mounted chip resistors located close to the input is recommended.

FIGURE 7. ESD Diodes in Standard ECL Operation

FIGURE 8. ESD Diodes in PECL Operation

# Dual Supply Translators— The Conventional Approach

Dual supply ECL-to-TTL and TTL-to-ECL IC translators have been in general use for several years. These devices perform the logic level translations between ECL operating from a negative  $V_{\text{EE}}$  supply and TTL operating from a posi-

tive  $V_{CC}$  supply. This approach naturally allows each logic family to operate in their conventional and Data Book specified manner. System designers typically are most comfortable with the dual supply approach. This conventional method permits the use of the most familiar design practice for ECL and should easily yield reliable mixed signal system operation. The growing list of F100K 300 Series Dual Supply Translators, as shown in Figure 9, is testimony to the continued popularity and versatility of this approach.

| Features                                                  | 100324 | 100325        | 100329 | 100395 |

|-----------------------------------------------------------|--------|---------------|--------|--------|

| Data Bits                                                 | 6      | 6             | 8      | 9      |

| ECL-to-TTL                                                |        | Х             | Х      | Х      |

| TTL-to-ECL                                                | Х      |               | Х      |        |

| Flow-Thru                                                 | Х      | Х             |        |        |

| Latched                                                   |        |               |        |        |

| Registered                                                |        |               | Х      | X      |

| ECL Differential Input                                    |        | X<br>(Note 1) |        |        |

| ECL Differential<br>Output                                | Х      |               |        |        |

| ECL Output Drive $(\Omega)$                               | 50     |               | 50     |        |

| ECL Cutoff (Hi Z)                                         |        |               | Х      |        |

| TTL Output Drive (mA) (I <sub>OL</sub> /I <sub>OH</sub> ) |        | 20/–2         | 24/–3  | 64/–15 |

| TTL 3-STATE                                               |        |               | Х      | Х      |

| ECL Control Pins                                          |        |               | Х      | Х      |

| TTL Control Pins                                          | Х      |               |        |        |

| TPD E to T (ns Max)                                       |        | 4.8           | 7.7    | 6.4    |

| TPD T to E (ns Max)                                       | 3.0    |               | 3.9    |        |

| I <sub>EE</sub> (mA Max)                                  | -70    | -37           | -199   | -67    |

| I <sub>EE</sub> (mA Max) (Cutoff)                         |        |               | -199   |        |

| I <sub>CC</sub> (mA Max)                                  | 38     | 65            | 74     | 65     |

Note 1: V<sub>BB</sub> provided for Single-ended Operation

FIGURE 9. Table of F100K 300 Series Dual Supply Translators

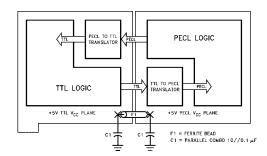

## Single Supply Translators— The New Wave Approach

Single Supply Translators that allow PECL-to-TTL or TTL-to-PECL interfaces are a recent addition to the F100K 300 Series ECL family. Development of these devices is motivated by the need for a convenient technique by which higher performance ECL logic can be integrated into existing TTL systems containing a single positive supply. These devices should also provide a vehicle for new lower cost designs of mixed signal single supply systems.

Figure 10 describes three such devices being offered in the F100K 300 Series family. The popularity of PECL operation is expected to grow significantly as designers become more familiar with the technique. As interest and usage of Single Supply Translators increase, the family of this type of device can be expected to expand.

A simple illustration of the ease with which the Single Supply Translator can accomplish the interface from TTL to PECL and back to TTL is shown in Figure 11. Note that the translator devices have on chip  $V_{CC}$  partitions that facilitate the use of dual powerplanes for the preservation of ECL

# **Single Supply Translators—The New Wave Approach** (Continued) noise immunity. Differential operation on the PECL side of noise immunity. A V<sub>BB</sub> reference voltage

the translator is recommended to be used to maximize

noise immunity. A V<sub>BB</sub> reference voltage output is provided on the 100390 device to facilitate single ended operation.

| Features                                                  | 100390     | 100391 |

|-----------------------------------------------------------|------------|--------|

| Data Bits                                                 | 6          | 6      |

| ECL-to-TTL                                                | Х          |        |

| TTL-to-ECL                                                |            | Х      |

| CMOS-to-ECL                                               |            |        |

| ECL Differential Input                                    | X (Note 2) |        |

| ECL Differential Output                                   |            | Х      |

| ECL Output Drive (Ω)                                      |            | 50     |

| ECL Cutoff (Hi Z)                                         |            |        |

| TTL Output Drive (mA) (I <sub>OL</sub> /I <sub>OH</sub> ) | 24/–3      |        |

| TTL 3-STATE                                               | Х          |        |

| TTL Control Pins                                          | Х          | Х      |

| CMOS Control Pins                                         |            |        |

| TPD E to T (ns Max)                                       | 6.4        |        |

| TPD T to E (ns Max)                                       |            | 1.7    |

| TPD C to E (ns Max)                                       |            |        |

| I <sub>EE</sub> (mA Max) (Cutoff)                         |            |        |

| I <sub>CC</sub> (mA Max)                                  | 48         | 60     |

Note 2: V<sub>BB</sub> provided for Single-ended Operation

FIGURE 10. Table of F100K 300 Series Single Supply Translators

FIGURE 11. Use of Single Supply Translators

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

# LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

# **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative