## Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

## AN-5047

Fairchild Semiconductor Application Note August 2002 Revised August 2002

# **Live Insertion Using Low Voltage Differential Signaling**

#### **Abstract**

Supporting live insertion or hot swapping is important in certain applications such as the ones used in telecommunications systems. These applications require maintenance, upgrades, and repairs to be conducted without shutting down the system or causing disruptions to traffic on the backplane. Inserting and removing cards on a backplane is a capability often required for maximizing system uptime. This paper will discuss how Low Voltage Differential Signaling (LVDS) technology supports live insertion for multidrop applications and hardware considerations to minimize the effects inserted cards have on a backplane.

## LVDS in Multi-Drop Configuration

Multi-drop configurations, which connect multiple receivers to a single driver, are possible with LVDS provided the transmission distance is short and stub lengths are kept as short as possible to preserve signal integrity. This configuration may be useful in data and clock distribution applications. A single termination resistor (matching the characteristic impedance) at the receiver inputs furthest away from the driver is all that is needed for achieving signal integrity.

## Power-Off High Impedance Bus Pins

Fairchild's LVDS drivers and receivers incorporate high impedance bus pins, which limit the power-off input current ( $I_{OFF}$  and  $I_{IOFF}$ ) to a maximum of  $\pm 20\mu A$ . This feature is useful in applications that employ more than one receiver, which are powered from local power supplies. If the power

is turned off to a receiver card, inputs (I<sub>IOFF</sub>) will be in high impedance and not load down the line. With the driver powered off and receiver on, driver outputs will be high impedance and LVDS receiver outputs will lock in a high state failsafe condition to avoid oscillation.

In point-to-point applications which is ideal for LVDS, with the driver powered down and receiver active, communication will cease and the receiver will go into a failsafe condition. With the driver active and receiver powered down, the high impedance bus pins will prevent any damage by limiting the current and not cause a latch-up condition on the receiver inputs.

To determine if a device supports power-off high impedance bus pins refer to the features list in the device datasheet and the receiver power-off input,  $I_{\rm IOFF}$  and the driver power-off output current parameter,  $I_{\rm OFF}$ .

#### **Live Insertion Test Set-Up**

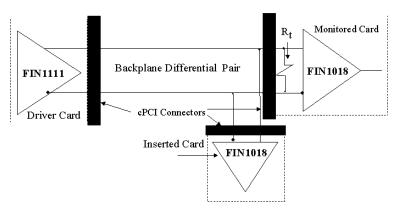

To evaluate and demonstrate live insertion capability of LVDS, lab testing done in Fairchild's EnSigna Lab has shown zero errors while plugging in cards to an active bus. A system card which had Fairchild's FIN1111 clock driver connecting to two load cards each having Fairchild's FIN1018 LVDS receivers on a backplane with a differential pair was used. The R+/R- of one load card was monitored, which had the termination resistor and the second load card was inserted. LVDS will not work without the terminating resistor, which is placed on the card rather than the backplane for optimum signal integrity. Figure 1 illustrates the multi-drop configuration used for the live insertion performance plot.

FIGURE 1. Multi-Drop Configuration for Live Insertion Testing

## Live Insertion Test Set-Up (Continued)

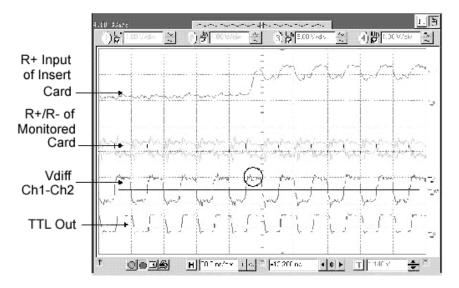

Screen capture of following channels included:

CH1: R+ Input of monitored card CH2: R- Input of monitored card CH3: TTL output of the monitored card

CH4: R+ of the inserted card

F3 : Math waveform (CH1 - CH2), Vdiff

FIGURE 2. Live Insertion Performance Plot

The results shown in Figure 2 illustrate effective isolation during a live insertion event. The highlighted portion of the differential (Vdiff) signal shows a distortion at the point the card is inserted. The disturbance is minimal resulting in noise margin of  $\sim\!\!350\text{mV}$  from the zero crossing pint of the differential signal. Channel 3 is the TTL output of the monitored card which is not impacted by the insertion of a second card and data is asserted once the inserted card gets powered up.

#### **Hardware Considerations**

Upon insertion of a card into a live backplane, assuming the occurrence of abnormalities on the signals is common on both signals, data should not be impacted. This is due to the fact that the deferential lines equally load the active line once asserted and any glitch seen as a common-mode modulation will be ignored by LVDS receivers.

Pin staggering within the card connector should be adopted as well for proper biasing of the devices and establish the highest level of isolation during live insertion. Asserting the ground, data and  $V_{CC}$  pins in the following sequence should be implemented with the power pin being the shortest pin and the data pins being the next shorter pins:

### Space for diagram?

- Ground Pin: Discharge path for any built up charge on the card.

- 2. I/O Data Pins: With no power the pins are high impedance, minimizing loading in the live bus.

- 3. V<sub>CC</sub> Pins: Last pin to assert for highest level of isolation

## Summary

In multi-drop applications, maintaining operation during the removal and insertion of cards is a requirement to minimize system downtime. LVDS devices that support power-off high impedance features should be considered for the system design. This feature will insure error free operation of the bus even when one or more receiver cards are not powered. The performance plot in Figure 2 illustrates no data disruptions or errors on the bus during a live insertion of a card. Along with the power-off high impedance feature of LVDS drivers and receivers, pin staggering on the edge connector of the card should be adopted for the highest level of isolation during live insertion events.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative