Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lange of the applicatio customer's to unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the

# **AN-4179** High Voltage D2pak Package, PCB Layout Guide

## Introduction

The new surface mountable high-voltage HV D2pak offers improved clearance and creepage voltage, versus the standard D2pak, for higher operating voltages, or operation in suboptimal environmental conditions. The innovative package upgrade is cost effective and can often be mounted to an existing PCB layout with little or no PCB modification.

The new HV D2pak improves the performance of the existing D2pak in many applications by overcoming many inherent limitations of the existing package. These limitations include:

- When the operating environment for an electronic component is contaminated with foreign material (dust), or moisture, the standard D2pak clearance and creepage can be insufficient to meet established safety and operating standards. This becomes especially relevant with operating voltages or standards above a few hundred volts.

- Based upon established practices, the pin-to-pin spacing of a standard D2pak is adequate for 800 V, or so. If higher voltages are required, the spacing of the pins must be increased or insulated in some manner. One way to do this is to remove the package center pin. This increases the voltage creepage and voltage clearance of the package and in turn increases the operating voltage of the part both externally and internally.

Removing the center pin, versus rearranging the pin spacing or adding additional plastic to the package, allows all of the existing handling and package placement equipment to be used without modification.

The distance from the package pins on the back of the standard D2pak to the metal of the heat tab on the back side of the package limits the creepage voltage. To overcome this, the heat tab is partially covered with plastic on the HV D2pak. This was carefully done so as to not affect the ability to solder the tab in a standard process.

#### **Overview of D2pak Packages**

Figure 1 and Figure 2 show the standard D2pak and the modified HV D2pak.

#### **Example: PCB Layout Spacing & Clearances**

To achieve the high operating voltages made possible by the new HV D2pak, the PCB layout must have the correct spacing and clearances.

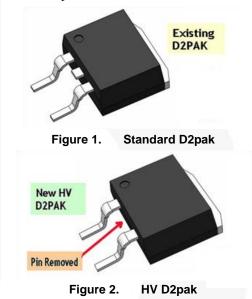

The Test Coupon in Figure 3 has several problems that limit the maximum operating voltage to less than the 1500 V rating of the attached BJT (FJBE2150D). To fully realize the potential of the BJT, the PCB must have the following:

- The spacing of the square pins going to the tester must be greater than 96 mils (1500/15.7) measured between the PCB square pin holes. What is shown is too small. The spacing needs to be increased or the traces and thru holes need to be painted with HV Corona Dope on both sides of the PCB to avoid arcing. Small surface arcing on the PCB could potentially damage the part and PCB.

- The center pin on the package layout must be removed from between the emitter and base and placed well to the right or left of the base and emitter pins or on the back of the PCB.

#### AN-4179

#### Note:

1. The HV D2pak has no center pin and improved clearances on the back side. The collector of the package is connected to the heat tab internally.

#### "Creepage & Clearance"

From various sources on the Internet and in the references found in the Reference section of the document, this can be defined as the following.

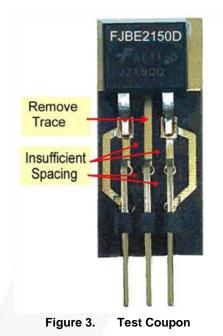

Creepage Distance: Creepage is the shortest path between two conductive parts on an insulator measured along the surface of the insulator. A proper and adequate creepage distance protects against tracking. Tracking is a process that produces a partially conducting path of localized deterioration on the surface of an insulating material as a result of the electric discharges on or close to an insulation surface. The degree of tracking required depends on two major factors: the comparative tracking index (CTI) of the material and the degree of pollution in the environment. Used for electrical insulating materials, the CTI provides a numerical value of the voltage that will cause failure by tracking during standard testing. IEC 112 [1] provides a fuller explanation of tracking and CTI. Tracking that damages the insulating material normally occurs because of one or more of the following reasons:

- Humidity in the atmosphere.

- Presence of contamination.

- Corrosive chemicals.

- Altitude at which equipment is to be operated.

**Clearance Distance:** Clearance is the shortest distance between two conductive parts (or between a conductive part and the bonding surface of the equipment) measured through air. Clearance distance helps prevent dielectric breakdown between electrodes caused by the ionization of air. The dielectric breakdown level is further influenced by relative humidity, temperature, and degree of pollution in the environment.

How much spacing is needed in high voltage circuits and setups? The general guideline in common use is to allow 7,500 to 10,000 volts, dc per inch in air; or 7.5 to 10 volts per 0.001 inches. These voltages will typically be lower over the surface of a material due to surface contaminants, moisture and/or the nature of the material.

# **Working Voltages**

Internet and document research defines Working Voltages as follows:

• A working voltage is the highest voltage to which the insulation under consideration is (or can be) subjected to when the equipment is operating at its rated voltage under normal use conditions.

The appropriate creepage and clearance values can be determined from the figures provided in the relevant tables in EN 60950.2 [2]. Values must sometimes be calculated. The following factors must be considered: determination of working voltages, pollution degree of the environment, and the over-voltage category of the equipment's power source.

When measuring working voltages, it is important to measure both peak and root-mean-square (rms) voltages. The peak value is used to determine the clearance, and the rms value is used to calculate creepage.

### **Requirements for HV Spacing?**

There is no absolute limit per-se' on HV spacing. The electronics industry has used TO-220 packages to 1600 V for many years. Although color TV manufacturers ended up requiring special packages with extended creepage and clearance (TO-3PF, etc.), manufacturers also use painted on insulating materials such as HV Corona Dope to gain added protection. As mentioned, a common rule of thumb in the industry for the TO-220 is to limit it to 800 V. This is considered a good number for reliable operation with reasonable allowances for contamination and moisture.

In order to better understand industry voltage ratings, opto coupler applications were also considered along with TO-

#### AN-4179

220 spacing. The entire industry sells opto isolators with 5 KV and 320 mil spacing that consistently passes hipot testing and actual use. The opto coupler ratings indicate the voltage withstanding levels that is acceptable <u>in practice</u> on a PCB board while providing a basis for the commonly used 800 volts rating.

- 1. If 320 mils (0.320 inches) is the spacing for an opto rated at 5 KV peak, then the allowable spacing must be 15.7 V per 1 mil (0.001 inch) (5000/320= 15.7 V) for creepage and clearance.

- 2. Since a TO-220 has a 0.050 clearance, this equals 785 V (15.7 \* 50). This seems to agree with the industry rule of thumb of around 800 volts.

Opto Couplers, are rated for peak, not continuous voltage. They can also be a safety issue if they isolate the power line from the power supply output. The operating environment for an opto must be fairly clean and low in moisture. Given enough contaminants and moisture, it will arc over and may cause damage as well as potentially starting a fire

Conversely, BJTs or FETs seldom provide power-line isolation so safety is less of an issue. Nevertheless, reliability is important, so operating voltages should be kept below 800 V for the TO-220 or D2pak packages unless special care is taken such as potting, or the use of an insulating coating. If higher voltages are needed, the HV D2pak should be used. The HV D2pak is rated for 2500 volts.

# Typical Creepage and Clearance Distances for different Packages Types

The following data is taken from Fairchild and other manufacturer's package specifications, and actual measurements performed by the author. These clearances and creepage numbers are for general information purposes and to aid comparison between various packages. Some of the information may be redundant.

- 8 pin DIP controller (Fairchild Integrated Green-Mode Controllers): Dip pin-pin spacing ~0.04 inches (1 mm); Across package spacing: 0.340

- TO-220, 3 pin package: pin to pin ~ 0.05"

- D2PAK with center pin: ~ 0.04 clearance, 0.04 creepage distance

- D2PAK with no center pin: ~ 0.2 clearance, 0.2 creepage distance

- DPAK with center pin: ~ 0.056 clearance, 0.056 creepage distance

- DPAK with no center pin: ~ 0.135 clearance , 0.135 creepage distance

- TO3PF with Plastic added for HV: ~ 0.130 clearance, 0.230 creepage distance

- TO246 with Plastic added for HV: ~ 0.130 clearance, 0.250 creepage distance

- 8 Pin DIP Opto: ~ 0.300 clearance, 0.340 creepage distance

- TOP-242 (Drain, startup): 0.070" clearance, 0.070" creepage distance

- STMicro Package: ~ 0.155" clearance, ~0.42" creepage distance (notch in package)

- HV D2pak: ~0.252 inches of creepage and clearance distance

#### Notes:

- 1. The HV D2pak has the center pin removed as well as plastic added to the rear of the package to achieve a creepage and clearance spacing of 0.252 inches (6.40 mm).

- The maximum voltage spec for the package is 2500 volts to allow for internal clearances and insulation breakdown limitations. If the 15.7 volt per mil rule of thumb was used without regard for internal limitations, or issues such as the environmental cleanliness, the creepage and clearance voltage would be 3956 volts.

## HV D2pak PCB Layout

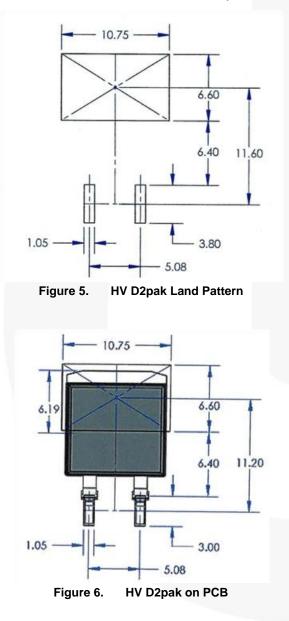

The HV D2pak package can work with existing PCB layouts up to 800 V, or so, without changes. For maximum operating voltages, the layout must be modified as shown in Figure 5 and Figure 6. As indicated, the modified creepage and clearance is ~ 6.40 mm, or 252 mils. This results in a roughly 3x operating voltage increase to around 2500 volts. Figure 5 shows the increased separation distance between the pin lands and the tab mount. Figure 6 shows the HV D2pak when mounted on the modified PCB layout.

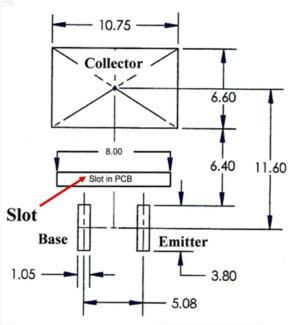

#### Improving the Layout

Adding a slot in the PCB between the base and emitter pads and the collector pad, as shown in Figure 7, can significantly increase the creepage distance and operating voltage for the PCB and BJT. This can be especially important where surface contamination and/or moisture could be present. There is no magic number as to the length or width of the slot. The slot should be long enough to add the desired creepage path length across the PCB surface to raise the creepage breakdown voltage sufficiently for the particular application. The larger the slot width, the less likely contaminates will form across the slot. The slot must be open to be effective.

Additional protection from the effects of moisture and dirt could be obtained by painting HV Corona Dope, or some other suitable insulation, on the completed PCB assembly.

Figure 7. BJT Landing Pattern with Slot (Top View)

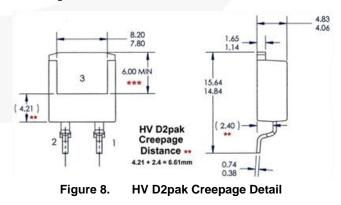

## HV D2pak Creepage

Apart from removing the center pin, creepage was increased in the HV D2pak by reducing the size of the heat tab (terminal 3, Figure 8) on the back side of the package. The HV D2pak tab was reduced in size compared to the standard D2pak and partially covered with plastic to increase the creepage distance and operating voltage. Refer to **\*\*** and **\*\*\*** in Figure 8.

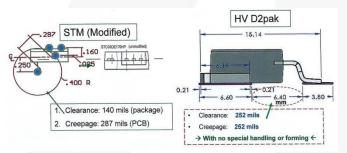

## HV D2pak PCB Layout vs. STMicro Package

As noted previously, it is important to maintain proper creepage and clearance on a PCB layout to avoid voltage breakdown and potential failure of the application.

Figure 9 compares a HV STM part with the HV D2pak. The STM package is difficult to mount on a PCB while maintaining adequate creepage and clearance performance. The withstanding voltage can be dramatically improved by using specialized lead forming and vertical mounting. Both of these modifications add cost and additional processing steps. Lead-forming introduces the potential for component damage thus reducing reliability. Vertical mounting introduces spacing issues in addition to reducing the amount of vibration the arrangement can withstand. Vertical mounting also requires special provision for any required heat sinking. The HV D2pak requires no special forming or handling, and can be directly mounted on the PCB which can provide heat sinking and overall improved reliability.

Figure 9. STM Package vs. HV D2pak

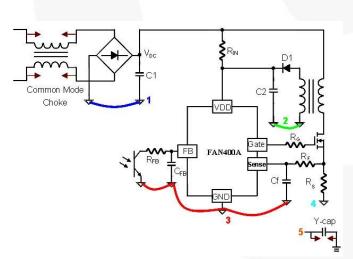

Figure 10. SMPS PCB Layout

### **General PCB SMPS Layout Guide**

High-frequency switching current / voltage make printed circuit board layout a very important design issue. Good PCB layout minimizes excessive EMI, helps the power supply survive during surge/ESD tests, and can improve reliability.

Application Note, AN-400A, located at <u>Fairchildsemi.com</u> provides additional details, when laying out a PCB for switch-mode power supplies.

**Guidelines**: For better EMI performance and reduced line frequency ripples, the output bridge rectifier should be connected to capacitor C1 first, then to the switching circuits, *see Figure 10*.

- The high-frequency current loop is in C1 transformer – MOSFET – Rs – C1. The area enclosed by this current loop should be as small as possible. Keep the traces (especially 4 to 1) short, direct, and wide. Highvoltage traces related to the drain of the MOSFET and RCD snubber should be kept far away from the control circuits to prevent unnecessary interference. If a heatsink is used for the MOSFET, connect this heat-sink to ground.

- As indicated by path 3, the ground of control circuits should be connected first, then other circuitry.

- As indicated by path 2, the area enclosed by transformer auxiliary windings, D1, and C2 should also be kept small. Place C2 close to controller FAN400C for good decoupling.

Two suggestions with different pros and cons for ground connections are recommended.

- GND 3 → 2 → 4 → 1: This arrangement could avoid common impedance interference for the sense signal.

- GND 3 → 2 → 1 → 4: This could be better for ESD tests where the earth ground is not available on the power supply. Regarding the ESD discharge path, the charges go from secondary, through the transformer stray capacitance, to GND2 first. Then the charges go from GND2 to GND 1 and back to the mains. It should be noted that control circuits should not be placed on the discharge path. Single point connection of common mode chokes can decrease high-frequency impedance and increase ESD immunity.

- Should a Y-cap be required between primary and secondary, connect the cap to the positive terminal of C1 (V<sub>DC</sub>). If this Y-cap is connected to primary GND, it should be connected to the negative terminal of C1 (GND1) directly. Point discharge of this Y-cap also helps for ESD. However, the creepage between these two pointed ends should be at least 5 mm according to safety requirements.

#### APPLICATION NOTE

## References

- [1] IEC 112:1979, "Method for Determining the Comparative and the Proof Tracking Indices of Solid Insulating Material under Moist Conditions," International Electrotechnical Commission, Brussels.

- [2] BS EN 60950:2000, "Safety of Information Technology Equipment," British Standards Institute (BSI), United Kingdom.

- [3] IEC 60664:1980 "Insulation Co-ordination within Low-Voltage Systems Including Clearances and Creepage Distances for Equipment," International Electrotechnical Commission, Brussels.

- [4] BS EN 61010-1:1990, "Safety Requirements for Electrical Equipment for Measurement, Control, and Laboratory Use, Part 1: General Requirements," BSI, United Kingdom.

- [5] Calculating Creepage and Clearance Early Avoids Design Problems Later by Homi Ahmadi

- [6] AN-400A, Low-Power Green-Mode PWM Flyback Power Controller without secondary feedback, Fairchild Semiconductor Inc.

- [7] High Voltage Spacing, Evan Mayerhoff, High Voltage Connection, Inc.

- [8] Calculating Spacing between PCB Traces for Various Voltage Levels http://www.smps.us/pcbtracespacing.html

# **Industry Standards**

- 1. IPC-2221A, Generic Standard on Printed Board Design, addresses spacing in sections 6.3 and 10.1.4, along with table 6-1.

- 2. UL 61010A-1, Electrical Equipment For Laboratory Use; Part 1: General Requirements

- 3. UL 61010B-1, Electrical Equipment For Measurement, Control, and Laboratory Use. Part 1: General Requirements. See Annex C - Measurement of CLEARANCES and CREEPAGE DISTANCES, Annex D - Parts between which insulation requirements are specified (see 6.4 and 6.5.2)

- 4. UL 60950, Safety of Information Technology Equipment

# **Related Datasheets**

FAN400A - Low-Power Green-Mode PWM Flyback Power Controller without Secondary Feedback

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC