## PCIe-SIO4BX2 Hardware User's Manual

### Four Channel PCIe High Performance Serial I/O Featuring RS422/RS485/RS232 Software Configurable Transceivers and 32K Byte FIFO Buffers (256K Byte total)

RS485 RS422/V.11 RS232/V.28

General Standards Corporation 8302A Whitesburg Drive Huntsville, AL 35802 Phone: (256) 880-8787 Fax: (256) 880-8788 URL: www.generalstandards.com E-mail: techsupport@generalstandards.com

Rev 1

#### PREFACE

#### **Revision History**

- 1. Rev NR Mar 2013 Original rev from PMC66-SIO4BXR manual.

- 2. Rev 1– May 2013

Additional copies of this manual or other **General Standards Corporation** literature may be obtained from:

General Standards Corporation 8302A Whitesburg Drive Huntsville, Alabama 35802 Telephone: (256) 880-8787 Fax: (256) 880-8788 URL: www.generalstandards.com

The information in this document is subject to change without notice.

**General Standards Corporation** makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Although extensive editing and reviews are performed before release to ECO control, **General Standards Corporation** assumes no responsibility for any errors that may exist in this document. No commitment is made to update or keep current the information contained in this document.

**General Standards Corporation** does not assume any liability arising out of the application or use of any product or circuit described herein, nor is any license conveyed under any patent right of any rights of others.

**General Standards Corporation** assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

**General Standards Corporation** reserves the right to make any changes, without notice, to this product to improve reliability, performance, function, or design.

#### All rights reserved

No parts of this document may be copied or reproduced in any form or by any means without prior written consent of **General Standards Corporation**.

Copyright © 2013 General Standards Corporation

#### **RELATED PUBLICATIONS**

ZILOG Z16C30 USC® User's Manual ZILOG Z16C30 USC® Product Specifications Databook

> ZILOG, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 (408) 370-8000 http://www.zilog.com/

PLX PEX8311AA Data Book

PLX Technology Inc. 390 Potrero Avenue Sunnyvale, CA 4085 (408) 774-3735 http://www.plxtech.com/

<u>EIA-422-A – Electrical Characteristics of Balanced Voltage Digital Interface Circuits</u> (EIA order number EIA-422A)

<u>EIA-485 – Standard for Electrical Characteristics of Generators and Receivers for Use in Balanced Digital</u> <u>Multipoint Systems</u> (EIA order number EIA-485)

EIA Standards and Publications can be purchased from:

GLOBAL ENGINEERING DOCUMENTS 15 Inverness Way East Englewood, CO 80112 Phone: (800) 854-7179 http://global.ihs.com/

PCI Local Bus Specification Revision 2.2 December 18, 1998

Copies of PCI specifications available from: PCI Special Interest Group NE 2575 Kathryn Street, #17 Hillsboro, OR 97124 http://www.pcisig.com/

> General Standards Corporation 8302A Whitesburg Drive •Huntsville, AL 35802 Phone: (256)880-8787 or (800)653-9970 FAX: (256)880-8788 Email: sales@generalstandards.com

### **TABLE OF CONTENTS**

| RELATED PUBLICATIONS.       II         TABLE OF CONTENTS       III         CHAPTER 1: INTRODUCTION.       1         1.0       GENERAL DESCRIPTION       1         1.1       ZIGZIO UNIVERAL SERIAL CONTROLLER       2         1.2       DEEP TRANSMIT/RECEIVE FIFIOS.       2         1.3       MULTIPROTOCOL TRANSCEIVERS.       3         1.4       PMC/PCI INTERFACE.       3         1.5       GENERAL PURPOSE IO       3         1.6       CONNECTOR INTERFACE.       3         1.7       NEW FEATURES.       3         1.7       NEW FEATURES.       4         2.0       REGISTER MAP.       4         2.1       BOARD CONTROL: LOCAL OFISET 0X0000.       5         2.1.2       BOARD DOTITOL: LOCAL OFISET 0X0004.       6         2.1.3       BOARD DOTITOL: LOCAL OFISET 0X0004.       6         2.1.4       TIMESTAMP: LOCAL OFISET 0X0004.       7         2.1.4       TIMESTAMP: LOCAL OFISET 0X0004.       7         2.1.4       TIMESTAMP: LOCAL OFISET 0X0014 / 0X0024 / 0X0034 / 0X0044 / 0X0044.       8         2.1.7       CHANNEL XALMOST FLAGS: LOCAL OFISET 0X0014 / 0X0024 / 0X0034 / 0X0044.       8         2.1.4       TIMESTAMP: LOCAL OFISET 0X0016 / 0X0028 / 0X003                                                                                                                                                                                                                   | PREFAC | СЕ                                 | I  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------|----|

| CHAPTER 1: INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RELATI | ED PUBLICATIONS                    | II |

| 1.0       GENERAL DESCRIPTION.       1         1.1       Z16C30 UNIVERSAL SERIAL CONTROLLER       2         1.2       DEEP TRANSMIT/RECEIVE FIFOS       2         1.3       MULTTROTOCOL TRANSCEIVERS       3         1.4       PMC/PCI INTERFACE       3         1.5       GENERAL PURPOSE IO       3         1.6       CONNECTOR INTERFACE       3         1.7       NEW FEATURES       3         CHAPTER 2: LOCAL SPACE REGISTERS       4         2.0       REGISTER MAP       4         2.1       GSC FIRMWARE REGISTERS       4         2.1       FIRMWARE REGISTERS       4         2.1.1       FIRMWARE REGISTERS       4         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0004       6         2.1.4       TIMESTAMP: LOCAL OFFSET 0X0016 / 0X0024 / 0X0034 / 0X0034 / 0X0044       8         2.1.7       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0016 / 0X0024 / 0X0034 / 0X0044       8         2.1.8       CHANNEL X ALMOST FLAGS: LOCAL OFFSET 0X0016 / 0X0024 / 0X0034 / 0X0034 / 0X0044       8         2.1.9       CHANNEL X ALMOST FLAGS: LOCAL OFFSET 0X0016 / 0X0024 / 0X0034 / 0X0034 / 0X0044       8         2.1.9       CHANNEL X ALMO                                                                                                                                                                                         | TABLE  | OF CONTENTS                        |    |

| 1.1       Z16C30 UNIVERSAL SERIAL CONTROLLER       2         1.2       DEFF TRANSMIT/RECEIVE FIFOS       2         1.3       MULTEROTOCCI TRANSCEIVERS       3         1.4       PMC/PCI INTERFACE       3         1.5       GENERAL PURPOSE IO       3         1.6       CONNECTOR INTERFACE       3         1.7       NEW FEATURES       3         CMAPTER 2: LOCAL SPACE REGISTERS       4         2.0       REGISTER MAP       4         2.1       GSC FIRMWARE REGISTERS       4         2.1       FIRMWARE REGISTERS       4         2.1       FIRMWARE REGISTERS       4         2.1.1       FIRMWARE REGISTERS       4         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004       6         2.1.3       MURTSTAWE: LOCAL OFFSET 0X0004       7         2.1.4       TIMESTAWE: LOCAL OFFSET 0X0016 / 0X0024 / 0X0034 / 0X0044       8         2.1.7       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0034 / 0X0044       8         2.1.8       CHANNEL XLMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0038 / 0X0044       8         2.1.8       CHANNEL XLMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0038 / 0X0044       8         2.1.9       CHANNEL XLMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024                                                                                                                                                                                         | CHAPTI | ER 1: INTRODUCTION                 | 1  |

| 1.2       DEEP TRANSMIT/RECEIVE FIFOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.0    |                                    |    |

| 1.3       MULTIPROTOCOL TRANSCEIVERS.       .3         1.4       PMC/PCI INTERFACE       .3         1.5       GENERAL PURPOSE IO       .3         1.6       CONNECTOR INTERFACE       .3         1.7       NEW FEATURES.       .3         1.7       NEW FEATURES.       .3         CHAPTER 2: LOCAL SPACE REGISTERS.       .4         2.0       REGISTER MAP.       .4         2.1       GSC FIRMWARE REGISTERS.       .4         2.1.1       FIRMWARE REVISION: LOCAL OFFSET 0X0000       .5         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004       .6         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0000       .7         2.1.4       TIMESTAMP: LOCAL OFFSET 0X0000       .7         2.1.5       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0020 / 0X0030 / 0X0040       .7         2.1.6       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0022 / 0X0034 / 0X0044       .8         2.1.7       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0022 / 0X0034 / 0X0044       .8         2.1.8       CHANNEL FIFO: LOCAL OFFSET 0X0018 / 0X0028 / 0X0038 / 0X0048       .8         2.1.9       CHANNEL FIFO: LOCAL OFFSET 0X0060       .10         2.1.10       INTERRUPT REGISTERS       .9       .111 <tr< td=""><td>1.1</td><td>Z16C30 Universal Serial Controller</td><td>2</td></tr<>                                                                                                   | 1.1    | Z16C30 Universal Serial Controller | 2  |

| 1.4       PMC/PCI INTERFACE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.2    | DEEP TRANSMIT/RECEIVE FIFOS        | 2  |

| 1.5       GENERAL PURPOSE IO       3         1.6       CONNECTOR INTERFACE       3         1.7       NEW FEATURES       3         CHAPTER 2: LOCAL SPACE REGISTERS       4         2.0       REGISTER MAP       4         2.1       GSC FIRNWARE REGISTERS       4         2.1.1       FIRMWARE REVISION: LOCAL OFFSET 0X0000       5         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004       6         2.1.3       BOARD CONTROL: LOCAL OFFSET 0X0000       7         2.1.4       TIMESTAMP. LOCAL OFFSET 0X0000C       7         2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0020 / 0X0030 / 0X0044       8         2.1.6       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0034 / 0X0044       8         2.1.6       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0034 / 0X0044       8         2.1.6       CHANNEL STAL CONTROL/STATUS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0032 / 0X0044       8         2.1.8       CHANNEL STAL CONTROL/STATUS: LOCAL OFFSET 0X0010 / 0X0024 / 0X0035 / 0X0048       8         2.1.9       CHANNEL STAL CONTROL/STATUS: LOCAL OFFSET 0X005 / 0X0054 / 0X0058 / 0X005C       9         2.1.10       INTERRUPT REGISTERS       9       1.110         2.1.11       INTERRUPT REGISTERS       10                                                                                                                                   | 1.3    | MULTIPROTOCOL TRANSCEIVERS         | 3  |

| 1.6       CONNECTOR INTERFACE       3         1.7       NEW FEATURES       3         CHAPTER 2: LOCAL SPACE REGISTERS       4         2.0       REGISTER MAP.       4         2.1       GSC FERMWARE REGISTERS       4         2.1.1       FIRMWARE REGISTERS       4         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0000       5         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0004       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0000C       7         2.1.4       TIMESTAMP. LOCAL OFFSET 0X0000C       7         2.1.5       CHANNEL XX ALMOST FLAGS: LOCAL OFFSET 0X0014 / 0X0024 / 0X0033 / 0X0040       7         2.1.6       CHANNEL XX ALMOST FLAGS: LOCAL OFFSET 0X0011 / 0X0022 / 0X0033 / 0X0044       8         2.1.7       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0012 / 0X0032 / 0X0033 / 0X0044       8         2.1.8       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0X0016 / 0X0022 / 0X0032 / 0X0042 / 0X0044       8         2.1.9       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0X005 / 0X0052 / 0X0035 / 0X0042       9         2.1.10       INTERRUPT REGISTERS       9       9         2.1.11       INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0X0066       10         2.1.12       INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0X00064       10                                                                                                                                           | 1.4    |                                    |    |

| 1.7       New Features       3         CHAPTER 2: LOCAL SPACE REGISTERS       4         2.0       Register Map       4         2.1       GSC Firmware Registers       4         2.1.1       Firmware Revision: Local OFFSET 0x0000       5         2.1.2       BOARD CONTROL: Local OFFSET 0x0004       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0x0004       7         2.1.4       TIMESTAMP: LOCAL OFFSET 0x000C       7         2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0020 / 0x0030 / 0x0040       7         2.1.6       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0022 / 0x0033 / 0x0048       8         2.1.7       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0022 / 0x0033 / 0x0044       8         2.1.6       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0022 / 0x0033 / 0x0044       8         2.1.7       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0022 / 0x0033 / 0x0044       8         2.1.8       CHANNEL SYNC DETECT B YTE: LOCAL OFFSET 0x0010 / 0x0022 / 0x0033 / 0x0042       8         2.1.9       CHANNEL SYNC DETECT B YTE: LOCAL OFFSET 0x0060       9         2.1.10       INTERRUPT REGISTERS       9         2.1.11       INTERRUPT REGISTERS       9         2.1.12       INTERRUPT REGISTERS       10                                                                                                                         | 1.5    | GENERAL PURPOSE IO                 | 3  |

| CHAPTER 2: LOCAL SPACE REGISTERS.       4         2.0       REGISTER MAP.       4         2.1       GSC FIRMWARE REGISTERS.       4         2.1.1       FIRMWARE REVISION: LOCAL OFFSET 0X0000.       5         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004.       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0008.       7         2.1.4       TIMESTAMP: LOCAL OFFSET 0X0000C.       7         2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0014 / 0X0024 / 0X0034 / 0X0040.       7         2.1.6       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0014 / 0X0024 / 0X0034 / 0X0044.       8         2.1.7       CHANNEL FIFO: LOCAL OFFSET 0X0018 / 0X0028 / 0X0038 / 0X0048       8         2.1.9       CHANNEL FITO: LOCAL OFFSET 0X0018 / 0X0028 / 0X0038 / 0X0048       8         2.1.9       CHANNEL FITO: LOCAL OFFSET 0X0016 / 0X0027 / 0X0034 / 0X0044       8         2.1.9       CHANNEL FITO: LOCAL OFFSET 0X0000 / 0X0027 / 0X0034 / 0X0044       8         2.1.9       CHANNEL SYNC DETECT B YTE: LOCAL OFFSET 0X0050 / 0X0054 / 0X0058 / 0X005C       9         2.1.10       INTERRUPT STATUS: LOCAL OFFSET 0X0060       10         2.1.12       INTERRUPT STATUS: LOCAL OFFSET 0X0060 / 0X0084 / 0X0088 / 0X008C       11         2.1.14       INTERRUPT STATUS: LOCAL OFFSET 0X00060 / 0X0044 / 0X0088 / 0X008C <t< td=""><td>1.6</td><td>CONNECTOR INTERFACE</td><td>3</td></t<> | 1.6    | CONNECTOR INTERFACE                | 3  |

| 2.0       REGISTER MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.7    | New Features                       | 3  |

| 2.1       GSC Firmware Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHAPTI | ER 2: LOCAL SPACE REGISTERS        | 4  |

| 2.1       GSC Firmware Registers       4         2.1.1       Firmware Revision: Local OFFSET 0x0000       5         2.1.2       BOARD CONTROL: LOCAL OFFSET 0x0004       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0x0006       7         2.1.4       TIMESTAMP: LOCAL OFFSET 0x000C       7         2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0020 / 0x0030 / 0x0040       7         2.1.6       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0x0014 / 0x0024 / 0x0034 / 0x0044       8         2.1.7       CHANNEL FIFO: LOCAL OFFSET 0x0018 / 0x0028 / 0x0032 / 0x0032 / 0x0044       8         2.1.8       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0x0010 / 0x002C / 0x003C / 0x004C       8         2.1.9       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0x0060 / 0x0054 / 0x0058 / 0x005C       9         2.1.10       INTERRUPT REGISTERS       9       9         2.1.11       INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0x0064       10         2.1.12       INTERRUPT EDGE/LEVEL: LOCAL OFFSET 0x0066       11         2.1.14       INTERRUPT EMEGISTER: LOCAL OFFSET 0x0080 / 0x0084 / 0x0088 / 0x008C       11         2.1.14       INTERRUPT EMEGISTER: LOCAL OFFSET 0x0060 / 0x0044 / 0x0088 / 0x008C       11         2.1.15       CHANNEL PIN SOURCE: LOCAL OFFSET 0x0080 / 0x0094 / 0x0098 / 0x009C       14         2.1.16                                                              | 2.0    | REGISTER MAP                       | 4  |

| 2.1.1       FIRMWARE REVISION: LOCAL OFFSET 0X0000       5         2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004       6         2.1.3       BOARD STATUS: LOCAL OFFSET 0X0008       7         2.1.4       TIMESTAMP: LOCAL OFFSET 0X000C       7         2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0010 / 0X0020 / 0X0030 / 0X0040       7         2.1.6       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0X0014 / 0X0024 / 0X0034 / 0X0044       8         2.1.7       CHANNEL REPO: LOCAL OFFSET 0X0018 / 0X0028 / 0X0038 / 0X0048       8         2.1.8       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0X0010 / 0X0022 / 0X0037 / 0X004C       8         2.1.9       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0X0060 / 0X0054 / 0X0058 / 0X005C       9         2.1.10       INTERRUPT REGISTERS       9       9         2.1.11       INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0X0064       10         2.1.12       INTERRUPT EDGE/LEVEL: LOCAL OFFSET 0X0066       11         2.1.14       INTERRUPT BIDE/LEVEL: LOCAL OFFSET 0X0066       11         2.1.14       INTERRUPT BIDE/LEVEL: LOCAL OFFSET 0X0066       11         2.1.14       INTERRUPT BIDE/LEVEL: LOCAL OFFSET 0X0080 / 0X0084 / 0X0088 / 0X008C       11         2.1.14       INTERRUPT BIDE/LEVEL: LOCAL OFFSET 0X0060 / 0X0084 / 0X0088 / 0X008C       11         2.1.15                                                                       |        |                                    |    |

| 2.1.2       BOARD CONTROL: LOCAL OFFSET 0X0004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                                    |    |

| 2.1.3       BOARD STATUS: LOCAL OFFSET 0X0008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.1.2  |                                    |    |

| 2.1.4       TIMESTAMP: LOCAL OFFSET 0X000C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                    |    |

| 2.1.5       CHANNEL TX ALMOST FLAGS: LOCAL OFFSET 0x0010 / 0x0020 / 0x0030 / 0x0040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.1.4  |                                    |    |

| 2.1.6       CHANNEL RX ALMOST FLAGS: LOCAL OFFSET 0X0014 / 0X0024 / 0X0034 / 0X0044                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.1.5  |                                    |    |

| 2.1.7       CHANNEL FIFO: LOCAL OFFSET 0X0018 / 0X0028 / 0X0038 / 0X0048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.1.6  |                                    |    |

| 2.1.8       CHANNEL CONTROL/STATUS: LOCAL OFFSET 0x001C / 0x002C / 0x003C / 0x004C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.1.7  |                                    |    |

| 2.1.9       CHANNEL SYNC DETECT BYTE: LOCAL OFFSET 0x0050 / 0x0054 / 0x0058 / 0x005C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.1.8  |                                    |    |

| 2.1.10INTERRUPT REGISTERS92.1.11INTERRUPT CONTROL: LOCAL OFFSET 0x0060.102.1.12INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0x0064.102.1.13INTERRUPT EDGE/LEVEL: LOCAL OFFSET 0x0068112.1.14INTERRUPT HI/LO: LOCAL OFFSET 0x006C.112.1.15CHANNEL PIN SOURCE: LOCAL OFFSET 0x0080 / 0x0084 / 0x0088 / 0x008C112.1.16CHANNEL PIN STATUS: LOCAL OFFSET 0x0090 / 0x0094 / 0x0098 / 0x009C142.1.17PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0x0000 / 0x0004 / 0x00A4 / 0x00A8 / 0xAC152.1.14FIFO COUNT REGISTER: LOCAL OFFSET 0x00D0 / 0x00D4 / 0x00D8 / 0x00DC152.1.15FIFO SIZE REGISTER: LOCAL OFFSET 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC152.1.16FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8152.1.17FEATURES REGISTER: LOCAL OFFSET 0x00F8152.1.17FEATURES REGISTER: LOCAL OFFSET 0x00F8162.2UNIVERSAL SERIAL CONTROLLER REGISTERS162.2.1USC REGISTER ACCESS172.2.3USC DATA TRANSFER172.2.4USC REGISTER MEMORY MAP18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                    |    |

| 2.1.11       INTERRUPT CONTROL: LOCAL OFFSET 0x0060                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.1.10 |                                    |    |

| 2.1.12       INTERRUPT STATUS/CLEAR: LOCAL OFFSET 0x0064                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                    |    |

| 2.1.13       INTERRUPT EDGE/LEVEL: LOCAL OFFSET 0x0068       11         2.1.14       INTERRUPT HI/LO: LOCAL OFFSET 0x006C       11         2.1.15       CHANNEL PIN SOURCE: LOCAL OFFSET 0x0080 / 0x0084 / 0x0088 / 0x008C       11         2.1.16       CHANNEL PIN STATUS: LOCAL OFFSET 0x0090 / 0x0094 / 0x0098 / 0x009C       14         2.1.13       PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0x00A0 / 0x00A4 / 0x00A8 / 0xAC       15         2.1.14       FIFO Count Register: LOCAL OFFSET 0x00D0 / 0x00D4 / 0x00D4 / 0x00D8 / 0x00C       15         2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00F8       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                      |        |                                    |    |

| 2.1.14       INTERRUPT HI/LO: LOCAL OFFSET 0X006C       11         2.1.15       CHANNEL PIN SOURCE: LOCAL OFFSET 0X0080 / 0X0084 / 0X0088 / 0X008C       11         2.1.16       CHANNEL PIN STATUS: LOCAL OFFSET 0X0090 / 0X0094 / 0X0098 / 0X009C       14         2.1.13       PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0X00A0 / 0X00A4 / 0X00A8 / 0XAC       15         2.1.14       FIFO COUNT REGISTER: LOCAL OFFSET 0X00D0 / 0X00D4 / 0X00D8 / 0X00DC       15         2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0X00E0 / 0X00E4 / 0X00E8 / 0X00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0X00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0X00F8       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                                    |    |

| 2.1.15       CHANNEL PIN SOURCE: LOCAL OFFSET 0x0080 / 0x0084 / 0x0088 / 0x008C       11         2.1.16       CHANNEL PIN STATUS: LOCAL OFFSET 0x0090 / 0x0094 / 0x0098 / 0x009C       14         2.1.13       PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0x00A0 / 0x00A4 / 0x00A8 / 0xAC       15         2.1.14       FIFO COUNT REGISTER: LOCAL OFFSET 0x00D0 / 0x00D4 / 0x00D8 / 0x00DC       15         2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00FC (0x00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                    |    |

| 2.1.16       CHANNEL PIN STATUS: LOCAL OFFSET 0x0090 / 0x0094 / 0x0098 / 0x009C       14         2.1.13       PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0x00A0 / 0x00A4 / 0x00A8 / 0xAC       15         2.1.14       FIFO COUNT REGISTER: LOCAL OFFSET 0x00D0 / 0x00D4 / 0x00D8 / 0x00DC       15         2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00F7 (0x00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                    |    |

| 2.1.13       PROGRAMMABLE CLOCK REGISTERS: LOCAL OFFSET 0x00A0 / 0x00A4 / 0x00A8 / 0xAC       15         2.1.14       FIFO COUNT REGISTER: LOCAL OFFSET 0x00D0 / 0x00D4 / 0x00D8 / 0x00DC       15         2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00FC (0x00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                    |    |

| 2.1.14       FIFO Count Register: Local Offset 0x00D0 / 0x00D4 / 0x00D8 / 0x00DC       15         2.1.15       FIFO Size Register: Local Offset 0x00E0 / 0x00E4 / 0x00E8 / 0x00EC       15         2.1.16       FW Type ID Register: Local Offset 0x00F8       15         2.1.17       Features Register: Local Offset 0x00FC (0x00197AF4)       16         2.2       Universal Serial Controller Registers       16         2.2.1       USC Reset       16         2.2.2       8-Bit USC Register Access       17         2.2.3       USC Data Transfer       17         2.2.4       USC Register Memory Map       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                    |    |

| 2.1.15       FIFO SIZE REGISTER: LOCAL OFFSET 0X00E0 / 0X00E4 / 0X00E8 / 0X00EC       15         2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0X00F8       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0X00FC (0X00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                    |    |

| 2.1.16       FW TYPE ID REGISTER: LOCAL OFFSET 0x00F8.       15         2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00FC (0x00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                    |    |

| 2.1.17       FEATURES REGISTER: LOCAL OFFSET 0x00FC (0x00197AF4)       16         2.2       UNIVERSAL SERIAL CONTROLLER REGISTERS       16         2.2.1       USC RESET       16         2.2.2       8-BIT USC REGISTER ACCESS       17         2.2.3       USC DATA TRANSFER       17         2.2.4       USC REGISTER MEMORY MAP       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                    |    |

| 2.2UNIVERSAL SERIAL CONTROLLER REGISTERS162.2.1USC RESET162.2.28-BIT USC REGISTER ACCESS172.2.3USC DATA TRANSFER172.2.4USC REGISTER MEMORY MAP18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                    |    |

| 2.2.1       USC RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                    |    |

| 2.2.28-BIT USC REGISTER ACCESS172.2.3USC DATA TRANSFER172.2.4USC REGISTER MEMORY MAP18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                    |    |

| 2.2.3       USC DATA TRANSFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                                    |    |

| 2.2.4 USC REGISTER MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                    |    |

General Standards Corporation 8302A Whitesburg Drive 'Huntsville, AL 35802 Phone: (256)880-8787 or (800)653-9970 FAX: (256)880-8788 Empik colorements learned or of the second Email: sales@generalstandards.com

| 3.0    | INTRODUCTION                                   |    |

|--------|------------------------------------------------|----|

| 3.1    | RESETS                                         |    |

| 3.2    | FIFOs                                          |    |

| 3.2.1  | FIFO FLAGS                                     |    |

| 3.2.2  | FIFO COUNTERS                                  |    |

| 3.2.3  | FIFO SIZE                                      |    |

| 3.3    | BOARD VS. CHANNEL REGISTERS                    |    |

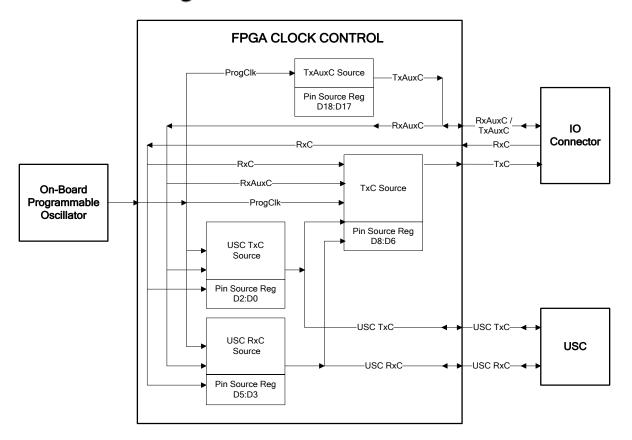

| 3.4    | PROGRAMMABLE OSCILLATOR / PROGRAMMABLE CLOCKS  |    |

| 3.5    | CLOCK SETUP                                    |    |

| 3.6    | MULTIPROTOCOL TRANSCEIVER CONTROL              |    |

| 3.7    | DCE/DTE MODE                                   | 23 |

| 3.8    | LOOPBACK MODES                                 | 23 |

| 3.9    | GENERAL PURPOSE IO                             |    |

| 3.10   | INTERRUPTS                                     |    |

| 3.11   | PCI DMA                                        |    |

| СНАРТ  | FER 4: PCI INTERFACE                           | 26 |

| 4.0    | PCI INTERFACE REGISTERS                        |    |

| 4.1    | PCI REGISTERS                                  |    |

| 4.1.1  | PCI CONFIGURATION REGISTERS                    |    |

| 4.1.2  | LOCAL CONFIGURATION REGISTERS                  |    |

| 4.1.3  |                                                |    |

| 4.1.4  |                                                |    |

| 4.1.4. | 1 DMA CHANNEL MODE REGISTER: (PCI 0x80 / 0x94) | 27 |

| СНАРТ  | FER 5: HARDWARE CONFIGURATION                  | 28 |

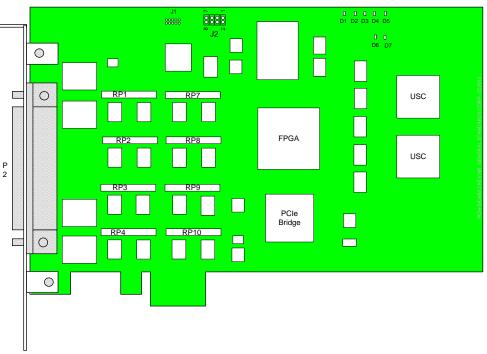

| 5.0    | BOARD LAYOUT                                   |    |

| 5.1    | BOARD ID JUMPER J2                             |    |

| 5.2    | TERMINATION RESISTORS                          |    |

| 5.3    | LEDs                                           |    |

| 5.4    | INTERFACE CONNECTOR                            |    |

| СНАРТ  | FER 6: ORDERING OPTIONS                        |    |

| 6.0    | ORDERING INFORMATION                           |    |

| 6.1    | INTERFACE CABLE                                |    |

| 6.2    | Device Drivers                                 |    |

| 6.3    | CUSTOM APPLICATIONS                            |    |

| APPEN  | DIX A: PROGRAMMABLE OSCILLATOR PROGRAMMING     |    |

|        |                                                |    |

| APPEN  | IDIX B: FIRMWARE REVISIONS / FEATURES REGISTER |    |

iv

### **CHAPTER 1: INTRODUCTION**

#### **1.0 General Description**

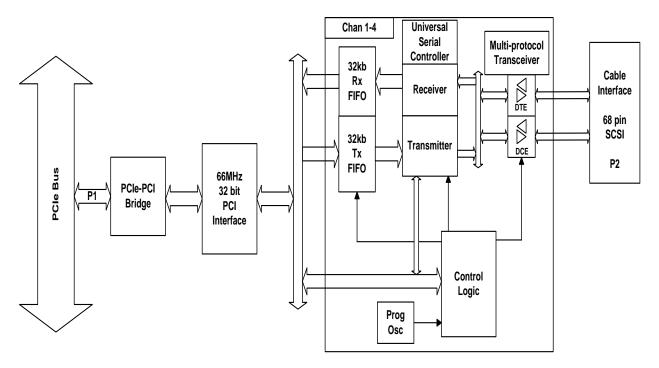

The PCIe-SIO4BX2 is a four channel serial interface card which provides high speed, full-duplex, multi-protocol serial capability for PCIe applications. The PCIe-SIO4BX2 combines multi-protocol Dual Universal Serial Controllers, deep external FIFOs, and software selectable multi-protocol transceivers to provide four fully independent synchronous/asynchronous serial channels. These features, along with a high performance one lane PCIe interface engine, give the PCIe-SIO4BX2 unsurpassed performance in a serial interface card.

#### Features:

- One Lane PCI Express (PCIe) Interface

- Four Independent RS422/RS485/RS232 Serial Channels

- Serial Mode Protocols Asynchronous, Monosync, Bisync, SDLC, HDLC, Nine-Bit, IEEE 802.3

- Synchronous Serial Data Rates up to 10Mbps

- Asynchronous Serial Data Rates up to 1Mbps

- Independent Transmit and Receive FIFOs for each Serial Channel 32K byte each

- Multi-protocol Transceivers support RS422/RS485 and RS232

- Parity and CRC detection capability

- Programmable Oscillators provide increased flexibility for Baud Rate Clock generation

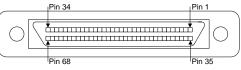

- SCSI type 68 pin front edge I/O Connector

- Eight signals per channel, configurable as either DTE or DCE: 3 Serial Clocks (TxC,RxC,AuxC), 2 Serial Data signals (TxD,RxD), CTS, RTS, DCD

- Unused signals may be reconfigured as General Purpose IO

- Fast RS422/RS485 Differential Cable Transceivers Provide Data Rates up to 10Mbps

- RS232 Cable Transceivers Provide Data Rates up to 250kbps

- Industry Standard Zilog Z16C30 Multi-Protocol Universal Serial Controllers (USC®)

- Standard Cable to four DB25 connectors and Custom Cables available

- Available drivers include VxWorks, WinNT, Win2k, WinXP, Linux, and Labview

- Industrial Temperature Option Available

Functional Diagram:

Figure 1-1 Block Diagram of PCIe-SIO4BX2

#### 1.1 Z16C30 Universal Serial Controller

The PCIe-SIO4BX2 is designed around the Z16C30 Universal Serial Controller(USC). The Z16C30 is a dual channel multi-protocol serial controller which may be software configured to satisfy a wide variety of serial communications applications. The USC supports most common asynchronous and synchronous serial protocols. The USC provides many advanced features, including:

- Completely independent transmitter and receiver operation

- Odd/Even/Space/Mark parity

- Two 16-bit or one 32-bit CRC polynomial

- Eight Data Encoding methods NRZ, NRZB, NRZI-Mark, NRZI-Space, Biphase-Mark, Biphase-Space, Biphase-Level, and Differential Biphase-Level

#### **1.2 Deep Transmit/Receive FIFOs**

Data is transferred to/from the serial interface through Transmit and Receive FIFOs. Each of the four serial channels has an independent Transmit FIFO and a Receive FIFO for a total of eight separate on-board FIFOs. These FIFOs are always 32k bytes deep. FIFOs allow data transfer to continue to/from the IO interface independent of PCI interface transfers and software overhead. The required FIFO size may depend on several factors including data transfer size, required throughput rate, and the software overhead (which will also vary based on OS). Generally, faster baud rates (greater than 500kbps) will require deeper FIFOs. Deeper FIFOs help ensure no data is lost for critical systems.

The SIO4BX2 provides access to complete FIFO status to optimize data transfers. In addition to Empty and Full indicators, each FIFO has a programmable Almost Empty Flag and a programmable Almost Full Flag. These FIFO flags may be used as interrupt sources to monitor FIFO fill levels. In addition, real-time FIFO counters showing the exact number of words in the FIFO are also provided for each FIFO. By utilizing these FIFO counters, data transfers can be optimized to efficiently send and receive data.

#### **1.3 Multiprotocol Transceivers**

The SIO4BX2 data is transferred over the user interface using high-speed multiprotocol transceivers. These multiprotocol transceivers are software selectable as RS422/RS485, or RS232 on a per channel basis. Each channel direction may also be configured as DTE or DCE configuration. This allows for either full duplex or half duplex configurations.

#### 1.4 PMC/PCI Interface

The control interface to the SIO4BX2 is through the PMC/PCI interface. An industry standard PCI9056 bridge chip from PLX Technology is used to implement PCI Specification 2.2. The PCI9056 provides the 32bit, 66MHz (264MBit/sec) interface between the PCI bus and the Local 32 bit bus. It also provides for high-speed DMA transfers to efficiently move data to and from the board.

#### 1.5 General Purpose IO

Since some signals may not be used in all applications, the SIO4BX2 provides the flexibility to remap unused signals to be used as general purpose IO. For example, this would allow support for an application requiring DTR/DSR signals to be implemented on an unused DCD or TxAuxC signals. This also allows signals from unused channels to be available as general purpose IO.

#### **1.6** Connector Interface

The SIO4BX2 provides a user IO interface through a front-side card edge connector. All four serial channels interface through this high-density, 68 pin SCSI-3 type connector, and are grouped to simplify separating the cable into four distinct serial connectors.

Standard cables are available from General Standards in various lengths to adapt the single 68 pin SCSI-3 connector into four DB25 connectors (one per channel). A standard cable is also available with a single 68 pin SCSI-3 connector on one end and open on the other. This allows the user to add a custom connector (or connect to a terminal block). General Standards will also work with customers to fabricate custom cables. Consult factory for details on custom cables.

#### 1.7 New Features

The PCIe-SIO4BX2 has been enhanced with several new features. These include improved receive data status recording, timestamping of data, flexible FIFO memory allocation, sync/standard channel select, and channel reset.

#### **CHAPTER 2: LOCAL SPACE REGISTERS**

#### 2.0 Register Map

The SIO4BX2 is accessed through three sets of registers – PCI Registers, USC Registers, and GSC Firmware Registers. The GSC Firmware Registers and USC Registers are referred to as Local Space Registers and are described below. The PCI registers are discussed in Chapter 3.

The Local Space Registers are divided into two distinct functional register blocks – the GSC Firmware Registers and the USC Registers. The GSC Firmware Registers perform the custom board control functions, while the USC Registers map the Zilog Z16C30 registers into local address space. The register block for each USC channel is accessed at a unique address range. The table below shows the address mapping for the local space registers.

| Local Address Range | <b>Base Address Offset</b> | <b>Register Block Description</b> |

|---------------------|----------------------------|-----------------------------------|

| 0x0000 - 0x00FF     | 0x0000                     | GSC Firmware Registers            |

| 0x0100 - 0x013F     | 0x0100                     | Channel 1 USC Registers           |

| 0x0140 - 0x01FF     |                            | Reserved                          |

| 0x0200 - 0x023F     | 0x0200                     | Channel 2 USC Registers           |

| 0x0240 - 0x02FF     |                            | Reserved                          |

| 0x0300 - 0x033F     | 0x0300                     | Channel 3 USC Registers           |

| 0x0340 - 0x03FF     |                            | Reserved                          |

| 0x0400 - 0x043F     | 0x0400                     | Channel 4 USC Registers           |

The GSC Firmware Registers are detailed in Section 2.1. The USC Registers are briefly touched on in Section 2.2 of this manual, but are described in much greater detail in the <u>Zilog Z16C30 Users Manuals</u>.

#### 2.1 GSC Firmware Registers

The GSC Firmware Registers provide the primary control/status for the SIO4BX2 board. The following table shows the GSC Firmware Registers.

| Offset Address | Size | Access*    | Register Name             | Default Value (Hex) |

|----------------|------|------------|---------------------------|---------------------|

| 0x0000         | D32  | Read/Write | Firmware Revision         | E51001XX            |

| 0x0004         | D32  | Read/Write | Board Control             | 00000000            |

| 0x0008         | D32  | Read Only  | Board Status              | 000000XX            |

| 0x000C         | D32  | Read/Write | Timestamp                 | 00000000            |

| 0x0010         | D32  | Read/Write | Ch 1 Tx Almost Full/Empty | 00070007            |

| 0x0014         | D32  | Read/Write | Ch 1 Rx Almost Full/Empty | 00070007            |

| 0x0018         | D32  | Read/Write | Ch l 1 Data FIFO          | 000000XX            |

| 0x001C         | D32  | Read/Write | Ch 1 Control/Status       | 0000CC00            |

| 0x0020         | D32  | Read/Write | Ch 2 Tx Almost Full/Empty | 00070007            |

| 0x0024         | D32  | Read/Write | Ch 2 Rx Almost Full/Empty | 00070007            |

| 0x0028         | D32  | Read/Write | Ch 2 FIFO                 | 000000XX            |

| 0x002C         | D32  | Read/Write | Ch 2 Control/Status       | 0000CC00            |

| 0x0030         | D32  | Read/Write | Ch 3 Tx Almost Full/Empty | 00070007            |

| 0x0034         | D32  | Read/Write | Ch 3 Rx Almost Full/Empty | 00070007            |

| 0x0038         | D32  | Read/Write | Ch 3 Data FIFO            | 000000XX            |

**General Standards Corporation**

8302A Whitesburg Drive Huntsville, AL 35802 Phone: (256)880-8787 or (800)653-9970 FAX: (256)880-8788 Email: sales@generalstandards.com

|               |     |            | 1                               |          |

|---------------|-----|------------|---------------------------------|----------|

| 0x003C        | D32 | Read/Write | Ch 3 Control/Status             | 0000CC00 |

| 0x0040        | D32 | Read/Write | Ch 4 Tx Almost Full/Empty       | 00070007 |

| 0x0044        | D32 | Read/Write | Ch 4 Rx Almost Full/Empty       | 00070007 |

| 0x0048        | D32 | Read/Write | Ch 4 Data FIFO                  | 000000XX |

| 0x004C        | D32 | Read/Write | Ch 4 Control/Status             | 0000CC00 |

| 0x0050        | D32 | Read/Write | Ch 1 Sync Byte                  | 00000000 |

| 0x0054        | D32 | Read/Write | Ch 2 Sync Byte                  | 00000000 |

| 0x0058        | D32 | Read/Write | Ch 3 Sync Byte                  | 00000000 |

| 0x005C        | D32 | Read/Write | Ch 4 Sync Byte                  | 00000000 |

| 0x0060        | D32 | Read/Write | Interrupt Control               | 00000000 |

| 0x0064        | D32 | Read/Write | Interrupt Status                | 00000000 |

| 0x0068        | D32 | Read Only  | Interrupt Edge/Level            | FFFF7777 |

| 0x006C        | D32 | Read/Write | Interrupt High/Low              | FFFFFFF  |

| 0x0070-0x007C |     |            | RESERVED                        |          |

| 0x0080        | D32 | Read/Write | Ch 1Pin Source                  | 0000020  |

| 0x0084        | D32 | Read/Write | Ch 2 Pin Source                 | 0000020  |

| 0x0088        | D32 | Read/Write | Ch 3 Pin Source                 | 0000020  |

| 0x008C        | D32 | Read/Write | Ch 4 Pin Source                 | 0000020  |

| 0x0090        | D32 | Read Only  | Ch 1Pin Status                  | 000000XX |

| 0x0094        | D32 | Read Only  | Ch 2 Pin Status                 | 000000XX |

| 0x0098        | D32 | Read Only  | Ch 3 Pin Status                 | 000000XX |

| 0x009C        | D32 | Read Only  | Ch 4 Pin Status                 | 000000XX |

| 0x00A0        | D32 | Read/Write | Programmable Osc RAM Addr       | 00000000 |