# DSTni-LX Data Book

Revision F Part Number GC-900-252

#### **Copyright and Trademark**

© 2003 Grid Connect, Inc. All rights reserved.

No part of this manual may be reproduced or transmitted in any form for any purpose other than the purchaser's personal use, without the express written permission of Grid Connect, Inc. Grid Connect, Inc. has made every effort to provide completeness and accuracy of this material, but makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability or fitness for a particular purpose. In no event shall Grid Connect, Inc. be liable for any incidental, special, indirect, or consequential damages whatsoever included but not limited to lost profits arising out of errors or omissions in this manual or the information contained herein.

Grid Connect, Inc. products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of a Grid Connect, Inc. product could create a situation where personal injury, death, or severe property or environmental damage may occur. Grid Connect, Inc. reserves the right to discontinue or make changes to its products at any time without notice.

Grid Connect and the Grid Connect logo, and combinations thereof are registered trademarks of Grid Connect, Inc.

DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered trademark of Xerox Corporation. Am186 is a trademark of Advanced Micro Devices, Inc. DataFlash® is a registered trademark of Atmel Corporation. BasicCAN and PeliCAN are registered trademarks of Phillips Semiconductors. SPI is a trademark of Motorola, Inc. All other product names, company names, logos or other designations mentioned herein are trademarks of their respective owners.

#### **Grid Connect**

1630 W. Diehl Rd. Naperville, IL 60563 Phone: 630.245.1445 **Technical Support**

Phone: 630.245.1445 Fax: 630.245.1717

On-line: www.gridconnect.com

| Revision | Date       | Author | Comments                                              |

|----------|------------|--------|-------------------------------------------------------|

| Α        | 08-28-01   | GR     | Initial Release                                       |

| В        | 09-30-01   | AC     | Cosmetic changes and copyright page.                  |

| С        | 10-15-01   | AC     | Removed Glossary and Index, edited block diagram,     |

|          |            |        | Baud Rate table and made cosmetic changes throughout. |

| D        | 11-27-01   | GR     | Replaced Index. Revised format.                       |

| Е        | 2-18-02    | GR     | Ready is synchronous.                                 |

|          | 12/14/2005 |        | Last edited and saved. New Format                     |

|          | 1:58 PM    |        |                                                       |

| F        | 12-14-05   | GR     | Revised tables. Added notes                           |

## **Table of Contents**

| 1  |

|----|

| 1  |

| 1  |

| 2  |

| 3  |

| 3  |

| 3  |

| 4  |

| 5  |

| 5  |

| 5  |

| 5  |

| 5  |

| 5  |

| 5  |

| 6  |

| 6  |

| 6  |

| 6  |

| 6  |

| 8  |

| 8  |

| 9  |

| 9  |

| 9  |

| 9  |

| 10 |

| 10 |

| 12 |

| 12 |

| 12 |

| 13 |

| 14 |

| 25 |

| 28 |

| 29 |

|    |

| ۲ | reripheral Control Block                                                        | 31 |

|---|---------------------------------------------------------------------------------|----|

|   | 2.1 Memory Layout                                                               |    |

|   | 2.2 Peripheral Registers                                                        |    |

|   | 2.2.1 PCB Relocation Register (RELREG, Offset = FEh)                            |    |

|   | 2.2.2 Processor Release Level Register (PRL, Offset = F4h)                      | 33 |

|   | 2.2.3 System Configuration Register (SYSCON, Offset = F0h)                      |    |

|   | 2.2.4 Auxiliary Configuration Register(AUXCON, Offset = F2h)                    | 34 |

|   | 2.2.5 Chip Select                                                               | 34 |

|   | 2.2.6 Ready and Wait-State Programming                                          |    |

|   | 2.2.7 Upper Memory Chip Select Register (UMCS, Offset = A0h)                    | 36 |

|   | 2.2.8 Lower Memory Chip Select (LMCS, Offset = A2h))                            |    |

|   | 2.2.9 Middle Memory Chip Select (MMCS, Offset = A6h)                            |    |

|   | 2.2.10 Memory / Peripheral Control Select (MPCS, Offset = A8h)                  |    |

|   | 2.2.11 Peripheral Chip Selects (PACS, Offset = A4h)                             |    |

|   | 2.2.12 Dual Port Memory Select (DPMS, Offset = AAh)                             | 39 |

|   | 2.2.13 Chip Select Assignments.                                                 |    |

|   | 2.3 Timers                                                                      |    |

|   | 2.3.1 Timer Registers                                                           |    |

|   | 2.3.2 Basic Timer Operation                                                     |    |

|   | 2.3.3 Timer 0 and Timer 1 Control (T0CON, offset 56h; T1CON, offset 5Eh)        |    |

|   | 2.3.4 Timer 2 Control (T2CON, offset 66h)                                       |    |

|   | 2.3.5 Timer 0-2 Count (T0CNT, offset 50h; T1CNT, offset 58h; T2CNT, offset 60h) |    |

|   | 2.3.6 Timer Maxcount Compare                                                    |    |

|   | 2.3.7 Watchdog Timer Control (WDTCON, Offset = E6h)                             |    |

|   | 2.4 Interrupt Controller                                                        |    |

|   | 2.4.1 Interrupt Sources                                                         |    |

|   | 2.4.2 Allocation of external interrupts (INT0 – INT5)                           |    |

|   | 2.4.3 Interrupt control registers                                               |    |

|   | 2.4.4 In-Service Register (INSERV, offset 2Ch)                                  |    |

|   | 2.4.5 Interrupt Request Register (REQST, offset 2Eh)                            |    |

|   | 2.4.6 Interrupt Mask (IMASK, offset 28h)                                        |    |

|   | 2.4.7 Priority Mask (PRIMSK, offset 2Ah)                                        |    |

|   | 2.4.8 Interrupt Status (INTSTS, offset 30h)                                     |    |

|   | 2.4.9 Timer, SP1-0, SPI and DMA3-0 Interrupt Control                            |    |

|   | 2.4.10 INT5-0 Interrupt Control                                                 |    |

|   | 2.4.11 End of Interrupt (EOI, offset 22h)                                       |    |

|   | 2.4.12 Poll and Poll Status (POLL, offset 24h; POLLST, offset 26h)              | 52 |

|   | 2.5 DMA Controller                                                              |    |

|   | 2.5.1 DMA Channel Control Register (D0CON – D3CON)                              | 53 |

|   | 2.5.2 Source and Destination Pointer Register                                   |    |

|   | 2.5.3 Transfer Count Register (D0TC – D3TC)                                     |    |

|   | 2.5.4 DMA Requests                                                              |    |

|   | 2.5.5 DMA Acknowledge                                                           |    |

|   | 2.5.6 DMA Priority                                                              |    |

|   | 2.5.7 DMA Priority                                                              |    |

|   | 2.5.7 DMA Controller Reset                                                      |    |

|   |                                                                                 |    |

ii ◆ Table of Contents DSTni-LX Data Book

| 2.6 Asynchronous Serial Ports5                                                   | 57 |

|----------------------------------------------------------------------------------|----|

| 2.6.1 Receive FIFO                                                               |    |

| 2.6.2 Asynchronous Serial Port Register Summary5                                 |    |

| 2.6.3 Serial Port 0/1 Control (SP0CT, offset 80h; SP1CT, offset 10h)             |    |

| 2.6.4 Serial Port 0/1 Status (SP0STS, offset 82h; SP1STS, offset 12h)6           |    |

| 2.6.5 Serial Port 0/1 Transmit (SP0TD/SP1TD, offset 84h/14h)                     |    |

| 2.6.6 Serial Port 0/1 Receive (SP0RD/SP1RD, offset 86h/16h)6                     |    |

| 2.6.7 Serial Port 0 and 1 Baud Rate Divisor (SP0BAUD/SP1BAUD, offset 88h/18h)    | 54 |

| 2.6.8 Serial Port 0/1 RS485 / RS422 Control (SP0RS485/SP1RS485, offset 8Ah/1Ah)6 | 55 |

| 2.7 Serial Peripheral Interface (SPI) Port6                                      | 6  |

| 2.7.1 SPI Register Summary                                                       |    |

| 2.7.2 SPI Data (SPIDATA, Offset = 68h)6                                          |    |

| 2.7.3 SPI Control (SPICTRL, Offset = 6Ah)6                                       | 68 |

| 2.7.4 SPI Interrupt Control (SPICON, Offset = 4Ch)6                              | 68 |

| 2.7.5 SPI Status (SPISTAT, Offset = 6Ch)                                         |    |

| 2.7.6 SPI Slave Select (SPISSEL, Offset = 6Eh)                                   | 0  |

| 2.8 Programmable I/O Pins                                                        | 1  |

| 2.8.1 PIO Mode (PIOMODE0, offset 70h; PIOMODE1, offset 76h)7                     | 2  |

| 2.8.2 PIO Direction (PIODIRO, offset 72h; PIODIR1, offset 78h)7                  | 2  |

| 2.8.3 PIO Data (PDATA0, offset 74h; PDATA1, offset 7Ah)7                         | 3  |

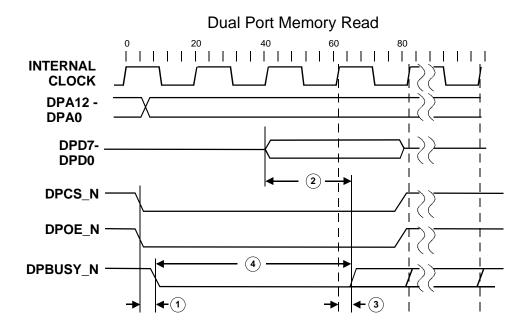

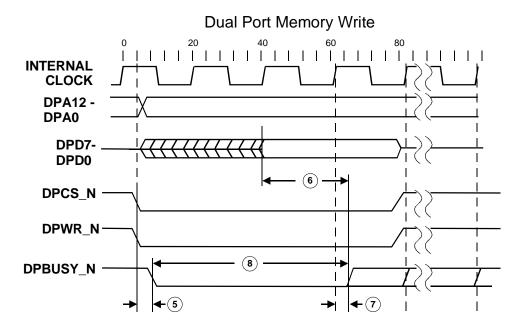

| 3 Dual Port RAM Memory 7                                                         | 75 |

| 3.1 Control Signals                                                              | _  |

| 3.1.1 Dual Port Memory Select (DPMS, Offset = AAh)                               |    |

| 3.1.2 Dual Port Memory Chip Select Assignments                                   |    |

| 3.2 Address Lines                                                                |    |

| 3.3 Data Lines                                                                   |    |

| 3.4 Interrupts                                                                   |    |

| 3.4.1 Interrupt Sources                                                          |    |

| 3.5 Busy Logic                                                                   |    |

| 3.6 Semaphores                                                                   |    |

| 3.7 Other Issues                                                                 |    |

| 4 External Non-Volatile Memory 8                                                 | 31 |

| 4.1 Parallel Flash                                                               |    |

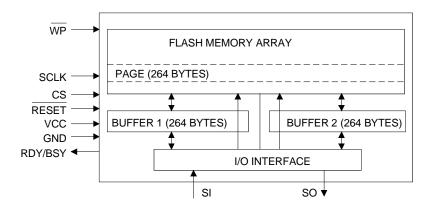

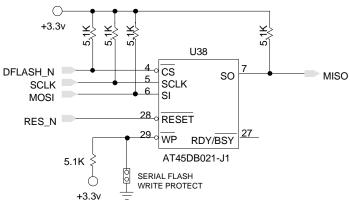

| 4.2 Serial Flash 8                                                               |    |

|                                                                                  | 37 |

DSTni-LX Data Book Table of Contents ● iii

| 6 BOOTSTrap ROM                                                             | 89  |

|-----------------------------------------------------------------------------|-----|

| 6.1 Bootstrap Description                                                   |     |

| 6.1.1 Memory                                                                |     |

| 6.1.2 Boot ROM                                                              | 90  |

| 6.1.3 RAM                                                                   | 90  |

| 6.1.4 Serial Flash                                                          | 90  |

| 6.1.5 Parallel Flash                                                        | 91  |

| 6.2 Bootstrap Operation                                                     | 91  |

| 6.2.1 Determine Operating Mode                                              |     |

| 6.2.2 Boot Checksum                                                         |     |

| 6.2.3 Hardware Initialization.                                              |     |

| 6.2.4 RAM Test                                                              |     |

| 6.2.5 Test for Serial Download                                              |     |

| 6.2.6 Test for Parallel Flash                                               |     |

| 6.2.7 Test for Serial Flash                                                 |     |

| 6.2.8 Serial Port Software Download to Flash                                |     |

| 6.2.9 Bootstrap LEDs                                                        |     |

| 6.3 Application Execution                                                   |     |

| 6.3.1 Execution from Serial Flash                                           |     |

| 6.3.2 Single Stage Load                                                     |     |

| 6.3.3 Two Stage Load                                                        |     |

| 6.3.4 Execution from Parallel Flash                                         |     |

| 6.3.5 Execute Directly from Flash.                                          |     |

| 6.3.6 Execute from RAM                                                      |     |

|                                                                             |     |

| 7 Ethernet                                                                  | 97  |

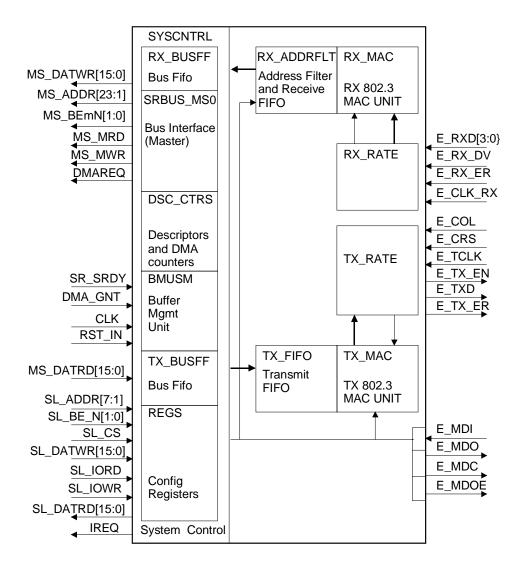

| 7.1 10/100MBps Ethernet Controller                                          | 97  |

| 7.1.1 Differences between the DSTni-LX Ethernet Controller and the AM79C960 |     |

| 7.2 Software Interface                                                      |     |

| 7.2.1 Initialization                                                        |     |

| 7.2.2 Descriptor Rings                                                      |     |

| 7.2.3 Descriptor Ring Polling                                               |     |

| 7.2.4 Transmit Descriptor Processing                                        | 105 |

| 7.2.5 Receive Descriptor Processing                                         | 106 |

| 7.2.6 MII Management functions                                              | 107 |

| 7.2.7 Reset                                                                 | 108 |

| 7.2.8 Speed selection                                                       | 109 |

| 7.2.9 Duplex mode                                                           | 109 |

| 7.2.10 Auto-Negotiation                                                     | 109 |

| 7.2.11 Restarting Auto-Negotiation.                                         |     |

| 7.2.12 Management frame                                                     | 112 |

| 7.2.13 Management Frame Format                                              | 112 |

| 7.3 Ethernet Operation                                                      | 113 |

| 7.3.1 Ethernet Interrupt (INT0)                                             |     |

| 7.3.2 Ethernet Interrupt Control Register                                   |     |

| 7.3.3 In-Service Register (INSERV, offset 2Ch)                              |     |

| 7.3.4 Interrupt Request Register (REQST, offset 2Eh)                        |     |

| 7.3.5 I/O Address Map                                                       |     |

| 7.3.6 MII Port Register                                                     |     |

| 7.3.7 Media Independent Interface (MII) Operation                           |     |

| () opening                                                                  |     |

| 8 CAN Controller                                          | 127 |

|-----------------------------------------------------------|-----|

| 8.1 CAN Overview                                          | 127 |

| 8.2 CAN Operation                                         | 128 |

| 8.2.1 CAN Interrupts (INT1 – INT2)                        | 129 |

| 8.2.2 CAN Interrupt Control Registers                     | 129 |

| 8.2.3 In-Service Register (INSERV, offset 2Ch)            |     |

| 8.2.4 Interrupt Request Register (REQST, offset 2Eh)      |     |

| 8.3 Internal Registers                                    |     |

| 8.3.1 Port Map of Internal Registers                      |     |

| 8.3.2 TX Message Registers                                | 132 |

| 8.3.3 Removing a message from a transmit holding register | 133 |

| 8.3.4 TxMessage Registers                                 | 134 |

| 8.3.5 RX Message Registers                                | 135 |

| 8.3.6 RxMessage Registers                                 | 135 |

| 8.3.7 Error Count and Status Registers                    | 137 |

| 8.3.8 Interrupt Flags                                     |     |

| 8.3.9 Interrupt Enable Registers                          |     |

| 8.3.10 CAN Operating Mode                                 |     |

| 8.3.11 CAN Configuration Registers                        |     |

| 8.3.12 Acceptance Filter and Acceptance Code Mask         |     |

| 8.3.13 CANbus Analysis                                    |     |

| 8.3.14 CAN Register Map                                   | 145 |

| 8.4 CAN Bus Interface                                     |     |

| 8.4.1 Interface Connections                               | 149 |

| 9 Profibus Controller                                     | 153 |

| 9.1 Interfacing to the ASPC2                              | 153 |

| 9.2 Profibus Operation                                    |     |

| 9.2.1 Profibus Interrupt                                  |     |

| 9.2.2 Profibus Interrupt Control Register                 |     |

| 9.2.3 In-Service Register (INSERV, offset 2Ch)            | 156 |

| 9.2.4 Interrupt Request Register (REQST, offset 2Eh)      |     |

| 9.2.5 Profibus Extended Control (PEC, offset 8Eh)         |     |

| 9.2.6 ASPC2 I/O Register Map                              |     |

| 9.2.7 ASPC2 SCB Memory Map                                | 161 |

| 9.3 Profibus Interface                                    |     |

| 9.3.1 Profibus DPV2 Diagnostic Port                       |     |

| 10 In-Circuit Emulator Support                            | 165 |

| 10.1 JTAG Interface                                       |     |

| 11 External Interfaces                                    | 167 |

| 11.1 System Bus                                           | 167 |

| 11.2 Interface to Dual Port Memory                        | 167 |

| 11.3 Interface to Serial Ports                            |     |

| 11.3.1 EIA/TIA-232                                        | 168 |

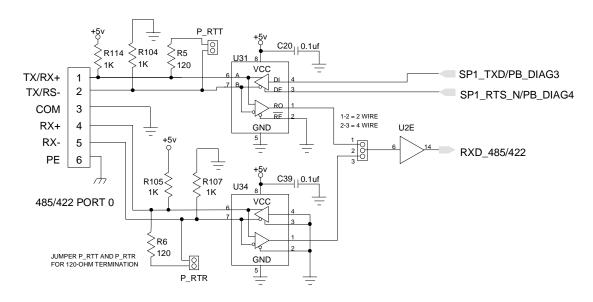

| 11 3 2 FIA/TIA-485                                        | 160 |

| 12 Elec              | ctrical Specifications                                | 171 |

|----------------------|-------------------------------------------------------|-----|

| 12.                  | .1 Operating Conditions                               | 171 |

| 12.                  | .2 Absolute Maximum Ratings                           | 171 |

| 12.                  | .3 DC Characteristics                                 | 171 |

| 12.                  | .4 Switching Parameters and Waveforms                 | 172 |

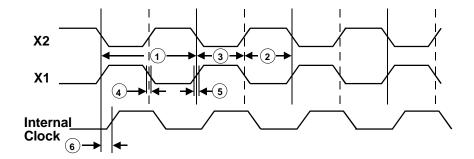

|                      | 12.4.1 Clock Switching Parameters                     |     |

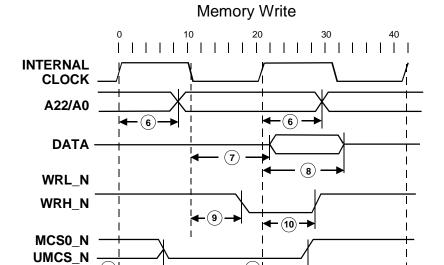

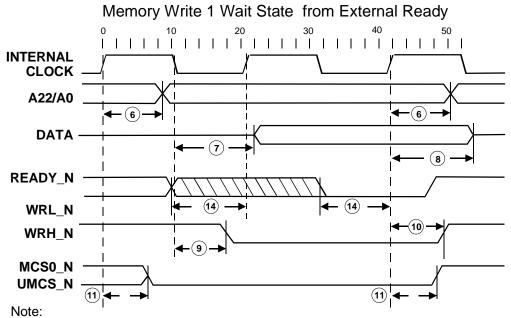

|                      | 12.4.2 Memory Write Parameters                        | 173 |

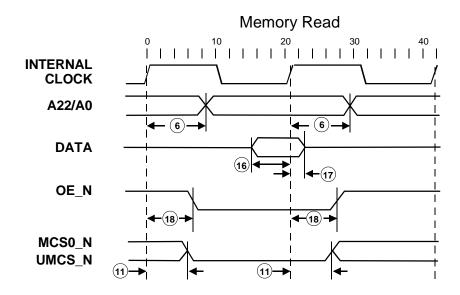

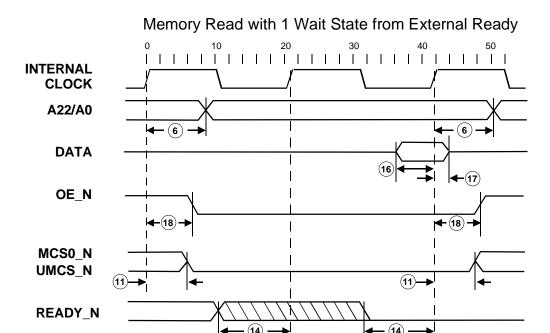

|                      | 12.4.3 Memory Read Parameters                         | 175 |

| 13 Pac               | kage Description                                      | 179 |

| 14 Source References |                                                       | 181 |

| 14.                  | .1 Atmel Corporation                                  | 181 |

|                      | 14.1.1 AT45DB021A Serial DataFlash®, Rev. 1642B-08/00 |     |

| Index                | 183                                                   |     |

vi • Table of Contents

# **List of Figures**

| Figure 1 - DSTni-LX Block Diagram                                        | 2   |

|--------------------------------------------------------------------------|-----|

| Figure 2 - Typical DSTni-LX System Block Diagram                         | 4   |

| Figure 3 - Block Diagram: Major Circuits                                 | 10  |

| Figure 4 - Block Diagram: Clock, Power, Timers                           | 11  |

| Figure 5 - Block Diagram: JTAG, DMA, Serial Ports                        | 11  |

| Figure 6 - Block Diagram: BUS Interface, Chip-Select, RAM ROM, PIO/DPRAM | 11  |

| Figure 7 - Block Diagram: Ethernet, SPI, CAN, ProfiBus                   | 12  |

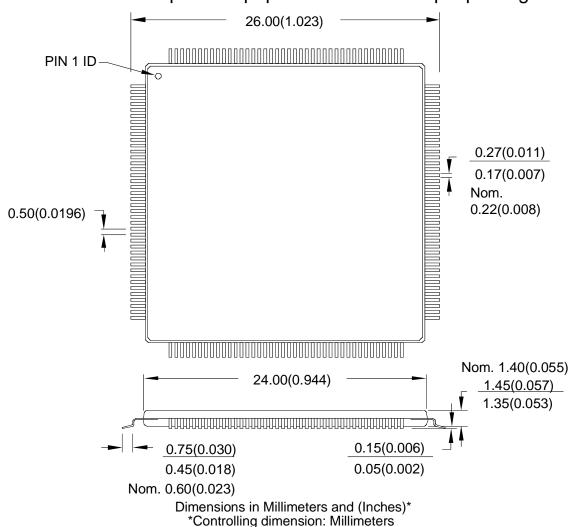

| Figure 8 - DSTni-LX 160-Pin Package                                      | 13  |

| Figure 9 - 48 MHz Clock                                                  | 28  |

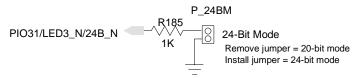

| Figure 10 - 24-Bit Address Option                                        | 29  |

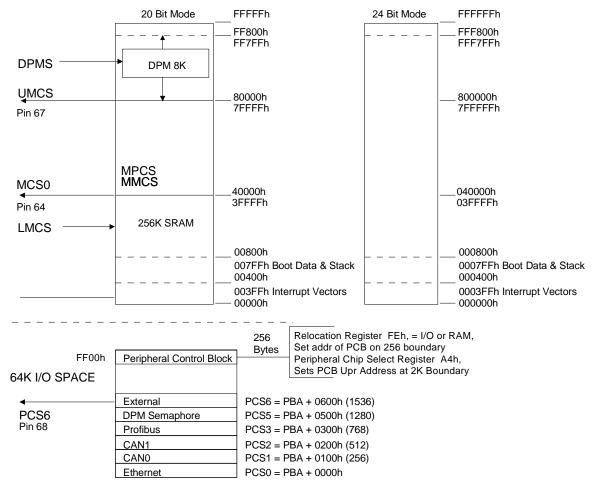

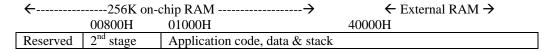

| Figure 11 - Memory Layout                                                |     |

| Figure 12 - External Parallel Flash Block Diagram                        |     |

| Figure 13 - 2MB Flash Circuit Diagram                                    | 82  |

| Figure 14 - Serial Flash Circuit Diagram                                 | 86  |

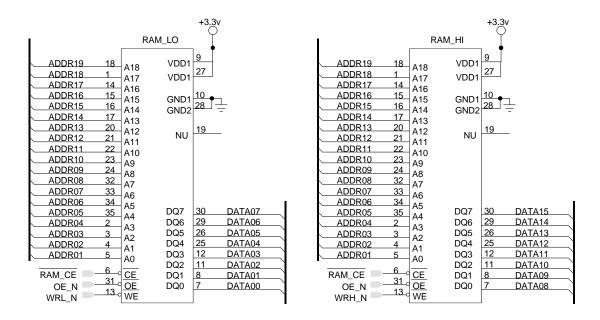

| Figure 15 - External RAM                                                 | 87  |

| Figure 16 - Bootstrap Memory Map                                         | 89  |

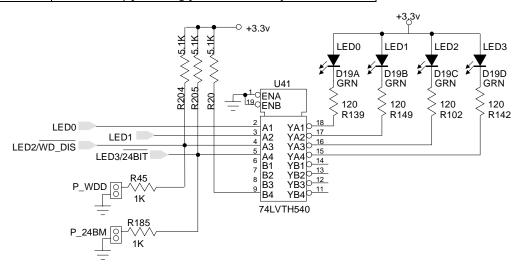

| Figure 17 - Bootstrap LEDs                                               | 93  |

| Figure 18 - Ethernet Controller Block Diagram                            | 99  |

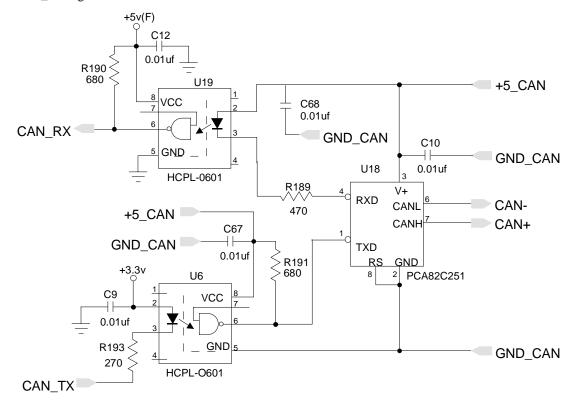

| Figure 19 - CAN Bus Interface                                            | 149 |

| Figure 20 - CAN Connector                                                | 149 |

| Figure 21 - Power for CAN                                                | 150 |

| Figure 22 - CAN Transceiver and Isolation Circuits                       | 151 |

| Figure 23 - Profibus 9-Pin DSUB Connector                                | 162 |

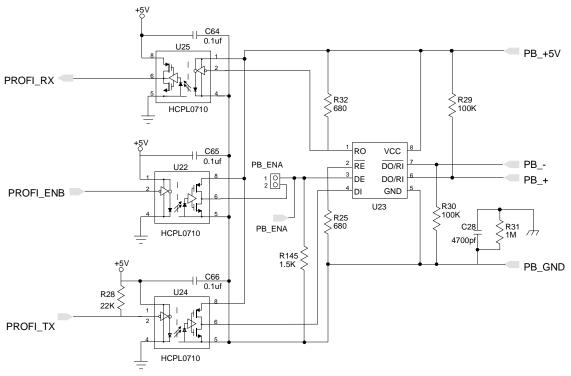

| Figure 24 - Profibus Interface Circuit Diagram                           | 162 |

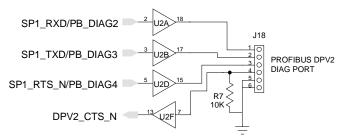

| Figure 25 - Profibus DPV2 Port Diagram                                   |     |

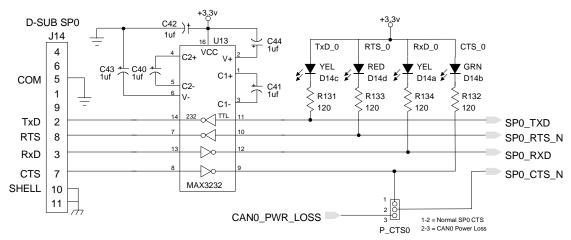

| Figure 26 - EIA/TIA-562 Circuit                                          |     |

| Figure 27 - EIA/TIA-485 Circuit                                          |     |

| Figure 28 - 160-Lead LQFP Package                                        |     |

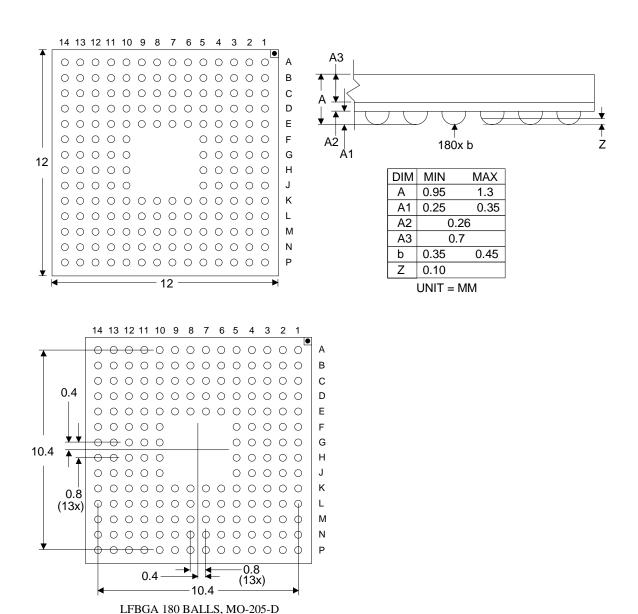

| Figure 29 - LX180BGA Package                                             |     |

|                                                                          |     |

## **List of Tables**

| Table I - Peripheral Register Offset Map                     | 32  |

|--------------------------------------------------------------|-----|

| Table 2 - Chip Select Registers                              |     |

| Table 3 - UMCS Base Address and Size                         | 36  |

| Table 4 - UMCS Wait State and Ready Select                   | 36  |

| Table 5 - MMCS Wait State and Ready Select                   | 37  |

| Table 6 - Chip Select Assignments                            | 40  |

| Table 7 - Peripheral I/O Address Assignments                 | 40  |

| Table 8 - Timer Registers                                    | 41  |

| Table 9 - WDT COUNT Settings                                 | 45  |

| Table 10 - WDT Duration                                      | 45  |

| Table 11 - Interrupt Sources                                 |     |

| Table 12 - External Interrupt Assignments                    | 48  |

| Table 13 - Interrupt Control Registers                       |     |

| Table 14 - DMA Controller Register Map                       | 53  |

| Table 15 - Serial Port Registers                             | 58  |

| Table 16 - Serial Port 1 DMA modes                           | 59  |

| Table 17 - Serial Port 0 DMA modes                           | 59  |

| Table 18 - Common Baud Rates                                 | 64  |

| Table 19 - SPI Registers                                     | 67  |

| Table 20 - Programmable I/O Pin Assignments                  | 71  |

| Table 21 - PIO Registers                                     |     |

| Table 22 - PIO Mode and Direction Combinations               | 73  |

| Table 23 - Serial flash page usage                           | 90  |

| Table 24 - Bootstrap LED Usage                               | 93  |

| Table 25 - Ethernet Controller Differences                   | 98  |

| Table 26 - Initialization Block Format                       |     |

| Table 27 - MII Management Register Set                       | 107 |

| Table 28 - MII Management - Control Register Bit Definitions | 108 |

| Table 29 - MII Status Register 1 Bit Definitions             | 111 |

| Table 30 - MII Management Frame Format                       |     |

| Table 31 - Ethernet I/O Address                              |     |

| Table 32 - CAN I/O Address                                   |     |

| Table 33 - CAN Interrupt Assignments                         |     |

| Table 34 - CAN Internal Registers                            |     |

| Table 35 - TxMessage_0 Registers                             | 134 |

| Table 36 - RxMessage Registers                               | 135 |

| Table 37 - Profibus I/O Address                              |     |

| Table 38 - Profibus Interrupt                                | 155 |

| Table 39 - DPV2 Mode pin assignments                         | 158 |

# **List of Registers**

| Register 1 - PCB Relocation Register, RELREG                                     | 33 |

|----------------------------------------------------------------------------------|----|

| Register 2 - Processor Release Level, PRL                                        | 33 |

| Register 3 - System Configuration Register, SYSCON                               | 33 |

| Register 4 - Auxiliary Configuration Register, AUXCON                            | 34 |

| Register 5 - Upper Memory Chip Select, UMCS                                      | 36 |

| Register 6 - Lower Memory Chip Select, LMCS                                      | 37 |

| Register 7 - Middle Memory Chip Select, MMCS                                     | 37 |

| Register 8 - Memory / Peripheral Control Select Register, MPCS                   |    |

| Register 9 - Peripheral Address Chip Select Register, PACS                       | 39 |

| Register 10 - Dual Port Memory Select, DPMS                                      | 39 |

| Register 11 - Timers 0-1 Mode / Control Registers, TOCON, T1CON                  |    |

| Register 12 - Timer 2 Mode / Control Register                                    |    |

| Register 13 - Timer Count Register, TOCNT, T1CNT, T2CNT                          |    |

| Register 14 - Timer Maxcount Register                                            | 44 |

| Register 15 - Watchdog Timer Control Register, WDTCON                            | 44 |

| Register 16 - In-Service Register, INSERV                                        |    |

| Register 17 - Interrupt Request Register, REQST                                  |    |

| Register 18 - Interrupt Mask Register, IMASK                                     | 50 |

| Register 19 - Interrupt Priority Mask Register, PRIMSK                           | 50 |

| Register 20 - Interrupt Status Register, INTSTS                                  |    |

| Register 21 - Internal Peripheral Interrupt Registers                            | 51 |

| Register 22 - External Interrupt Control Registers, IxCON                        |    |

| Register 23 - End of Interrupt Register, EOI                                     | 52 |

| Register 24 - Poll and Poll Status Registers, POLL/POLLST                        | 52 |

| Register 25 - DMA Control Registers, DxCON                                       | 53 |

| Register 26 - DMA Destination Address High Register, DxDSTH                      | 55 |

| Register 27 - DMA Destination Address Low Register, DxDSTL                       |    |

| Register 28 - DMA Source Address High Register, DxSRCH                           | 55 |

| Register 29 - DMA Source Address Low Register, DxSRCL                            |    |

| Register 30 - DMA Transfer Count Register, DxTC                                  |    |

| Register 31 - Serial Port 0 and 1 Control Registers, SPOCT, SP1CT                |    |

| Register 32 - Serial Ports 0 and 1 Status Registers, SP0STS, SP1STS              |    |

| Register 33 - Serial Port 0 Transmit Registers, SP0TD, offset 84h                |    |

| Register 34 - Serial Port 1 Transmit Registers, SP1TD, offset 14h                |    |

| Register 35 - Serial Port 0 Receive Registers, SPORD, offset 86h                 |    |

| Register 36 - Serial Port 1 Receive Registers, SP1RD, offset 16h                 | 63 |

| Register 37 - Serial Port 0 Baud Rate Divisor Register, SP0BAUD, offset 88h      |    |

| Register 38 - Serial Port 1 Baud Rate Divisor Register, SP1BAUD, offset 18h      | 64 |

| Register~39-Serial~Port~0~RS485/RS422~Control~Register,~SP0RS485,~offset~8Ah     | 65 |

| Register 40 - Serial Port 1 RS485 / RS422 Control Register, SP1RS485, offset 1Ah |    |

| Register 41 - SPI Data Register, SPIDATA                                         |    |

| Register 42 - SPI Control Register, SPICTRL                                      |    |

| Register 43 - SPI Interrupt Control Register, SPICON                             | 68 |

| Register 44 - SPI Status Register, SPISTAT                                       |    |

| Register 45 - SPI Slave Select Register, SPISSEL                                 | 70 |

| Register 46 - PIO Mode 1 Register, PIOMODE1                       | 72  |

|-------------------------------------------------------------------|-----|

| Register 47 - PIO Mode 0 Register, PIOMODE0                       | 72  |

| Register 48 - PIO Direction 1 Register, PIODIR1                   | 72  |

| Register 49 - PIO Direction 0 Register, PIODIR0                   | 72  |

| Register 50 - PIO Data 1 Register, PDATA1                         | 73  |

| Register 51 - PIO Data 0 Register, PDATA0                         |     |

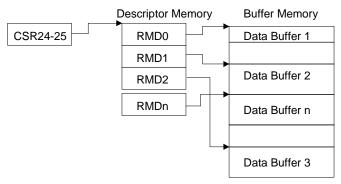

| Register 52 - RMD0: ADR[15:0]                                     | 102 |

| Register 53 - RMD1: Status                                        | 102 |

| Register 54 - RMD2: Buffer Byte Count, BCNT                       | 103 |

| Register 55 - RMD3: Message Byte Count, MCNT                      | 103 |

| Register 56 - TMD0: ADR[15:0]                                     | 103 |

| Register 57 - TMD1: Status                                        | 103 |

| Register 58 - TMD2: Buffer Byte Count, BCNT                       | 104 |

| Register 59 - TMD3: Error Status                                  | 104 |

| Register 60 - Ethernet Interrupts                                 | 114 |

| Register 61 - External Interrupt Control Register, IOCON          | 114 |

| Register 62 - In-Service Register for Ethernet                    |     |

| Register 63 - Interrupt Request Register for Ethernet             |     |

| Register 64 - CSR0: Status Register                               |     |

| Register 65 - CSR1: Initialization Address Register, IADR[15:0]   |     |

| Register 66 - CSR2: Initialization Address Register, IADR[23:16]  |     |

| Register 67 - CSR3: Interrupt Mask Register                       |     |

| Register 68 - CSR4: Features Control                              |     |

| Register 69 - CSR8: Reserved                                      | 120 |

| Register 70 - CSR9: Reserved                                      |     |

| Register 71 - CSR10: Reserved                                     |     |

| Register 72 - CSR11: Reserved                                     | 120 |

| Register 73 - CSR12: PADR[15:0]                                   | 120 |

| Register 74 - CSR13: PADR[31:16]                                  | 120 |

| Register 75 - CSR14: PADR[47:32]                                  | 120 |

| Register 76 - CSR15: Mode Register                                | 121 |

| Register 77 - CSR16: Initialization Address Register, IADR[15:0]  | 122 |

| Register 78 - CSR17: Initialization Address Register, IADR[23:16] | 122 |

| Register 79 - CSR24: Base Address of RX ring[15:0]                | 122 |

| Register 80 - CSR25: Base Address of RX ring[23:16]]              |     |

| Register 81 - CSR30: Base Address of TX ring[15:0]                | 122 |

| Register 82 - CSR31: Base Address of TX ring[23:16]]              | 122 |

| Register 83 - CSR46: Poll Time Counter, POLL                      | 122 |

| Register 84 - CSR47: Polling Interval, POLLINT                    | 123 |

| Register 85 - CSR76: Receive Ring Length, RXLEN                   | 123 |

| Register 86 - CSR78: Transmit Ring Length, TXLEN                  | 123 |

| Register 87 - CSR88-89: Chip ID                                   | 123 |

| Register 88 - CSR112: Missed Frame Count, MFC                     | 123 |

| Register 89 - CSR114: Receive Collision Count, RXCC               | 124 |

| Register 90 - MII Port Register, MIIP                             | 124 |

| Register 91 - External Interrupt Control Registers, I1CON & I2CON |     |

| Register 92 - In-Service Register for CAN                         |     |

| Register 93 - Interrupt Request Register for CAN                  |     |

| Register 94 - External Interrupt Control Register, I3CON          |     |

| Register 95 - In-Service Register for Profibus                    |     |

x ◆ List of Registers DSTni-LX Data Book

| Register 96 - Interrupt Request Register for Profibus | 157 |

|-------------------------------------------------------|-----|

| Register 97 - Profibus Extended Control, PEC          | 157 |

DSTni-LX Data Book List of Registers ◆ xi

## 1 Introduction

## 1.1 Purpose of This Manual

This manual describes the technical features and programming interface of the DSTni-LX-001/-002 Communications Single Chip Solution (SCS) device. This manual is intended for hardware engineers, software engineers, and system integrators who are considering using the DSTni-LX in their designs.

| 1.2 Manual Overview                                                 |        |

|---------------------------------------------------------------------|--------|

| The information in this manual is organized into the following chap | oters: |

| 1 Introduction                                                      | 1      |

| 2 Peripheral Control Block                                          | 31     |

| 3 Dual Port RAM Memory                                              | 75     |

| 4 External Non-Volatile Memory                                      | 81     |

| 5 External RAM                                                      | 87     |

| 6 Bootstrap ROM                                                     | 89     |

| 7 Ethernet                                                          | 97     |

| 8 CAN Controller                                                    | 127    |

| 9 Profibus Controller                                               | 153    |

| 10 In-Circuit Emulator Support                                      | 165    |

| 11 External Interfaces                                              | 167    |

| 12 Electrical Specifications                                        | 171    |

| 13 Package Description                                              | 179    |

| 14 Source References                                                | 181    |

DSTni-LX Data Book Introduction ◆ 1

## 1.3 General Description

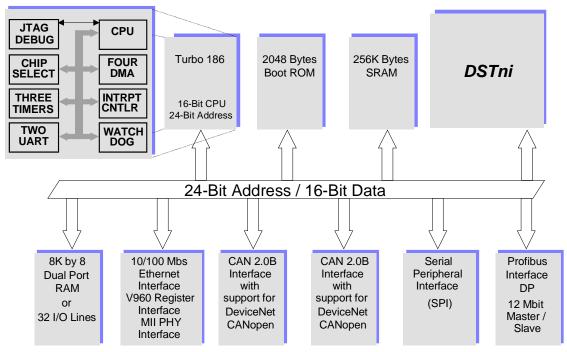

The DSTni-LX contains all of the necessary functions to support the most requested embedded communication technologies. This device provides Intel 80186 compatibility to existing software, while providing 12.5 MIPS of processor performance as a platform that is capable of handling the most demanding embedded communication tasks. Designed as a synchronous device providing multiple networks, the DSTni-LX has on board support for multiple CAN channels, Profibus (DSTni-LX-002), Ethernet, RS232, RS422 & RS485. To provide the highest performance possible, the DSTni-LX has on-board 256K Bytes of high-speed (10ns) SRAM, 8Kx8 dual port memory for co-processor applications and an SPI interface for communications to serial flash or other SPI networking applications.

<sup>\*</sup> Profibus interface is available in DSTni-LX-002

Figure 1 - DSTni-LX Block Diagram

2 • Introduction DSTni-LX Data Book

### 1.4 Key Features & Benefits

- Intel compatible 80186 16-bit microprocessor with on-chip peripherals operating at 48Mhz and providing 12+ MIPS of high-speed performance

- AMD 960 compatible 10/100 Mbps Ethernet controller with MII PHY interface

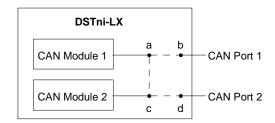

- Two CAN V2.0B 1 Mbps fully compatible with the Bosch specification.

- Profibus DP master/slave controller (100% Siemens ASPC2 compatible)(DSTni-LX-002 only)

- Two asynchronous RS232/422/485 serial channels, RTS/CTS and DMA support

- 256K bytes of SRAM memory, 2K bytes of boot ROM

- 8K bytes of dual port memory with interrupt and semaphore support

- Integrated DMA, interrupt controller, timers, Watchdog timer, and memory select logic

- External 16M byte addressable memory space (24-bit mode)

- 32 I/O pins or dual port memory interface

- 160-Pin LQFP package, 180BGA Package

- JTAG interface with in-circuit emulator support for breakpoints and trace buffer

- Industrial temperature specifications

## 1.5 Hardware Description

DSTni-LX features a high performance (12.5 MIPS) Intel 80186 compatible device operating at 48Mhz.

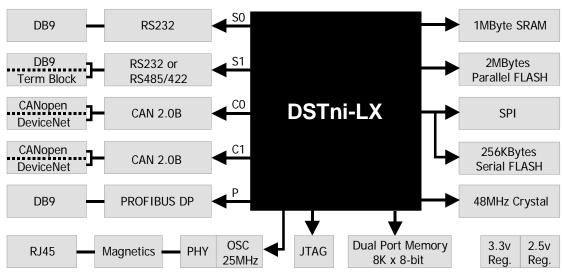

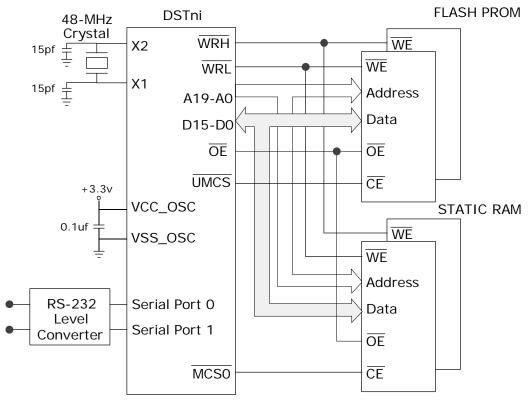

This chip combines a powerful microprocessor with on-chip memory and all required communication peripherals. For simple stand-alone applications, the DSTni-LX can be implemented as the primary microprocessor in the system and simply interfaced to required external components (see

Figure 2 - Typical DSTni-LX System Block Diagram). In more complex multi-processor applications, the DSTni-LX is applied as a co-processor and uses an on board 8k x 8 dual-port memory for two-way communications between the host processor and the DSTni-LX microprocessor.

Required peripherals of the DSTni-LX include an external serial flash device or parallel non-volatile memory (flash or EPROM) to load the 256K of internal RAM memory, a crystal/oscillator and any required transceiver components for the supported communication controllers. If serial or parallel Flash are not used, the serial port (SP0) can be used to download programs to the internal RAM.

The DSTni-LX is designed to use standard x86 development tools and operating systems for ease of development and to leverage existing software source code. Having been designed to be an effective solution for various communications technologies that are used in industrial communications, the DSTni-LX is ideal for medical electronics (see warning below), vehicle electronics, building control, embedded communications or web servers, protocol converters, and other intelligent commercial and industrial applications.

#### **WARNING:**

The DSTni-LX should NOT be used as a critical component in life-support devices or systems.

#### 1.5.1 High Performance 16-Bit Microprocessor

The DSTni-LX has an on-chip 80186 compatible, 16-bit microprocessor with its related peripherals (interrupt controller, timer, chip select logic). This microprocessor has additional features to support a

DSTni-LX Data Book Introduction • 3

24-bit address space, which allows up to 16M bytes of memory to be used. Internally, the DSTni-LX has 16-bit wide, 256K bytes of SRAM memory (20-bit mode), for maximum performance.

The turbo 186 microprocessor is the heart of the DSTni-LX controller. The microprocessor executes the software or firmware loaded in internal or external memory. The microprocessor instruction set is software compatible with the Intel/AMD 80186 and 80188 microprocessors and uses standard compilers and development tools for Intel x86 microprocessors. This allows the DSTni-LX to be fully software compatible with 8086, 8088, 80186, and 80188 family of processors. Normally, an 80186-48Mhz microprocessor executes instructions between 4-12 clock cycles. The DSTni-LX microprocessor has been enhanced to execute instructions in 1-4 clock cycles, thus giving 12.5 MIPS of performance.

Figure 2 - Typical DSTni-LX System Block Diagram

#### 1.5.2 Programmable Timers

The integrated timers provide a software vehicle to count or time external events. Each timer is equipped with a max count register, which defines the maximum count the timer will reach. Timer 0 and 1 each have two max counts registers. The programmer has the option of either normal timing functionality or when enabled, these timers can be defined to alternate. Timer 0 has an output that can be used to generate waveform signals with programmable duty cycles.

4 • Introduction DSTni-LX Data Book

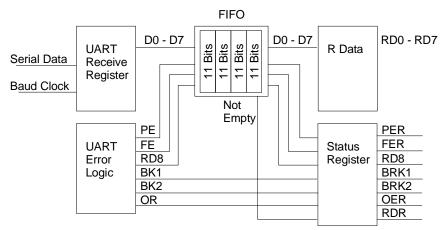

#### 1.5.3 Asynchronous Serial Ports

The DSTni-LX provides two asynchronous serial ports. These ports provide a read/write port for full duplex operation with programmable baud rate up to 230400. Any combination of the following are supported:

- 7 or 8-bit data transfers

- 1 or 2 stop bits

- Even, odd or no parity

The receive portion of the serial ports provides break character recognition and error detection for frame, parity and overrun errors. In addition, they are programmable to generate interrupts whenever one of these error conditions is detected. Interrupts can be generated by the serial port to signal that the transmitter is available to accept a new character or that valid data has been received. Both of the serial channels support RTS/CTS control signals and DMA control. An additional register has been added to support high-speed protocols and signaling for RS-422/485.

#### 1.5.4 Interrupt Controller

The DSTni-LX integrated interrupt controller manages and prioritizes the internal and external interrupt sources. Internal interrupt sources include the Timers and DMA channels. These sources can be disabled by their own control register or by the mask bits within the interrupt controller.

#### 1.5.5 SPI Controller

The Serial Peripheral Interface (SPI Controller) provides communication with external devices in master mode. The SPI also supports communication between processors if an external processor is connected to the system. The DSTni-LX uses the SPI port to load from serial flash all boot strap data to initiate operation.

#### 1.5.6 Hardware Watchdog Timer

The DSTni-LX has been developed to provide the developer with a configurable Watch Dog Timer. This externally accessible pin (wdog\_n) can be used to monitor the on board DSTni-LX CPU. The Watch Dog Timer (WDT) is a count-down counter that is reset via software at a programmable periodic rate. Should the WDT count down to zero it will reset the DSTni-LX CPU.

#### 1.5.7 10/100 Mbps Ethernet Controller

The DSTni-LX has an Ethernet 10/100 Mbps controller with Media Independent Interface (MII), and is register compatible with the Advanced Micro Devices AM79C960. Supported protocols are: IEEE 802.3 and ANSI88023. Additionally, the DSTni-LX has a buffer for message receive and transmit.

#### 1.5.8 Static RAM

The DSTni-LX additionally provides 256K bytes of on-chip zero wait state 10NS static RAM (20-bit mode). The bootstrap will zero this SRAM after reset. The static RAM is 16 bits wide internally, which allows for maximum microprocessor performance. The 160-pin package has been designed to bring out all data lines to access the full externally supplied 16M Bytes of memory (24-bit mode).

#### 1.5.9 Profibus DP Master/Slave Controller

The DSTni-LX-002 has a fully licensed Siemens Profibus core providing master or slave capability. Profibus DP Master/ Slave is a European standard for industrial communications. It supports up to 12 Mbps baud rate, with up to 128 devices, and was designed to use Siemens configuration tools.

DSTni-LX Data Book Introduction ● 5

#### 1.5.10 Boot ROM Memory

The DSTni-LX has on-chip Boot ROM of 2048 bytes, which supports loading of code from any of the following:

- Serial flash device

- Parallel non-volatile memory (flash or EPROM)

- Serial port (SP0)

#### 1.5.11 Dual Port Memory Shares 32 I/O Pins

Each of the 32 user-programmable I/O pins can be configured for normal operation, as inputs or outputs. Several different registers are provided for I/O control. Specifically, the mode and direction registers are used to establish I/O characteristics of each pin. All 32 I/O pins contain either an internal pull-down or pull-up circuit regardless of the function selected. The DSTni-LX has 8K bytes of 8-bit wide dual port memory, which is functionally compatible with the Integrated Device (IDT) dual port memory IDT7005 chip. When enabled, the dual port memory is made available as shared pins on 27 of the 32 I/O pins. If the dual port memory is not required, the 27 I/O pins are available as user defined I/O.

#### 1.5.12 Dual 1 Mbps CAN Controllers

The DSTni-LX provides two individual CAN-2.0B channels. These CAN channels have been designed to function with high levels of data integrity in extremely noisy electrical environments. Both channels are capable of high-speed (1 Mbits/s) data transmission over short distances (40 m) and low-speed (5 kbits/s) transmissions at lengths of up to 10,000 meters. The multi-master CAN bus is highly fault tolerant, with powerful error detection and handling. The DSTni-LX adds filtering, input and output queues, and complete diagnostics bits; which provides significant feature enhancements over competitive products.

#### 1.6 Communication Protocols

#### 1.6.1 CAN

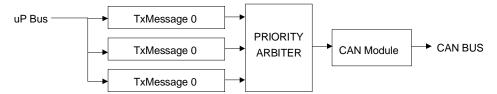

Included among the onboard communications peripherals are two, totally independent CAN controllers. Both channels are 100% Version 2.0B compliant. The maximum Baud rate is 1Mbps. Each CAN channel is integrated with a simple 16-bit internal I/O interface. There are 62, 16 bit Read/Write registers for each channel that allow full access and control of all CAN functions. The DSTni-LX with an internal CAN interface results in a major performance increase over typical 8-bit external CAN interfaces. This performance increase is directly related to the 48Mhz system clock speed, which is a true 16-bit synchronous data access interface, with no external timing constraints that typically add wait states

Another distinguishing feature of the DSTni-LX CAN interfaces are the transmit holding registers. Each channel contains 3 separate transmit holding registers, which integrate a "Priority Arbiter." This provides a two-fold advantage.

- 1. This allows "queuing" of any outgoing CAN messages, which reduces processor loading of the application.

- 2. The "Priority Arbiter" allows you to override a pending lower priority message that is already in one of the transmit buffers.

6 ● Introduction DSTni-LX Data Book

This is extremely useful for CAN protocols that require "SYNC" messages to be sent at defined intervals. Included in the design is a "listen-only" mode for CAN diagnostic and/or bus analyzing. Additionally, inclusion of 2 CAN channels makes this device a perfect candidate for simultaneous control and diagnostics of a CAN bus. A typical example of this flexibility is the use of CAN channel 1 as an active master or slave while using CAN channel 2 in the listen only mode for analyzing all CAN bus activity.

These features allow efficient, modular application software to be written since each channel operates independently. Having separate interrupts also enhances modularity.

Listed below are some of the notable features for each DSTni-LX CAN channel:

#### Processor Interface

- 14, fully programmable interrupt sources

- Fully synchronous, 0-wait states, efficient 16-bit data interface

- Simple 16-bit I/O access

- Internal "Loop-Back" mode for diagnostics

- Control and Status registers

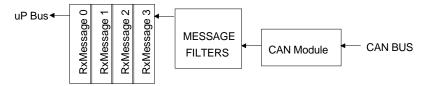

3 fully programmable ACR (Acceptance Code Reg.) and AMR (Acceptance Mask Reg.) filters

- Receive Message filter includes: Full 29- bit ID, IDE, RTR, and 16 data bits

- Separate enable bit for all 3 filters

#### **Transmitter Features**

- 3 separate Transmitter holding registers

- Transmitter priority arbiter

- Transmission Abort function (pending messages still in registers)

#### Receive Features

- 4 deep receive message (14 bytes per message) FIFO

- FIFO Level status indicator with programmable threshold

#### Special CAN Features

- Listen only mode

- Supports both 11-bit ID and 29-bit ID

- Arbitration lost capture Error register

- Error event capture that includes an actual frame reference pointer to pinpoint errors

DSTni-LX Data Book Introduction ● 7

#### 1.6.2 Profibus

Profibus is a one of several vendor-independent, open field-bus communication networks supported by the DSTni-LX-002. Profibus allows communication between devices of several different manufacturers on one network that comply with the international standards of EN 50170 and EN 50254. Profibus can be used for both high-speed time critical applications and complex communication tasks. The networking technology of Profibus is based on serial field bus systems for networking of distributed Non-or Intelligent programmable devices. Operation to 12Mbits/second is fully supported.

The DSTni-LX-002 Profibus feature is a multi-master system that allows joint operation of several automation, engineering or visualization systems and peripherals on one bus. Commonly called Profibus DP, the node definitions are as follows:

#### Master

These devices control the data communication on the bus. A master can send messages without an external request when it holds the bus access rights, which is called a token. Masters are also called active stations.

#### Slave

These are peripherals such as I/O devices, valves, drives and measuring transducers. Slave devices do not have bus access rights and they can only acknowledge received messages or send messages to the master when requested.

The DSTni-LX-002 supports both I/O and complex data transfer using Profibus. The Profibus DP implementation on the DSTni-LX-002 has been highly optimized for speed, ease of development and low connection costs. The most typical applications are for communication between automation systems and distributed peripherals. DSTni-LX-002 Profibus DP is suitable as a replacement for conventional, parallel signal transmission operating at 24 VDC in manufacturing automation as well as for analog signal transmissions implementing 4 to 20 mA technologies found in process automation.

The DSTni-LX-002 also includes all of the latest feature sets of Profibus DP communications, which include both DPV-1 & 2 extensions.

#### 1.6.3 Ethernet

Ethernet is a mature networking solution with hundreds of vendors providing hardware and software products. Presently, Ethernet is widely used as the network backbone for businesses, government and educational institutions. Most recently, the embedded application world has taken a new look at the deployment of Ethernet in other applications that have only been proprietary in the past. One such application is for Industrial Automation.

Since its original inception in the early 1980s, the Ethernet standard has been updated and expanded to support higher data rates and more predictable throughput. Ethernet is now available at speeds of 10 Mbps, 100 Mbps and 1000 Mbps (Gigabit), full duplex or half duplex operation; and provides a variety of bus technologies, such as twisted pair wire, fiber optic cable and wireless.

The DSTni-LX on-chip Ethernet controller provides a choice 10 Mbps or 100 Mbps data rates and either full or half duplex operation. The controller interface is software compatible with the Am79C960 Ethernet Controller from AMD.

The DSTni-LX Ethernet controller uses its Media Independent Interface (MII) to interface with an Ethernet transceiver (PHY), such as the Level One LTX971. The MII provides the means to set parameters in the PHY such as data rate, full or half duplex and loopback. This provides a raw Ethernet packet interface that allows developers to implement their own network protocols over Ethernet.

8 • Introduction DSTni-LX Data Book

### 1.7 Development Tools

The development environment for the DSTni-LX is the standard x86 tools. One of the development kits contains an in-circuit emulator (ICE) that communicates with the DSTni-LX through the JTAG port. The ICE tools allows the developer to load software, set breakpoints, view trace buffer, and many other standard ICE functions. The Paradigm C compiler with a 24-Bit supported tool set is available.

#### 1.7.1 Paradigm

Paradigm C++ features a powerful integrated development environment (IDE), which permits all the tools needed for software development to be completely integrated. Now all the commonly used tools such as editors, browsers, compilers, debuggers, and source version control are available in one place, taking x86 software development to a new level of productivity. Paradigm C++ operates on Windows 95/98, Windows NT 4.0, Windows 2000 or Windows ME.

#### 1.7.2 FS<sup>2</sup> ICE

The VSA-8X/18X System Analyzer from FS² was designed to support the special features and integrated peripherals of the DSTni-LX product. Special "silicon hooks" were integrated into the DSTni-LX that support "On-Chip" extensions, which provides a powerful debug tool with advanced features.

The VSA-8X/18X debugger is contained in a compact chassis that connects to the target system using a standard 20-pin AMP debug connector. It requires access to only 4 pins in the core processor. The system runs on a Windows® 95/98/NT/2000 PC over an IEEE-1284 EPP/ECP high speed parallel port. An optional graphical, source level debugger program provides an intuitive, easy to use interface.

#### 1.7.3 Developers Evaluation Kits

Three evaluation kits are available. They contains software and/or hardware components suitable for initial setup and development of an operating communication system.

Kits may include:

- FS2 In-Circuit Emulator (ICE) /Debugger

- Paradigm C++ Integrated Development Environment (IDE), including 20 and 24-bit data addressing, editors, browsers, compilers, assemblers, linkers, locaters, and debuggers.

- Real-time Operating System (RTOS)

- DSTni-LX Hardware/software documentation

Optional components: Please refer to the software stacks and other modules in the price list.

DSTni-LX Data Book Introduction • 9

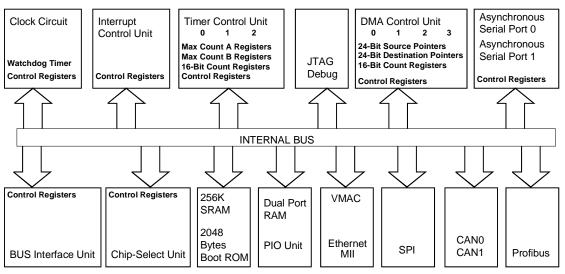

## 1.8 System Diagram

### 1.8.1 DSTni-LX Block Diagram

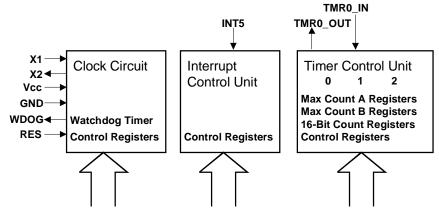

The major circuits of the DSTni-LX are shown in the following diagram. Profibus is available only on the DSTni-LX-002.

Figure 3 - Block Diagram: Major Circuits

10 ◆ Introduction DSTni-LX Data Book

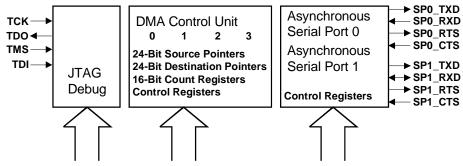

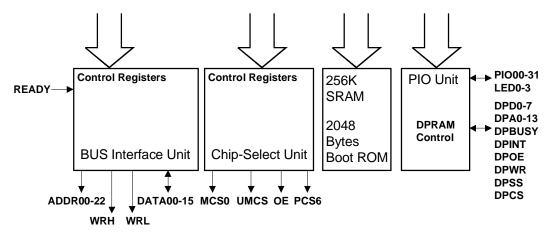

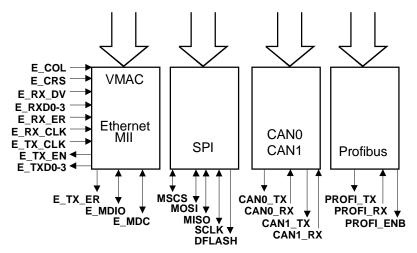

The following diagrams show the major blocks with associated pins.

Figure 4 - Block Diagram: Clock, Power, Timers

Figure 5 - Block Diagram: JTAG, DMA, Serial Ports

The four pins for Serial Port 1 are multiplexed to provide for support for the Profibus DPV2 Isochron Mode of Operation.

Figure 6 - Block Diagram: BUS Interface, Chip-Select, RAM ROM, PIO/DPRAM

DSTni-LX Data Book Introduction ● 11

Figure 7 - Block Diagram: Ethernet, SPI, CAN, ProfiBus

Note: MSCS is used for SPI Master Collision Input. DFLASH is used for SPI Slave 0 Select or Serial Flash.

## 1.9 Programming

The DSTni-LX contains the same basic set of registers, instructions, and addressing modes as the industry-standard 186 microcontroller. For more information about the register set, memory organization, I/O space, instruction set, segments, data types and addressing modes, see the following document.

The Am186 and Am188 Family Instruction Set Manual, order# 21267

## 1.10 System Overview

#### 1.10.1 DSTni-LX Package Options

The DSTni-LX is an enhanced 80186 16-bit microprocessor with integrated interrupt controller, 3 timers, 4-channel DMA controller, external chip selects, watchdog timer and JTAG port. All DSTni-LX chips contain 256KB SRAM, 2 KB Boot ROM, 8 KB dual-port RAM, 2 Serial Ports, 2 CAN 2.0B ports, and an SPI port.

| Part Number    | 160 Pin<br>LQFP<br>Device | 180 Pin<br>BGA<br>Device | 16 Mb<br>External<br>Memory | Two (2)<br>CAN<br>Channels | Profibus<br>Master/Slave | 10/100<br>Ethernet<br>MAC |

|----------------|---------------------------|--------------------------|-----------------------------|----------------------------|--------------------------|---------------------------|

| DSTni-LX-001   | •                         |                          | •                           | •                          |                          | <b>*</b>                  |

| DSTni-LX-002   | •                         |                          | •                           | •                          | •                        | <b>*</b>                  |

| DSTni-LX-180BP |                           | •                        | •                           | •                          | •                        | <b>*</b>                  |

12 ◆ Introduction DSTni-LX Data Book

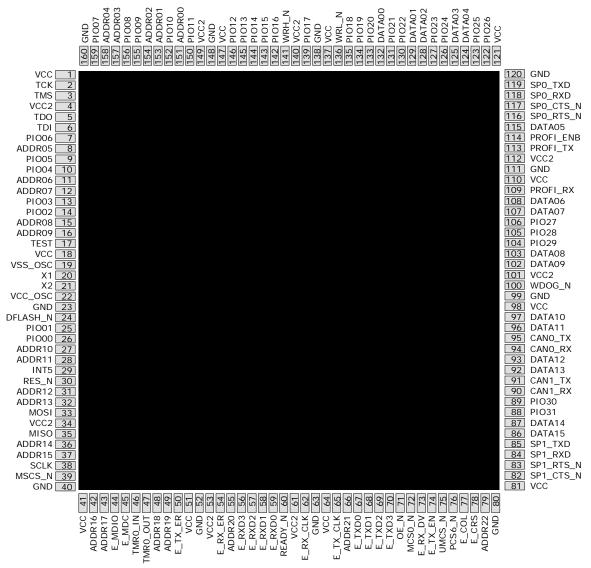

#### 1.10.2 DSTni-LX 160-Pin Package

Figure 8 - DSTni-LX 160-Pin Package

DSTni-LX Data Book Introduction ● 13

## 1.10.3 Pin Descriptions

| ADDR22 –<br>ADDR00 | Address Bus<br>(Outputs)     | These 23 signals are output pins. They supply non-multiplexed memory or I/O addresses to the connected system. ADDR22 is the MSB and ADDR00 is the LSB. <b>NOTE:</b> Although not available as an external pin, ADDR23 is internally used and is the MSB of the Address Bus. All lines are always enabled which means they do not enter a high-impedance state. Following a system reset, ADR22-20 remain in the logic low state for "Real" or 20-bit mode. In "extended" or 24-bit mode, ADR22-20 function as normal address lines.                                                                        |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA15 –<br>DATA00 | Data Bus<br>(Bi-Directional) | These 16 signals make up the external Data Bus pins. DATA15 is the MSB and DATA00 is the LSB. This Data Bus is bi-directional to allow system data to be passed in and out through READ and WRITE accesses respectively. This bus also goes into the high-impedance state when the system is not accessing external I/O or memory.                                                                                                                                                                                                                                                                          |

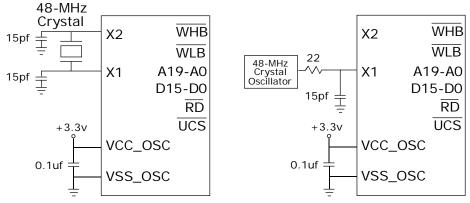

| X1                 | Crystal Input                | This pin and the X2 pin provide connections for the internal oscillator circuit. If an external crystal is used, the X2 pin is required as well. For external clock or oscillator circuits with digital output drivers, this pin can be connected directly and the X2 pin is left unconnected. See 48MHz Clock, page 28, for information about selecting crystals and using a crystal oscillator.                                                                                                                                                                                                           |

| X2                 | Crystal Output               | This pin and the X1 pin provide connections for the internal oscillator circuit (see X1 description above). See 48MHz Clock, page 28, for information about selecting crystals and using a crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                              |

| RES_N              | Reset<br>(Input)             | This input pin forces the microcontroller to perform a reset. When RES_N is asserted, the microcontroller immediately terminates its present activity, clears its internal logic, and CPU control is transferred to the reset address, FFFF0h (20-bit mode) or FFFFE0H (24-bit mode). Note this processor has an internal 2048 bytes of "BOOT-ROM" located at the top of the address space, so execution will always start here when reset occurs. Any externally connected devices in the reset vector address will be overridden by the internal logic. See the "BOOTSTRAP ROM" section for more details. |

| TCK                | JTAG Clock<br>(Input)        | The JTAG interface is used by the In-Circuit Emulator to access the hardware registers that support the breakpoint and trace functions. The four interface pins are TCK, TMS, TDI, and TDO. See the "In-Circuit                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                | JTAG Mode<br>(Input)         | Emulator" section for more details.  The ESD tolerance for the TDO output, pin 5 is only about 500 Volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TDI                | JTAG Data In<br>(Input)      | This output is used by the JTAG interface to the FS-2 In-System Emulator. ESD precautions such as a grounded work area, using wrist straps, and making the connection, or removing the connection when the                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDO                | JTAG Data Out<br>(Output)    | power is off, need to be used. When the JTAG interface is not being used, there is no issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WDOG_N             | Watchdog<br>(Output)         | This output pin is used to indicate that a Watchdog Reset or timeout has occurred. The signal is active low and will revert back to high when the processor has gone through the reset vector. Typically this output signal is used to reset or signal external circuitry that the Watchdog timer has timed out.                                                                                                                                                                                                                                                                                            |

14 • Introduction DSTni-LX Data Book

| SP0_RXD                   | Serial Port 0<br>Receive Data<br>(Input)          | This pin is used to receive asynchronous serial data from an externally connected device through serial Port 0. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP0_TXD                   | Serial Port 0<br>Transmit Data<br>(Output)        | This pin is used to send asynchronous serial data to an externally connected device through serial Port 0. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SP0_RTS_N                 | Serial Port 0<br>Request to Send<br>(Output)      | If enabled, this "flow control" pin is used to signal an external device that the processor has serial data and is requesting to send it through serial Port 0. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.                                                                                                                                                                                                                                                                                                                                                                                         |

| SP0_CTS_N                 | Serial Port 0 Clear<br>to Send<br>(Input)         | If enabled, this "flow control" input pin is used to signal the processor that an externally connected device is ready to receive serial data through serial Port 0. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.                                                                                                                                                                                                                                                                                                                                                                                    |

| SP1_RXD/<br>DIAG2         | Serial Port 1<br>Receive Data<br>(Bi-directional) | This is a multiplexed pin. In the default Serial Port mode, this input pin is used to receive asynchronous serial data from an externally connected device through serial Port 1. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features. The alternate mode of operation for this pin provides support for the Profibus DPV2 Isochron Mode of Operation. In this mode, the pin is an                                                                                                                                                                                                                           |

|                           |                                                   | output utilizing the Profibus specific function of "DIAG2".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SP1_TXD/<br>DIAG3         | Serial Port 1<br>Transmit Data<br>(Output)        | This is a multiplexed pin. In the default Serial Port mode, this input pin is used to send asynchronous serial data to an externally connected device through serial Port 1. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features. The alternate mode of operation for this pin provides support for the Profibus DPV2 Isochron Mode of Operation. In this mode, the pin is an                                                                                                                                                                                                                                |

| SP1_RTS_N/<br>DIAG4       | Serial Port 1<br>Request to Send<br>(Output)      | output utilizing the Profibus specific function of "DIAG3".  This is a multiplexed pin. The default mode for this pin is the RTS Serial Port function. If this "flow control" function is enabled, this output pin is used to signal an external device that the processor has serial data and is requesting to send it through serial Port 1. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.  The alternate mode of operation for this pin provides support for the Profibus DPV2 Isochron Mode of Operation. In this mode, the pin is an output utilizing the Profibus specific function of "DIAG4". |

| SP1_CTS_N/<br>ASPC2_CTS_N | Serial Port 1 Clear<br>to Send<br>(Input)         | This is a multiplexed pin. The default mode for this pin is the CTS Serial Port function. If this "flow control" function is enabled, this input pin is used to signal the processor that an externally connected device is ready to receive serial data through serial Port 1. See the "Asynchronous Serial Ports" section for more details including enhanced RS-485 and DMA features.  The alternate mode of operation for this pin provides support for the Profibus DPV2 Isochron Mode of Operation. In this mode, the pin is an input utilizing the Profibus specific function of "ASPC2_CTS_N".                                                           |

DSTni-LX Data Book Introduction ● 15

| OE_N    | Output Enable<br>(Output)                     | This pin (Output Enable) is an active low output signal used to access external memory along with the chip select signals. This signal goes active for all external memory access made by the processor. It is typically connected to the output enable pin of static RAM, or Flash device. It provides the tri-state bus disable function to the device when in the inactive or high state.                                                                                                                                                                                  |

|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRL_N   | Write Low Byte<br>(Output)                    | This pin (Write Low Byte) is an active low output signal used to indicate an external memory write access is being performed on the low byte of the system data bus, D07-D00. It is typically connected to the Write enable pin of the external memory device.                                                                                                                                                                                                                                                                                                                |

| WRH_N   | Write High Byte<br>(Output)                   | This pin (Write High Byte) is an active low output signal used to indicate an external memory write access is being performed on the upper byte of the system data bus, D15-D08. It is typically connected to the Write enable pin of the external memory device.                                                                                                                                                                                                                                                                                                             |

| UMCS_N  | Upper Memory<br>Chip Select<br>(Output)       | This pin is an active low output signal and indicates to the system that an external memory access is in progress to the upper memory block. The starting address and size of the upper memory block are programmable up to 512 Kbytes in 20-bit mode and up to 8 Mbytes in 24-bit mode. When the system comes out of reset, UMCS_N is active for the top 64 Kbyte memory block. This signal is typically connected to the chip enable of an external non-volatile storage device. Note that the on-chip BOOTROM overrides the very top 2048 bytes of the UMCS_N memory area. |

| MCS0_N  | Middle Chip<br>Select 0<br>(Output)           | This pin is an active low output signal and indicates to the system that an external memory access is in progress to the middle memory block range. The internal logic is hard wired so that the MCS0_N pin is always active in the range of 40000h to 7FFFFh in 20-bit mode and 040000h to 7FFFFFh in 24-bit mode. MCS0_N is automatically enabled after a reset or power up.                                                                                                                                                                                                |

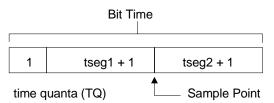

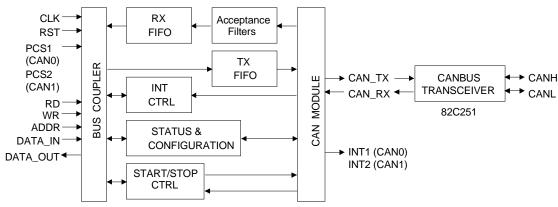

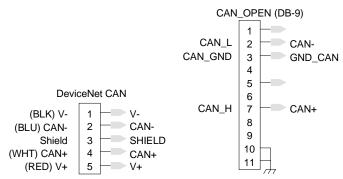

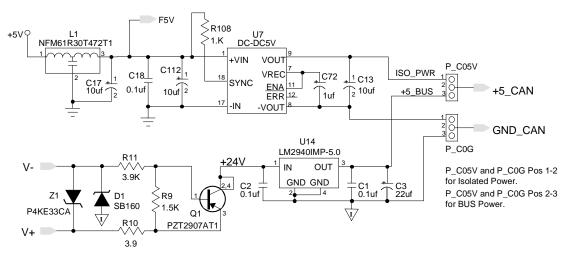

| READY_N | External Ready<br>(Input)                     | This pin is an active low input signal. It is a synchronous ready that indicates to the processor that the addressed memory space or I/O device will complete a data transfer. This input contains an internal pull-down resistor, so to always assert the ready condition to the processor, this pin can be left open.  NOTE: Do not use this signal to synchonize slow peripherals or slow memory. This will cause the Ethernet to fail and the processor to crash.                                                                                                         |