Design-In Guide netX 51/52

Hilscher Gesellschaft für Systemautomation mbH www.hilscher.com

# **Table of Contents**

| 1 | Intro | duction                                                         |     |

|---|-------|-----------------------------------------------------------------|-----|

|   | 1.1   | About this document                                             | 4   |

|   | 1.2   | List of revisions                                               |     |

|   | 1.3   | References to documents                                         |     |

|   | 1.4   | Legal notes                                                     |     |

|   | 1     | 1.4.1 Copyright                                                 |     |

|   |       | 1.4.2 Important notes                                           |     |

|   |       | 1.4.3 Exclusion of liability                                    |     |

|   |       | 1.4.4 Warranty                                                  |     |

|   |       | 1.4.5 Export regulation                                         |     |

|   |       | 1.4.6 Registered trademarks                                     |     |

| _ |       | •                                                               |     |

| 2 |       | c concepts                                                      | 9   |

|   | 2.1   | netX 51/52 - introduction                                       |     |

|   | 2.2   | netX 51 or netX 52 – Which netX is the right one?               |     |

|   | 2.3   | netX 51/52 – Basic design structures                            | .11 |

|   | 2.4   | Design checklist                                                | .12 |

|   |       | 2.4.1 Checklist for loadable firmware                           |     |

|   |       | 2.4.2 Checklist for linkable object module                      |     |

|   | 2.5   | Design examples                                                 |     |

|   | -     | 2.5.1 Communication interface                                   |     |

|   |       | 2.5.2 Gateway                                                   |     |

|   |       | 2.5.3 Encoder interface                                         |     |

|   |       | 2.5.4 IO-Link Proxy for all real-time Ethernet systems          |     |

| _ | D :   |                                                                 |     |

| 3 |       | C circuits                                                      |     |

|   | 3.1   | Power supply                                                    |     |

|   | 0.0   | 3.1.1 Core voltage regulator                                    |     |

|   | 3.2   | System clock                                                    |     |

|   | 3.3   | Power-on reset and reset in                                     |     |

|   | 3.4   | netX 51/52 chip mode selection                                  |     |

|   | 3.5   | Boot options                                                    | .21 |

|   |       | 3.5.1 Configured by the RDY/RUN pins                            |     |

|   |       | 3.5.2 Configuration and parameterization by the security EEPROM |     |

|   |       | 3.5.3 System RDY/RUN LED                                        |     |

|   |       | 3.5.4 Host interface mode during boot up                        |     |

|   | 3.6   | External memory                                                 | .26 |

|   |       | 3.6.1 Serial memory interface                                   |     |

|   |       | 3.6.1.1 SPI Flashs                                              |     |

|   |       | 3.6.1.2 QSPI Flash                                              |     |

|   |       | 3.6.1.3 MMC/SD card                                             |     |

|   |       | 3.6.2 Parallel memory interface                                 |     |

|   |       | 3.6.2.1 SRAM and Flash                                          |     |

|   |       | 3.6.3 SDRAM                                                     |     |

|   | 3.7   | Host interface                                                  |     |

|   |       | 3.7.1 Dual-port memory                                          |     |

|   |       | 3.7.1.1 8/16/32-bit data width and dual-port memory size        |     |

|   |       | 3.7.1.2 Control lines                                           |     |

|   |       | 3.7.1.3 Non-multiplexed mode                                    |     |

|   |       | 3.7.1.4 Multiplexed mode                                        |     |

|   |       | 3.7.1.5 Ready/Busy signal                                       |     |

|   |       | 3.7.2 Serial port memory (SPI/QSPI access to DPM)               |     |

|   |       | 3.7.3 Extension bus                                             |     |

|   |       | 3.7.3.1 Non-multiplexed mode                                    |     |

|   |       | 3.7.3.2 Multiplexed mode                                        |     |

|   |       | 3.7.4 MII port 2 acts as a PHY or MAC interface                 |     |

|   |       | 3.7.5 SDRAM memory extension                                    |     |

|   |       | 3.7.6 MMIO signals                                              |     |

|   |       | 3.7.7 PIO signals                                               |     |

|   |       | 3.7.8 External pull-ups/pull-downs, unused signals              |     |

|   | 3.8   | Multiplexed IO matrix (MMIO)                                    |     |

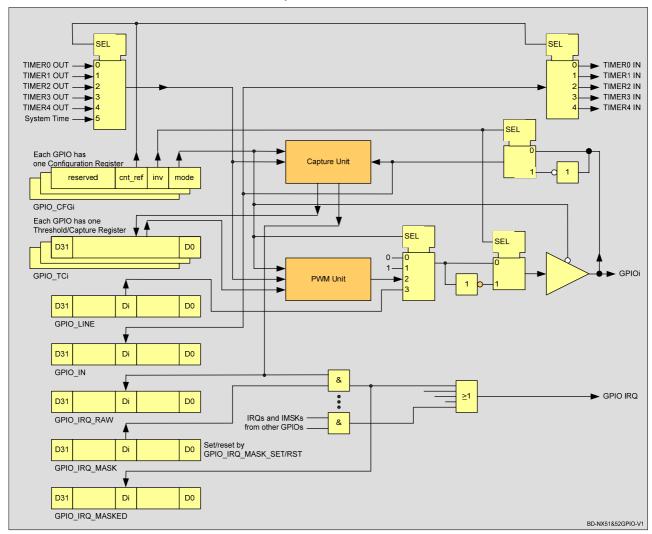

|   | 3.9   | General purpose IOs                                             |     |

|   |       | Serial interfaces                                               |     |

|   | 3.10  | OCHAI IIICHAUCS                                                 | .ാര |

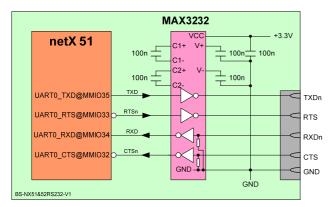

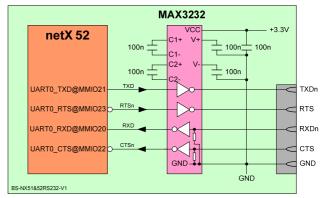

|   |            | 3.10.1 UARTs                                                        | 56  |

|---|------------|---------------------------------------------------------------------|-----|

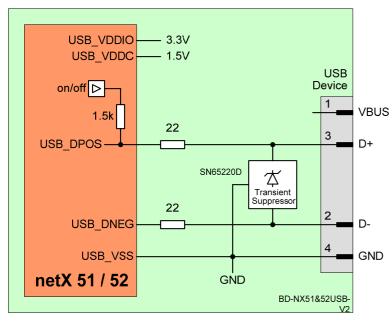

|   |            | 3.10.2 USB                                                          |     |

|   |            | 3.10.3 SPI                                                          |     |

|   |            | 3.10.4 I2C                                                          |     |

|   |            | 3.10.5 CAN                                                          |     |

|   | 3.11       | IO-Link                                                             |     |

|   |            | Fieldbus interfaces                                                 |     |

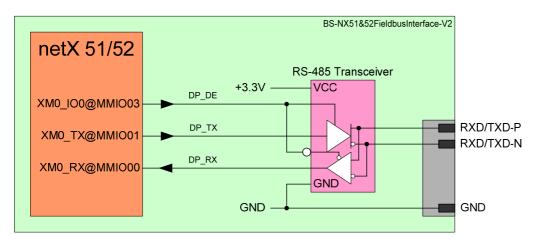

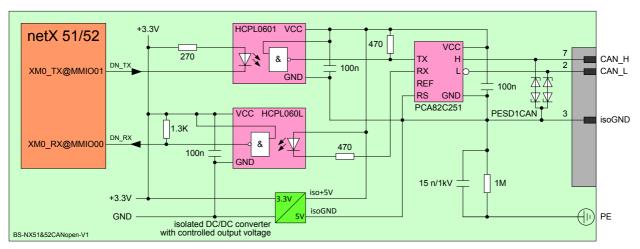

|   | 3.12       | 3.12.1 CANopen interface                                            |     |

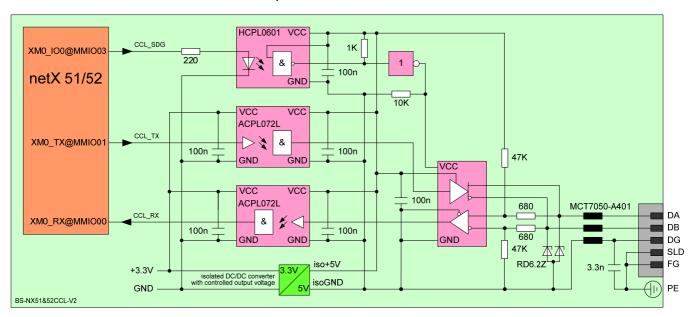

|   |            | 3.12.2 CC-Link interface                                            |     |

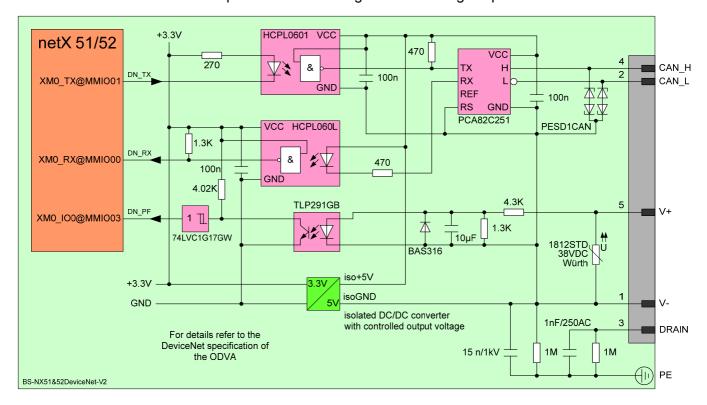

|   |            | 3.12.3 DeviceNet interface                                          |     |

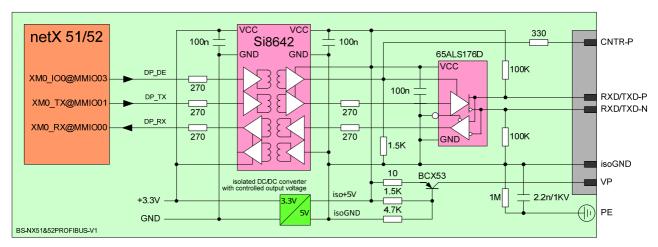

|   |            | 3.12.4 PROFIBUS interface                                           |     |

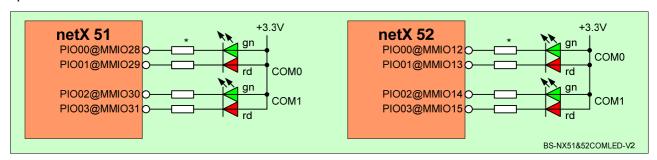

|   |            | 3.12.5 Fieldbus status LEDs                                         |     |

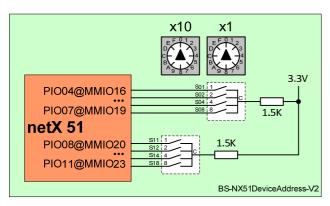

|   |            | 3.12.6 Fieldbus address switches                                    |     |

|   | 3.13       | Real-time Ethernet (RTE) interface                                  |     |

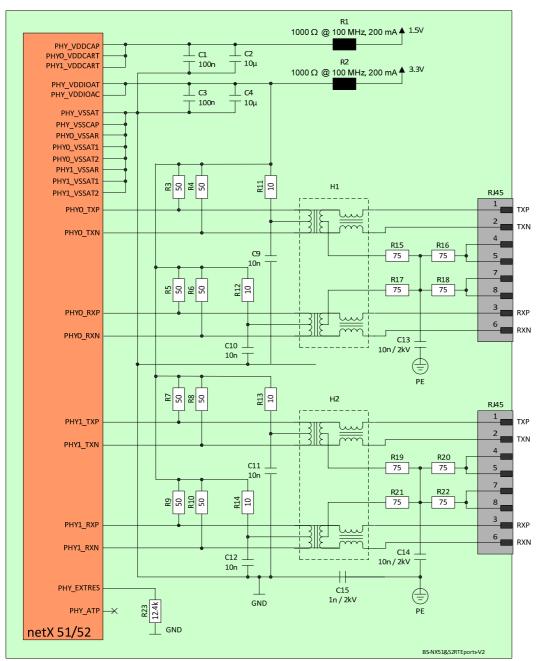

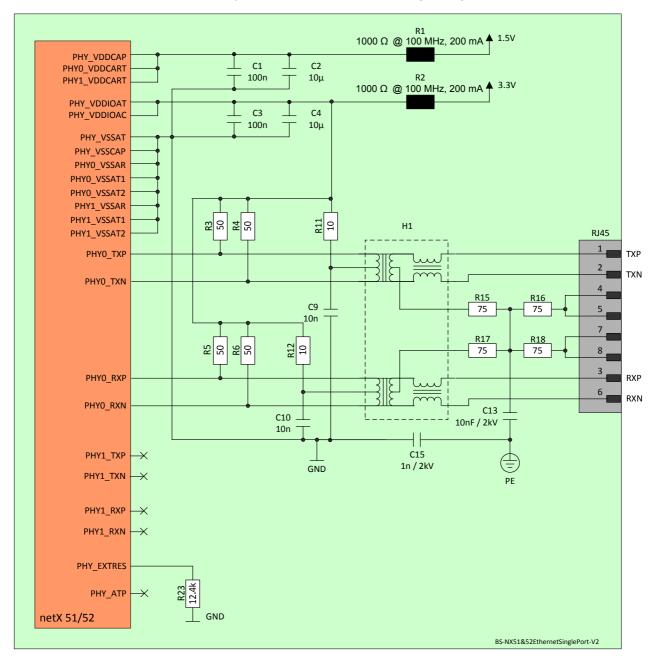

|   |            | 3.13.1 Twisted pair                                                 |     |

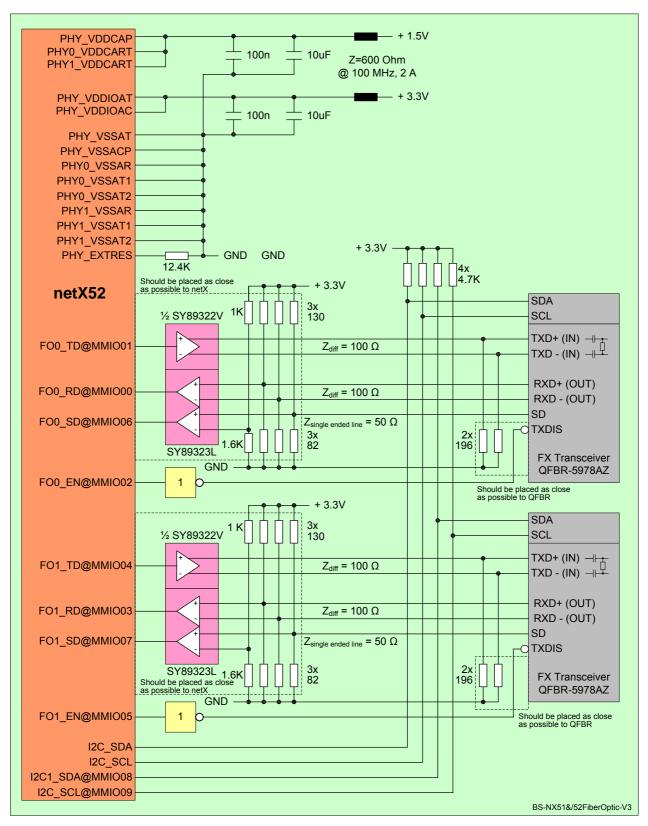

|   |            | 3.13.2 Fiber optic                                                  | 70  |

|   |            | 3.13.2.1 Transceivers with internal AC-termination                  |     |

|   |            | 3.13.2.2 Diagnostic monitoring interface                            | 70  |

|   |            | 3.13.4 Ethernet status LEDs                                         |     |

|   |            | 3.13.4.1 Ethernet communication status LEDs                         |     |

|   |            | 3.13.4.2 Real-time Ethernet protocol status LEDs                    |     |

|   |            | 3.13.5 RTE device address switches                                  |     |

|   |            | 3.13.6 Real-time Ethernet synchronization signals                   | 78  |

|   |            | 3.13.7 Special real-time Ethernet requirements                      | 79  |

|   |            | 3.13.7.1 Fast StartUp – Special feature of PROFINET                 | 79  |

|   |            | 3.13.7.2 QuickConnect <sup>™</sup> – Special feature of EtherNet/IP | 79  |

| 4 | Debu       | ıg and test interfaces                                              | 80  |

| • | 4.1        | JTAG interface                                                      |     |

|   |            | 4.1.1 Hilscher's 'mini-JTAG' connector                              |     |

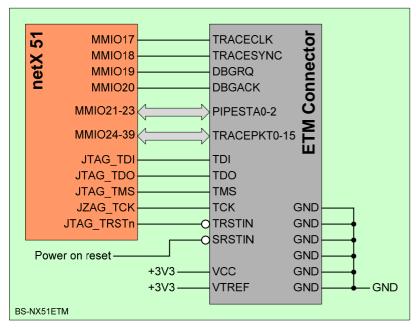

|   | 4.2        | ETM interface                                                       |     |

|   | 4.3        | Boundary scan test                                                  |     |

| _ |            | ·                                                                   |     |

| 5 |            | ource overview                                                      |     |

|   | 5.1        | rcX kernel                                                          |     |

|   | 5.2        | Memory requirements of Hilscher stacks                              |     |

| 6 | Gene       | eral design considerations                                          | 87  |

|   | 6.1        | Thermal behavior                                                    | 87  |

|   |            | 6.1.1 Basics                                                        | 87  |

|   |            | 6.1.2 Estimates                                                     |     |

|   |            | 6.1.3 Recommendations                                               |     |

|   | 0.0        | 6.1.4 Rules of thumb                                                |     |

|   | 6.2        | EMC behavior                                                        |     |

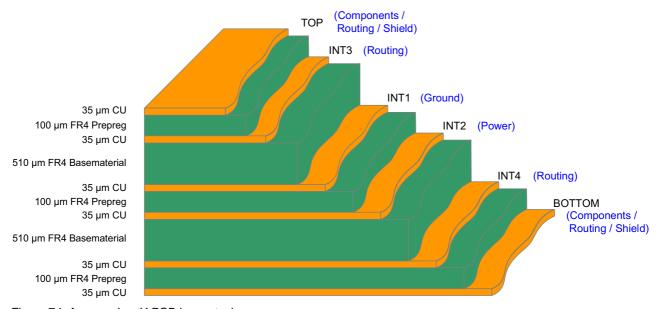

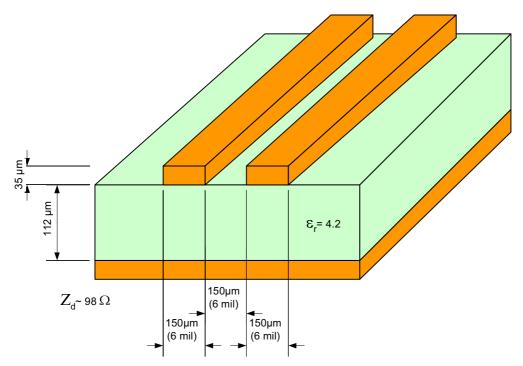

|   |            | 6.2.1 Layer stack                                                   |     |

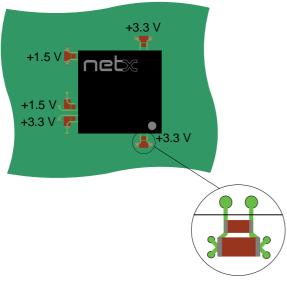

|   |            | 6.2.2 Decoupling capacitors                                         |     |

|   |            | 6.2.4 Clock circuits                                                |     |

|   |            | 6.2.5 Ethernet interface                                            |     |

|   |            | 6.2.6 Memory bus                                                    |     |

|   |            | 6.2.7 Planes                                                        | 95  |

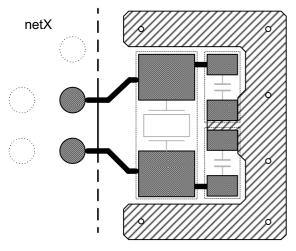

|   |            | 6.2.8 VIAs and signal fan out under netX 51/52                      | 96  |

| 7 | Refe       | rence section                                                       | 97  |

| • | 7.1        | Crystals                                                            |     |

|   | 7.2        | Serial Flash memory / EEPROM                                        |     |

|   | 7.3        | Parallel Flash memory                                               |     |

|   | 7.3<br>7.4 | SDRAM                                                               |     |

|   | 7.5        | Other components                                                    |     |

| _ |            | •                                                                   |     |

| 8 |            | endix                                                               |     |

|   | 8.1        | List of tables                                                      |     |

|   | 8.2        | List of figures                                                     |     |

|   | 8.3        | Contacts                                                            | 101 |

Introduction 4/101

## 1 Introduction

#### 1.1 About this document

This document is directed to hardware developers creating a hardware design with a communication controller of the Hilscher's netX family. It does not explain netX technology and features, which is covered by the corresponding Technical Data Reference Guides.

It describes the standard circuitry around all netX interfaces like memory interface (SDRAM, FLASH) USB, UARTs, XMACs (Ethernet and field bus), LCD, as well as power supply, reset and clock circuits along with the standard netX I/O resources (PIOs, GPIOs) that have been assigned a default functionality at Hilscher. This includes Status LEDs, control signals and sync signals for RTE applications.

Although the system designer is basically completely free to select any available I/Os for I/O purposes, it is important that he complies with the standard port definitions, whenever loadable firmware (LFW) from Hilscher is to be used, as this kind of firmware necessarily assumes compliance with Hilscher standard assignments.

#### Note:

Designers should be aware, that not all components supported by netX hardware (e.g. parallel FLASH) are necessarily also supported by existing software/firmware or tools from Hilscher! Hence it is strongly recommended, to consult the feature table in the following chapter, to make sure that all desired hardware features of the planned design are eventually supported by the firmware that will run on the design. This applies not only, but particularly to customers planning to use loadable firmware (LFW) from Hilscher instead of doing own firmware development.

Resources that are currently not supported by loadable firmware (LFW) or where no drivers/code are yet available may still already be supported by existing Hilscher devices (e.g. Gateways). It is hence recommended to check with Hilscher sales, if there is already an existing solution for your problem. Further, Hilscher offers several custom design services for netX hardware and software, as well as manufacturing services, providing an easy way to your custom product. For detailed information and quotes, please contact Hilscher sales.

Hilscher also offers a schematic review service, allowing your hardware design to be checked by netX experienced hardware engineers. Hilscher Sales will be happy to provide an individual quote for this service, after receiving your schematics (PDF format).

Note:

Before starting a design, it is strongly recommended, to consult the latest Errata Sheets (available on the Hilscher website www.hilscher.com) of the netX controllers!

Introduction 5/101

#### 1.2 List of revisions

| Rev | Date       | Name             | Chapter                                                | Revision                                                                                        |

|-----|------------|------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 5   | 2014-12-16 | HJH /<br>SH / HH | All                                                    | Complete review and update with additional details.                                             |

| 6   | 2015-01-23 | НН               | 3.7.1.1                                                | Correction: High signal to select 8-bit mode, low signal to select 16-bit mode.                 |

| 7   | 2015-08-26 | HN/HH            | 2.3                                                    | Section netX 51/52 – Basic design structures: Figure 3 updated.                                 |

|     |            |                  | 2.5.1                                                  | Section Communication interface: Figure 5: Resistors added (correction).                        |

|     |            |                  | 2.5.3                                                  | Section Encoder interface: Figure 9: Level shifter added (correction).                          |

|     |            |                  | 3.7.4                                                  | Section MII port 2 acts as a PHY or MAC interface: Figure 49 updated.                           |

|     |            |                  | 3.7.4                                                  | Section <i>MII port 2 acts as a PHY or MAC interface</i> : Table 15 signals MDC and MDIO added. |

|     |            |                  | 3.10.2                                                 | Section USB: Figure 53 corrected.                                                               |

|     |            |                  | 3.12.2                                                 | Section CC-Link interface: Figure 57 updated.                                                   |

|     |            |                  | 3.12.3                                                 | Section DeviceNet interface: Figure 58 updated.                                                 |

|     |            |                  | 3.12.5,<br>3.12.6,<br>3.13.4.1,<br>3.13.4.2,<br>3.13.5 | Resistor value range added and MMIO numbers corrected.                                          |

|     |            |                  | 3.13.2.2                                               | Section Diagnostic monitoring interface: Figure 64 corrected.                                   |

|     |            |                  | 3.13.6                                                 | Section Real-time Ethernet synchronization signals: EtherNet/IP Adapter added.                  |

|     |            |                  | 4.1                                                    | Section JTAG interface: Figure 69 corrected.                                                    |

|     |            |                  | 5.2                                                    | Section Memory requirements of Hilscher stacks: Table updated.                                  |

Table 1: List of revisions

#### 1.3 References to documents

This document refers to the following documents:

- [1] Hilscher Gesellschaft für Systemautomation mbH: Technical Data Reference Guide, netX 51/52,Revision 2, English, 2013.

- [2] Hilscher Gesellschaft für Systemautomation mbH: Dual-Port Memory Interface, English, Revision 12, 2013-03

- [3] Hilscher Gesellschaft für Systemautomation mbH: netX Security Memory, Implementation and use, English, Revision 2, 2009-10

- [4] Hilscher Gesellschaft für Systemautomation mbH: Migration Guide netX 50 to netX 51/52, English, Revision 5, 2013-08

- [5] Hilscher Gesellschaft für Systemautomation mbH: Programming Reference Guide netX 51/52, English, Revision 4, 2015-01

Table 2: References to documents

Introduction 6/101

# 1.4 Legal notes

## 1.4.1 Copyright

© Hilscher, 2008-2015, Hilscher Gesellschaft für Systemautomation mbH

All rights reserved.

The images, photographs and texts in the accompanying material (user manual, accompanying texts, documentation, etc.) are protected by German and international copyright law as well as international trade and protection provisions. You are not authorized to duplicate these in whole or in part using technical or mechanical methods (printing, photocopying or other methods), to manipulate or transfer using electronic systems without prior written consent. You are not permitted to make changes to copyright notices, markings, trademarks or ownership declarations. The included diagrams do not take the patent situation into account. The company names and product descriptions included in this document may be trademarks or brands of the respective owners and may be trademarked or patented. Any form of further use requires the explicit consent of the respective rights owner.

### 1.4.2 Important notes

The user manual, accompanying texts and the documentation were created for the use of the products by qualified experts, however, errors cannot be ruled out. For this reason, no guarantee can be made and neither juristic responsibility for erroneous information nor any liability can be assumed. Descriptions, accompanying texts and documentation included in the user manual do not present a guarantee nor any information about proper use as stipulated in the contract or a warranted feature. It cannot be ruled out that the user manual, the accompanying texts and the documentation do not correspond exactly to the described features, standards or other data of the delivered product. No warranty or guarantee regarding the correctness or accuracy of the information is assumed.

We reserve the right to change our products and their specification as well as related user manuals, accompanying texts and documentation at all times and without advance notice, without obligation to report the change. Changes will be included in future manuals and do not constitute any obligations. There is no entitlement to revisions of delivered documents. The manual delivered with the product applies.

Hilscher Gesellschaft für Systemautomation mbH is not liable under any circumstances for direct, indirect, incidental or follow-on damage or loss of earnings resulting from the use of the information contained in this publication.

Introduction 7/101

## 1.4.3 Exclusion of liability

The software was produced and tested with utmost care by Hilscher Gesellschaft für Systemautomation mbH and is made available as is. No warranty can be assumed for the performance and flawlessness of the software for all usage conditions and cases and for the results produced when utilized by the user. Liability for any damages that may result from the use of the hardware or software or related documents, is limited to cases of intent or grossly negligent violation of significant contractual obligations. Indemnity claims for the violation of significant contractual obligations are limited to damages that are foreseeable and typical for this type of contract.

It is strictly prohibited to use the software in the following areas:

- for military purposes or in weapon systems;

- for the design, construction, maintenance or operation of nuclear facilities;

- in air traffic control systems, air traffic or air traffic communication systems;

- in life support systems;

- in systems in which failures in the software could lead to personal injury or injuries leading to death

We inform you that the software was not developed for use in dangerous environments requiring fail-proof control mechanisms. Use of the software in such an environment occurs at your own risk. No liability is assumed for damages or losses due to unauthorized use.

### 1.4.4 Warranty

Although the hardware and software was developed with utmost care and tested intensively, Hilscher Gesellschaft für Systemautomation mbH does not guarantee its suitability for any purpose not confirmed in writing. It cannot be guaranteed that the hardware and software will meet your requirements, that the use of the software operates without interruption and that the software is free of errors. No guarantee is made regarding infringements, violations of patents, rights of ownership or the freedom from interference by third parties. No additional guarantees or assurances are made regarding marketability, freedom of defect of title, integration or usability for certain purposes unless they are required in accordance with the law and cannot be limited. Warranty claims are limited to the right to claim rectification.

# 1.4.5 Export regulation

The delivered product (including the technical data) is subject to export or import laws as well as the associated regulations of different counters, in particular those of Germany and the USA. The software may not be exported to countries where this is prohibited by the United States Export Administration Act and its additional provisions. You are obligated to comply with the regulations at your personal responsibility. We wish to inform you that you may require permission from state authorities to export, re-export or import the product.

Introduction 8/101

## 1.4.6 Registered trademarks

CANopen® is a registered trademark of CAN in AUTOMATION - International Users and Manufacturers Group e.V. (CiA), Nuremberg.

CC-Link® is a registered trademark of Mitsubishi Electric Corporation, Tokyo, Japan.

DeviceNet® and EtherNet/IP® are trademarks of ODVA (Open DeviceNet Vendor Association, Inc).

EtherCAT® is a registered trademark and a patented technology of Beckhoff Automation GmbH, Verl, Germany, formerly Elektro Beckhoff GmbH.

Modbus® is a registered trademark of Schneider Electric.

Powerlink® is a registered trademark of B&R, Bernecker + Rainer Industrie-Elektronik Ges.m.b.H, Eggelsberg, Austria

PROFIBUS® und PROFINET® are registered trademarks of PROFIBUS International, Karlsruhe.

Sercos interface® is a registered trademark of Sercos International e. V., Suessen, Germany.

I2C is a registered trademark of NXP Semiconductors, formerly Philips Semiconductors.

All other mentioned trademarks are property of their respective legal owners.

Basic concepts 9/101

# 2 Basic concepts

#### 2.1 netX 51/52 - introduction

### Real-Time Ethernet / Fieldbus

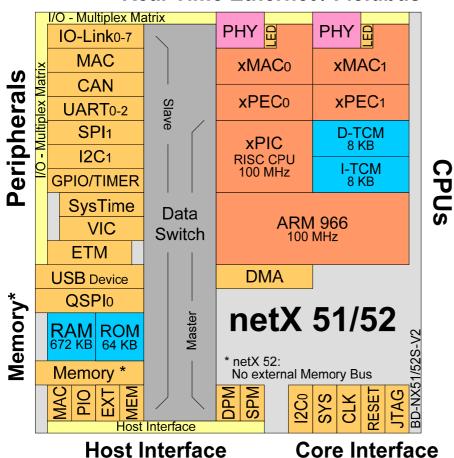

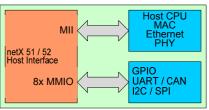

Figure 1: netX 51/52 block diagram

The netX 1/52 is a highly integrated network controller with two communication channels. The integrated PHYs can be programmed to run any important real-time Ethernet system. Apart from the 32 bit/100 MHz main CPU, it has an additional 32-bit/100 MHz RISC CPU for handling some background tasks. This helps achieve very fast bus cycles down to 100 us without influencing the protocol stack running on the ARM CPU.

It has a 672 KB internal SRAM and a QSPI/SPI interface to connect a serial Flash which contains the program code. Moreover, netX 51 has a memory interface for SDRAM, Flash or SRAM to enlarge the internal memory.

It incorporates many peripheral functions like 8-channel IO-Link master, CAN controller, a third Ethernet channel mainly used for diagnostic purposes. Of course, all standard interfaces like UART, USB device, SPI, and I2C master or slave are available, too. The multiplex matrix reduces the number of peripheral signals to the number required for the current application.

Peripherals and CPUs are connected via a switch matrix where data transfers simultaneously take place as long as they have a different destination or source area.

A special feature is the very flexible host interface which can be configured to work as DPM, intelligent serial port memory, extension bus or memory controller for SRAM/SDRAM.

Basic concepts 10/101

# 2.2 netX 51 or netX 52 – Which netX is the right one?

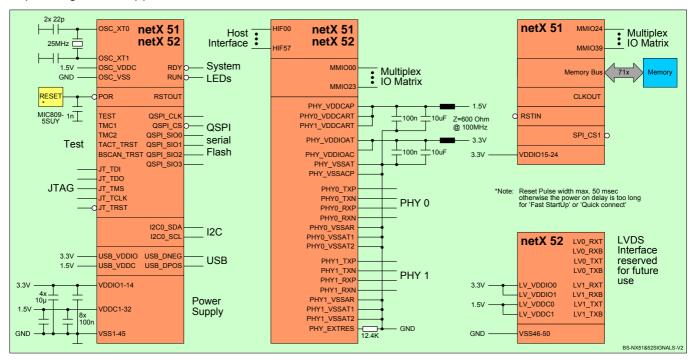

The following schematic gives an overview of the signals and the differences between netX 51 and netX 52. To have the right understanding: both devices contain the same piece of silicon. The netX 52 does not have so many peripheral I/O signals and no external memory bus. Thus, the housing is smaller and the chip is cheaper.

The netX 51/52 needs a 3.3 V power supply for the I/Os and a 1.5 V for the core voltage. Only a few external components are needed e.g. a crystal, a reset generator and additional memory depending on the application.

Figure 2: netX 51/52 signals

- The silicon inside the netX 51 or 52 is the same!

- netX 51 has a larger housing of 19x19 mm with 1 mm pitch and 324 pins plus

- a memory bus to enlarge the memory with an external SDRAM, SRAM or Flash

- a multiplex IO matrix with 40 I/Os: 16 more than netX 52, for that reason it can drive 8 IO-Link channels instead of 5 like netX 52

- three signals: Clock out, reset in and SPI chip select 1

- netX 52 has a small housing of 15x15 mm with 0.8 mm pitch and 244 pins

- netX 52 is pin-compatible with netX 6

- netX 52 is cheaper than netX 51 due to a smaller housing and less pins

- → For a pure communication interface: netX 52 is the right choice

- the protocol stacks as loadable firmware do not need an external SDRAM

- easier layout, smaller footprint, lower costs for components

- using standard schematic for finalizing the design quickly without risk

- → Running additional application software on the chip: Use netX 51 to have more memory space

Basic concepts 11/101

→ For a stand-alone application, i.e. an IP67 IO block where the host interface can be configured as memory bus to connect a SDRAM: netX 52 might be a good option.

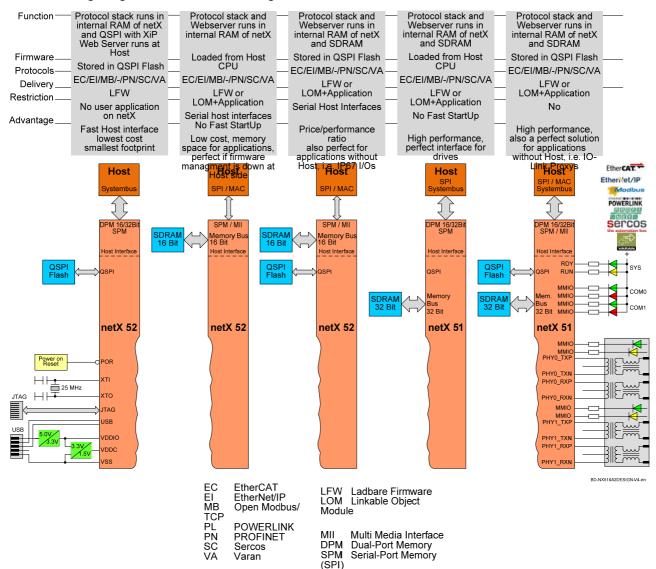

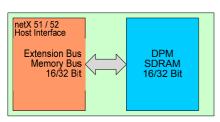

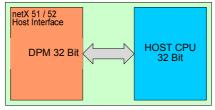

# 2.3 netX 51/52 – Basic design structures

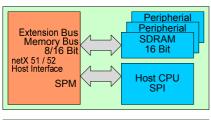

If you start developing a design with netX 51/52, you have to decide on whether you want to use netX 52 or whether you want to add a lot of application code to the protocol stack. In that case, the netX 51 would be the right choice.

The following diagram shows basic design structures:

Figure 3: netX 51/52 - Basic design structures

Most customers are running Hilscher protocol stacks on the netX. If you also want to do this, you have to follow instructions on how to develop the hardware that our protocol stacks can run without any modification.

You will find most of these instructions in this manual. On the next pages, we provide various design examples. We also have an excellent support team. If you do not have the resources, we can develop and produce the requested device for you.

Basic concepts 12/101

# 2.4 Design checklist

## 2.4.1 Checklist for loadable firmware

- ☑ Do I have a possibility to load my firmware from e.g. Flash, host controller, Ethernet?

- Are the boot options and system LEDs set up correctly?

- ☑ How do I get my firmware into my device USB, UART, host, Ethernet?

- ☑ If I need additional memory, is it set up correctly?

- ☑ Is my fieldbus / real-time Ethernet Interface connected correctly?

- ☑ Are my fieldbus / real-time Ethernet LEDs connected?

- ☑ Is my host controller associated properly?

- ☑ Do I have all basic components like power supply, power-on reset, system clock?

## 2.4.2 Checklist for linkable object module

- ☑ Do I have a possibility to load my firmware from e.g. Flash, host controller, Ethernet?

- ☑ Are the boot options and system LEDs set up correctly?

- ☑ How do I get my firmware into my device USB, UART, host, Ethernet?

- ☑ Is my external memory set up correctly?

- ☑ Is my fieldbus / real-time Ethernet interface connected correctly?

- ☑ Are my fieldbus / real-time Ethernet LEDs connected?

- ☑ Do I have all basic components like power supply, power-on reset, system clock?

- ☑ Do I need some debug options?

- ☑ Are all of my peripherals e.g. CAN, GPIOs, I2C, SPI, UARTs connected?

Basic concepts 13/101

# 2.5 Design examples

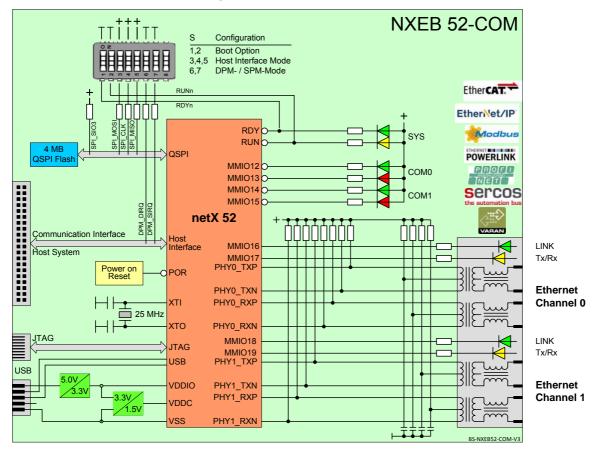

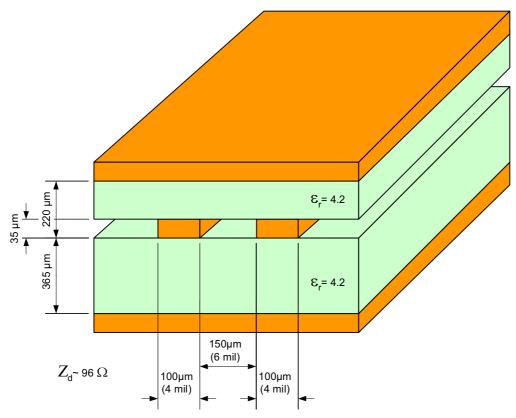

### 2.5.1 Communication interface

- Standard netX 52 core for all real-time Ethernet systems

- netX 52 with all core components on 25 x 25 mm²

Figure 4: NXEB 52-COM

This is the most frequently used design for a general communication interface. It needs only a few external components. The host interface can be configured from a high speed 32-bit parallel DPM to a very fast SPI connection. Alternatively, you can configure a UART, CAN or some digital I/Os on the same pins. In a final design, resistors will substitute the DIP switch.

Figure 5: NXEB 52-COM block diagram

Basic concepts 14/101

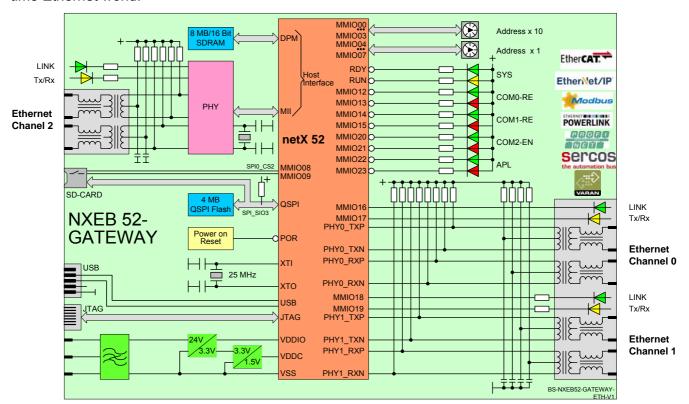

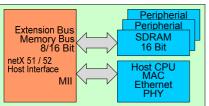

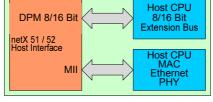

### 2.5.2 Gateway

- Gateway between real-time and standard Ethernet

- Use MII port at the host interface in combination with 8 MB SDRAM

Figure 6: NXEB 52-GATEWAY

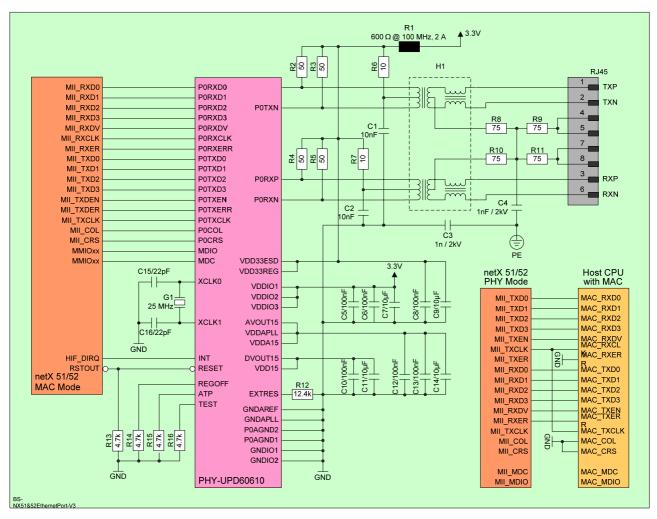

The third Ethernet port is often used as a local diagnostic port. It can also be used as a type of gateway to transfer standard TCP/IP frames into the non-real-time channel of the real-time Ethernet system e.g. EtherCAT or Sercos.

The dedicated CAN port is a nice option for gateways between a legacy system and the new real-time Ethernet world.

Figure 7: NXEB 52-GATEWAY block diagram

Basic concepts 15/101

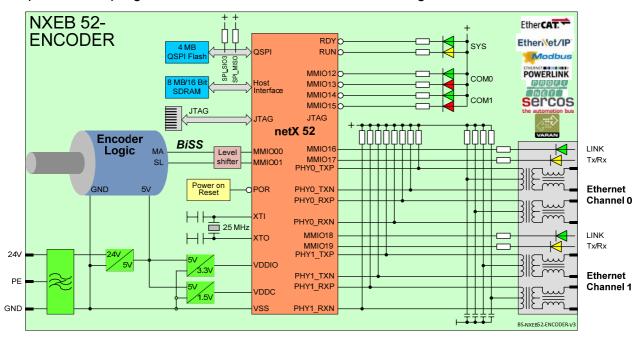

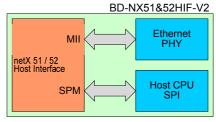

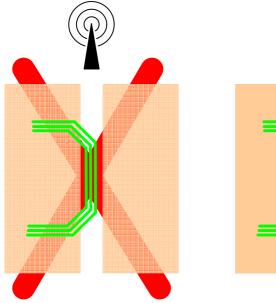

#### 2.5.3 Encoder interface

- Compact 53 mm diameter

- BiSS interface implemented on xPIC

- External SDRAM via host interface due the encoder profile

- 85 °C operating temperature with cooling interface to the encoder housing

Figure 8: NXEB 52-ENCODER

By implementing the  $BiSS^R$  protocol on the xPIC we have realized a glue-less connection between the netX 51/52 and the  $BiSS^R$  chip.

The special requirement of an operating temperature of +85°C can be met with a closed temperature coupling between the netX and the encoder housing.

Figure 9: NXEB 52-ENCODER block diagram

Basic concepts 16/101

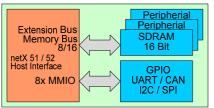

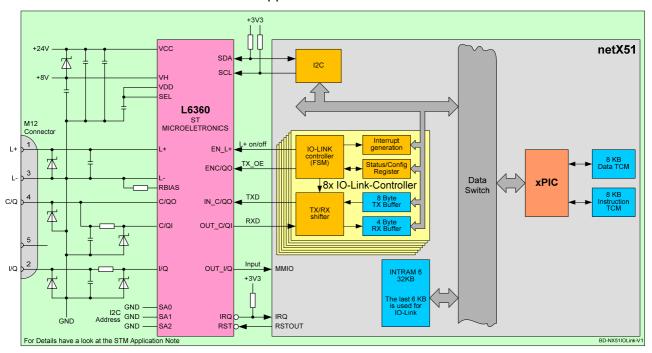

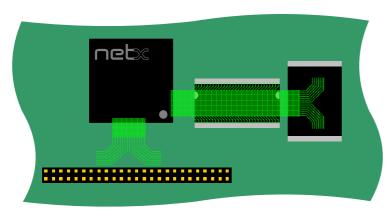

## 2.5.4 IO-Link Proxy for all real-time Ethernet systems

- IO-Link gateway based on netX 51

- One hardware design for all real-time Ethernet systems

- 8 channels, IO-Link V1.1, implemented on xPIC

- Performance

Figure 10: IO-Link Gateway with netX 51

In this design example we also use the xPIC to run the lower protocol layer. This results in a very cost-effective design for IP67 IO-Link IO-blocks. Beside the compact hardware design, the proxy functionality is available between IO-Link and any important real-time Ethernet system.

Basic circuits 17/101

## 3 Basic circuits

# 3.1 Power supply

netX 51/52 requires an I/O voltage supply of 3.3 V and a core voltage supply of 1.5 V.

For worst case scenarios, the 3.3 V supply should be able to deliver a current of 350 mA for the netX part (netX, memory, etc.) of the circuit. If the core voltage regulator is also supplied by the 3.3 V rail, the max. current will increase accordingly.

The core supply should be able to deliver 900 mA.

Lower max. currents may be sufficient for certain applications e.g. applications that do not use the Ethernet ports. For details on power consumption see the Technical Data Reference Manual of the netX chip (see reference [1]).

It is recommended to implement a separate core voltage supply for the netX even if a 1.5 V supply is required by other parts of the system (e.g. FPGA). The output voltage of this separate supply should be "programmable" either by approx. digital input pins or by external resistors. This allows you to continue using the same design after the netX type used has gone through a die shrink process, which always results in a reduced core voltage.

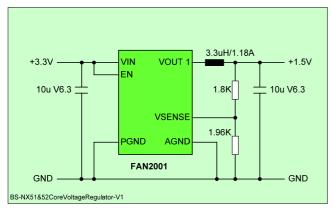

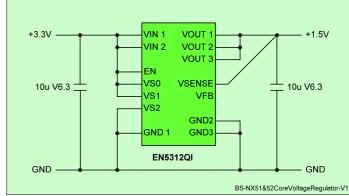

## 3.1.1 Core voltage regulator

A Hilscher standard circuit for the core voltage regulator uses a FAN2001 (Fairchild Semiconductor) step-down DC-DC converter and is in Figure 11. The complete part name is FAN2001MPX. The inductor is a CR32NP-3R3 (Sumida). The capacitors are ceramic types (X5R/X7R), resistors 1%.

An alternative part, especially for designs with space constraints, is the EN5312Q (Enpirion), which delivers 1A, has an integrated inductor and provides 3 digital inputs for setting the output voltage, requiring only two 10  $\mu$ F ceramic caps as additional external components (see www.enpirion.com for detailed information).

Figure 11: netX core voltage regulator

Basic circuits 18/101

# 3.2 System clock

netX 51/52 uses an internal oscillator with an external crystal or an external oscillator for generating the 25 MHz base clock. This clock will be stabilized by a PLL which generates all internal clocks of the chip.

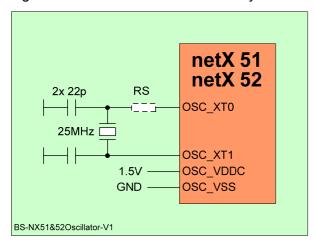

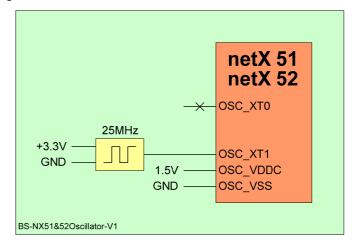

Figure 12 shows the circuits for the system clock generation:

Figure 12: netX 51/52 system oscillator circuit

The values of the capacitors and the serial resistor (Rs) depend on the used crystal. If the same crystal is used all Hilscher netX products are equipped with, the resistor Rs will not be used and is replaced by a wire. The capacitors should have a value of 22 pF.

If a different crystal is used, you have to consult the data sheet of the crystal to determine the appropriate values.

The Hilscher standard netX system crystal is an ABM7-25.000 MHz-D2Y-T manufactured by Abracon.

Alternatively, an external oscillator can be used and is connected according to the schematic (Figure 12, right).

Note: An external oscillator or a different crystal you wish to use must have a frequency of 25 MHz and a max. tolerance of +/- 100 ppm throughout the complete temperature range, the design will be specified for!

- Q1: We already have crystals or oscillators in store with a different frequency or a higher tolerance. Can we also use these parts for the system oscillator?

- A1: No. The 25 MHz clock is the base for all other netX clocks. It influences any timing around the netX, like SDRAM timing, Baud rates, Ethernet timing, etc. Deviating from the specified frequency will most likely result in a system that does not work properly.

Basic circuits 19/101

#### 3.3 Power-on reset and reset in

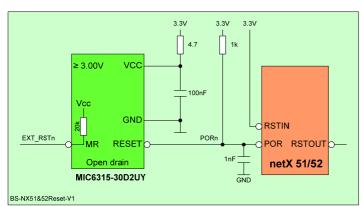

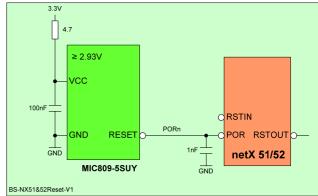

The netX 51/52 provides a Schmitt-trigger power-on reset (PORn), netX 51 an additional Reset Input (RSTINn). The POR signal should be generated by a dedicated reset circuit which also checks that the VDDIO voltage has reached the min. level of 3 V.

Reset generator components are often available with a push/pull or an open drain output. If the design uses the JTAG Interface of the netX, select an open drain type, since this allows you to simply connect the reset signal from the JTAG connector (which is also specified as open drain) to the output of the reset generator. Of course, a pull-up resistor must be attached to the PORn signal if open drain reset sources are used.

The optional RSTINn, commonly used by an external host processor to reset the netX, also provides a Schmitt-trigger gate. The netX 51 provides an internal pull-up resistor (nominal 50 k $\Omega$ ) and could be left open if not used. However, it is recommended to tie it to VDDIO (+3.3V), since this can improve EMC behavior.

When placing the components during PCB design, place the reset source(s) near the reset inputs of the netX to keep the traces of the reset signals short. Routing reset signals all over the PCB may result in bad EMC behavior of the design, since ESD may cause undesired resets of the chip. We recommend connecting a 1 nF ceramic capacitor to GND and PORn close to the netX PORn pin. The following figure shows the standard reset circuits:

Figure 13: netX 51/52 reset circuits

| Reset device specification | MIC6315-30D2UY                  | MIC809-5SUY                    |  |  |

|----------------------------|---------------------------------|--------------------------------|--|--|

| Min.                       | 20 ms                           | 30 ms                          |  |  |

| Тур.                       | 28 ms                           | -                              |  |  |

| Max.                       | 44 ms                           | 66 ms                          |  |  |

| Reset level                | 3.0 V ± 2,5 % (2.925 V 3.075 V) | 2.93 V ± 2.4 % (2.85 V 3.00 V) |  |  |

| Temperature range          | –40 °C +85 °C                   | –40 °C +85 °C                  |  |  |

Table 3: Reset device specification

Note:

In case of PROFINET (using the Fast StartUp function) and EtherNet/IP (using the QuickConnect function) the delay in the reset circuit must always be observed. The delay should NEVER exceed the max. of 66 ms. Make sure that the core voltage is stable and over 1.425 V before the PORn signal is released. An example for such a component is the MIC6315-30D2UY from the company Micrel.

Section JTAG interface on page 80 shows the reset circuit in combination with the JTAG interface.

Basic circuits 20/101

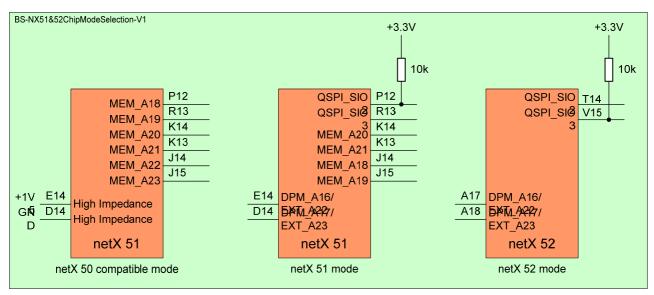

# 3.4 netX 51/52 chip mode selection

As described in the previous chapter, netX 51 and netX 52 contain the same piece of silicon, i.e. the same die. Additional netX 51 can upgrade a netX 50 design by a direct replacement on the same PCB. These three modes have to be configured by two resistors.

On netX 51, the ROM code uses the pins MEM\_A18/QSPI\_SIO2 and MEM\_A19/SQPI\_SIO3 to read the configured chip mode and on netX 52 the pins QSPI\_SIO2 and QSPI\_SIO3. Both pins are sampled after a negative edge at the power-on reset and the internal PLL reaches a stable state:

|                           | netX<br>51 | MEM_A18/<br>QSPI_SIO2 | MEM_A19/<br>QSPI_SIO2 | Pin J14 | Pin J15 | Pin E14              | Pin D14              | Version  | USB ID |

|---------------------------|------------|-----------------------|-----------------------|---------|---------|----------------------|----------------------|----------|--------|

| Chip<br>Mode              | netX<br>52 | QSPI_SIO2             | QSPI_SIO3             | -       | -       | Pin A17              | Pin A18              | register |        |

| netX 50<br>compati        |            | open (low)            | open (low)            | MEM_A22 | MEM_A23 | High impedance       | High impedance       | 0x243    | 0x18   |

| netX 51                   |            | pull-up<br>(high)     | open (low)            | MEM_A18 | MEM_A19 | DPM_A16 /<br>EXT_A22 | DPM_A17 /<br>EXT_A23 | 0x643    | 0x18   |

| netX 52                   |            | open (low)            | pull-up<br>(high)     | -       | 1       | DPM_A16 /<br>EXT_A22 | DPM_A17 /<br>EXT_A23 | 0xA43    | 0x19   |

| Undefined /<br>do not use |            | pull-up<br>(high)     | pull-up<br>(high)     | -       | ı       | -                    | -                    | -        | -      |

Table 4: netX 51/52 chip mode selection

This achieves QSPI signals on netX 51, two more address signals at the host interface and changes at the version register and the USB ID. MEM\_A18/19 substitute MEM\_A22/23 because the highest memory addresses are normally not used.

Note: If netX 51 is used as a direct replacement for netX 50, you must use the netX 50-compatible mode. Otherwise you risk damage to the netX 51 because on a netX 50-based PCB pin E14 is connected with +1.5 V and pin D14 with GND. For more information on the direct replacement of netX 50, refer to the Migration Guide

Figure 14: netX 51/52 chip mode selection

Basic circuits 21/101

# 3.5 Boot options

Right after turning on the power or pressing the reset button, the netX searches for a bootable code image. Usually this image is a second stage boot loader or a firmware. The netX checks a sequence of devices for a bootable image: the boot sequence. The devices in the boot sequence are checked one after the other. The ROM loader checks device by device and starts the first valid image found.

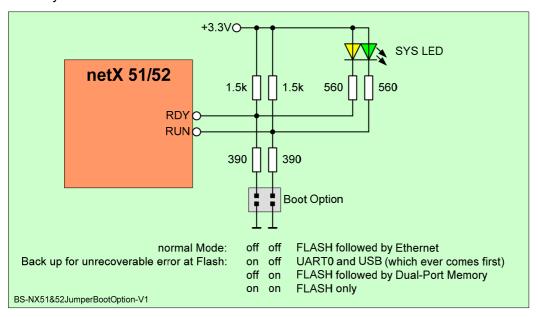

# 3.5.1 Configured by the RDY/RUN pins

The state of the RDY/RUN pins after any type of reset defines the boot sequence.

Figure 15 shows an example circuit to realize the states for the different boot options without the Security EEPROM.

Figure 15: netX 51/52 RDY/RUN circuit

|         | Flash / Ethernet boot mode         | Serial boot mode | Flash / DPM boot mode     | Flash boot mode           |  |

|---------|------------------------------------|------------------|---------------------------|---------------------------|--|

| netX 51 | Par. Flash memory bus              | UART0 or USB     | Par. Flash memory bus     | Par. Flash memory bus     |  |

|         | QSPI CS0 Flash                     |                  | QSPI CS0 Flash            | QSPI CS0 Flash            |  |

|         | SPI CS0 EEPROM SPI CS1 MMC/SD card |                  | SPI CS0 EEPROM            | SPI CS0 EEPROM            |  |

|         |                                    |                  | SPI CS1 MMC/SD card       | SPI CS1 MMC/SD Card       |  |

|         | Ethernet                           |                  | Dual-Port Memory          | None                      |  |

| netX 52 | Par. Flash host interface          | UART0 or USB     | Par. Flash host interface | Par. Flash host interface |  |

|         | QSPI CS0 Flash                     |                  | QSPI CS0 Flash            | QSPI CS0 Flash            |  |

|         | SPI CS0 Flash                      |                  | SPI CS0 EEPROM            | SPI CS0 EEPROM            |  |

|         | SPI CS2 MMC/SD card                |                  | SPI CS2 MMC/SD card       | SPI CS2 MMC/SD Card       |  |

|         | Ethernet                           |                  | Dual-Port Memory          | None                      |  |

Table 5: Boot sequence and devices for the different boot options

**Note:** The Flash/Ethernet boot mode is most common. You can program a complete empty Flash or EEPROM via Ethernet with the firmware. Thereafter the device will always start this firmware. The serial boot mode is used as a backup function.

Basic circuits 22/101

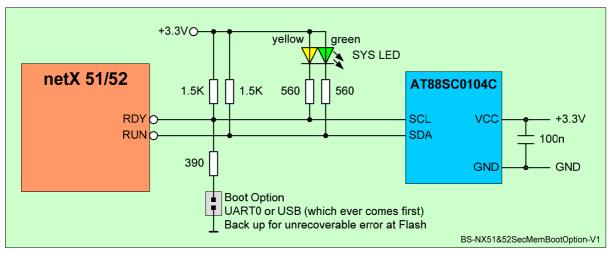

## 3.5.2 Configuration and parameterization by the security EEPROM

The security EEPROM is a further possibility to define the current boot option. It is divided into parts that only Hilscher can read and write by help of a security algorithm mainly used for master or other software licenses. Other parts with defined configuration parameters e.g. MAC address, SDRAM set up parameter or device information like serial number, production date and manufacture code. In addition, there is also a 32-byte part which can be completely defined by the user. The security EEPROM is mandatory in master application using Hilscher master protocol stacks. Since netX 51/52 are primarily designed for slave applications, a security EEPROM is not required. If you have enough space on your PCB, it might be a good design strategy to include a security EEPROM, but do not assemble it as long as it is not necessary. An explanation of the purpose and use of the security EEPROM is available on the Hilscher website in document Dual-Port Memory [2] and AppNote security EEPROM [3].

On netX 51/52, the security EEPROM must not be connected to the I2C interface! The RDY and RUN pins are used instead, see Figure 16.

Figure 16: Sample schematic, netX 51/52 security memory and RDY/RUN LED

You can use type AT88SC0104C only.

| Note: | If you want to use a security EEPROM, order it from Hilscher because it is a special |

|-------|--------------------------------------------------------------------------------------|

|       | customized version of the AT88SC0104C. Only Hilscher can correctly write the license |

|       | and other crucial information to the security memory in a netX-readable format.      |

|       |                                                                                      |

**Note:** All other I2C components in a netX 51/52 design have to be connected to the I2C interface of netX 51/52. The I2C emulation on the RDY and RUN pins is used by the first stage loader only and is not accessible for users!

- Q1: Now that there is only a button for the serial boot mode, how can I enter the DPM boot mode or the extension bus boot mode on my design?

- A1: The netX 51/52 can store the boot mode in the user area of the security EEPROM.

Basic circuits 23/101

Q2: I prefer doing things in hardware. Can't I still use the jumpers as with the other circuits?

A2: No, you cannot use the jumpers along with the EEPROM. I2C accesses do not allow you to drive signals actively high. Hence, the RDY and RUN pins must always have strong pull-ups when the EEPROM is to be accessed. The netX 51/52 ROM loader will not even look for a security EEPROM unless it detects a high level on the RDY and RUN pins.

- Q3: Now that the boot mode is stored in the EEPROM, do I still need the serial boot mode button?

- A3: The serial boot mode allows you to (re-)flash the firmware and to set or modify the boot mode stored in the EEPROM. Therefore it is strongly recommended.

- Q4: Why are the system LEDs not connected antiparallel as with the other circuits?

- A4: The diodes need to be connected differently because the antiparallel circuit has too much impact on the quality of the I2C signals.

- Q5: I do not want to use the security memory. Where does the firmware get the MAC address from?

- A5: The MAC address could be stored in a flash sector called device label, or set up through an rcX packet.

Basic circuits 24/101

## 3.5.3 System RDY/RUN LED

For displaying system status, a system LED (dual LED or two single LEDs) is defined:

| LED | Color  | Description                                |

|-----|--------|--------------------------------------------|

| RDY | Yellow | netX with operating system is running      |

| RUN | Green  | User application is running without errors |

Table 6: RDY / RUN I FD status

Designers could use LEDs with other colors, but we recommend using the Hilscher definition. Especially when interpreting blink codes for troubleshooting, it is helpful if customer and support see the same colors.

#### Note:

In netX schematics, the RDY and RUN pins usually have a negating circle. However, the polarity of these pins (when used as outputs) depends on a register setting. Apart from the two bits that enable the output driver (pin configured as output) and set the level of the pin, there is a third bit for each pin that determines the polarity (active high or active low). Thus, it actually depends on these polarity bits, if the (output-) pins are active low or active high!

These polarity bits do not affect the pins when used as inputs (RDY and RUN inputs are never inverted).

The RDY and RUN pins are always shown as active low because this level will switch on the corresponding LED according the given schematic.

Basic circuits 25/101

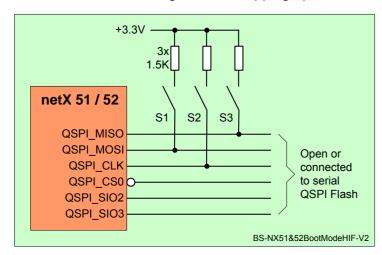

## 3.5.4 Host interface mode during boot up

A special case occurs if the boot sequence contains devices connected to the host interface. The host interface offers a variety of functions with just a few pins. Each pin has several functions. To prevent physical damage to the netX, the host interface should only use the functions that are really connected. Using other functions with the connection might cause permanent damage.

Example 1: A board has a DPM interface connected to the host interface pins. The host interface should be used as a DPM, but not as a memory interface.

Example 2: A board has a parallel flash connected to the host interface pins. The host interface should be used as a memory interface, but not as a DPM.

The netX offers both, DPM and parallel Flash, as boot devices. A way is required to determine which functions of the host interface can be used.

At this point the strapping options become important. They configure what is really connected to the host interface. When the netX executes the boot sequence for DPM mode, it first consults the strapping options. If, and only if, the device matches the settings of the strapping options, the netX looks for a bootable image. If the strapping options do not match, the device will be ignored.

Figure 17: How to configure the host interface mode during boot up

| SPI0_MOSI | SPI0_CLK | SPI0_MISO | Device at host interface which netX boots from                                     |

|-----------|----------|-----------|------------------------------------------------------------------------------------|

| none      | none     | none      | Ignore host interface during boot.                                                 |

| none      | none     | pull up   | 16-bit SDRAM and up to 4 MByte address range                                       |

| pull up   | none     | pull up   | 32-bit SDRAM and up to 4 MByte address range                                       |

| none      | pull up  | none      | 16-bit SRAM and up to 4 MByte address range                                        |

| none      | pull up  | pull up   | From host CPU via serial dual-port memory (SPM)                                    |

| pull up   | none     | none      | From host CPU via 8-bit parallel dual-port memory and up to 2 KByte address range. |

| pull up   | pull up  | pull up   | From host CPU via 8-bit parallel dual-port memory and up to 64 KByte address range |

| pull up   | pull up  | none      | Reserved. Do not use it.                                                           |

Table 7: Host interface mode

Basic circuits 26/101

# 3.6 External memory

Basically, the netX 51/52 provide three different interfaces to connect external memory. All interfaces are working independently from each other:

Serial memory interface for QSPI Flash, SPI EEPROMs and MMC/SD-cards

This is the favorite place to store the program code.

QSPI with the Execution-in-Place (XiP) function can also run directly

the program code for some low priority background tasks.

Do not use SPI EEPROMs for new designs!

Parallel memory interface available only on netX 51 for Flash/SRAM/SDRAM

Mostly used with a cheap 8 MB/32-bit SDRAM to enlarge the internal

memory with a good overall performance.

Host memory interface for Flash, SRAM, SDRAM

It takes a lot of signals from the host interface and you have to check which functions are still available. For details, see chapter Host

Interface.

When connecting memory components to the parallel Flash, SRAM or SDRAM interface, designers should always recalculate the capacitive load of these interface signals. The limitations are:

Parallel memory interface 10 pF for data lines and 15 pF for all other signals

As standard you can only connect one memory device.

Host memory interface 30 pF on all signals

The capacitive load directly influences the signal timing (the higher the load, the longer the signal delay) which has a limited scope with SDRAMs. Since the allowed range of operating conditions (min./max. voltage, min./max. temperature) further influences signal timing, capacity limits need to be defined that ensure a safe operation throughout the whole voltage and temperature range.

If these capacity limits are exceeded, this may, to a certain extent, be compensated by two clock phase parameters of the SDRAM interface. Such "out-of-spec-designs" are imaginable, but require careful evaluation!

Note:

If you are using our standard firmware, consider that it supports only the memory devices listed in the reference section of this manual. Of course, other memories can also be used, but not without prior evaluation and tests. To clarify details, contact our netX Support!

Basic circuits 27/101

## 3.6.1 Serial memory interface

The netX 51/52 has a dedicated SPI/QSPI controller to be used for program code.

An additional SPI controller can be mapped to the MMIOs that are supposed to be used with external peripheral devices.

SPI/QSPI uses high clock rates. This means: Keep the traces short.

#### 3.6.1.1 SPI Flashs

SPI Flashs have already been on the market for a long time. We, thus, strongly recommend not to use these components for new designs due to the following disadvantages:

Longer program load time since they have only a single wire transfer and the bandwidth is only

one fourth of QSPI Flash

Non Execution-in-Place i.e. they cannot enlarge the size of the executable code, especially in

netX 52 applications

#### Important:

If you are using standard loadable firmware (LFW) without SDRAM for netX 52 designs, you cannot use SPI Flashs! See next section about *QSPI Flash* on page 28.

If you want to use other Flash memories, please contact Hilscher before.

While an SPI Flash can be connected to three different chip select signals, it must be connected to chip select 0 (SPI0\_CS0n), if the design is to be able to boot from this SPI Flash.

**Note:** SPI0\_CS2n is available on MMIO pins.

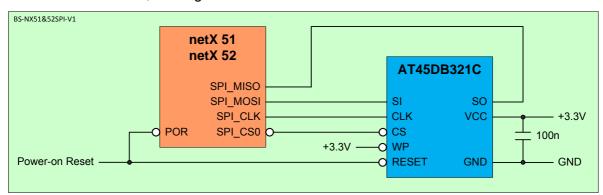

A standard component used by Hilscher was the AT45DB321 from ATMEL providing a capacity of 4 MB. For connection, see Figure 18:

Figure 18: netX 51/52 SPI Flash

**Note:** ATMEL does not continue with their serial EPROM business which was taken over from Adesto. The new component number is AT45DB321E.

Basic circuits 28/101

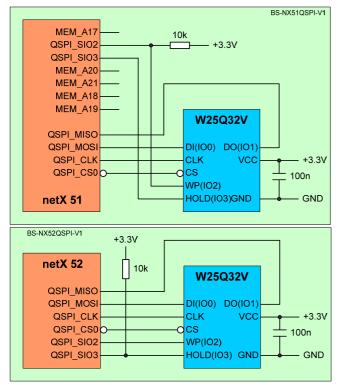

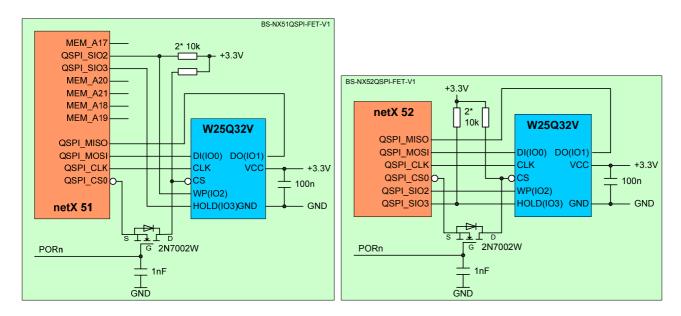

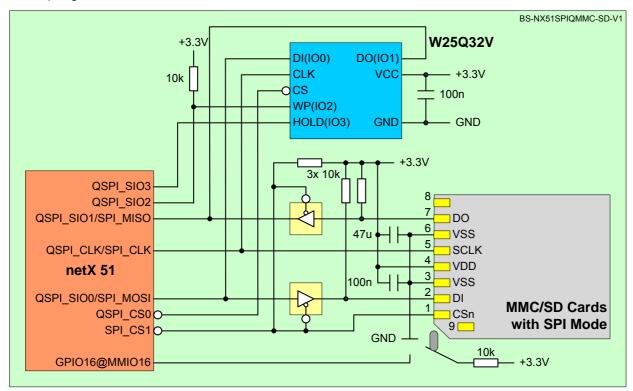

#### 3.6.1.2 **QSPI Flash**

Instead of a standard SPI Flash, a QSPI Flash may be used on netX 51/52 designs. It allows you to reduce the time required for loading large firmware images and to reduce boot up time. These Flashes can be switched to a second mode that allows the simultaneous serial transmission of 4 bit.

This feature has been implemented for designs that run PROFINET and are required to provide the so-called "Fast Startup" (FSU) feature. It is available on netX 51 and netX 52 for read and write.

The currently available solution allows a startup time for PROFINET slave firmware of less than 500 ms.

The supported Flash type is a W25Q32V from Winbond Electronics.

#### **Important:**

Since netX 52 uses XiP to execute loadable firmware, we highly recommend Windbond W25Q32. If you want to use other Flash memories, please contact Hilscher before.

Table 8 shows the pin connection for netX 51 and netX 52:

|         | Pin assignment | SPI_CSn<br>QSPI_CSn | SPI_CLK<br>QSPI_CLK | SPI_MOSI<br>QSPI_SIO0 | SPI_MISO<br>QSPI_SIO1 | QSPI_SIO2 | QSPI_SIO3 |

|---------|----------------|---------------------|---------------------|-----------------------|-----------------------|-----------|-----------|

| netX 51 | Standard       | U14                 | V15                 | V16                   | U15                   | P12       | R13       |

| netX 52 | Standard       | U15                 | V16                 | U16                   | T15                   | T14       | V15       |

Table 8: QSPI pin assignment netX 51/52

Figure 19 shows how to connect this Flash to netX 51 and netX 52:

Figure 19: netX 51/52 with QSPI Flash

Continued on the next page.

Basic circuits 29/101

**Note:** The FET is used to meet the datasheet requirement of this QSPI device: The CS signal should follow the power supply. According to experience and examinations the FET is left out in the Hilscher standard designs, this is not 100% compliant with the datasheet, but has not resulted in problems for many years.

Basic circuits 30/101

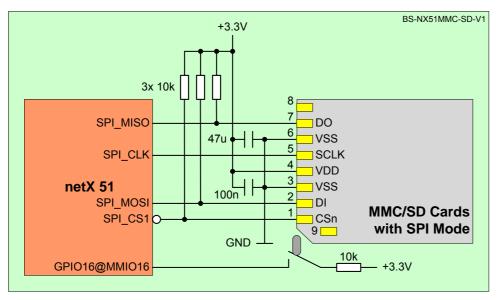

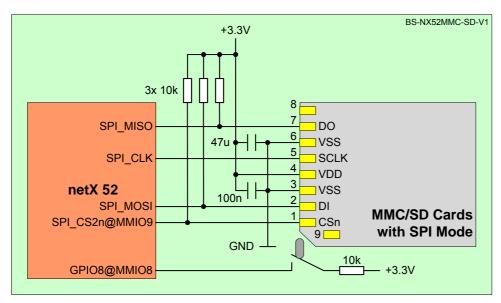

#### 3.6.1.3 MMC/SD card

Instead of an SPI Flash a MMC/SD card can be connected via SPI to the netX, which even allows you to boot a firmware image stored on such a card. To detect insertion or removal of the MMC/SD card during operation, an insertion signal has been defined which has to be pulled high if an MMC/SD card is in the socket. If the MMC/SD card is connected to the SPI bus in addition to a Flash memory, we recommend decoupling the MMC/SD card with switchable bus drivers.

| Function           | netX 51 pin name and number |     | netX 52 pin name and number |    |  |

|--------------------|-----------------------------|-----|-----------------------------|----|--|

| MMC/SD card insert | GPIO15 at MMIO16            | U2  | GPIO08 at MMIO08            | N2 |  |

| SPI Chip Select    | SPI0_CS1n                   | T14 | SPI0_CS2n at MMIO09         | P2 |  |

Table 9: MMC/SD card insertion and CSn signal

Figure 20: netX 51 MMC/SD card

Figure 21: netX 52 MMC/SD card

Basic circuits 31/101

**Note:** The card selection signals use the internal pull-down resistor at MMIO to have a defined low-level if there is no card. The pull-up resistors at DO, DI, CSn and the 47u capacitor are necessary according the SD card specification.

If the MMC/SD card is connected to the SPI bus in addition to a Flash memory, we recommend decoupling the MMC/SD card with a switchable bus driver.

Figure 22: MMC/SD card and Flash memory on SPI bus

**Note**: Drivers are required for parallel operation.

Basic circuits 32/101

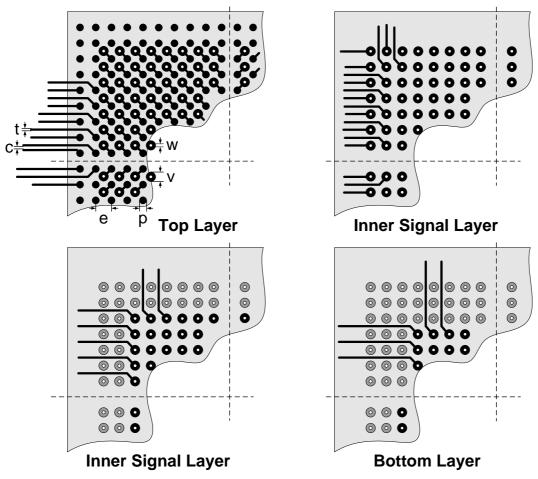

## 3.6.2 Parallel memory interface

netX 51/52 contain two completely independent external memory interface controllers. The first one is connected to the memory interface of netX 51, the second one to the host interface of netX 51/52. However, the SDRAM controller of the external memory interface differs from that of the host interface: The external memory interface SDRAM controller is a high-performance multichannel and multi-cache controller. The SDRAM controller of the host interface is a single-channel SDRAM-light controller containing 16 or 32 data bits.

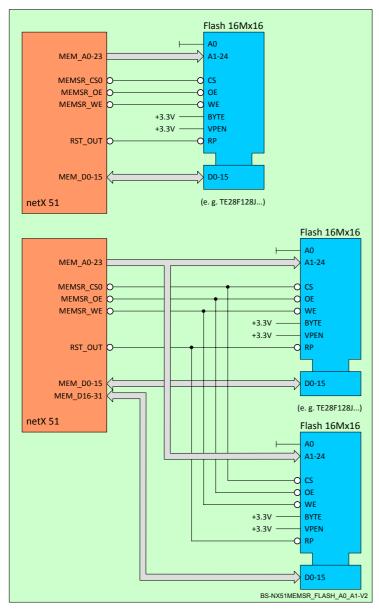

#### 3.6.2.1 SRAM and Flash

For large firmware images for applications executing code directly from the Flash, the use of a parallel Flash is inevitable. Parallel Flash connected to the netX 51 may be 8-, 16- or 32-bit wide; two 16-bit components may be paired for 32-bit wide access.

**Note:** rcX does not support a Flash file system at a parallel Flash.

For performance reasons, 32-bit components should be used when executing code directly from the Flash although 16-bit wide components are very common.

The netX 51 SRAM/Flash memory controller provides three different chip-select signals (MEM\_CS[2:0]) allowing to select three different memory components or pairs of components (two paired 16-bit Flashes use a common chip select signal), each with its own set of parameters (timing and bus width).

If the design is to boot from a parallel Flash, chip-select 0 must be used for selecting this Flash.

The memory controller is designed to never "waste" any address lines regardless of the bus width setting. Hence, in 8-bit mode, address line A0 is used for low and high byte selection, while in 16-bit mode A0 selects low and high word and in 32-bit mode, A0 is simply the LSB of a DWORD address.

For that reason, consult the data sheet of the desired Flash component to determine the correct way of hooking up the address lines of the Flash.

Basic circuits 33/101

Many (16-bit) Flash components (e.g. TE28F128J...) use address line A0 for low/high byte selection when operating the component in 8-bit mode. They do not use A0 at all when used in 16-bit mode. Hence, with such components A0 of the Flash must be grounded (to prevent floating), while A0 of the netX is connected to A1 of the Flash, A1 to A2, A2 to A3, etc. The following schematics show examples:

Figure 23: netX 51 Flash - Address line A0 for low/high byte selection

Basic circuits 34/101

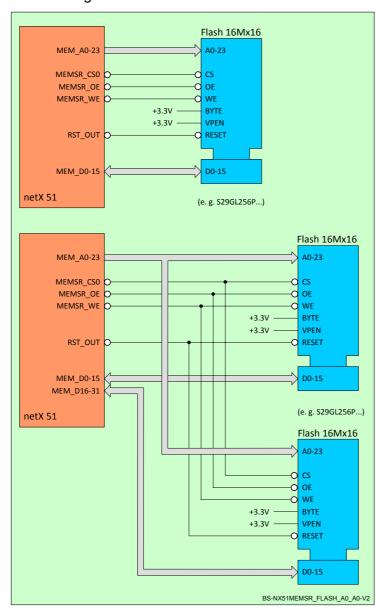

Other Flash components (e.g. S29GL256P...) always use A0 as the LSB of a word (16 bit) address. Hence, the address lines of such components must be connected straight forward as shown in Figure 24:

Figure 24: netX 51 Flash - A0 as the LSB of a word address

- Q1: Is it possible to access the parallel Flash connected to the netX by another processor (e.g. host processor) while the netX does not use the Flash or is held in reset?

- A1: This will work only with additional components. Since memory interfaces are usually not designed for multi-master access, the netX always drives all memory interface signals, except the data lines, even while it is held in reset state. Hence, accessing any memory components by another processor is possible only if the memory components can be isolated from the netX memory interface by appropriate bus switches.

Basic circuits 35/101

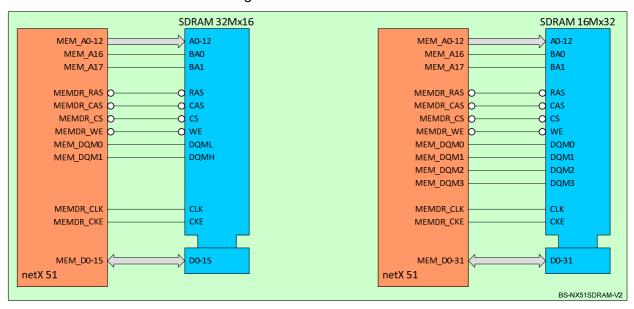

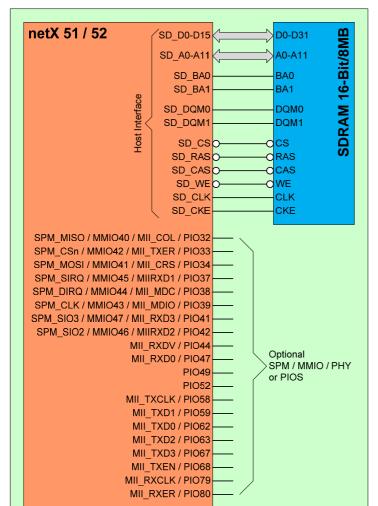

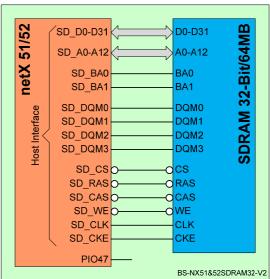

#### 3.6.3 SDRAM

The netX 51 has a separate memory bus to support an SDRAM.

netX 52 needs no external SDRAM, but an SDRAM can be connected to the host interface. In this case the DPM will be limited to a Serial Port Memory.

SDRAM components connected to netX may be 16-bit or 32-bit wide. Two 16-bit components may be paired to allow a 32-bit wide access. Using two 8-bit components (paired for 16-bit) or four 8-bit components (32-bit) is also possible.

For using SDRAM, designs of 32-bit width are generally recommended to make full use of the memory controller performance. The use of one 32-bit wide component instead of two 16-bit (or four 8-bit) components is further recommended due to an easier PCB design and reduced load capacity (two 16-bit components usually add twice the load to the address and control signals as a comparable 32-bit component).

- Q1: In the meantime DDR-3 RAM or higher is state of the art. Why are the netX chips only equipped with an outdated SDRAM interface?

- A1: Well, SDRAM isn't really outdated. DDR RAM technology was invented for the short-lived PC market on which it is commonly accepted that components have extremely short life cycles, a limited operating condition range, and substantial power consumption. Since DDR RAMs work with internal PLLs they cannot be used on older (slower) memory interfaces. DDR RAM technology is not suitable for the embedded / industrial market where customers usually look for an availability of several years. Further, even powerful embedded processor technology like ARM cannot necessarily compete with common PC processors in terms of processing power. Thus, it would make little sense to connect such processors to DDR RAMs anyway.

Connecting SDRAM to the netX is pretty straight forward, besides address lines A16 and A17, which are used for the bank select signals BA0 and BA1.

Figure 25: netX 51 SDRAM 1 \* 16 bit, 1 \* 32 bit

Basic circuits 36/101

### 3.7 Host interface

The netX 51/52 host interface (HIF) has 58 signals in total and provides various connections:

- 8/16/32-bit dual-port memory (DPM): section *Dual-port memory* on page 37

- Dual-port memory via SPI/QSPI (SPM): section Serial port memory (SPI/QSPI access to DPM) on page 42,

- 8/16/32-bit extension bus (EXT): section *Extension bus* on page 44,

- Media independent interface (MII): section MII port 2 acts as a PHY or MAC interface on page 48

- 16/32-bit SDRAM

- 8x MMIO for GPIO, UART, CAN, I2C, SPI

Table 10 shows the signals which can be combined on the host interface.

|         |        | Dual-port memory |          |        | Extension bus |          |          | SDRAM  |        | МІІ |

|---------|--------|------------------|----------|--------|---------------|----------|----------|--------|--------|-----|

|         |        | 8 Bit            | 16 Bit   | 32 Bit | 8 Bit         | 16 Bit   | 32 Bit   | 16 Bit | 32 Bit |     |

| MII     |        | <b>✓</b>         | <b>✓</b> | ī      | ✓             | ✓        | ı        | ✓      | ı      | -   |

| SPM     |        | -                | -        | -      | ✓             | 1        | -        | ✓      | -      | ✓   |

| 8x MMIO |        | ✓                | -        | -      | ✓             | <b>✓</b> | -        | ✓      | -      | ✓   |

| CDDAM   | 16 Bit | -                | -        | -      | <b>✓</b>      | <b>√</b> | <b>√</b> | -      | -      | ✓   |

| SDRAM   | 32 Bit | -                | -        | -      | <b>✓</b>      | <b>√</b> | <b>√</b> | -      | -      | -   |

Table 10: Signal combination on host interface

The host interface always works in little-endian mode.

The host interface signal buffers are **not PCI-compliant** and **not 5 V-tolerant**. However, they are equipped with internal pull-up resistors (nominal 50 k $\Omega$ ) and usually do not require any external pull-up resistors. Only pin HIF\_SDCLK with signal DPM\_SIRQ has an internal pull-down resistor (nominal 50 k $\Omega$ ).

Figure 26: Host interface connection possibilities

Basic circuits 37/101

#### 3.7.1 **Dual-port memory**

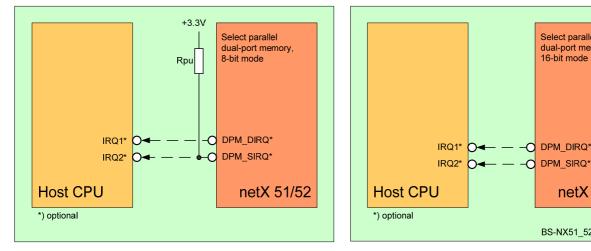

#### 3.7.1.1 8/16/32-bit data width and dual-port memory size

In DPM mode, netX 51/52 support 8, 16 or 32-bit data width. In general, the min. DPM size is 2 KB. With 8 or 16-bit data width the max, size is 1 MB, with 32-bit data width the max. DPM size is 256 KB.

Before you start your design, observe the following information:

### 8/16-bit mode

The second stage boot loader offers a detection function to select parallel dual-port memory mode (8 or 16 bit) or serial port mode. Therefore, the second stage boot loader evaluates the signal at pin DPM DIRQ and DPM SIRQ during startup. Table 11 lists the selected mode depending on the signal state.

| DPM_DIRQ signal during startup | DPM_SIRQ signal during startup | Mode                                        |

|--------------------------------|--------------------------------|---------------------------------------------|

| 1 (high)                       | 1 (high)                       | Parallel dual-port memory mode: 8-bit mode  |

| 1 (high)                       | 0 (low)                        | Parallel dual-port memory mode: 16-bit mode |

| 0 (low)                        | Х                              | Serial port mode                            |

Table 11: DPM\_SIRQ signal during startup

netX 51/52 has an internal pull-down resistor (nominal 50 kΩ) at DPM SIRQ and an internal pullup resistor (nominal 50 k $\Omega$ ) at DPM DIRQ. A pull-up resistor  $R_{pu}$  with a recommended value of  $2.2 \text{ k}\Omega$  is required to generate a high signal if the DPM\_SIRQ is not connected to the host CPU.

Figure 27: Using the second stage boot loader to select parallel dual-port memory with 8 or 16-bit mode

If DPM SIRQ or DPM DIRQ is connected to the host CPU, pay attention to the internal Note: resistor of the pin of the host CPU for dimensioning a pull-up or pull-down resistor to generate a proper signal according to Table 11.

### 32-bit mode

You can use netX in 32-bit dual-port memory mode. This requires you to configure the netX for this mode. If you use the second stage boot loader, you have to set parameters in the second stage boot loader to activate the 32-bit mode using the Tag List Editor tool.

Select parallel dual-port memory, 16-bit mode

DPM DIRQ\*

netX 51/52

BS-NX51\_52DPM8\_16-V2

Basic circuits 38/101

### **Dual-port memory size**

The default size of the DPM is 64 KB. If loadable firmware is used on the netX a size of 64 KB is the recommended size for a design and the host can access all communication channels located in the DPM. A dual-port memory size of 16 KB (address lines DPM\_A0 to DPM\_A13) is possible with loadable firmware, but the host can access one communication channel only! Address line DPM\_14 and DPM\_A15 have to be connected with a pull-down resistor of 1 k to GND to access the lowest 16 KB of the DPM. Be aware, if the host can access 16 KB of the DPM only, you will lose functionality and future extensions.

The address lines DPM\_A0 to DPM\_A15 are located at the same netX pins for all three modes 8, 16 and 32-bit mode and address a DPM size of up to 64 KB.

### Dual-port memory size of 128 KB and more

If you want to create a design with a DPM size of 128 KB (which requires DPM\_A16) or a size of 256 KB (which requires DPM\_A16 and DPM\_A17), make sure to use different pins for 8/16-bit mode and for 32-bit mode.

If you want to create a design with a DPM size of 512 KB (DPM\_A0 to DPM\_A18) or a size of 1 MB (DPM\_A0 to DPM\_A19), remember that you can use 8 or 16-bit mode only.

| Dual-port memory |         | 8/16-bit mode             |     | 32-bit mode |             |

|------------------|---------|---------------------------|-----|-------------|-------------|

| Size             | Address | netX 51 pin netX 52 pin ı |     | netX 51 pin | netX 52 pin |

| 128 KB           | DPM_A16 | B13                       | C12 | E14         | A17         |

| 256 KB           | DPM_A17 | A14                       | C11 | D14         | A18         |

| 512 KB           | DPM_A18 | A13                       | A11 | -           |             |

| 1 MB             | DPM_A19 | C12                       | C10 | -           |             |

Table 12: netX pin for a DPM size of 128 KB and more

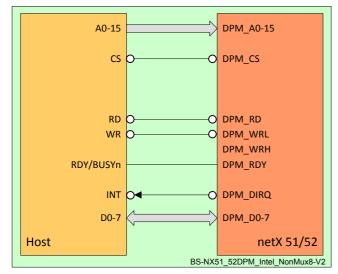

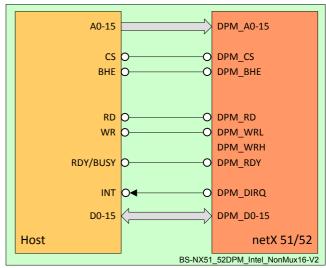

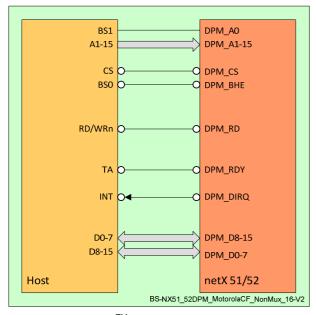

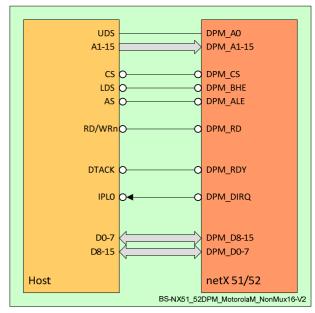

### 3.7.1.2 Control lines

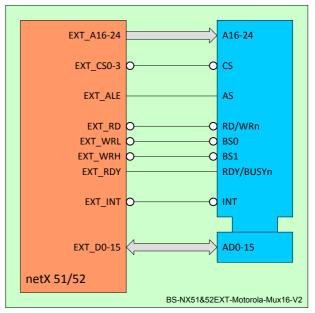

In DPM mode, the host interface can be controlled by separate read (RDn) and write (WRn, WRLn, WRHn) signals ("Intel mode") or by a combined RD/WRn signal indicating the direction of the access and byte strobe signals ("Motorola mode"). In "Intel mode", either a single write signal can be used (WRLn) or two write signals (WRLn, WRHn) for writing to the low byte (WRLn) and high byte (WRHn) separately.

In case of a 16-bit Host systems with word access, the address line A0 should be connected to GND. The following table shows the decoding logic for byte and word access.

| BHEn | A0 | Function         |  |  |

|------|----|------------------|--|--|

| 0    | 0  | word access      |  |  |

| 0    | 1  | access high byte |  |  |

| 1    | 0  | access low byte  |  |  |

| 1    | 1  | no access        |  |  |

Table 13: Function table of 16-bit decode logic

Basic circuits 39/101

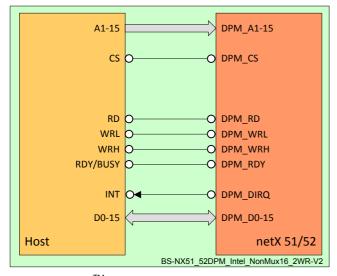

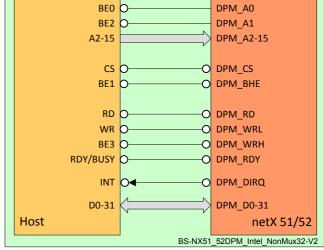

# 3.7.1.3 Non-multiplexed mode

The following schematics show some examples for common setups in non-multiplexed mode:

Figure 28: Intel TM interface, 8-bit, non-multiplexed

Figure 29: Intel ™ interface, 16-bit, non-multiplexed

Figure 30: Intel  $^{\rm TM}$  interface, 16-bit, non-multiplexed, 2 write signals (low byte, high byte)

Figure 31: Intel  $^{\text{TM}}$  interface, 32-bit, non-multiplexed

Basic circuits 40/101

Figure 33: Motorola TM M68000, 16-bit, non-multiplexed

# 3.7.1.4 Multiplexed mode

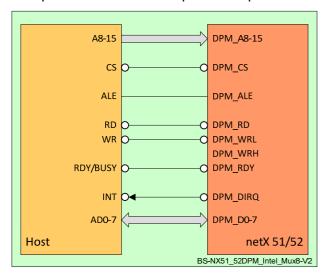

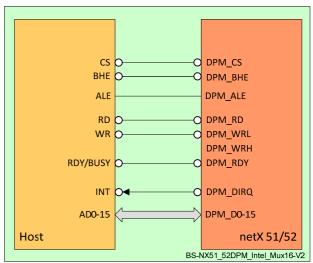

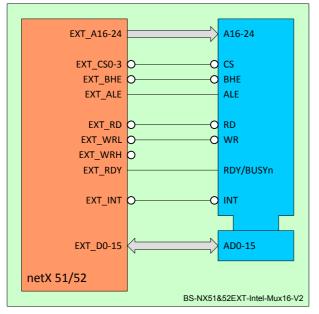

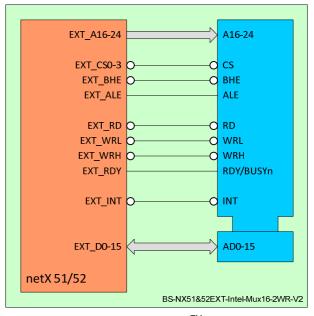

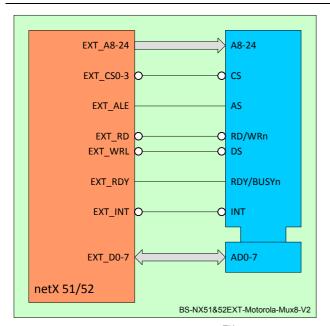

The netX host interface can also be operated in multiplexed mode in which the data lines are alternatingly used for data and the lower address signals. The following schematics show some examples for common setups in multiplexed mode:

Figure 34: Intel TM interface, 8 bit, multiplexed

Figure 35: Intel TM interface, 16 bit, multiplexed

Basic circuits 41/101

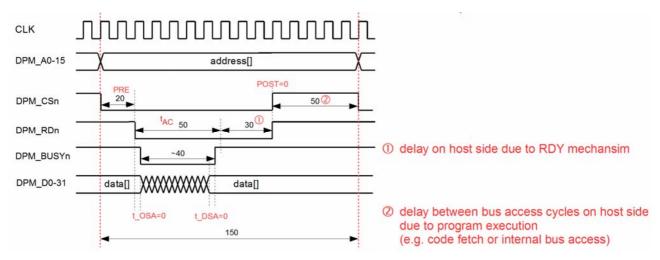

### 3.7.1.5 Ready/Busy signal

In the Dual-Port memory mode of the host interface the netX provides an internal memory area which can be read or written from the internal ARM CPU and from an external host CPU. As a real DPM, the netX uses a READY/BUSYn signal to resolve access conflicts if both CPU try to access the memory area simultaneously.

To make sure that the host processor will read valid data or the netX successfully accepts the written data from the host, while keeping access cycles as short as possible, it is **absolutely necessary** for the host processor to support the Ready/Busy signal in connection with netX.

To allow interfaces without glue logic, the netX Ready/Busy signal supports two different modes:

Ready mode: The active DPM\_RDY signal indicates that there is no access conflict.

Busy mode: The active DPM\_BUSYn signal indicates that the netX is still busy and the

cycle has to be delayed.

The Ready/Busy signal can be configured as an active high or active low signal, as push/pull or open drain, open source with sustained tri-state option (signal edge is actively driven).

**Note:** Our standard firmware uses the Busy mode with an active low signal. All schematics of this manual show the Ready/Busy signal as DPM\_BUSYn.

In the netX 51/52 Technical Reference Guide this signal often appears in the timing diagrams as RDY (Ready mode / active high).

Figure 36: DPM read access by using DPM\_BUSYn signal

If your host CPU does not support a Ready/Busy signal, you can access the DPM without it if you observe the guaranteed min. access time  $t_{AC}$  of 55 ns. In that case you have to set the host CPU pulse width of DPM\_RDn on 60 ns plus the required host CPU data set up time. This results in a short cycle time of about 100 ns.

Basic circuits 42/101

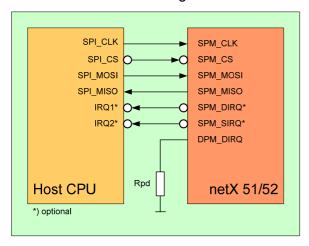

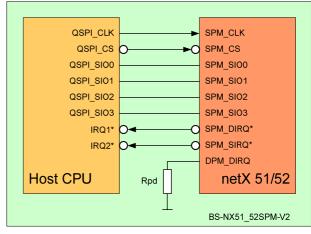

# 3.7.2 Serial port memory (SPI/QSPI access to DPM)

The netX 51/52 support the connection between host CPU and netX DPM via SPI and QSPI where the netX is the slave. Table 14 shows the SPI/QSPI serial DPM signals:

| Pin     |         | 001        | 0051        |                                               |

|---------|---------|------------|-------------|-----------------------------------------------|

| netX 51 | netX 52 | SPI signal | QSPI signal | Comment                                       |

| G16     | D18     | SPM_CLK    | SPM_CLK     | SPI or QSPI: serial clock input               |

| H16     | F17     | SPM_CSn    | SPM_CSn     | SPI or QSPI: chip-select input                |

| H15     | G16     | SPM MOSI   | SPM SIO0    | SPI: master out slave in data input           |

|         |         |            |             | QSPI: serial data bit 0                       |

| J16     | G18     | SPM MISO   | SPM SIO1    | SPI: master in slave out data output          |

|         |         | _          | _           | QSPI: serial data bit 0                       |

| D18     | C17     | -          | SPM_SIO2    | QSPI only: serial data bit 2                  |

| C18     | B17     | -          | SPM_SIO3    | QSPI only: serial data bit 3                  |

| G18     | C18     | SPM_DIRQn  | SPM_DIRQn   | Optional DIRQ for host (e.g. for data IRQ)    |

| G15     | B18     | SPM_SIRQn  | SPM_SIRQn   | Optional SIRQ for host (e.g. for service IRQ) |

Table 14: SPI/QSPI to DPM (serial DPM) pin assignment

The host CPU sends read and write commands via the SPI/QSPI connection to the netX controller. A state machine within the netX translates these commands into parallel read and write access to the DPM without interfering with the ARM CPU and sends the answer back to the host CPU.

Figure 37: SPI/QSPI to DPM interconnection

The second stage boot loader offers a detection function to select parallel dual-port memory mode or serial port memory mode. If you want to activate the serial port memory mode, a low signal is required at pin DPM\_DIRQ during startup. A pull-down resistor  $R_{pd}$  with a recommended value of 2.2 k $\Omega$  is required to generate this low signal. Note that a high signal at pin DPM\_DIRQ during startup activates the parallel dual-port memory mode.

If you do not want to use the detection function of the second stage boot loader, you can omit resistor  $R_{pd}$ , but you still have to activate the serial port mode. You can do this, e.g. by configuring the second stage boot loader.

Basic circuits 43/101

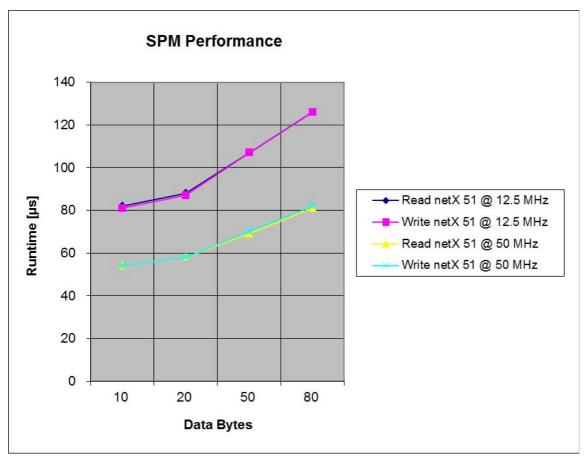

The SPI clock is defined up to 125 MHz and the QSPI clock up to 33 MHz. Due to the lack of a speed SPI controller, we have tested the connection up to 80 MHz. The following diagram provides information on the typical transfer rate:

Figure 38: SPM performance

Basic circuits 44/101

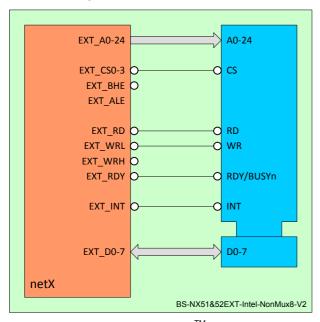

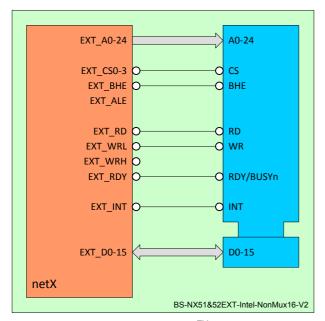

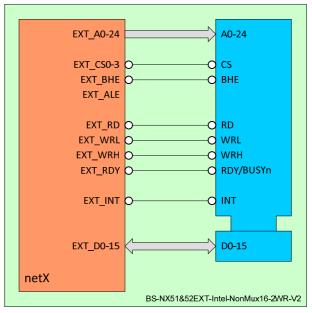

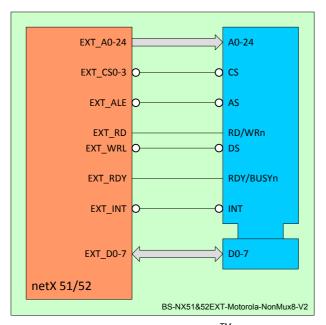

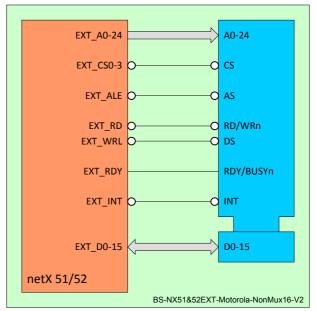

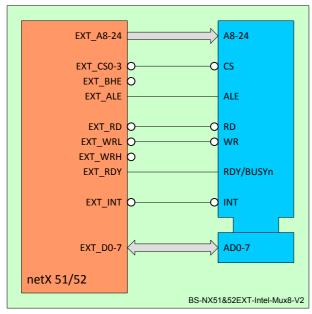

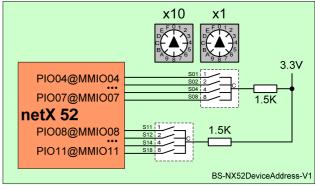

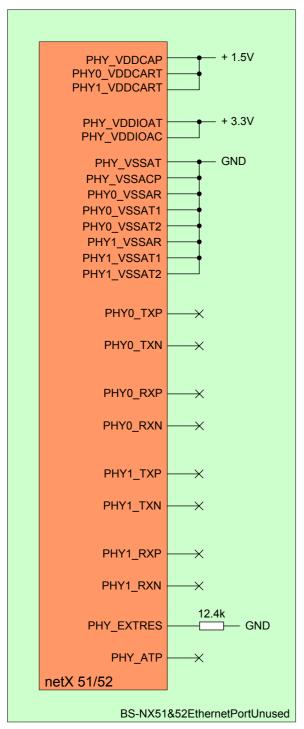

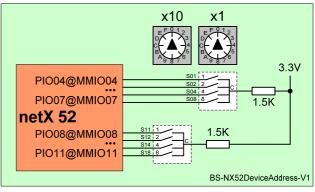

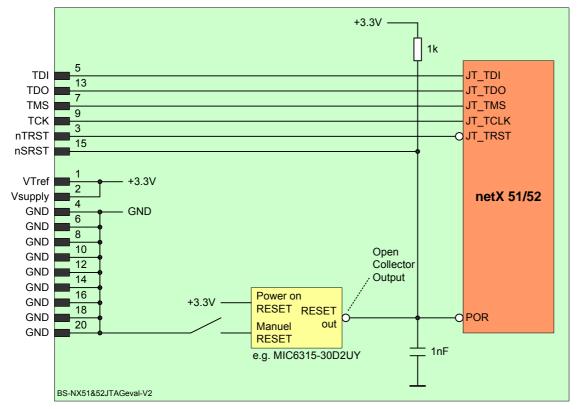

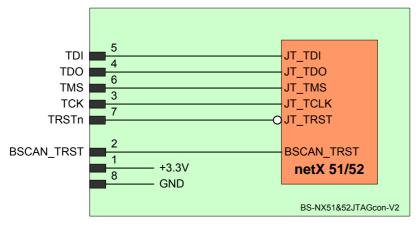

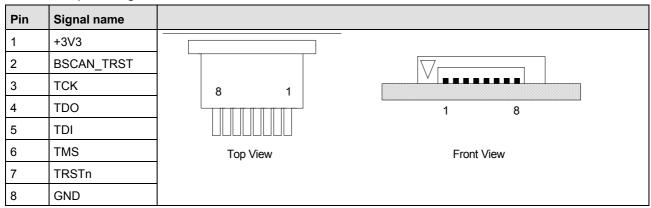

### 3.7.3 Extension bus