1

# 1 Help Contents

# CoDeveloper™ from Impulse Accelerated Technologies

# Version 3.70

Please review the Before You Begin section for important information.

Before You Begin (Read This First) Version History

<u>CoDeveloper Product Overview</u> <u>About Impulse C</u> Quick Start Tutorials <u>CoDeveloper Eclipse IDE</u> <u>CoBuilder User Guide</u> Impulse C User Guide Impulse C Function Reference <u>Platform Support Package Overview</u> <u>Registering Your Software</u> <u>License Agreement</u> <u>Copyright Acknowledgements</u>

All contents unless otherwise noted are Copyright © 2002-2015 Impulse Accelerated Technologies. All rights reserved.

# 1.1 CoDeveloper Product Overview

# Welcome to CoDeveloper™ Version 3.70

Welcome to CoDeveloper: advanced software tools enabling high-performance applications on FPGAbased programmable platforms. CoDeveloper allows you to: • Generate optimized VHDL or Verilog from C.

2

- Partition your algorithms using a multiple process, parallel programming model.

- Iteratively optimize, pipeline and parallelize your C-language applications for high performance.

- Describe and generate I/O, in the form of streams, signals, memories and registers.

- Create HDL modules for use with other hardware components, or..

- Create complete hardware/software systems for high performance, FPGA-based computing.

- Target a wide variety of available FPGA platforms.

CoDeveloper is designed for use with leading tools for embedded software and programmable hardware development, including FPGA synthesis tools, desktop C/C++ development tools and embedded compiler and debugger tools.

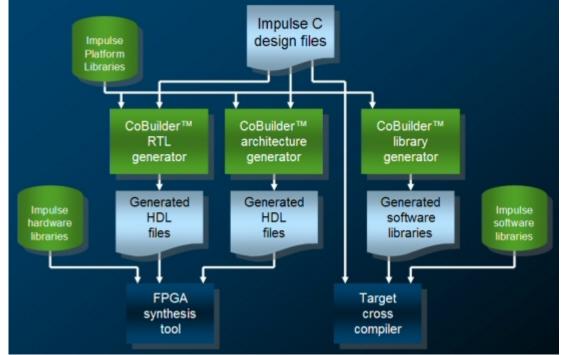

The complete CoDeveloper environment consists of a set of libraries allowing Impulse C applications to be executed in a standard C/C++ desktop compiler, for simulation and debugging purposes, as well as cross-compiler and translation tools allowing Impulse C applications to be implemented on selected programmable hardware platforms. Additional tools for application profiling and co-simulation with other environments, including links to EDA tools for hardware simulation, are provided.

## Introducing Impulse C

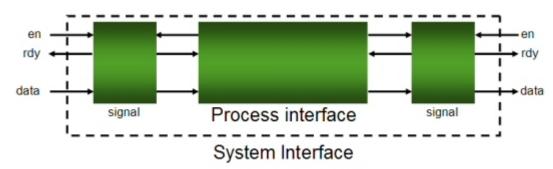

<u>Impulse C</u> is a library of functions and related datatypes that provide a programming environment, and a programming model, for highly parallel applications targeting FPGA-based platforms. Impulse C has been designed to simplify the expression, verification and compilation of complex applications consisting of multiple (potentially hundreds) of distinct parallel processes. Impulse C has been optimized for mixed software/hardware targets, with the goal of abstracting details of inter-process communication and allowing relatively platform-independent application design.

CoDeveloper includes the Impulse C libraries and associated software tools that help you use standard C language for the design of highly parallel applications targeting FPGAs. CoDeveloper includes an <u>Application Manager</u>, <u>Application Monitor</u>, compatibility with common development environments (including Microsoft Visual C++, Eclipse, and tools based on GCC), platform-specific FPGA compilers and other resources for Impulse C application developers.

## For Module Generation and for Processor Acceleration

There are two primary uses for Impulse C, and which of these two uses best fits your particular needs will impact how you use the Impulse C in combination with other FPGA development tools.

*Module generation* refers to the use of Impulse C, along with other methods of design (including VHDL and/or Verilog, and possibly other design tools based on Simulink or other high-level entry methods) to create one or more modules, or blocks, of intellectual property (IP) that will be combined with other IP to create a complete system. In this mode of use, you will use Impulse C to describe one or more connected hardware processes, generate hardware for these processes, then connect them, using traditional hardware design methods and tools, to other components in your system. For this purpose, you will need some understanding of hardware design and hardware description languages (HDLs). With this knowledge, you will be able to use Impulse C as a front-end design tool to rapidly create synthesizable hardware components. To understand how to interface your Impulse C processes to other components, you will also need to have a good understanding of Impulse C stream, signal, memory and register interfaces and how they relate to the generated hardware interfaces.

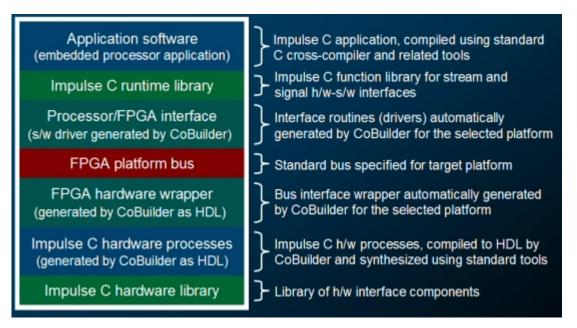

#### Processor acceleration refers to the use of Impulse C, in combination with a

<u>Platform Support Package</u>, to create a hardware-accelerated system. In this mode of use, your goal is to create one or more hardware accelerators that are directly connected, via predefined and automatically configured stream and memory communication channels, to an FPGA embedded processor, or to a host computer for server acceleration. To achieve this, you will not need to have deep knowledge of hardware design, and you do not need to be an experienced FPGA designer. You

will, however, need to have a basic understanding of the platform tools provided to you by your FPGA vendor, or the supplier of your FPGA-based computing system, and you will need to study the platform-specific tutorials and examples provided with the CoDeveloper product. It is also helpful if you have performed at least one of the platform tutorials provided by your FPGA vendor (or FPGA system vendor) so you understand the basic steps for creating an FPGA-based computing system.

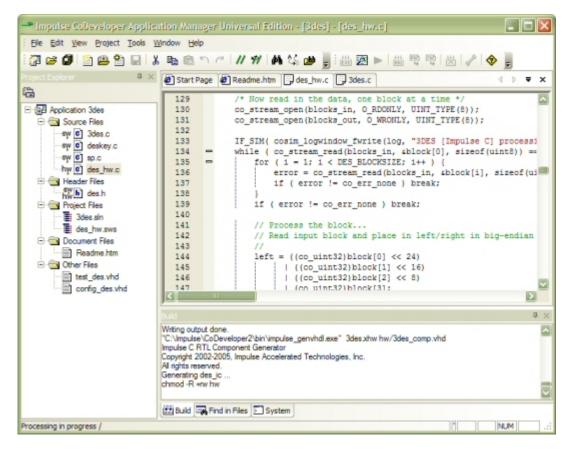

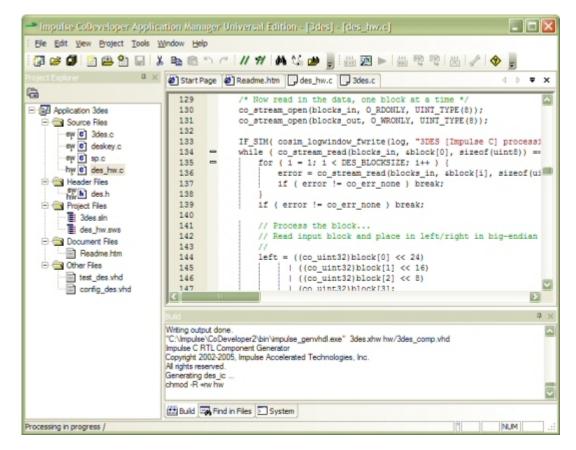

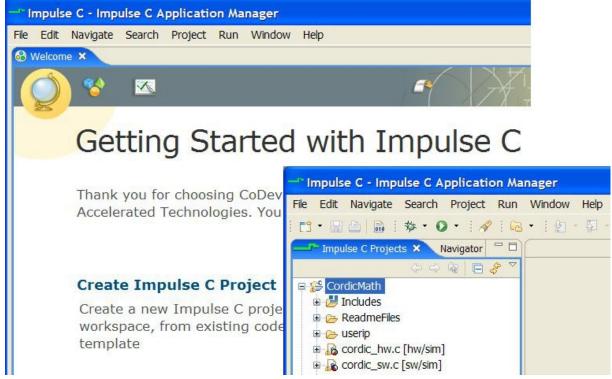

# The CoDeveloper Application Manager

The CoDeveloper Application Manager can be used to quickly generate new Impulse C applications, as well as to manage existing applications and their constituent files. You can use the Impulse C Application Manager to create entirely new projects (perhaps using the <u>Impulse C Design Assistant</u> to help create new Impulse C files) or to help manage existing Impulse C projects.

Because Impulse C is compatible with standard third-party compilers, you can use CoDeveloper in combination with popular development and debugging tools to form a complete application development environment.

# **Getting Started**

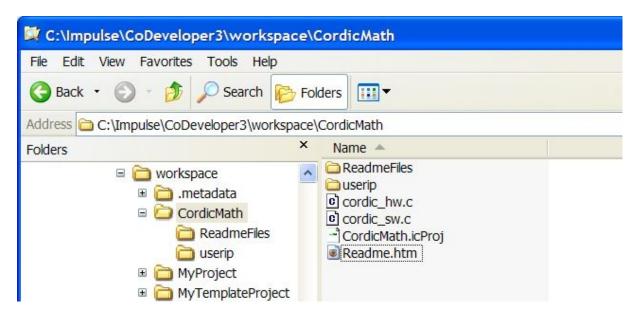

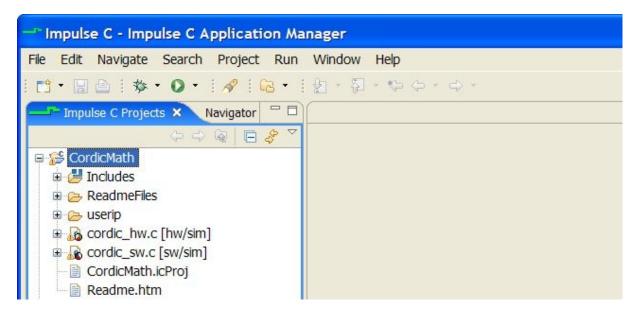

To get started using CoDeveloper and Impulse C, you should load one of the tutorial sample projects included in the Examples subdirectory of your Impulse C installation. The examples provided are intended to demonstrate a variety of useful Impulse C concepts, including various methods of specifying inter-process communication and the writing of Impulse C test routines (commonly called *test benches*). These examples will also help you to understand how to create and manage an Impulse C project.

To load a sample project, select the "Sample Projects" tab in the CoDeveloper Start Page. Select one

of the sample projects.

When you have opened a sample project, you will see one or more source files listed in the Impulse C Projects view. You can double click on any file name listed to open a source file editing window.

Note: Additional examples and tutorials are included with each Platform Support Package that you have installed with your CoDeveloper software, and on the Impulse website.

## See Also

About Impulse C Application Monitor Quick Start Tutorials

## 1.1.1 Before You Begin

### **Release Notes**

This is release 3.70 of CoDeveloper, from <u>Impulse Accelerated Technologies</u>. For a list of changes from previous versions, please see <u>Version History</u>.

# HOW TO GET STARTED

## Tutorials

Before starting with CoDeveloper, we strongly suggest that you make use of the supplied tutorials, either by following the steps presented or by casual reading. Doing so will make your initial work with CoDeveloper and Impulse C much easier, and will provide you with useful insights into parallel programming and mixed hardware/software development methods.

Several Quick Start Tutorials are provided in this Help document.

The Impulse website hosts the most up-to-date version of the Tutorials and other documentation:

http://www.ImpulseC.com/Tutorials

## Documentation

You can access this Help document, the *CoDeveloper User's Guide*, from the Help menu in the CoDeveloper Application Manager.

Documentation is provided with your CoDeveloper installation in the form of compiled HTML Help files (.chm). You can open any of these files, found in the "Help" and "Architectures" directories of your CoDeveloper installation, by double-clicking them.

#### Linux

The Linux edition of CoDeveloper does not include a graphical development environment. For documentation on developing Impulse C applications using command line tools, see the section <u>Command Line Tools</u>.

## **Platform-Specific Documentation**

Tutorials and documentation for specific FPGA boards or platforms are included in the Platform Support Package (PSP) Help files installed with your software. Open the PSP Help files from the

CoDeveloper Application Manager's Help menu; select "Platform Support Package Help" and choose the .chm file for your platform from the dialog that appears.

### Linux

Platform Support Package Help files are available in PDF format in the "Help" subdirectory of the CoDeveloper installation.

## Sample Projects

A number of sample Impulse C projects are included in this installation. Once you have a sample project open, you can review the Impulse C source code, build and run a desktop simulation, or invoke the Impulse C hardware compiler to generate HDL and hardware/software interface files.

To work with these examples:

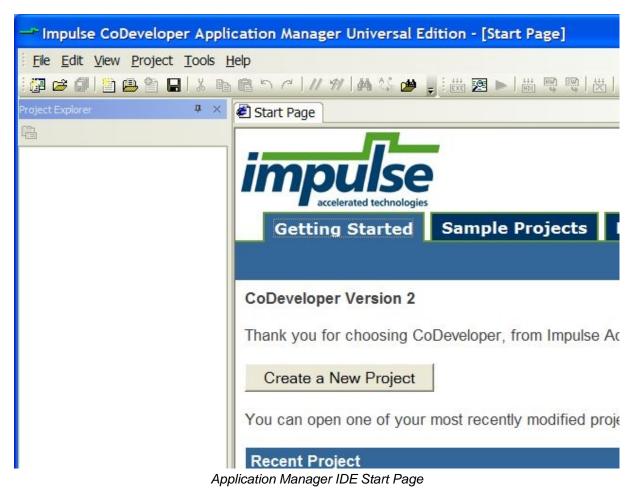

1. Start the CoDeveloper Application Manager by selecting Start > Impulse Accelerated Technologies > CoDeveloper 3.70 > CoDeveloper Application Manager.

2. The Start Page will appear; you can also open the Start Page by selecting the View > Start Page menu item.

- 3. Click the Sample Projects tab to display a page listing many Impulse C projects.

- 4. Click a project link to open the project.

### Linux

Sample Impulse C projects are found in the \$IMPULSEC\_HOME/Examples directory. See the section <u>Command Line Tools</u> to learn how to build an Impulse C project in Linux.

# **VISUAL STUDIO USAGE NOTES**

CoDeveloper includes an optional plugin for Microsoft Visual Studio. This plugin lets you simulate, debug, and generate HDL for an Impulse C project from within the Visual Studio environment. Documentation for the Visual Studio plugin can be found here:

http://impulsec.com/AppNotes/APP112\_VISUAL\_STUDIO\_08/APP112\_VISUAL\_STUDIO\_08.

### <u>pdf</u>

The Impulse C simulation libraries are compatible with and tested in the Visual Studio version 6, .NET (version 7), 2005 (version 8), and 2008 (version 9) environments. Sample projects for desktop simulation with Visual Studio may be provided with your installation. Please note that if you copy these sample projects out of the installation directory to your own working directory, you may need to modify the include and library file path settings within the Visual Studio project.

# SYSTEM REQUIREMENTS

### Windows

The following is required to make full use of CoDeveloper:

- CPU with 1GHz or better clock speed, 32- or 64-bit Intel/AMD architectures

- 1GB RAM

- Windows 2000, XP, or Vista

The following additional software is optional:

- Microsoft Visual Studio, or

- Any other Windows-compatible C/C++ development environment

#### Linux

6

- CPU with 1GHz or better clock speed, 32-bit Intel/AMD architectures (64-bit supported with a workaround, see below)

- 512MB RAM

- Red Hat Enterprise Linux (RHEL) 5.0 or later, or similar distribution

- gcc 3.4 or later

- GNU make 3.81 or later

# INSTALLATION NOTES

The following comments apply to all releases:

- The CoDeveloper Version 3 software can be installed on the same computer as CoDeveloper Version 2, but you will need to change the environment variables IMPULSEC\_HOME and IMPULSE\_GCC\_HOME to switch between versions. For example, if Version 3 is installed in "C:\Impulse\CoDeveloper3" and Version 2 is installed in "C:\Impulse\CoDeveloper2", then you will need to change IMPULSEC\_HOME to reflect the version you are currently using.

- Due to limations in FPGA tools, it is not recommended that you install CoDeveloper into a directory that includes spaces in the directory path (such as "C:\Program Files") or create CoDeveloper projects in directories that include spaces (such as "My Documents"). Doing so may cause unexpected errors in third-party FPGA synthesis/place-and-route tools.

### Linux

• After installation, the IMPULSEC\_HOME, PATH, and LD\_LIBRARY\_PATH environment variables will be set automatically at login time by a shell script installed in /etc/profile.d. If these variables are not set upon login, they may be set manually by running "codeveloper-profile.sh" (found in the CoDeveloper installation directory).

### Linux (64-bit)

- Install 32-bit gcc and libc libraries. These packages' names differ across distributions. For example, Kubuntu requires the lib32gccl and libc-dev-i386 packages.

- Edit \$IMPULSEC\_HOME/MakeRules/Makefile.rules, adding the "-m32" flag to both CFLAGS and LDFLAGS variables.

- Modify \$LD\_LIBRARY\_PATH to include paths to 32-bit libraries first. For example: export LD\_LIBRARY\_PATH=/usr/lib32:/lib32:\$LD\_LIBRARY\_PATH

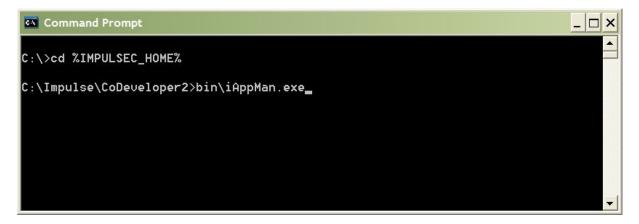

# IMPULSEC\_HOME ENVIRONMENT VARIABLE

The CoDeveloper installation creates an environment variable, IMPULSEC\_HOME, that must be set to the installation directory (typically "C:\Impulse\CoDeveloper3"). This environment variable is used to locate many resources required by the CoDeveloper environment.

For example, IMPULSEC\_HOME must point to a directory containing a "Libraries" subdirectory, and the "Libraries" directory in turn must include the Impulse C desktop simulation libraries (impulsec.dll and impulsec.lib in Windows, or libImpulseC.so in Linux).

### Windows

The "Libraries" subdirectory must be on the PATH so your compiled application can find impulsec.dll at run-time.

# SYNPLICITY USAGE NOTES

To synthesize CoDeveloper outputs using Synplicity Synplify, you will need to create a Synplify project and import the Impulse component library files into that project along with the CoDeveloper-generated HDL files (which are normally written to the "Hardware\hw" subdirectory of your project). If you make use of the Export Generated Hardware feature of CoDeveloper, these library files will be copied to your specified Synplify project area automatically. The Impulse library files must be assigned to the library "impulse" in your Synplify project.

Note also that if you are synthesizing VHDL generated by CoDeveloper using the Synplify or Synplify Pro tools, you will need to modify the Impulse library file "impack.vhd" as follows (beginning at around line 153):

```

-- NOTE: Synplicity Synplify does not support signatures. Use the commented

version

-- of the following attribute statement if you encounter errors during analysis.

--

function sub(v1, v2 : std_ulogic_vector) return std_ulogic_vector;

attribute ccs_op of sub [std_ulogic_vector, std_ulogic_vector return

std_ulogic_vector] : function is "-";

-- attribute ccs_op of sub : function is "-";

```

#### Change to:

```

-- attribute ccs_op of sub [std_ulogic_vector, std_ulogic_vector return

std_ulogic_vector] : function is "-";

attribute ccs_op of sub : function is "-"; -- No signature

```

This change is required due to limitations in the Synplicity VHDL analyzer, which does not support the use of signatures. (Note that this change may result in warnings or other errors in certain VHDL simulators.)

## See Also

Version History License Agreement

## 1.1.2 Version History

### Version 3.70.e

- Updated October 19, 2012

- Added plugin for Visual Studio C++ 2010 Express and Standard editions

- Added support for multi-bank memory in SM Debugger

- Added support for co\_memoy\_readblock/writeblock with multi-bank memory

- PSP:

- Fix MicroBlaze DVI PSP HDL to compile correctly with ISE v13.4+

- Added Altera Qsys PSP supporting Avalon-ST and NIOS II withn Qsys

- Removed nonexistent Virtex-6 PLB and APU PSPs, please use relevant MicroBlaze PSPs instead

- Performance improvements for impulse\_arch3 and impulse\_genlib to speed up generating large (>100 processes) designs

- · Fixed unintended latch generation in banked memory

- Fixes in primitive functions:

- · Fixed issue with return value timing

- · Fixed issue with multiple primitives executing in the same stage

- Fixed array argument in primitive call under conditional control

- · Fixed address to array from output pointer

- Fixed extra stream read in pipeline when break appears before call to co\_stream\_read()

- Fixed crash due to unused global variable

### CoDeveloper from Impulse Accelerated Technologies

- Fixed Verilog parameter generation in autoip

- Fixed generics mismatch error when running Altera PSPs with SM Debugger

### Version 3.70.d

- Updated January 31, 2012

- <u>CoValidator Testbench Generator</u>: New support for Active-HDL

- New support for PSP options

- Bug fixes

8

## Version 3.70.c

- Updated October 31, 2011

- Enabled shared memory configurations in multiple-PE designs

- · Fixed a problem with Verilog generation related to 'x' assignments in final else clauses

- Modified the \_top.v/.vhd output file to correctly include stream adapters

### Version 3.70.b

- Updated July 28, 2011

- Improved optimization performance

- Fix issue with read-only global scalar variable initializations

- Update Xilinx floating point support to v4.0 of the Xilinx libraries

- Improved floating/integer conversion functions for Xilinx targets

- Bug fixes

### Version 3.70.a

- Updated June 6, 2011

- Many new optimization features including floating point optimizations

- Improved Stage Master Explorer interface

- Support for register arrays

- Updated and improved PSPs

- Updated examples

### Version 3.60.d

- Updated February 1, 2010

- New floating point optimization features

- Added support for math library

- Updated and improved PSPs including XD2000i and GiDEL

- Updated examples

## Version 3.60.a

- Updated August 31, 2009

- New PSPs: Xilinx Virtex-6 APU and PLB v4.6

- Updated <u>online tutorials</u> for Xilinx ISE 11.2

- CoValidator: User-defined startup script for ModelSim (autorun.do)

- CoValidator: Refer to Altera libraries when using ModelSim Altera Edition

- · CoValidator: Remove CoValidator stream traces on 'clean'

- · CoValidator: Don't overwrite ModelSim batch files, to preserve user edits

- No limit to width of streams in desktop simulation

- · Bug fix: Multidimensional array offsets calculated with missing bits

- Bug fix: Five bits used to compare 64-bit integers

- Bug fix: Maximum number of predicates exceeded

- Bug fix (XD1000 PSP): Generate makefile to include co\_util.c when building library

• Pico Computing PSP for E-14 and later supports CoreGen

## Version 3.50.a

- <u>CoValidator Testbench Generator</u>: Create ModelSim HDL testbenches

- New PSPs: Xilinx DVI Filter, for Video Starter Kit; additional PSPs add MicroBlaze FSL and PLB support

- New PSP: Virtex-5 PowerPC PLB v4.6; streams, signals, and registers only

- PSP- and board-specific tutorials updated and moved to web: <u>http://www.ImpulseAccelerated.com/Tutorials/</u>

- "Scalarize array variables" option works with all integer types

- Enforce support/maintenance expiration date in license

- Speed up license checkout, most noticeable in Linux release

- Corrections to Help sections on the CoDeveloper IDE

- Bug fix: Generate one co\_port for a co\_register with multiple connections to processes

- Bug fix: Visual Studio plugin uses wrong path when CoDeveloper installed in a non-default location

- Bug fix: Visual Studio plugin PSP listing was out of date

- Bug fix: Hardware processes writing streams flush data when closing

- Bug fix: Desktop simulation deadlock in co\_stream\_close after multiple reopen

- Bug fix: AppMonitor Help not found

# Version 3.40.a

- Updated February 17, 2009

- SGI RC100 RASC 2.2 PSP: Includes shared memory (co\_memory) support for onboard SRAMs

- New PSPs: Xilinx Open Source Linux Virtex-5 APU and Virtex-4 APU

- Linux installer: Environment variables set automatically on login, using /etc/profile.d

- Linux installer: Fix error w/partial context using chcon

- · Linux installer: Non-root user install script, linked on website from install instructions

- Improved compiler reports on pipeline performance

- Updated documentation on pointer support

- Display support expiration date in CoDeveloper Application Manager

- Bug fix: impulse\_sm crash when pipelining a primitive in limited cases

- Bug fixes related to pipelining primitives and pointer parameters to primitives

# Version 3.30.a

- Updated December 15, 2008

- Improved pipeline scheduling, to allow rate=1 pipelines in some cases

- Microsoft Visual Studio 9 plugin for Impulse C projects

- New example: ComplexFIR for Xilinx MicroBlaze

- Updated Xilinx MicroBlaze tutorials for EDK 10.1i SP3

- Corrections to Impulse C Function Reference for co\_register functions

- Clarified Help documentation on HDL testbenches using streams

- Corrections in PowerPC PSP documentation

- Add missing PDF Help documents to Linux release

- Bug fix: Add missing cosim\_log.h to Xilinx MicroBlaze FSL PSP

- Bug fix: Buffer overflow in impulse\_impc.exe

- Bug fix: Logical "not" precedence error in VHDL

- Bug fix: Stream operation return value comparison

- Bug fix: Out-of-order stream writes w/conditional

- Bug fix: Stage Master Explorer crashes when changing stageDelay several times

- Bug fix: Signed multiply generated mistakenly for int16\*uint16

### Version 3.20.b

- Updated September 3, 2008

- Stage Master Explorer for Linux

- Updated Xilinx PowerPC and MicroBlaze tutorials for EDK 10.1i

- Reduced logic usage for asymmetric multipliers

- Bug fix for byte-size DMA transfers with PLB v4.6

- Support hardware/software export in Linux for the XD1000 PSP

- Support multiple concurrent software processes communicating with hardware on the XD1000

- Updated XD1000 PSP to support stream base addresses in SOPC Builder >7.0

- Added DGEMM tutorial to XD1000 Help

- Updated Opal Kelly PSP documentation

- Added Opal Kelly Mandelbrot sample project

- Removed Cray XD1 PSP and examples

- Bug fix: Stage Master crashes under Windows Server 2003

## Version 3.20.a

- Updated June 25, 2008

- Altera floating-point library for all Altera-based PSPs

- New PSP: Xilinx Virtex-5 APU (streams only)

- New PSP: Xilinx BlueCat Linux MicroBlaze FSL

- New PSP: Xilinx PowerPC PLB v4.6

- MicroBlaze v7 support

- XtremeData XD1000 PSP co\_memory interface updated for better performance

- Microsoft Windows Vista support

- Microsoft Visual Studio 8 project generator (Beta)

- New example: DGEMM for XtremeData XD1000

- Updated ComplexFIR tutorial for Xilinx ISE 10.1i

- Updated the ImageFilter5X5 example for better pipelining

- Stage Master Explorer: Annotate HDL with original C source line numbers

- Fewer misleading messages from libCoreGenCommon.tcl

- Bug fix: Add missing mem\_if.vhd to Opal Kelly PSP

- Bug fix: Bad names in co\_stream\_attach (Quartus 7.x)

- Bug fix: New File (Design Assistant) does not add file to project properly

- Bug fix: Help links broken in Eclipse IDE

- Bug fix: Correctly output >64-bit constants when generating HDL

- Bug fix: Latches were inferred for some registers in Verilog when using ISE

- Bug fix: Constant values not generated correctly in HDL under Linux

- Bug fix: Stage Master Debugger (ccycle.exe) not found in some installations

- Bug fix: co\_signal outputs not captured correctly in VHDL

- Bug fix: Some co\_memory logic was synthesized away in Verilog

- Bug fix: Variable latched on last stage of pipeline got incorrect data

## Version 3.10.b

- Updated February 15, 2008

- First release for Linux

- Scheduler improvements and bug fixes

- Multiplier generation controlled with CO SET pragmas; support generation as pipelined or nonpipelined DSP blocks, or as LUTs, for Xilinx platforms

- Xilinx CoreGen library support, including pipelined divider and CORDIC functions

- Updated Xilinx PSP documentation on shared memory locations

- Remove Altera Nios Platform Support Package (Nios II still supported)

- Performance updates to some examples

- Fix minor issues in MicroBlaze ComplexFIR tutorial

- Updated SGI PSP docs on co\_iterate\_hardware and "done" flag, stream sizes; added section on troubleshooting

- SGI PSP automatically generates a bitfile using ISE upon hardware export

- Bug fix: Add missing signals to Verilog co\_memory interface

- Bug fix: "Enable logic cannot be generated for net types" error w/Verilog input co\_signals

## Version 3.00.b

- Updated November 20, 2007

- First public 3.0 release (Beta)

- Updated documentation for Eclipse IDE

- New PSP: GiDEL PROCWizard

- New PSP: SGI RC100 (RASC)

- Replaced DRC RPU110-L200 PSP with updated VHDL version

- Updated Pico PSP for E-16; revised software driver for better performance, new bitfile build process

- Added ComplexFIR tutorial example for MicroBlaze and EDK 9.2i to replace 3DES

- Bug fix: Error finding environment variable with recent Altera tools releases

- Bug fix: Error generating memory interfaces for Verilog platforms

# Version 3.00.a

- Updated October 13, 2007

- First 3.0 release (Alpha)

- Eclipse IDE for managing Impulse C projects, including built-in C debugger

- · Support for array offsets and global arrays in co\_memory block read/write operations

- Default locations for co\_memory

- True dual-port memory for Altera FPGAs

- Xilinx PLB shared memory

- Shared memory I/O timing improvements

- · Verilog floating-point support for Xilinx platforms, using XST

- Use divmod modules for modulus and division in Verilog

- New PSP: DRC RPU110-L200, v1.0

- PSP infrastructure: Pass streams' co\_kind in connection list (for PSPs' GenerateBUS)

- Sync legacy IDE's State Page sample project list with V3 list

- Minor editing fixes to PSP Help files and sample projects

- Sample project: MicroBlaze MemoryIO example uses single-process producer/consumer

- Sample project: Fix 3DES example VHDL test bench stream timing errors

- Sample project: Fix compilation error in Mandelbrot sample for Virtex-4 APU under EDK 9.1i

- Bug fix: Block RAM generation problem for Verilog PSPs

- · Bug fix: Close PLB hardware-to-software streams properly

- Bug fixes: FLATTEN pragma code generation

- Bug fix: Crash with pipelined primitive

- Bug fix: Pipeline with latency >64 does not start (Verilog)

- Bug fixes: Pipeline termination problems

- Bug fix: Floating-point operations inside conditionals

# Version 2.20.h

- Updated May 8, 2007

- Updated XtremeData XD1000 Platform Support Package to version 1.1

- Bug fix: sema.vhd not exported for some platforms

- Bug fix: Semaphore counter off by one

### Version 2.20.g

12

- Updated April 27, 2007

- Primitive functions can be pipelined

- Switch statements supported within if-statements

- Bug fix: Xilinx APU co\_stream\_close malfunctioning

- Bug fix: Xilinx APU HW\_STREAM\_READ\_NB macro returns incorrect value on success

- · Bug fix: Passing/storing library options from CoDeveloper options dialog

- Bug fix: Non-32-bit co\_signals generated as co\_ports have incorrect port sizes

- Bug fix: Various Verilog stream issues (e.g., data always zero)

- Bug fix: Global array logic synthesized away ("wr0" port tied to zero)

- · Bug fix: Xilinx floating-point division scheduled incorrectly

- Updates to Sample Project and Help and Support listings on Start Page

- · Minor updates to some example projects

### Version 2.20.f

- Updated March 1, 2007

- Floating-point types are displayed in Application Monitor

- New project template: One-Process Testbench (Floating-Point)

- Updated Xilinx MicroBlaze tutorials for ML401 board and EDK 8.2

- Improved PLB wrapper timing

- FSL reset connection fix

- · Active-low reset supported in FSL wrapper

- Improved support for APU instruction flushing

- Bug fix: APU conflict with FPU instructions

- Bug fix: "long long int" warning in impulse\_prep

- · Bug fix: Opal Kelly export failed to copy any files

- Bug fix: "driver" directory not exported for Xilinx platforms

- Bug fix: HDL generation problem with co\_memory\_ptr

- Bug fix: co\_signal\_wait not blocking

- Bug fix: Problem with multipliers in Altera Quartus

- "Allow double-precision types and operators" option always available

## Version 2.20.e

- Updated January 10, 2007

- New optimization: Multiplier generation analyzes casts and constants to minimize size

- · New optimization: Multiply/divide by two is replaced by bit shift operation

- New optimization: Modulo by power of two is replaced by logical AND operation

- co\_register\_read and co\_signal\_wait no longer require a cycle delay (Xilinx, Altera platforms)

- · Non-constant operands supported on right-hand side of shift operations

- Initial support for custom I/O implementations

- · Bug fix: Unsupported MPD file parameter causes warnings

- Bug fix: Verilog user IP not included in pcore

- New PointerSort example illustrating memory usage

# Version 2.20.d

- Updated December 19, 2006

- New Mandelbrot tutorial for Opal Kelly

- New ComplexFIR example for Xilinx MicroBlaze FSL

- Improved hardware generation error messages

- · Bug fix: Global variable access in multiples of same process gives bad HDL

- Bug fix: Export source dir is not taken from Generate Options

- Bug fix: Export Verilog files for Xilinx EDK

- Documentation update: stream burst operations

# Version 2.20.c

- Updated December 4, 2006

- Added XtremeData Platform Support Package

- Corrected errors in project templates

- Added new single-process test bench template

- Updated Pro Tools installer

- Added 0-bit signals to Verilog output

- Updated Pico Computing E-14 platform support

- Updated Opal Kelly platform support for FrontPanel 3.0

- Added edge-detection example with 5X5 kernel

- Updated documentation

- Fixed various optimizer defects

## Version 2.20.b

- Updated August 31, 2006

- · Added support for array function parameters

- Added Lattice FPGA platform support files (Verilog output)

- Added National Instruments LabVIEW FPGA platform support files

- Added Pico Computing E-14 Cardbus platform files

- Fixed bug related to co\_register types

- Improved Altera Quartus tutorial documents

- Added Verilog support for Altera Nios 2 platform

- Added quad-word read/write macros for Xilinx Virtex-4 FX platform

- · Added library options field to Generate Options dialog

- Added co\_stream\_config function

- · Various optimizer and hardware generation improvements

# Version 2.10.g

- Updated June 13, 2006

- Added support for co\_semaphore types and related functions

- Added support for n-bit signals via co\_signal\_create\_ex function

- Added FFT32\_Fixed and FFT32\_Float examples

- Added support for external HDL functions via CO IMPLEMENTATION pragma

- Added support for dual port memories in Altera FPGAs

- Added ExtFunction, Cordic\_Sine and CordicMath examples

- Improved support for co\_port interfaces

- Fixed problem related to implicit latches in hardware primitives

- · Fixed problem related to unary minus operations for float types

# Version 2.10.e

- Updated March 28, 2006

- Added support for active-low reset

- Updated tutorial for Xilinx Virtex-4 APU (EDK 8.1)

- Added support for Nallatech DIMEtalk

- Added support for fast clock floating point cores (Xilinx)

Documentation improvements

## Version 2.10.d

14

- Updated February 28, 2006

- Added support for double-precision floating point (Xilinx targets)

- Resolved an optimization problem with complex control statements

- Fixed library incompatibility with EDK 7.1

- Fixed problem with shared OPB memories

- Added examples ImageFilterKernel and ImageFilterKernel5X5

- Fixed problem with certain mod operations

## Version 2.10.c

- Updated February 3, 2006

- Updated examples mult32x32, mult18x18, DNA

- Fixed stream write blocking problem with OPB (Xilinx targets)

- · Fixed problems with pointer arguments to hardware functions

- Fixed problem with CO FLATTEN pragma

## Version 2.10.b

- Updated January 13, 2006

- Updated FFT example (Xilinx)

- New example: BubbleSort

- Updated Project Templates

## Version 2.10.a

- Released December 28, 2005

- Support added for C structs (see restrictions)

- Support added for single precision floating point (Xilinx targets)

- Resolved error with multiple-cycle hardware primitive functions

- New example: EdgeDetect\_struct

- Improvements made to Cray XD1 platform support package

## Version 2.01.g

- Released November 4, 2005

- New Project Wizard templates added

- Support added for global static arrays added (Xilinx platforms)

- · Problem with 64-bit assignments resolved

- · Pipeline optimization issues related to type conversions resolved

- Sign-extension problem with division operations resolved

- Problem with FLATTEN pragma hardware generation resolved

- Improvements to Cray XD1 platform support (Beta release)

- Updated Xilinx MicroBlaze tutorials

- Pipeline graph format change

# Version 2.01.f

- Updated October 15, 2005

- New Project Wizard added

- Problem with (0 downto 0) VHDL vector conversions fixed

- Problem with array size rounding fixed

- Added Synplicity project file generation (Tools menu)

- Verilog output improvements

- · Various optimizer and code generator improvements

- New examples: SquareRoot, RadixSort and Mult32X32

## Version 2.01.e

- Updated September 8, 2005

- Support for hardware functions and the PRIMITIVE pragma

- New generate option "Do not include co\_ports in bus interfaces"

- New FLATTEN pragma for generating combinatorial logic

- New NONRECURSIVE pragma for forcing non-recursive pipeline optimizations

- · Support for .mak files in the project explorer

- Support for abs() operation via macro

- Fixed error with array sizes (rounding up to nearest power of 2)

- Verilog output improvements

- New Prime example demonstrating use of a hardware function

# Version 2.01.d

- Updated July 25, 2005

- Support for FlexIm license manager

- Support for std\_logic (resolved) types in top-level interface

- New block diagram window in Application Monitor

- Support for external editors

- Optimizer and IDE bug fixes

# Version 2.01.c

- Released June 30, 2005

- Support for Verilog output

- New co\_port type for module generation

- New Application Monitor interface

# Version 2.01.b (Beta)

- Released April 29, 2005

- New Application Manager user interface

- Redesigned Design Assistant

- Redesigned HDL generator

- · Preliminary support for Verilog output

- Many optimizer and code generation improvements

- Improved error messages

- Reorganized examples directory

# Version 1.22.d

- Released January 28, 2005

- Added co\_par\_break statement

- Resolved issue with multiple pipelines and redundant HDL declarations

## 16 CoDeveloper from Impulse Accelerated Technologies

- · Resolved issues with "const" array declarations

- Updated Help file tutorials for updated Xilinx and Altera software

- Added log file output (CoDeveloper.log) for transcript messages

- Various optimizer and code generation improvements

## Version 1.22.c

- Released November 30, 2004

- Added MicroBlaze FSL uClinux Platform support and related example

- Added Mandelbrot examples

- Resolved issues with co\_bit\_\* functions

- Various optimizer and code generation improvements

### Version 1.22.b

- Released September 26, 2004

- Added support for memory type "asyncrom" for Xilinx targets (co\_array\_config)

- Added FFT and DCT examples

- Added "fast" (two clock cycle rate) 3DES example for Xilinx targets

### Version 1.22.a

- Released September 7, 2004

- Added support for shared OPB memory in Xilinx MicroBlaze FSL platform

- · Various optimizer and code generation improvements

## Version 1.21.e

- Released August 16, 2004

- Added support for Altera Nios II Platform Support Package

- · Resolved issue with Makefile.rules format

## Version 1.21.d

- Released July 30, 2004

- Resolves issues with Make and SHELL variable

- Improved transcript window. (Uncheck the "use external make window" option to use the internal transcript instead of using an external command window for Make processes.)

- Added support for Virtex II Pro (PowerPC) Platform Support Package

- Numerous RTL compiler and IDE bug fixes

# Version 1.21.b

- Released July 2, 2004

- Improved support for shared memories

- New example: MemoryIO (demonstrates use of shared memories on Xilinx platforms)

- Automatic Makefile generation

- Impulse\_unroll program renamed to impulse\_prep

- Numerous bug fixes

## Version 1.20.c

• Released April 22, 2004

- · Support for integer division added for hardware processes

- Support for co\_register and associated functions added

- Support for loop unrolling (UNROLL pragma) added

- Improved Support for shared memories

- New example: Fir51 (FIR filter with loop unrolling, demonstrates UNROLL pragma)

- New example: SimpleCounter (demonstrates use of streams and signals)

- New example: UpDownCounter (demonstrates use of co\_register for hardware process)

- Numerous bug fixes

# Version 1.10.j

- Released March 15, 2004

- Support for shared memories

- Improved documentation and examples for hardware interfaces (Universal Version)

- New hardware simulation tutorial (Universal Version)

- New examples (ImageFilter and ImageFilterDMA) for Altera

- Application Monitor peformance improvements

- Numerous bug fixes

# Version 1.10.g

- Released February 20, 2004

- New text editing component

- New licensing system

- First commercial version

# Version 1.10.c

- Released February January 5, 2004

- Release candidate 1 (final Beta)

# 1.1.3 License Agreement

# Impulse CoDeveloper™ End User License Agreement

LICENSE. Impulse CoDeveloper is provided under license from Impulse Accelerated Technologies, Inc. Impulse Accelerated Technologies hereby grants you, as a Customer and Licensee, a nonexclusive license to use the accompanying software programs on a single CPU at any given point in time. The Licensee is bound by the terms of the license purchased and may use the software accordingly. A "Node-locked" license must be used on the computer for which the license was granted. A "Floating" license may be used on any compatible computer in a computer network in a local area network (LAN) configuration. For the purpose of this agreement a LAN is designated as a set of computers interconnected to each other wherein the computer serving as the license server is NOT physically separated by the client computer running the software by more than one kilometer.

Product(s) provided under this agreement are copyrighted and licensed (not sold). Impulse Accelerated Technologies and its Licensors retain title to the software and any patents, copyrights, trade secrets,

and other intellectual property rights therein. Impulse Accelerated Technologies does not transfer title to the Products to Licensee.

TERM AND TERMINATION: This Agreement is effective from the date the software is received using any medium (downloaded from the internet/intranet, transferred via disks, etc.) until this Agreement is terminated. Any unauthorized reproduction or use of the Program and/or documentation will immediately terminate this Agreement without notice. Upon termination you are required to destroy/uninstall the installed software and documentation.

COPYRIGHT AND PROPRIETARY RIGHTS: Both United States Copyright Laws and International Treaty provisions protect the Program and documentation. This means that you must treat the documentation and Program just like a book, with the exception of making archival copies for the sole purpose of protecting your investment from loss. The Program may be used by any number of people, and may be moved from one computer to another, so long as there is No Possibility of its being used by two people at the same time.

RESTRICTIONS: The Software contains copyrighted material, trade secrets, and other proprietary information. You may not de-compile, reverse engineer, disassemble, or otherwise reduce the Software to a human-perceivable form. The Software may include software and/or hardware-based license management features. You may not reverse engineer the license management software. You may not modify the hardware or software configuration of your computer to create a false identity (host-id) for your computer. You may not modify or prepare derivative works of the Software in whole or in part.

DISCLAIMER AND LIMITATION OF LIABILITY: This software and documentation are licensed "AS-IS", without warranty as to performance. Impulse Accelerated Technologies EXPRESSLY disclaims ALL warranties, express or implied, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS OF THIS PROGRAM FOR A PARTICULAR PURPOSE. In no event shall Impulse Accelerated Technologies be held liable for any damages due to the use or inability to use of the software distrubution or parts thereof, even if Impulse Accelerated Technologies has been advised of the possibilities of such damages.

RESELLING: Only Impulse Accelerated Technologies authorized distributors may resell or distribute this product. Unauthorized resale of, or transfer of license to, the Software is specifically prohibited.

EXPORT RESTRICTION: You agree that you will not export or re-export the Software, reference images or accompanying documentation in any form without the appropriate government licenses.

© 2002 - 2015 Impulse Accelerated Technologies. All rights reserved.

# 1.1.4 About Impulse C

## About Impulse CoDeveloper

Impulse CeDeveloper<sup>™</sup> allows you to compile C-language directly into optimized logic ready for use with popular FPGA devices. Use the Impulse tools to quickly prototype mixed software/hardware systems and perform design iterations in just minutes or hours, instead of days or weeks.

Impulse CoDeveloper includes the Impulse C software-to-hardware compiler, interactive parallel

optimizer, and Platform Support Packages supporting a wide range of FPGA-based systems. Impulse tools are compatible with all popular FPGA platforms and tools.

Impulse CoDeveloper is for software application developers and FPGA designers seeking a faster path to FPGA hardware. CoDeveloper is ideally suited to image and video processing, digital signal processing, data compression/encryption, and hardware-accelerated computing. The Impulse C compiler is a high-level synthesis tool that is based on standard ANSI C. The Impulse tools enable highly iterative, software-oriented design methods and are compatible with a wide variety of FPGA-based platforms.

CoDeveloper allows you to use standard C tools and programming methods to accelerate your embedded, workstation and server applications.

- Partition your code between the processor and the FPGA accelerator.

- Use multiple parallel processes for increased performance.

- Verify and debug using familiar C-language development tools.

- Compile and optimize using interactive, graphical tools.

- Parallelize and pipeline your critical C code.

- Generate FPGA hardware ready for use with your selected FPGA-based platform.

- Generate host-FPGA interfaces for selected platforms.

Please note that Impulse C is not intended for directly converting large, monolithic C applications (typically consisting of many C subroutines called using a remote procedure call, or RPC, programming model) to hardware. The CoDeveloper tools include advanced C-to-hardware compilation capabilities, but these are intended to be used on a process-by-process basis. It is up to you, as the application developer, to make use of the CoDeveloper tools and Impulse C libraries to effectively develop applications appropriate for these new categories of programmable hardware platforms. In the tutorials included in this document (and in the Platform Support Package documents that are also included with CoDeveloper) we'll show you how.

## See Also

Impulse C User Guide The Programming Model <u>Product Overview</u> <u>CoDeveloper Eclipse IDE</u> CoBuilder User Guide

## 1.1.5 Contents

# CoDeveloper™ from Impulse Accelerated Technologies

# Version 3.70

Please review the Before You Begin section for important information.

Before You Begin (Read This First) Version History

<u>CoDeveloper Product Overview</u> <u>About Impulse C</u> Quick Start Tutorials <u>CoDeveloper Eclipse IDE</u> <u>CoBuilder User Guide</u> Impulse C User Guide Impulse C Function Reference <u>Platform Support Package Overview</u> <u>Registering Your Software</u> <u>License Agreement</u> Copyright Acknowledgements

All contents unless otherwise noted are Copyright © 2002-2015 Impulse Accelerated Technologies. All rights reserved.

# 1.2 CoDeveloper Application Manager

**CoDeveloper Application Manager IDE**

Simulation Features Screen Displays Design Management Features

1.2.1 Simulation Features

# Verify Designs with Three Levels of Simulation

The Impulse C development environment supports three levels of design simulation:

- Desktop software simulation

- Cycle-accurate hardware simulation

- HDL testbench generation

Each type of simulation can be run in a matter of seconds after making changes to your Impulse C code. These features give you the power to quickly track down defects, analyze performance, optimize

22

parallel hardware, and verify the output of the Impulse C compiler.

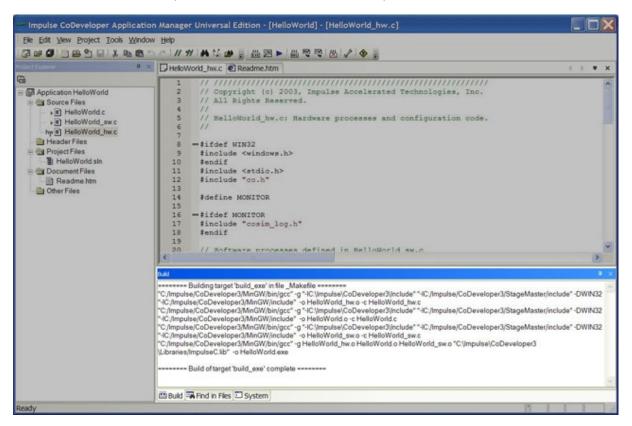

## **Desktop Simulation Using Standard Programming Environments**

Desktop, or "software", simulation involves running all the components of an Impulse C application on the desktop development PC. While an Impulse C application can include code whose final implementation is intended for both the FPGA fabric (in the form of hardware processes) and an embedded or host CPU (software processes), desktop simulation executes all of these components together as software running in the development PC's CPU. The advantages of software simulation are:

- Rapid prototyping: Change C code to change the design

- Fast simulation times: Run compiled C code natively on a desktop CPU

- Iterative development: Design changes are ready for testing at a software development pace-recompiling takes seconds

The CoDeveloper <u>Application Manager</u> and CoMonitor <u>Application Monitor</u>, when used in conjuction with a standard desktop compiler, form a complete system for the compilation, execution, and monitoring of Impulse C design descriptions. The system includes an Impulse C build facility (based on Make) and Impulse C instrumentation functions useful for simulating and debugging your Impulse C applications.

For desktop simulation, Impulse C applications are compiled into a native Windows executable that may be run directly or executed from within a debugger. While any C compiler and debugger can be used, CoDeveloper includes GNU gcc/gdb and also offers a Microsoft Visual Studio plugin. When launched, Impulse C executable files interact with the CoMonitor Application Monitor system to allow detailed investigation of your multi-process application. Impulse C instrumentation functions allow processes and streams to be monitored and log output to be written.

# **Cycle-Accurate Hardware Simulation**

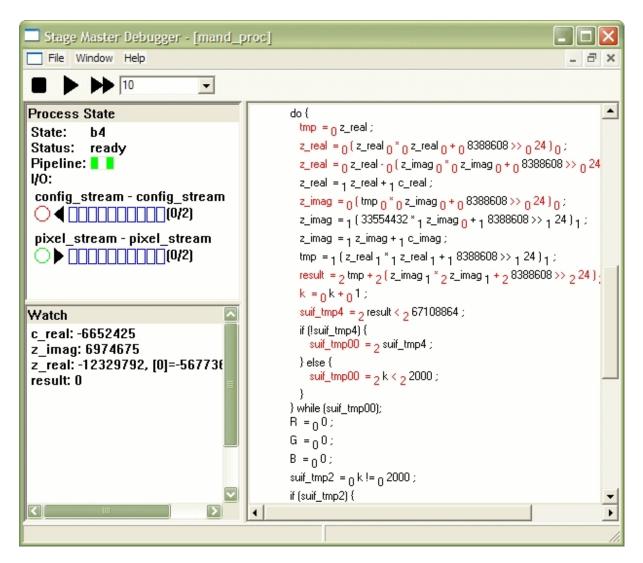

<u>Stage Master Debugger</u> simulates the Register Transfer Level (RTL) hardware generated by the Impulse C compiler alongside the software portions of the application. You can step through the hardware portions of your design clock cycle by clock cycle, as they would execute on the FPGA, using a simple graphical debugger. The original Impulse C source code is displayed, highlighting the statements that execute in parallel during simulation. Stage Master Debugger gives rapid feedback on how source code changes affect hardware performance, speeding the optimization process.

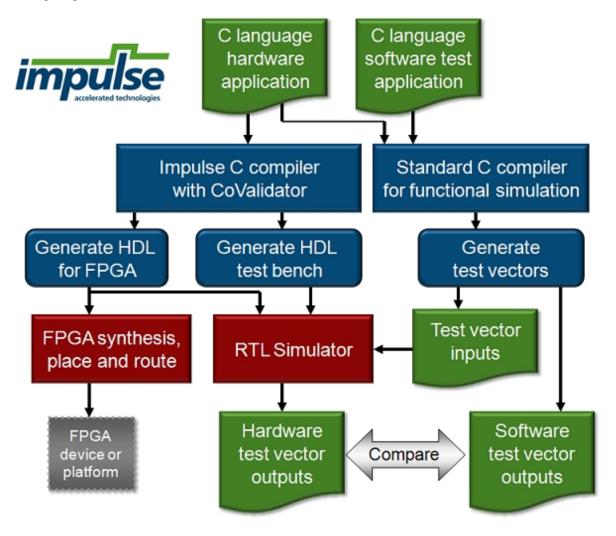

## Generate HDL Testbenches and Close the Loop

The <u>CoValidator Testbench Generator</u> integrates into the entire Impulse C design flow to build confidence in the result of C-to-FPGA compilation. During desktop simulation, CoValidator traces events on the I/O channels of your design and creates test vectors. When generating hardware, CoValidator creates a custom HDL testbench for your application that reads the same test vectors used in desktop simulation. Finally, CoValidator generates scripts for multiple HDL simulators, so you can simulate your project with a single command. The result: a ready-to-run environment for verifying the RTL output of the Impulse C compiler. The outputs of HDL simulation are written to test vector files that can be compared directly to the software simulation's output, thus "closing the loop".

## See Also

Simulating Impulse C Applications Application Monitor Build Software Simulation Executable Launch Software Simulation Executable Stage Master Debugger CoValidator Testbench Generator Simulation Options

### 1.2.1.1 Simulating Impulse C Applications

Simulation is an important element of the application development process. During simulation your goal will be to verify that your application and its component algorithms operate as expected, both in terms of algorithmic correctness and in terms of required performance.

Simulating for correct application behavior—behavioral simulation—is relatively easy once you have developed the necessary test stimulus and written a corresponding set of software tests for your application. Because Impulse C is compatible with standard C and C++ programming environments, you can use the full power of C programming to create complex, repeatable software test suites, and you can use standard C debugging tools to track down and fix errors in your application.

When simulating your application on your development machine ("desktop simulation", or "software simulation"), it is important to understand that the parallelism you express using Impulse C's stream, message, and process model are implemented by your desktop compiler using the threading model and associated libraries associated with your chosen environment. This means that the parallel behaviors you specify and the timing relationships between independently running processes may be very different from the behaviors and timing of your application when implemented on an actual programmable platform target.

Hardware simulation, using <u>Stage Master Debugger</u>, also executes on the desktop CPU. However, this time the hardware portions of your application run clock cycle by clock cycle as they would in the FPGA hardware. Software processes still execute as threads, at the whim of the operating system scheduler.

HDL simulation, where the hardware portions of your application are simulated as Register Transfer Level (RTL) logic in a third-party tool such as ModelSim, gives an even more accurate representation of how your Impulse C code will run on the FPGA. Performing HDL simulation requires a "testbench", an HDL program that stimulates the various hardware signals in your design to send and receive test data ("test vectors") between the simulator and your Impulse C hardware module. The CoValidator tool is capable of automatically generating testbenches for Impulse C applications, tracing the execution of desktop simulation to create test vectors used by the testbench.

## See Also

Simulation Features Simulation Options Software Simulation Executable

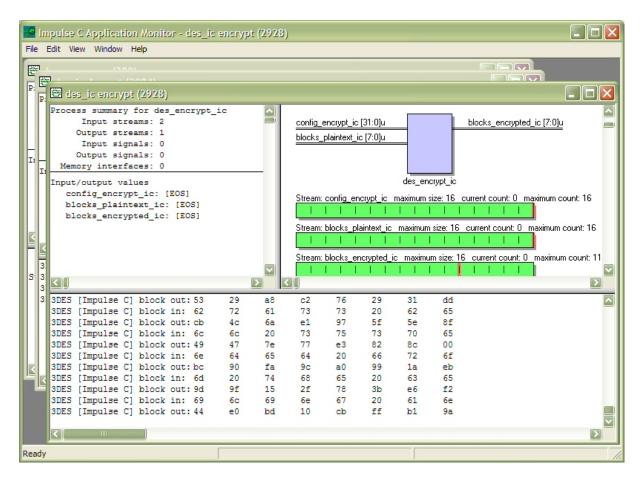

## 1.2.1.2 Application Monitor

## Description

The CoMonitor Application Monitor allows you to observe your application as it executes, capturing messages, stream data values and other information generated as a result of instrumenting your application. One or more Application Monitor log windows may be created by your application, with each window corresponding to a separate Impulse C hardware or software process.

# How You Use It

To make use of the Application Monitor, you must call the **cosim\_logwindow\_init** function in your Impulse C application's configuration function to set up the connection between your application and the Application Monitor.

To display an Application Monitor window for a process, call the **cosim\_logwindow\_create** function in that process.

The following functions may be used in your application to format and display text messages in a log window:

**cosim\_logwindow\_write(logwindow, str)** - This function writes an unformatted string value to the specified log window.

**cosim\_logwindow\_fwrite(logwindow, formatstring, arg1, arg2...)** - This function writes a formatted string value to the specified log window.

If your Impulse C application includes calls to these functions and you have invoked the Application Monitor prior to executing your simulation executable, then your simulation will communicate with the Application Monitor while it runs, displaying debugging messages and other information as appropriate.

Refer to the CoMonitor on-line help (Help > Help menu item) for additional details.

## See Also

**Build Software Simulation Executable**

Launch Software Simulation Executable Simulation Options cosim\_logwindow\_init cosim\_logwindow\_create cosim\_logwindow\_fwrite

### 1.2.1.3 Build Software Simulation Executable

### Description

This menu item builds a <u>Software Simulation Executable</u>. CoDeveloper runs the "make" program to invoke the C compiler and linker, generating a Windows-compatible executable.

## What You Do

To generate a simulation executable, do the following:

- (Optional) Select Project > Options from the menu bar to bring up the <u>Build Options</u> dialog. Alternatively, you can bring up the dialog by clicking on the Options toolbar button. Set "Desktop Simulation (.EXE) Build Options" as needed. Click on the Close button to close the dialog and save the options.

- 2. Select the Build Software Simulation Executable item from the Project menu, or click the Build Software Simulation Executable toolbar button.

## See Also

Build Options Software Simulation Executable

### 1.2.1.4 Launch Software Simulation Executable

### Description

This option launches the project's software simulation.

Simulation options available in the Simulate tab of the Options dialog box allow you to:

- 1. Specify whether the simulation executable should always be updated (rebuilt) prior to execution, and

- 2. Specify whether the <u>Application Monitor</u> should be started prior to your simulation executable being launched. The Application Monitor allows you to observe the behavior of your application through the use of process-specific monitoring windows.

# What You Do

To run the project's software simulation executable, do the following:

- 1. (Optional) Specify the name of your simulation executable, including path information as appropriate, in the Simulate Options dialog.

- Select the Project > Lauch Software Simulation Executable item from the menu bar or click on the Launch Software Simulation Executable toolbar button. The selected simulation executable is executed in a separate Windows Command Prompt window.

# See Also

Simulation Features Simulation Options Software Simulation Executable

## 1.2.1.5 Software Simulation Executable

### Description

A **Software Simulation Executable** is a native Windows executable file created as a result of compiling and linking your Impulse C application. Simulation executable files are intended for desktop simulation of your application, and may be run under the control of a standard C debugger. The <u>CoMonitor Application Monitor</u> may also be used as a debugging aid if appropriate instrumentation functions have been included in the application.

### See Also

Simulation Features Build Software Simulation Executable Launch Software Simulation Executable Simulation Options

#### 1.2.1.6 Simulation Options

### Description

The Options dialog contains a tab entitled "Simulation". The project options displayed here control desktop (software) simulation, hardware simulation using <u>Stage Master Debugger</u>, and HDL testbench generation using <u>CoValidator</u>.

|                                                        | Hardware Simulation (Stage Master Debugger)            |  |  |

|--------------------------------------------------------|--------------------------------------------------------|--|--|

| Launch Application Monitor                             | Update hardware simulation executable                  |  |  |

| Update software simulation executable                  | Hardware simulation executable name:<br>HelloWorld.exe |  |  |

| Software simulation executable name:<br>HelloWorld.exe |                                                        |  |  |

| Software simulation working directory:                 | HDL Simulation<br>Generate HDL testbench               |  |  |

|                                                        |                                                        |  |  |

|                                                        |                                                        |  |  |

|                                                        |                                                        |  |  |

|                                                        |                                                        |  |  |

|                                                        |                                                        |  |  |

# What You Do

To set Simulation options, select Project > Options from the menu bar to bring up the Options dialog. Alternatively, you can bring up the dialog by clicking on the Options toolbar button. Select the Simulation tab, then set options as needed. The various options are discussed below.

When you are finished setting options, click the OK button to close the dialog and update the current project options. Click the Apply button to update the options, but not close the dialog. Project settings are not saved to the project file (.icProj) until requested, for example using the File > Save Project menu item.

# **Software Simulation Options**

**Launch Application Monitor** - Choose this option to cause the CoMonitor Application Monitor to be launched prior to running the simulation executable.

**Update software simulation executable** - Choose this option to cause the software simulation executable to be built prior to launching.

Software simulation executable name - Use this field to specify the filesystem path to the software

simulation executable. You may enter either a path relative to the project's directory or an absolute path. When creating a new project, this field is automatically filled in with a name derived from the name of the project.

**Software simulation working directory** - Use this optional field to specify a working directory in which to launch a simulation executable. If blank, the current project directory is assumed to be the working directory.

**Software simulation command line arguments** - Use this optional field to specify any command line arguments to your simulation executable.

# Hardware Simulation (Stage Master Debugger) Options

**Update hardware simulation executable** - Choose this option to cause the hardware simulation executable to be built prior to launching.

**Hardware simulation executable name** - Use this field to specify the filesystem path to the hardware simulation executable. The path entered here is interpreted as a path relative to the Stage Master Debugger build directory. When creating a new project, this field is automatically filled in with a name derived from the name of the project.

## **HDL Simulation Options**

**Generate HDL testbench** - Choose this option to generate test vectors during software simulation, and to generate a ModelSim HDL testbench during HDL generation. See the section of this document entitled "<u>CoValidator Testbench Generator</u>" for more details.

### See Also

Simulation Features Software Simulation Executable Build Software Simulation Executable Stage Master Debugger CoValidator Testbench Generator

# 1.2.2 Screen Displays

The CoDeveloper Application Manager windows include:

Project Explorer Window Transcript Window Toolbar Buttons Impulse C Design Assistant Application Monitor

## See Also

**Design Management Features**

Simulation Features CoBuilder User Guide Impulse C User Guide

### 1.2.2.1 Menu Bar

## Description

The CoDeveloper main menu includes the following categories:

File Edit View Project Tools Window Help

## See Also

**Toolbar Buttons**

1.2.2.1.1 File Menu

## Description

The File menu options include:

New Project Open Project... Close Project Save Project As... New File... Open File... Add File... Close File Save File Save File As... Exit

# See Also

Edit Menu View Menu Window Menu Design Management Features

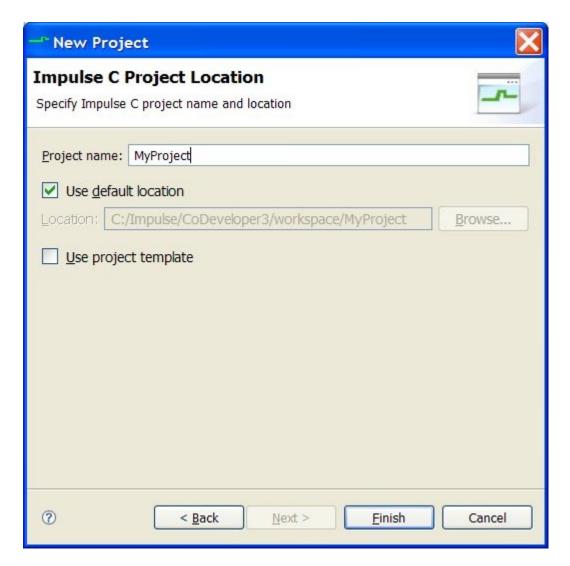

1.2.2.1.1.1 New Project

## Description

Creates a new blank or template project and closes the currently open project.

## What You Do

To open a new project, select the File / New Project option from the menu bar or click on the New Project toolbar button.

If the current project has changed since it was last saved, a dialog box will appear asking if you want to save the current project. Click:

Yes to save the current project and start a new project.

**No** to start a new project without saving the current project.

**Cancel** to cancel this command and return to the CoDeveloper.

The Create New Project dialog will appear. You can choose to create a blank project or one based on a template.

## **Creating a Blank Project**

By default, the Create New Project dialog will select the "Blank Project" template when it appears.

- 1. Fill in the "Project name" field.

- 2. In the "Location" field, enter the absolute path (including drive letter) to the directory where the project will be stored. This directory must already exist.

- 3. (Optional) If you select the "Create a folder for this project" option, the project will be stored in a new directory with the same name as the "Project name", located under the "Location". For example, in the screenshot below, a new project named "Northstar" will be created in the directory "C:\projects\Northstar".

- 4. Click OK.

- The Application Manager will now display your new blank project. You may now add new source files (<u>File / New File</u>) or existing source files (using the <u>Project Explorer window</u> or the <u>Build Options dialog</u>) to the project.

| Project types:             |                                    | Templates:                     | Preview:      |        |

|----------------------------|------------------------------------|--------------------------------|---------------|--------|

| Project Te                 | mplates<br>I Application Templates | Title<br>@Blank Project        |               |        |

| < This template            | represents a blank projec          | t with no source code and defa | ult settings. |        |

| Project name:              | Northstar                          |                                |               |        |

| Project name:<br>.ocation: | Northstar<br>C:\projects           |                                |               | Browse |

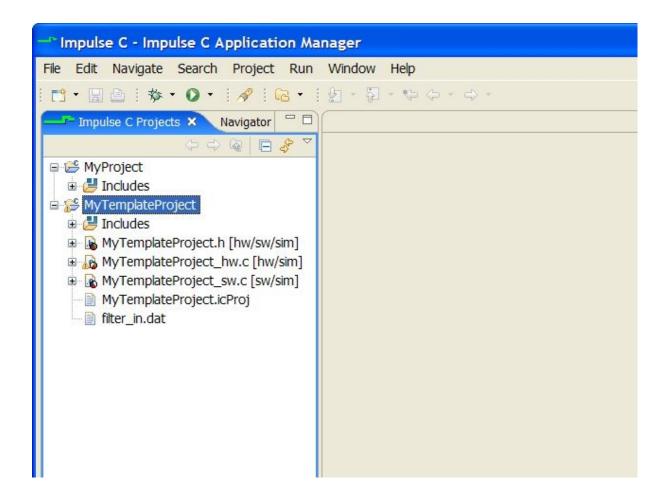

# Creating a Project from a Template

You can create a project that includes hardware and software source files implementing a complete Impulse C application by selecting one of the application templates in the Create New Project dialog. Such projects include all the necessary code for generating a simple FPGA design (processes, configuration function, main(), etc.). Several templates are available, representing a range of possible design choices.

| roject types: | 1 <b>-</b>                          | Templates:                                                                                                                                                                                                                                                                                                                         | Preview:  |        |

|---------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|

| Project Te    | mplates<br>al Application Templates | Title         Image: One input stream, two out         Image: Two input streams, two o         Image: Two input streams, one o         Image: One input stream, one me         Image: One memory, one output         Image: Three parallel processes         Image: Three pipelined processes         Image: One-process testbench | Producer/ | Filter |

|               | Northstar                           | Dne-process testbench (fl<br>t stream and one output stream. A s<br>er desktop simulation or execution on                                                                                                                                                                                                                          |           |        |

| ocation:      | C:\projects                         |                                                                                                                                                                                                                                                                                                                                    |           | Browse |

- 1. Select "General Application Templates" in the "Project types" window.

- 2. Select a template in the "Templates" window.

- 3. Fill in the "Project name" and "Location" fields as for a blank project, and optionally select the "Create a folder for the project" option.

- 4. Click OK.

- 5. The New Project Wizard will appear. Each template presents a different wizard, prompting you to fill in the template by providing names and other properties for processes and I/O channels (streams, signals, etc.). When you have made your selections, click Finish to close the wizard and generate the project.

- 6. The Application Manager will now display your new template project. You may now edit the source code, <u>build</u> and <u>run</u> desktop simulation, or <u>generate hardware</u> for your application.

### See Also

New File File / Add File...

1.2.2.1.1.2 Open Project...

## Description

Open a CoDeveloper Impulse C project. Project files have a .icProj file extension.

# What You Do

To open a project, select the File > Open Project... option from the menu bar or click on the Open Project toolbar button.

If a project is already open, a dialog box will then ask if you want to save the current project. Click on:

**Yes** to save the current project and open the project file dialog box. Then choose a project to open and click OK.

**No** to open the project file dialog box without saving the current project. Then, from the project file dialog box, choose a project to open and click OK.

**Cancel** to cancel this command and return to the current project.

## See Also

File / Close Project Project / Clean Project Project Files Window Open File...

1.2.2.1.1.3 Close Project

## Description

Closes the currently open project.

## What You Do

To close a project, select the File > Close option from the menu bar. The program will then ask if you want to save the current project.

Click on:

Yes to save the current project before closing it.

No to close the current project without saving it.

**Cancel** to cancel this command and return to the current project.

1.2.2.1.1.4 Save Project

## Description

Saves the current project (and any associated open files). Note that the project is saved to a .icProj file.

# What You Do

To save the current project, select the File -> Save Project option from the menu bar or click on the Save Project toolbar button. The program will then save the currently open project (and any associated open files) if the project is already named. If the project is not named, selecting this option brings up the <u>Save Project As ...</u> dialog box.

1.2.2.1.1.5 Save Project As...

## Description

Saves the current project to a new file name. Note that the project is saved to a .icProj file.

## What You Do

To save a project to a new or different file name, select the File > Save Project As... option from the menu bar. The program will then open a Save As ... dialog box. Enter a new name for the project and click OK.

1.2.2.1.1.6 New File...

### Description

Creates a new Impulse C source file. When you select this option, the Impulse C Design Assistant will appear and allow you to create a new Impulse C application source file--either an blank file or one generated from a template.

1.2.2.1.1.7 Open File ...

### Description

Opens an existing file in a text editor window.

### What You Do

To open a file in a text editor window, do one of the following:

**Menu / Toolbar Button Method** - Select the File > Open File... option in the menu bar or click on the Open File toolbar button. The Open dialog box will then appear. Select the file you wish to edit and click OK.

Double-click a Project File - Double-click on the filename in the Project Explorer window.

1.2.2.1.1.8 Add File...

## Description

Adds a selected project-related file (.c. .h or other file) to the current project. Selected files are added to sections of your project (such as Source Files or Project Files) depending on the file name extension. Once added to your project, files may be moved in the project tree as desired.

## What You Do

To add a module to your project, select the File -> Add File... option from the menu bar or click the Add File toolbar button. Select a file and click the Open button to exit the file selection dialog.

### Note

You can rearrange the display order of files in the Project Explorer window, or move files to specific sections of the window, by right-clicking a file and using the Move Up or Move Down options in the context menu that appears.

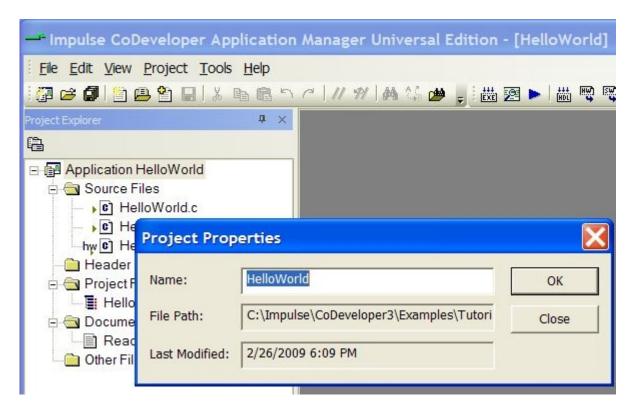

Also note that files are, by default, added to your project with relative path information. The absolute path to the file, as understood by an open project, is displayed by right-clicking the file and selecting Properties from the context menu that appears.

## See Also

### New File (Design Assistant)

1.2.2.1.1.9 Close File

## Description

Closes the currently active text editing window.

## What You Do

To close the currently active text editing window, select the File > Close File option from the menu bar. If the contents of the file have changed, you will be prompted to save the file.

1.2.2.1.1.10 Save File

## Description

Saves the contents of the currently active text editing window.

### Tip

Saving a file will not automatically add the file to your project. To add a file to the currently open project, use the File / Add File option from the menu bar.

## What You Do

To save the contents of the currently active text editing window, select the File > Save option from the menu bar.

1.2.2.1.1.11 Save File As...

## Description

Saves the contents of the currently active text editing window to a new or different file name.

## What You Do

To save a file to a new or different name, select the File > Save File As... option from the menu bar or use the shortcut keystroke. The program will then open a Save As ... dialog box. Enter a new name for the file and click OK.

1.2.2.1.1.12 Exit

## Description

Closes the program.

## What You Do

To exit the program, select the File > Exit option from the menu bar.

If the project has been modified, a dialog box will appear. Click on:

Yes save the current project and exit.

No to exit without saving.

Cancel to return to the program.

1.2.2.1.2 Edit Menu

# Description

The Edit menu items perform standard Windows editing functions. A brief summary of each is given below.

## Undo

This option undoes the most recent action in the text editing window. The shortcut key for this option is **Ctrl+Z**. This option can be used successively to undo up to 255 previous actions.

# Redo

This option redoes the most recent text editing action that was undone using the **Undo** option above.

# Cut

This option deletes a marked portion of text (block-marked using the mouse or the Shift and arrow keys) from a text editing window and copies it to the Clipboard. This action replaces the previous contents of the Clipboard. The shortcut key for this option is **Ctrl+X**.

# Сору

This option copies a marked portion of text (block-marked using the mouse or the Shift and arrow keys) from a text editing window to the Clipboard. This action replaces the previous contents of the Clipboard. The shortcut key for this option is **Ctrl+C**.

# Paste

This option copies the contents of the Clipboard into a text editing window at the location of the text cursor. The shortcut key for this option is **Ctrl+V**.

# Clear

This option deletes a marked portion of text (block-marked using the mouse or the Shift and arrow keys) from a text editing window. The shortcut key for this option is the **Delete** key.

# Select All

This option block-marks the entire contents of the currently active text editing window. The **Cut**, **Copy**, or **Clear** options can then be performed on the marked text. The shortcut key for this option is **Ctrl+A**.

# Find

This option opens the **Search** dialog box which allows you to perform a text search in the currently selected text editing window. Enter the word or words you wish to search for in the **Search for** field, and then select from the following options:

Match case - finds only words that match your query exactly as to upper and lower case.

**Match whole words only** - ignores partial words and finds only whole words that match your query (e.g., a whole-words-only search for **init** would skip **initialize**).

Regular expressions - searches the file using regular expressions.

Once you have selected the desired options, click on the **Next Match** or **Previous Match** buttons to begin the search, forward or backward in the file, respectively, from the cursor's location. To repeat a Search, select the **FindNext Match** or **Previous Match** buttons. To cancel the search, click the **Close** button.

# Replace

This option opens the **Search and replace** dialog box which allows you to perform a text search in the currently selected text editing window for a given text string and replace it with a second text string. To use the Replace feature, enter the word or words you wish to search for in the **Search for** field, enter the replacement word or words in the **Replace with** field, and then select from the following options:

Match case - finds only words that match your query exactly as to upper and lower case.

**Match whole words only** - ignores partial words and finds only whole words that match your query (e.g., a whole-words-only search for **init** would skip **initialize**).

**Regular expressions** - searches the file using regular expressions.

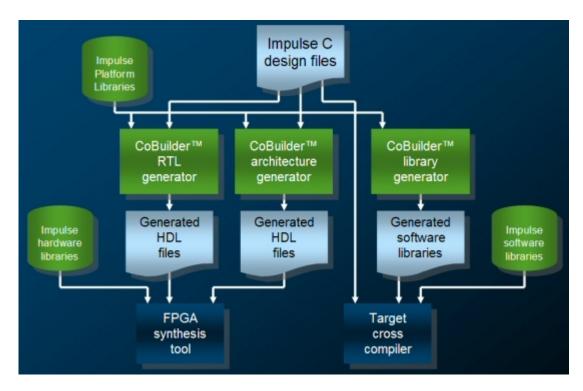

Replace in selection only - finds only strings within the selected text.