# Overview

The CoDeveloper environment for Impulse C supports a wide range of FPGA-based hardware/software platforms for embedded systems and high-performance computing. Each of these platforms is described by a Platform Support Package (PSP), which serves two purposes:

- 1. To specify platform capabilities so the Impulse tools can generate appropriate hardware descriptions and hardware/software interfaces

- 2. To extend the CoDeveloper environment to interact with third-party development tools

This document describes how to add support for a new platform to Impulse C using the PSP infrastructure.

| Date         | Revision                        |

|--------------|---------------------------------|

| August, 2011 | Added co_memory level 2 update  |

| July 6, 2007 | Fixed broken document reference |

| May 1, 2007  | Initial version                 |

# Revision History

# **FPGA Platforms**

Through Platform Support Packages, Impulse C allows the programmer to target a wide range of FPGA-based platforms. These platforms may include an embedded processor, an operating system, hardware and software libraries, and many different input/output interfaces, as well as the FPGA device itself. A platform may be associated with one particular hardware system, such as the XtremeData XD1000 high-performance computing platform, or may cover a broad family of development boards and devices, as with the "Xilinx Virtex-4 APU (VHDL)" Platform Support Package. System-level design tools, such as Nallatech's DIMEtalk software, can also be supported from Impulse C using Platform Support Packages, allowing Impulse C-generated hardware modules to be plugged in to a multi-component system.

The Impulse C compiler uses a PSP to generate files that map Impulse C code to the chosen platform. A PSP specifies how co\_stream, co\_memory, and other I/O channels are connected to the platform's hardware I/O devices. A co\_memory, for example, might be connected to an SDRAM controller core, or a co\_stream connected to a system bus.

Similarly, a PSP can specify how software drivers for those same interfaces are created by the Impulse C compiler. Other platform implementation details can be specified using a PSP, as well—from how C arrays are turned into HDL to what logic is used to implement floating-point operations.

# Platform Support Package Files

A Platform Support Package is a heterogeneous, hierarchical collection of files that describe a hardware/software platform to the Impulse C compiler tools. The structure of a PSP is defined using Extensible Markup Language (XML) files, according to formats and conventions specified by Impulse. Many other types of files can be contained in a PSP, including (but not limited to):

- Tcl scripts that generate HDL or C code

- HDL libraries

- Encrypted netlists describing IP cores

- C source files implementing software drivers

- Makefiles

# **XML File Structure**

The components of a platform and their relationships to one another are defined in XML files. The platform definition ("top-level") file refers to component definition files. For example, this XML element in a Xilinx MicroBlaze platform's definition file refers to an OPB bus component and names the location of the XML file defining that bus:

<bus name="opb0" file="VHDL/Xilinx/OPB/bus.xml"/>

Each major component of a platform has its own XML definition file, which details the features of that component.

| Filename       | Component                  | Description                                                                                                  |

|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------|

| bus.xml        | Bus (or other<br>I/O link) | Connects FPGA logic to external peripherals, off-<br>chip I/O, shared memories, and embedded or host<br>CPUs |

| cpu.xml        | CPU                        | External or embedded (hard- or soft-core) CPU                                                                |

| target.xml     | HDL                        | Hardware Description Language (Verilog or VHDL) targeted by Impulse C-to-HDL compiler                        |

| technology.xml | FPGA                       | FPGA device family or vendor                                                                                 |

| system.xml     | System                     | Characteristics of the entire system; a catch-all category                                                   |

Figure 1: PSP component files

# **Directory Structure**

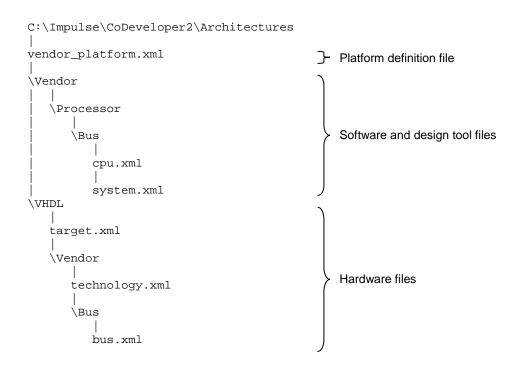

Files that describe the PSPs in the CoDeveloper environment are arranged in a hierarchical directory structure. The root of this directory tree is the "Architectures" subdirectory of the CoDeveloper installation (for example, "C:\Impulse\CoDeveloper2"). All platform definition files must be located directly under this root directory so CoDeveloper will find them.

#### Figure 2: PSP XML file organization

The branches of the tree are organized by convention, as follows:

- Hardware-related files, such as "bus.xml", "target.xml", or HDL libraries, are found under either the "VHDL" or "Verilog" subdirectories, according to the HDL they are written for.

- Software- or third-party-tool-related files, such as "cpu.xml" or "export.tcl", are organized directly under "Architectures".

- Files are stored in subdirectories by vendor name, then by more specific component names. For example, software driver files for the Altera Nios II embedded CPU are located in "Architectures/Altera/NiosII".

In general, we recommend that you follow the example of the existing PSPs in organizing files.

# Copy an Existing Platform

The best way to start creating a new Platform Support Package is to copy an existing one. Choose a PSP that is similar to yours and copy its platform definition file. Give the new file a unique name that includes the vendor and platform name, lowercase and separated by underscores by convention. For example, Cyberdyne Corporation's new SkyNet platform would be defined in the file "cyberdyne\_skynet.xml".

Once the new file is created, a new entry should appear in the drop-down list of PSPs in an Impulse C project's options dialog in CoDeveloper

C:\Impulse\CoDeveloper2\Architectures\xilinx\_generic.xml

Figure 3: Creating a new platform definition file

Edit the new top-level file and change the XML elements for components that are different in your platform. Depending on the platform, many elements will remain as-is, pointing to existing files. New components require specifying and creating new files.

When creating new component definition files, it may help to copy and rename a similar existing file. Once new component files are created, edit those files to define the characteristics of each component. Creating a new PSP is, in this way, a recursive process.

Where a platform does not include a component, such as a CPU, change the top-level file to refer to a "Generic" component definition file. For example, the "Lattice Generic (Verilog)" PSP does not have a CPU and is designed simply to generate standalone HDL modules appropriate to the Lattice FPGA technology, so the "system", "exporter", "bus", and "proc" XML elements and attributes all point to files in the "Generic" directories. These files, which ship with CoDeveloper, act as placeholders or provide minimal functionality.

Figure 4: Using "Generic" files as placeholders

The following sections of this document describe the platform definition file and the component definition files in more detail.

# Edit the Platform Definition File

The platform definition file (e.g., "xilinx\_v4\_apu.xml") defines a single "architecture" element containing several child elements that define components of the platform.

```

<?xml version='1.0'?>

<!DOCTYPE architecture PUBLIC "" "">

<architecture version="1.0" name="Xilinx Virtex-4 APU">

<bus name="apu0" file="VHDL/Xilinx/APU/bus.xml"/>

cproc name="cpu0" file="Xilinx/PPC/APU/cpu.xml" bus="apu0"/>

<pe name="PE0" target="VHDL/target.xml"</pre>

technology="VHDL/Xilinx/v4tech.xml"

system="VHDL/Generic/Generic/system.xml" bus="apu0"

cpu="cpu0"/>

<bus name="opb0" file="VHDL/Xilinx/OPB/bus.xml"/>

<mem name="ext0" bus="opb0" alloc="ext0_alloc"/>

<exporter file="Xilinx/EDK/export.tcl"/>

<library name="float" file="VHDL/Xilinx/float.xml"/>

<library name="float_fast" file="VHDL/Xilinx/float_fast.xml"/>

</architecture>

xilinx_v4_apu.xml

```

#### Figure 5: Example platform definition file

The XML elements that define the components are described below. Each element requires a "name" attribute (with the exception of "exporter"). Elements refer to one another by name to conceptually connect to one another. Each name must be unique to the PSP.

# **FPGA Elements**

The "pe" ("processing element") XML element describes a platform's FPGA.

Three attributes of the FPGA must be defined: "target", "technology", and "system". Two optional elements, "cpu" and "bus", may be defined to connect the FPGA to other components of the platform.

| Attribute  | Example File Path             | Description                   |

|------------|-------------------------------|-------------------------------|

| target     | VHDL/target.xml               | HDL targeted by the Impulse C |

|            |                               | compiler                      |

| technology | VHDL/Xilinx/technology.xml    | FPGA device family or vendor  |

| system     | VHDL/Xtreme/xd1000_system.xml | Other system components       |

#### Figure 6: "pe" element required attributes

The "target" attribute should always point to "VHDL/target.xml" or "Verilog/target.xml", depending on which HDL the Impulse C compiler should target when generating hardware for a user's application.

The "technology" attribute refers to the FPGA device family or vendor, and how certain aspects of Impulse C code are mapped to that specific FPGA technology. Few platforms—those based on an FPGA family that Impulse C does not already support—will require a new "technology". Point to a new "technology.xml" file if your platform will change:

- How C arrays are mapped to FPGA-local memories

- HDL library files that help implement Impulse C I/O channels (streams, registers, etc.) and some basic C operations (multipliers, etc.)

The details of the "target.xml" and "technology.xml" files are advanced topics beyond the scope of this document.

The "system" attribute refers to an XML file listing source or library files that should be included in every application targeting the platform. The "system.xml" file is a catch-all for files that aren't associated with another part of the system, such as a bus or CPU.

Associate the FPGA with a CPU or communication layer by setting the "cpu" and "bus" attributes to the names of "proc" and "bus" elements, respectively, in the PSP's top-level XML file.

# **Bus Elements**

The "bus" XML element refers to a bus or other communication logic used to move data between the FPGA and the rest of the system. The file ("bus.xml") this element refers to will define hardware libraries and a Tcl script that form the interface between Impulse C-generated I/O ports and the platform's communication logic.

Only the "name" and "file" attributes need be defined here. Change the "file" attribute to point to a new "bus.xml" file if the platform uses a new communication mechanism to or from the FPGA.

Example file path: "Verilog/Altera/Avalon/bus.xml"

# **CPU Elements**

Define a "proc" element if the platform supports an embedded or off-chip CPU, such as a PowerPC, Nios II, or Opteron, that will communicate with the FPGA. The "proc" element's file will describe the C source code and scripts that constitute the software driver for the Impulse C hardware.

The "file" attribute must point to the "cpu.xml" file that describes the CPU in detail. The "bus" attribute must refer to a "bus" element by name, and conceptually connects the CPU to that communication layer.

Since a software driver often depends on the choice of communication path to the FPGA ("bus"), the "cpu.xml" file is often organized under subdirectories first by the name of the CPU and then by the name of the bus.

Example file path: "Cray/Opteron/RT/cpu.xml"

#### **Memory Elements**

Define a "mem" element if the platform will support a memory device that is shared between the FPGA and the rest of the system, such as an SRAM or SDRAM.

The "mem" element differs from most of the other elements in the platform definition file in that it does not refer to an XML file. The "name" attribute is required, as is the "bus" attribute, which should be set to the name of a "bus" element defined elsewhere in the file.

The "alloc" attribute names the software memory allocation function for this memory. Software driver code generated by the Impulse C compiler will expect this function to be defined in source code provided by the PSP. See the section "Shared Memory Allocation" for details.

#### **Export Elements**

After generating HDL and driver code for an Impulse C application, CoDeveloper can export its output files for the next stages of development, which involve using hardware synthesis and software cross-compiler tools. This export process is controlled by a Tcl script that can be extended to do a variety of tasks, from simply copying the output files to another directory, to integrating with third-party tools such as Altera's SOPC Builder and Quartus II to assemble a complete system-on-a-chip and generate a bitfile for programming the FPGA.

If the new platform will change the export process, edit the "exporter" element to point to a new Tcl script.

Example file path: "Xilinx/EDK/export.tcl"

#### **Library Elements**

Platforms may specify any number of optional hardware libraries. These libraries define how C functions and operators are implemented in hardware by the Impulse C compiler. Floating-point operations or complex math functions, for example, can be specified in Impulse C hardware libraries.

For more information, see Impulse Application Note IATAPP108, "Using Hardware Libraries with Impulse C", available here:

http://impulsec.com/support\_appnotes.htm

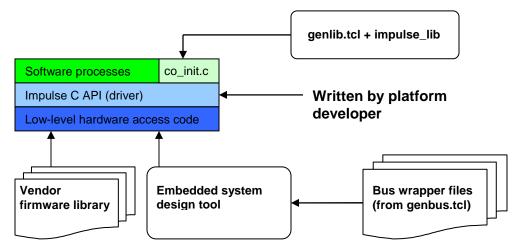

# Hardware/Software Interface

The most important purpose of a Platform Support Package is to define how the hardware/software interface is created. The hardware/software interface is the link between Impulse C-generated hardware in the FPGA and the rest of the system. PSPs define that link using Tcl scripts to create HDL (on the hardware side) and C source code (on the software side).

On the hardware side, compiler-generated HDL must be connected to physical hardware. Each co\_stream, co\_signal, co\_register, etc., that is connected between an Impulse C hardware process and a software process (or left open, using co\_port) will cause a set of ports to be generated by the compiler on the top-level HDL module. These ports must be connected to the actual hardware that will carry data between the FPGA and the rest of the system, whether that hardware is a system bus, a serial port, or any other I/O device.

On the software side, there are many ways to talk to the FPGA. Most commonly, the Impulse C hardware module's I/O interface registers are mapped into the memory address space of the platform's CPU. A software driver library is created that implements the Impulse C API functions (co\_stream\_read, co\_signal\_wait, etc.), reading and writing registers to exchange data and status information with the FPGA. Other implementations are possible; a co\_signal could be implemented using a CPU interrupt, for example.

The next sections describe how XML, Tcl, C, and HDL files used to implement both sides of the hardware/software interface

# Hardware Bus Wrappers: bus.xml and genbus.tcl

The "bus.xml" file controls how hardware is generated to connect Impulse C I/O channels (streams, etc.) to a particular hardware communication layer, such as a system bus. This file influences hardware generation in three ways:

- Defining bus characteristics used by the Impulse C compiler

- Listing HDL library files, netlists, or other files required to build bus-related hardware

- Naming a Tcl script called by the compiler to generate an HDL "bus wrapper" module

Figure 7: Example "bus" component definition file ("bus.xml")

The "bus.xml" file defines a single "bus" XML parent element with two attributes, "name" and "version". The "name" attribute will be used by the compiler to refer to buses of this type. (The "version" attribute is currently unused, but should be supplied.)

# **Bus Parameters**

The "param" XML child element is used to define characteristics of the bus that influence how the Impulse C compiler generates HDL for an application's I/O interfaces. Define each parameter by creating a "param" element with "name" and "value" attributes. Three parameters can be defined:

| Name     | Valid Values | Default | Description |

|----------|--------------|---------|-------------|

| steering | true, false  | None    |             |

| endianess [sic] | little, big    | None | Endianness expected of the data |

|-----------------|----------------|------|---------------------------------|

| size            | Any integer >0 | 32   | Number of data bits             |

#### Figure 8: Bus parameters

The Impulse C compiler generates HDL for I/O interfaces according to these parameters. For example, if a bus with a "size" of 32 is used by an application with 64-bit streams, the compiler will instantiate a resizing adapter component that will send each 64-bit stream packets using two 32-bit bus operations. A "size" parameter with the value "\*" will cause all Impulse C I/O interfaces to be generated with their requested data widths, as if the data bus were infinitely wide.

# Library Files

Files containing HDL or netlist components needed to build the bus interface hardware are listed using the "require" XML child element. Each "require" element must define the following attributes:

| Name | Valid Values                          | Description                                                        |  |

|------|---------------------------------------|--------------------------------------------------------------------|--|

| file | UNIX-style path                       | File path, relative to CoDeveloper's "Architectures"               |  |

|      |                                       | subdirectory                                                       |  |

| dst  | UNIX-style path                       | Directory path, relative to the "Hardware build directory",        |  |

|      |                                       | where the file should be copied during hardware generation         |  |

| type | "hdl"                                 | Type of file; must take value "hdl" (even for netlist files, etc.) |  |

|      | · · · · · · · · · · · · · · · · · · · |                                                                    |  |

Figure 9: "require" element attributes ("bus.xml")

When CoDeveloper generates hardware, each "required" file is copied from the "Architectures" tree to the Impulse C project's "Hardware build directory". Each listed file must therefore be distributed to end users with the PSP.

# Bus Wrapper Generator Script: genbus.tcl

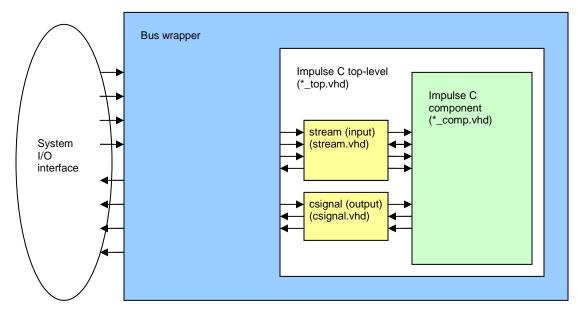

The bus wrapper is an HDL file that instantiates the top-level Impulse C module (in "\*\_top.vhd" or "\*\_top.v") and connects each Impulse C I/O interface to the system hardware that will carry the data. This wrapper component is generated by a Tcl script.

The Impulse C compiler will look for a "busgen" XML element in the "bus.xml" file. The "busgen" element must have one attribute, "file", whose value is the path to a Tcl script, the bus wrapper generator (named "genbus.tcl" by convention). The impulse\_arch compiler tool will invoke a callback function defined in the script to generate a bus wrapper for the top-level Impulse C HDL module.

The contents of the generated bus wrapper file are entirely up to the platform developer, who writes the "genbus.tcl" script. This script must define one Tcl callback procedure, "GenerateBUS", to which the compiler will pass data structures for all the Impulse C I/O interfaces between the application's hardware processes and the system. For complete details on the callback procedure's parameters, and Tcl procedures available to the programmer in the context of the script, see the "Impulse C HDL Interface Generation API" documentation, available for download on the Impulse Support Forum here:

http://www.impulse-support.com/forums/index.php?showtopic=342

The task of connecting Impulse C I/O interfaces to a system may be as simple as wiring ports to one another, or it may involve complex logic to arbitrate and multiplex data over a shared system bus. As before, we recommend copying an existing PSP's "genbus.tcl" script and using its code as a guide for developing a new bus interface generator.

# Impulse C Hardware I/O Interfaces

Each type of Impulse C I/O interface causes a different set of ports to be generated on the top-level module. These ports, and the behavior of the interfaces for input and output, are described here.

# **Input Streams**

Streams (co\_stream) serving as inputs to the Impulse C hardware have the following ports exposed on the top-level module:

| Name                            | Direction | Width (bits) | Description                                       |

|---------------------------------|-----------|--------------|---------------------------------------------------|

| <stream_name>_rdy</stream_name> | OUT       | 1            | Ready to accept data                              |

| <stream_name>_en</stream_name>  | IN        | 1            | Enable write                                      |

| <stream_name>_eos</stream_name> | IN        | 1            | Write operation indicates end-of-<br>stream (EOS) |

|                                 |           |              | Silealli (EUS)                                    |

| <stream_name>_data</stream_name> | IN | Bus size | Data to be pushed onto the input |

|----------------------------------|----|----------|----------------------------------|

|                                  |    |          | buffer                           |

#### Figure 11: Input stream ports

The width of the "\_data" signal will be determined by the "size" parameter in the "bus" element defined in "bus.xml". If an Impulse C application uses streams that are wider than the bus size, the Impulse C compiler will automatically instantiate "stream\_narrow" and "stream\_widen" components between the top-level ports and the hardware processes that allow large packets to be sent as a series of bus-size transactions. Smaller-than-bus-size packets, however, are not automatically packed into fewer, bussize transactions.

To write data to a stream, set the "\_en" signal high and present the input data on the "\_data" signal. When the "\_rdy" signal is high on a rising clock edge, the input buffer will register the data and the "\_en" input should be set low. The "\_eos" signal must be low while writing data.

To close an input stream, follow the same procedure for writing data, but set the "\_eos" signal high. Any data value written when the "\_eos" signal is raised will cause the stream to be closed.

| ▲ clk                                            | '0' | د و ک و ک و ک و الا و الا | الا و کر و ک |    |     |                 |

|--------------------------------------------------|-----|---------------------------|--------------|----|-----|-----------------|

| <pre><b>_</b>p_consumer_input_stream_rdy</pre>   | '0' |                           |              |    |     | و بنا الي ال    |

| <pre><b></b> p_consumer_input_stream_en</pre>    | '1' |                           |              |    | 1   | ک نہیں کا کے زی |

| <pre><b>\$</b> p_consumer_input_stream_eos</pre> | '0' |                           | 1            |    |     |                 |

| <pre><b></b> p_consumer_input_stream_idata</pre> | xx  | ( xx                      | ) 00 )       | 01 | XIX | 09              |

Figure 12: Writing and closing an input stream

# Output Streams

Streams (co\_stream) serving as outputs from the Impulse C hardware have the following ports exposed on the top-level module:

| Name                             | Direction | Width (bits)                        | Description                                         |

|----------------------------------|-----------|-------------------------------------|-----------------------------------------------------|

| <stream_name>_rdy</stream_name>  | OUT       | 1                                   | Data is ready to be read                            |

| <stream_name>_en</stream_name>   | IN        | 1                                   | Enable read                                         |

| <stream_name>_eos</stream_name>  | OUT       | 1                                   | Stream is closed; indicates end-of-<br>stream (EOS) |

| <stream_name>_data</stream_name> | OUT       | Bus size<br>(see "Input<br>Streams" | Data on the output buffer                           |

Figure 13: Output stream ports

To read data from a stream, wait for the "\_rdy" signal to go high, indicating data is ready on the "\_data" signal. If the "\_eos" signal is high, the stream has been closed and the data is not valid. Set "\_en" high to remove the data from the output buffer, wait for the next rising clock edge, and set "\_en" low again.

To close an output stream, flush the output buffer by performing read operations until the "\_eos" signal goes high. This assumes the writer eventually closes the stream—the flush operation will otherwise run forever.

| ▲ clk                                       | 'U' | و کو کی کی لاہ کا ہے کو کو کو کو کی ہے ا |  |

|---------------------------------------------|-----|------------------------------------------|--|

| p_producer_output_stream_rdy                | 'U' | الأوري كالأوري كأرته كالأوري كالأوري ال  |  |

| p_producer_output_stream_en                 | 'U' | 4                                        |  |

| p_producer_output_stream_eos                | 'U' |                                          |  |

| <pre>^ p_producer_output_stream_idata</pre> | хх  | (.)(00)( 01 )( 02 / 09 )                 |  |

Figure 14: Reading an output stream until close (EOS)

#### Input Signals

An input signal interface is generated when co\_signal\_wait is called on a co\_signal object in an Impulse C hardware process. The following set of ports is generated on the top-level HDL module:

| Name                             | Direction | Width (bits)        | Description     |

|----------------------------------|-----------|---------------------|-----------------|

| <signal_name>_en</signal_name>   | IN        | 1                   | Signal is valid |

| <signal_name>_data</signal_name> | IN        | Application-defined | Incoming data   |

Figure 15: Input signal ports

The width of a signal's "\_data" port is determined by the user application, in the call to co\_signal\_create or co\_signal\_create\_ex. A signal with a zero-bit datatype will be generated entirely without a "\_data" port.

The input signal protocol is simple: on a rising clock edge when "\_en" is high, the Impulse C hardware will register the data on the "\_data" port (and return from the co\_signal\_wait function).

#### **Output Signals**

An output signal interface is generated when co\_signal\_post is called on a co\_signal object in an Impulse C hardware process. The following set of ports is generated on the top-level HDL module:

| Name                             | Direction | Width (bits)                              | Description                 |

|----------------------------------|-----------|-------------------------------------------|-----------------------------|

| <signal_name>_en</signal_name>   | IN        | 1                                         | System is waiting on signal |

| <signal_name>_rdy</signal_name>  | OUT       | 1                                         | Output is valid             |

| <signal_name>_data</signal_name> | OUT       | Application-defined (see "Input Signals") | Output data                 |

#### Figure 16: Output signal ports

The system indicates it is waiting to receive a signal from the Impulse C hardware by setting the "\_en" port high. The hardware will respond by raising the "\_rdy" signal and presenting the data on the "\_data" port.

#### Input Registers

Registers (co\_register) serving as inputs to the Impulse C hardware have the following ports exposed in the top-level HDL module:

| Name                                 | Direction | Width (bits)        | Description    |

|--------------------------------------|-----------|---------------------|----------------|

| < <i>register_name</i> >_en          | IN        | 1                   | Input is valid |

| <register_name>_data</register_name> | IN        | Application-defined | Input data     |

Figure 17: Input register ports

These ports make up a simple write-only register interface with an enable ("\_en") signal. To write the register, raise the "\_en" signal and present the data on "\_data"; data will be registered on the rising clock edge.

# **Output Registers**

Registers (co\_register) serving as outputs from the Impulse C hardware have the following ports exposed in the top-level HDL module:

| Name                                  | Direction | Width (bits)        | Description |  |  |  |  |

|---------------------------------------|-----------|---------------------|-------------|--|--|--|--|

| <register_name>_value</register_name> | IN        | Application-defined | Output data |  |  |  |  |

|                                       |           |                     |             |  |  |  |  |

Figure 18: Output register ports

To read an output register, sample the "\_value" port on a rising clock edge.

# Impulse C Shared Memory Hardware Interface

The Impulse C co\_memory shared memory interface is designed to allow Direct Memory Access (DMA) from FPGA hardware to a specific memory device over a platformspecific system bus. A PSP must implement the bus controller logic necessary to translate the co\_memory requests coming from an Impulse C generated block into bus transactions for the system bus to be supported. If the platform uses a standard bus already implemented in for another platform then the bus controller can be reused. Implementations already exist for OPB, PLB, and Avalon.

As of CoDeveloper version 3, there is a new hardware interface with new features and new signals. The previous hardware interface is still supported via an adaptor component that is automatically instantiated when a shared memory based on the legacy interface is used. The legacy interface support is only available to support previous older shared memory implementations and **new shared memory implementations should not use the legacy interface**. The next section describes the new (level 2) hardware interface and the subsequent section describes the legacy (level 1) interface.

# Shared Memory Hardware Interface (Level 2)

Shared memory implementations must include the following element in the corresponding bus.xml file to indicate that it uses the level 2 interface: <pr

The level 2 shared memory implementations must support three types of requests: single-transaction load/store, contiguous block read/write, and multiple contiguous block read/write with stride (*slice*). Requests are initiated by Impulse C hardware in the top-level HDL file; the PSP is responsible for servicing these DMA requests with logic that connects to a system bus. Requests are transmitted to the PSP's bus wrapper via the following top-level HDL signals:

| Name                      | Direction | Width (bits) | Description                                   |

|---------------------------|-----------|--------------|-----------------------------------------------|

| <mem_loc>_idata</mem_loc> | IN        | Bus width    | Data read from memory                         |

| <mem_loc>_addr</mem_loc>  | IN        | 32           | Byte address of current word<br>(FPGA memory) |

| <mem_loc>_nextaddr</mem_loc> | IN  | 32                                   | Byte address of next word (FPGA memory)    |

|------------------------------|-----|--------------------------------------|--------------------------------------------|

| <mem_loc>_wri</mem_loc>      | IN  | 1                                    | Enable write to FPGA memory                |

| <mem_loc>_re</mem_loc>       | IN  | 1                                    | Enable read from FPGA memory               |

| <mem_loc>_odata</mem_loc>    | OUT | Bus width                            | Data to write to memory                    |

| <mem_loc>_ack</mem_loc>      | IN  | 1                                    | Indicates last word of request             |

| <mem_loc>_req</mem_loc>      | OUT | 1                                    | Indicates an active request                |

| <mem_loc>_block</mem_loc>    | OUT | 1                                    | When high, indicates block                 |

|                              |     |                                      | operation; low indicates load/store        |

| <mem_loc>_slice</mem_loc>    | OUT | 1                                    | When high, indicates a slice               |

|                              |     |                                      | operation.                                 |

| <mem_loc>_mode</mem_loc>     | OUT | 1                                    | When high, indicates write                 |

|                              |     |                                      | operation; low indicates read              |

| <mem_loc>_base</mem_loc>     | OUT | 32                                   | Base byte address into memory              |

| <mem_loc>_size</mem_loc>     | OUT | ciel(log <sub>2</sub> (bus width/8)) | Number of bytes per element                |

| <mem_loc>_chunk</mem_loc>    | OUT | 32                                   | Number of <i>elements</i> per block        |

|                              |     |                                      | (slice operations only)                    |

| <mem_loc>_stride</mem_loc>   | OUT | 32                                   | Number of <i>bytes</i> from the start of a |

|                              |     |                                      | block to the start of the next block       |

|                              |     |                                      | in system memory. (slice                   |

|                              |     |                                      | operations only)                           |

| <mem_loc>_start</mem_loc>    | OUT | 32                                   | Base byte address in FPGA                  |

|                              |     |                                      | memory                                     |

| <mem_loc>_count</mem_loc>    | OUT | 32                                   | Number of <i>elements</i> to transfer      |

#### Single transaction load/store

When <*mem\_loc>\_*block is low, a single element of <*mem\_loc>\_*size bytes is to be transferred between the system memory at address <*mem\_loc>\_*base and the FPGA. The FPGA address signals (<*mem\_loc>\_*start, <*mem\_loc>\_*addr, and <*mem\_loc>\_*nextaddr) are unused. The <*mem\_loc>\_*req signal is only active for one cycle to initiate the request. The <*mem\_loc>\_*ack signal should be asserted high when the transaction is complete and the controller will be ready to accept another request in the subsequent cycle.

For writes, the write data <mem\_loc>\_odata is valid in the cycle that <mem\_loc>\_req is asserted and remains valid until the <mem\_loc>\_ack signals is received. For reads, the <mem\_loc>\_wri signal should be asserted high during the cycle that <mem\_loc>\_idata becomes valid.

# Contiguous block read/write

When <*mem\_loc*>\_block is high and <*mem\_loc*>\_slice is low, a single contiguous block of <*mem\_loc*>\_count elements of <*mem\_loc*>\_size bytes are to be transferred between the system memory starting at address <*mem\_loc*>\_base and the FPGA memory starting at address <*mem\_loc*>\_start.

Data must be transferred to/from the FPGA memory in order. The signals <*mem\_loc*>\_wri and <*mem\_loc*>\_re must be asserted for exactly one cycle per element.

### Multiple block read/write (slice)

When <*mem\_loc>*\_block is high and <*mem\_loc>*\_slice is slice, <*mem\_loc>*\_count/<*mem\_loc>*\_chunk contiguous blocks of <*mem\_loc>*\_chunk elements of <*mem\_loc>*\_size bytes are to be transferred between the system memory starting at address <*mem\_loc>*\_base and the FPGA memory starting at address <*mem\_loc>*\_start. The starting address of block N+1 in system memory is equal to the starting address of block N + <*mem\_loc>*\_stride. The blocks in FPGA memory are contiguous. Thus, a read request gathers data blocks from system memory into a contiguous block in the FPGA memory, and a write request scatters data from a contiguous block of memory into blocks of system memory.

Data must be transferred to/from the FPGA memory in order. The signals <*mem\_loc>\_*wri and <*mem\_loc>\_*re must be asserted for exactly one cycle per element.

# Upgrading from legacy interface

The level 2 interface introduces the new <mem\_loc>\_re, <mem\_loc>\_slice, <mem\_loc>\_chunk, <mem\_loc>\_stride, and <mem\_loc>\_start signals. Additionally, the existing signals <mem\_loc>\_addr and <mem\_loc>\_nextaddr have been redefined to be the *byte* address of the current element being transferred to/from the FPGA memory.

# Legacy Shared Memory Hardware Interface

Read and write access is supported using contiguous block transfers or load/store (single-word) operations. Requests are initiated by Impulse C hardware in the top-level HDL file; the bus wrapper is responsible for servicing DMA requests with logic that connects to a system bus master or memory controller.

| Name                         | Direction | Width (bits)                   | Description                         |

|------------------------------|-----------|--------------------------------|-------------------------------------|

| config_en                    | IN        | 1                              | Base address input stream, enable   |

|                              |           |                                | write                               |

| config_eos                   | IN        | 1                              | Base address input stream, end-of-  |

|                              |           |                                | stream                              |

| config_data                  | IN        | 32                             | Base address input stream, base     |

|                              |           |                                | address value                       |

| config_rdy                   | OUT       | 1                              | Base address input stream, ready    |

|                              |           |                                | for write                           |

| <mem_loc>_idata</mem_loc>    | IN        | Bus width                      | Data read from memory               |

| <mem_loc>_addr</mem_loc>     | IN        | 32                             | Address of current word in on-chip  |

|                              |           |                                | buffer                              |

| <mem_loc>_nextaddr</mem_loc> | IN        | 32                             | Address of next word in on-chip     |

|                              |           |                                | buffer                              |

| <mem_loc>_wri</mem_loc>      | IN        | 1                              | Enable write to local input buffer  |

| <mem_loc>_odata</mem_loc>    | OUT       | Bus width                      | Data to write to memory             |

| <mem_loc>_ack</mem_loc>      | IN        | 1                              | Indicates last word of request      |

| <mem_loc>_req</mem_loc>      | OUT       | 1                              | Indicates an active request         |

| <mem_loc>_block</mem_loc>    | OUT       | 1                              | When high, indicates block          |

|                              |           |                                | operation; low indicates load/store |

| <mem_loc>_mode</mem_loc>     | OUT       | 1                              | When high, indicates write          |

|                              |           |                                | operation; low indicates read       |

| <mem_loc>_base</mem_loc>     | OUT       | 32                             | Base byte address into memory       |

| <mem_loc>_size</mem_loc>     | OUT       | log <sub>2</sub> (bus width in | Number of bytes per request word    |

|                                        |     | bytes), round up to nearest integer |                                |  |  |  |

|----------------------------------------|-----|-------------------------------------|--------------------------------|--|--|--|

| <mem_loc>_count</mem_loc>              | OUT | 32                                  | Number of words in the request |  |  |  |

| Figure 40. Ob and many interface marts |     |                                     |                                |  |  |  |

Figure 19: Shared memory interface ports

One set of interface ports will be generated on the top-level HDL module for each memory location used by an application's hardware processes. Memory locations are specified by the PSP's platform definition file; the "name" attribute of each "mem" element is a memory location that may be passed to the co\_memory\_create function. Many co\_memory objects can use to the same memory location by passing the same string in co\_memory\_create's "loc" parameter.

```

Architectures/altera_nios2.xml

```

```

void config(void * arg) {

co_memory memA, memB, memCoeff;

co_process sw0, hw0, hw1;

memA = co_memory_create("A", "heap0", 4096);

memB = co_memory_create("B", "heap0", 4096);

memCoeff = co_memory_create("coeff", "ext0", 256);

sw0 = co_process_create("sw", sw_function, 3, memA, memB, memCoeff);

hw0 = co_process_create("hw0", hw_function, 2, memA, memCoeff);

hw0 = co_process_create("hw1", hw_function, 2, memB, memCoeff);

//...

}

UserApp_hw.c

```

#### Figure 20: Memory locations

To share access to the single interface among multiple hardware processes, the Impulse C compiler will generate logic in the top-level HDL file that arbitrates between the processes using a compile-time priority mechanism. The hardware process created first in the Impulse C configuration function (by calling co\_process\_create) will receive first priority, followed by the other hardware processes in the order they were created. The arbitration logic ensures that DMA operations are atomic, but the user's application is responsible for synchronizing read/write access to the shared memory by the various Impulse C processes. (This synchronization can be accomplished using co\_signal, for example.)

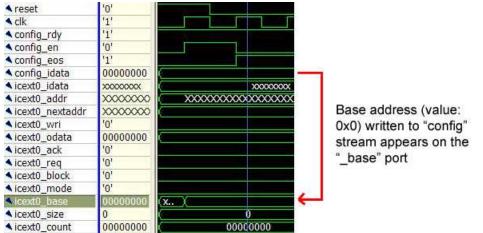

# **Base Address Configuration**

The base address of each memory location must be configured when the Impulse C hardware is initialized, before any of the application logic will begin executing. An input stream interface will be automatically generated in the top-level HDL file for any application that uses co\_memory in its hardware processes. This stream, named

"config", is used to write the base address for each memory location to an internal register.

To configure the base addresses, perform stream write operations as described in the section "Input Streams". One data packet must be written for each memory location, in the order in which co\_memory objects using the locations were created in the Impulse C application's configuration function. The "config" stream should be closed after the last base address is written.

Figure 21: Shared memory base address configuration

In a platform with a CPU, generated C code will be responsible for stimulating the "config" stream to write the base addresses. For more details on configuring shared memory base addresses from software, see the section "Shared Memory Initialization".

If a platform does not have a CPU, logic must be generated in the bus wrapper file that stimulates the "config" stream to write base addresses.

# **On-chip Buffers**

All Impulse C shared memory operations use on-chip memory resources to buffer input/output data. Each on-chip memory corresponds to a C array in application code and is implemented in hardware according to the PSP. Tcl scripts referred to by "ramgen" elements in the "technology.xml" file are responsible for generating HDL code to instantiate on-chip memory resources.

# **Block Read Requests**

A block read will be requested by the Impulse C hardware for each co\_memory\_readblock function call in a hardware process. The block read operation transfers a number of words from the shared memory to an on-chip buffer. After a request is initiated, one word can be transferred from the bus interface per clock cycle.

At the start of a block read request, the Impulse C hardware will raise the "\_req" and "\_block" signals. The "\_mode" signal will be low, to indicate a read operation. The "\_size" signal will contain the word size of the request (in bytes) and the "\_count" signal will indicate the number of these words in the request. The "\_base" signal will contain the byte offset from the shared memory's base address; the data sent in response should be read starting from this address.

Once the system is ready to respond to the request, it should place the input data on the "\_idata" port and raise the "\_wri" signal to indicate that the data should be written to the on-chip buffer on the rising clock edge. The word address in the buffer where the data will be written must be placed on the "\_addr" signal; for block read requests, this address always starts at zero and increments by one per clock cycle.

When "\_count" number of words have been read, raise the "\_ack" signal until the next rising clock edge (keeping the "\_wri" signal high) to indicate the request has been fulfilled. The Impulse C hardware will then set the "\_req" signal low and, "\_wri" and "\_ack" should be set low; the request is complete.

| '0'       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| '0'       | کاری کاری کار                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     | ر کاری کاری                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| '1'       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| '0'       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| '1'       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 00000000  |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| X0000000X | x0000000x )                                                                                           | 000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10001)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00020002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (00030003)                                                                                                                                                                                                                                                                                                                                                                          | 00040004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 00000000  | ********                                                                                              | . 0 )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ) 3 )(                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 00000000  |                                                                                                       | XXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                        | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |