# TECHNOLOGY THAT MOVES YOU

# **ISI-75**

# **Full Speed USB 1.1 Transceiver Core**

### Overview

The ISI-75 is a USB 1.1 Transceiver Hard core IP designed to help USB designers implement their chip designs by integrating this core together with a USB Controller and their application specific logic and software in an SOC design.

# ISI-75 Functional Blocks and Bus States

The ISI-75 design can be mapped into different process technologies. The design has been verified in many processes. It has been in high volume production since 1999. It is capable of transmitting and receiving at full and low speeds.

The signaling states are: J-state, K-state and Single Ended Zero state (SEO). The J-state is the idle state and differentiates full from low speed. The K-state identifies the start of a packet (SOP) and it signals auto resume from power suspend. The SEO state signals the End Of Packet (EOP), rest and a disconnected line. The signaling levels are summarized in table 7.1, section 7.1.4, chapter 7 of the USB Specification version 1.0.

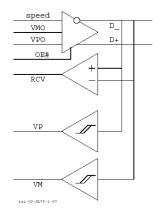

#### Port I/O Function

- •D+, D- (I/O) Differential Data Bus and connect to the USB cable

- •RCV (Output) Received Data and connect to the USB Controller

- •VP, VM (Output) These outputs are used to detect single ended zero, speed and error conditions and connect to the USB Controller.

- •OE# (Input) Output Enable. Active low. Enables the transceiver to transmit data on the bus. When not active, the transceiver is in the receive mode.

- Speed (Input) Slew rate control. When equal to one slew rate adjusted for high speed, when zero adjusted for low speed.

VMO VPO (Input) Input to the differential driver from the USB

## **Functional Diagram**

Controller.

#### PRODUCT BRIEF

## **Key Features**

- Digital CMOS Process Technology.

- It has been in high volume production in several processes ranging from .6u down to .13u

- Supports 12Mbits/s

"full speed" and

1.5Mbits/s "low

speed" operation.

- Interfaces directly to the 'Serial Interface Engine' provided by the USB implementer's forum.

- Design can be mapped into different process technologies.

- It is capable of transmitting and receiving at full and low speeds.