# **inter<sub>sil</sub>**

## PCB Design and Assembly Recommendations for Intersil HDA Module Technology

## Introduction

Intersil's module product family offers a unique packaging concept, the High Density Array (HDA) package. HDA encompasses lead pitches of 1.0mm and above. This package offers a variety of benefits including reduced lead inductance and both perimeter I/O pins (to ease PCB trace routing) and in-board I/O pins (for complex pinouts). Also, the exposed Au plated copper ePad technology offers good thermal and electrical performance. These features make the HDA packaged POL module an ideal choice for many new applications where thermal and electrical performance are important.

This tech brief provides general guidelines for use in developing land pattern layouts and solder mounting processes. It should be emphasized that these guidelines are general in nature and should only be considered a starting point in this effort. The user must apply their actual experiences and development efforts to optimize designs and processes for their manufacturing practices and the needs of varying end-use applications.

## **Package Construction**

#### High Density Array (HDA) Module Packing Highlights

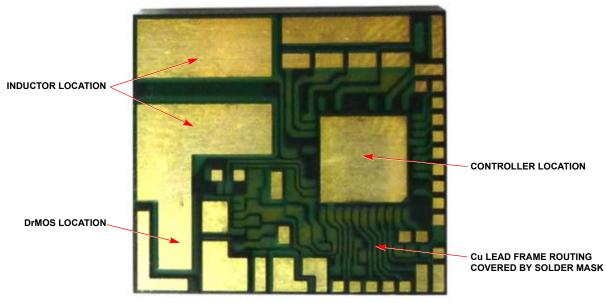

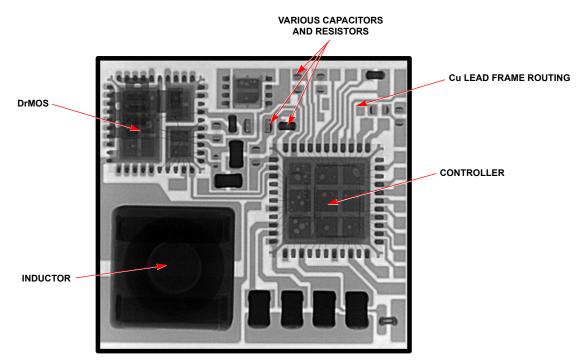

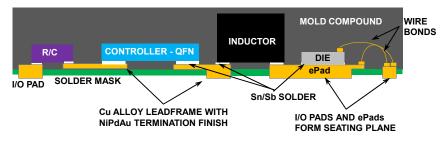

- HDA based on copper (Cu) lead frame technology

- Cu lead frame provides one routing layer

- Jumper wires and traces under components provide crossovers

- HDA provides superior thermal performance

- Power dissipating components are mounted directly to Cu lead frame for improved thermal performance.

- HDA is flexible

- Intersil offers a comprehensive family of HDA modules with thicknesses of 2.5mm, 3.7mm, and 7.5mm maximum (with 5.3mm maximum arriving soon)

- The HDA lead frame can be quickly modified to produce new products

- HDA provides high SMT yields

- NiPdAu lead finish provides excellent solderability

- I/O terminals and ePads form a seating plane below solder mask for easier SMT solder mounting

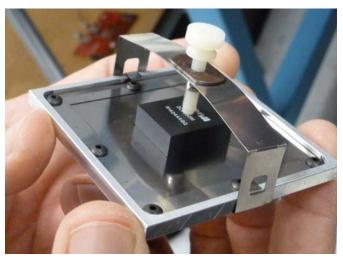

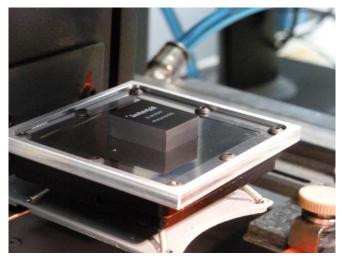

FIGURE 1. TYPICAL HDA MODULE PHOTOS

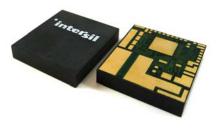

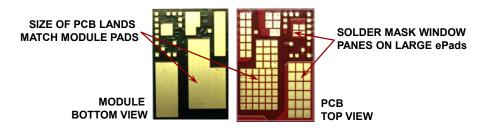

FIGURE 2. TYPICAL HDA BOTTOM VIEW - ISL8270M

NOTE: All pads are non-solder mask defined and extend above the SM surface. The pad finish is NiPdAu for good solderability. The Au finish is 0.6µin thick to prevent gold embrittlement of the solder joint.

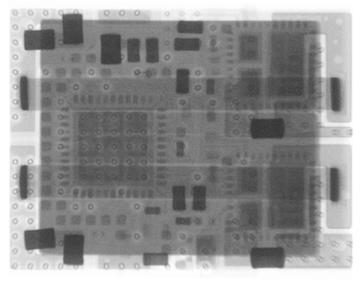

FIGURE 3. TYPICAL HDA MODULE X-RAY - ISL8270M

FIGURE 4. TYPICAL HDA MODULE CROSS-SECTION

## **Moisture Sensitivity**

## Moisture Sensitivity Handling, Packing, and Use

#### **MOISTURE SENSITIVITY**

Intersil HDA modules are moisture-sensitive devices. All Intersil HDA modules meet Moisture Sensitivity Level (MSL) 3 per J-STD-020.

Pb-free reflow is qualified per J-STD-020. Peak temperatures vary based on module thickness and volume, and are specified on the MSL label and at <u>www.intersil.com</u>.

#### PACKING AND LABELING

Intersil packs and labels HDA modules per J-STD-033. Standard packing is in JEDEC trays. Add a "-T" to the part number for tape and reel packing. For more information on tape and reel specifications for integrated circuits, see tech brief <u>TB347</u>.

#### HANDLING AND USE

Customers should handle and use HDA modules per J-STD-033. The modules are MSL 3 qualified – do not exceed 168-hour floor life. If floor life is exceeded, bake at +125°C for 48 hours.

## Reliability

## Standard HDA Module Development Flow and Qualification

Prior to the package and/or product builds for qualification (design phase), discrete component reliability reports are reviewed and approved. The Intersil Corporate Process Reliability group tests and/or approves process technology wear-out data (i.e., TDDB, Hot Carrier, HTRB, EM, etc.) to ensure the process technology for embedded controllers, power FETs, power stage, etc., meet the Intersil wear-out goals.

The package engineering group executes "look-ahead" evaluations to ensure the package is robust and meets design goals. Once the design phase is complete, the HDA power module and package moves into the Product/Package Reliability qualification phase.

#### **Typical Reliability Qualification Stress Tests**

- MSL Test Determines Moisture Sensitivity Level per J-STD-020.

- Precondition Stress Samples for BHAST, UHAST, THB, and TMCL are preconditioned. Stress includes moisture soak per MSL and three-time reflow cycles at the Pb-free peak reflow temperature, per J-STD-020.

- BHAST or THB Static bias in a moisture-rich environment. Stress targets possible electrolytic related failure mechanisms. Typical stress runs for 96 hours or 1000 hours, respectively.

- High Temperature Operating Life (HTOL) Dynamic operation, maximum operating voltage per datasheet. This stress test is used to verify the long term reliability of the module. Data is used to calculate FIT rate and MTTF. Typical stress runs for 1000 hours with module temperature set at +125°C.

- Temperature Cycling (TMCL) This stress test targets flaws in the thermo-mechanical properties of the module design or BOM. Typical stress includes 500 cycles at -65°C/+150°C or 1000 cycles at -40°C/+125°C.

- High Temperature Storage Life (HTSL) This stress test is used as an indicator of thermally activated failure mechanisms. Typical stress runs for 1000 hours at 150°C.

- Unbiased HAST (UHAST) This stress test accelerates the penetration of moisture through a protective mold compound and is used to identify failure mechanisms internal to the package, such as galvanic corrosion. Typical stress runs for 96 hours at +130°C/85% RH, 2ATM pressure.

- Reliability reports available on <u>www.intersil.com/support</u>

#### Intersil HDA Power Module – Board Level Reliability

Intersil verifies the BLR of HDA modules by:

- Mounting functional modules or daisy chain modules on PCBs

- Using SAC 305 or SnPb solder

- Performing temperature cycles of -40°C to +125°C, 12-minute dwell (typical)

- Running 2000 cycles (typical)

- Conducting down point and end point electrical tests to confirm module functionality or no resistance change

- Testing end point cross section to confirm no solder joint damage

A summary of BLR data is available at <u>www.intersil.com</u>. Detailed reports are also available. Contact Intersil Sales to request a detailed BLR report.

## **PCB Design Guidelines**

#### HDA – PCB Design Guidelines

- The Intersil HDA package outline drawing in the product datasheet includes a PCB footprint and solder stencil

- PCB lands in the form of SMD pads are preferred to improve gasketing

- PCB lands should match the HDA pads one-to-one

- Large ePads should be "windowpaned" with SM

- The SM webs provide gasketing to improve solder release during printing, control solder spread/thickness, and provide venting for out-gassing during reflow

- See the Package Outline Drawing (POD) for specific design recommendations

- Solder stencil apertures should be slightly smaller than the solder mask openings, 30µm typical.

- Via in pad should be filled and plated over (VIPPO) to prevent solder wicking into the vias.

- Electroless Nickel Immersion Gold (ENIG) PCB finish recommended

### **PCB Assembly Process**

#### **HDA – PCB Assembly Process**

- Profile with a thermal couple placed under the HDA module

- Follow solder paste supplier's reflow profile, but do not exceed HDA module's qualified peak reflow temp. Pb-free reflow is qualified per J-STD-020:

- Peak temperature varies based on module thickness and volume

- Peak temperature specified on MSL label or www.intersil.com

- Do not exceed 168-hour out of bag limit (MSL 3 qualified)

- If time limit exceeded bake per MSL label instructions

- Solder foil preforms may be used on large ePads to reduce solder voids and flux residue and to increase stand-off height

- Use the following assembly tooling materials for the SMT process:

- Electroless Nickel Immersion Gold PCB finish (ENIG)

- Stainless steel, laser cut stencils with Nano-coating

- 4 mil or 5 mil stencil thickness

- No clean, low void, Type 3 or 4 solder paste per ANSI/J-STD-005

- Follow paste suppliers recommendation for air or nitrogen purge during reflow

- Solder Print Inspection (SPI) is recommended to ensure consistent solder deposit area, height, and volume

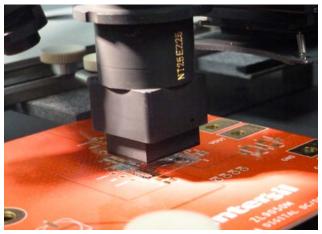

FIGURE 5. TYPICAL HDA MODULE PHOTOS

#### ISL8272M/ISL8273M Validated SMT Process Summary

#### TABLE 1. SCREEN PRINT

|                   | MACHINE         | MATERIALS         |                               |  |

|-------------------|-----------------|-------------------|-------------------------------|--|

| Screen Printer    | DEK Horizon 02i | Solder Paste      | Alpha CVP-390 SAC 305         |  |

| Pressure          | 8Kg             | Thawing Time      | 4 hrs                         |  |

| Speed             | 15mm/sec        | Auto Mix Time     | 3 min                         |  |

| Single/Dual Print | Single          | TOOLING           |                               |  |

| Separate Speed    | 0.3mm/sec       | Stencil Thickness | 5 mils                        |  |

| Separate Distance | 2mm             | Stencil Opening   | Per POD                       |  |

| Printing Gap      | 0mm             | Stencil Made      | Laser cut + electro polishing |  |

#### TABLE 2. COMPONENT PLACEMENT

|                 | MACHINE       | MATERIALS  |                        |  |

|-----------------|---------------|------------|------------------------|--|

| Chip Shooter    | Yamaha YG100G | Components | Intersil 8272M Modules |  |

| Pick-up Speed   | 30%           | Packing    | JEDEC Tray             |  |

| Place Speed     | 30%           | Pre-Bake   | NO                     |  |

| Transport Speed | 50%           | TOOLING    |                        |  |

| Place Height    | 0.2mm         | Feeder     | Tray Loader            |  |

| Vacuum Level    | 30%           | Nozzle     | 214                    |  |

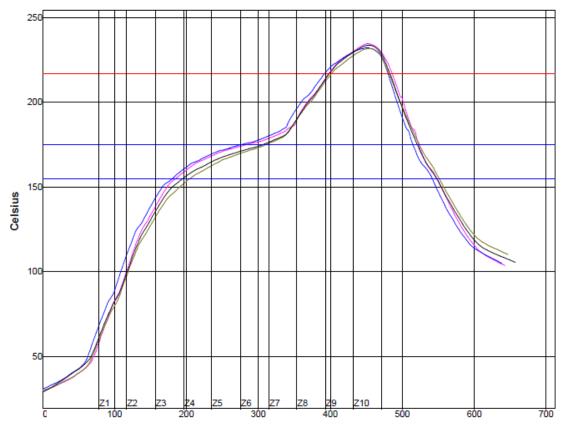

Seconds

| PWI= 163% | Max Risi | ng Slope    | Max Falli | ing Slope   | Soak Time | 155-175C     | Reflow Ti | ime /217C   | Peak   | Temp          |

|-----------|----------|-------------|-----------|-------------|-----------|--------------|-----------|-------------|--------|---------------|

| TC1       | 1.19     | <b>63</b> % | -1.18     | 93%         | 97.81     | 89%          | 88.11     | <b>87</b> % | 234.62 | -108%         |

| TC2       | 1.19     | <b>65</b> % | -1.27     | <b>89</b> % | 95.20     | <b>76</b> %  | 88.14     | 88%         | 232.21 | <b>-156</b> % |

| TC3       | 1.11     | 36%         | -1.02     | <b>99</b> % | 105.38    | <b>127</b> % | 79.90     | 33%         | 231.83 | <b>-163</b> % |

| TC4       | 1.13     | 42%         | -1.14     | 95%         | 111.46    | 157%         | 84.41     | <b>63</b> % | 233.73 | -125%         |

| Delta     | 0.08     |             | 0.25      |             | 16.26     |              | 8.24      |             | 2.79   |               |

| STATISTIC NAME                                                       | LOW LIMIT | HIGH LIMIT | UNITS          |

|----------------------------------------------------------------------|-----------|------------|----------------|

| Max Rising Slope (Target = 1.0)<br>(calculate slope over 30 seconds) | 0.7       | 1.3        | Degrees/Second |

| Max Falling Slope<br>(calculate slope over 30 seconds)               | -6.0      | -1.0       | Degrees/Second |

| Soak Time +155°C to +175°C                                           | 60        | 100        | Seconds        |

| Time Above Reflow -217 °C                                            | 60        | 90         | Seconds        |

| Peak Temperature                                                     | 235       | 245        | °C             |

#### ISL8272M, ISL8273M Validated SMT Process

FIGURE 6. ISL8272M, ISL8273M SAMPLE X-RAY

#### **PCBA Solder Joint Voiding Recommendations**

- There are no IPC standards for solder joint voids for bottom-terminated components

- Intersil recommends 25% maximum solder void for small I/O pads and 50% maximum solder void for large epads

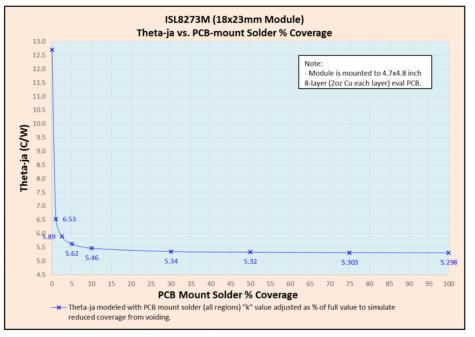

- Solder voids have minimal impact on thermal performance as shown in Figure 7

FIGURE 7.  $\theta_{\text{JA}}$  vs PCB-MOUNT SOLDER % COVERAGE

## **PCBA Rework**

For rework of defects underneath the package, the whole package needs to be removed.

Removal and rework of HDAs should be done on a rework station with thermal profile control (see <u>Figure 8</u>). The following steps are provided as a guideline – a starting point in developing a successful rework process.

FIGURE 8. REWORK STATION WITH THERMAL PROFILE CONTROL

#### Bake

Before rework, bake the PCB assembly at +125°C for at least 48 hours to remove any residual moisture.

#### **Component Removal**

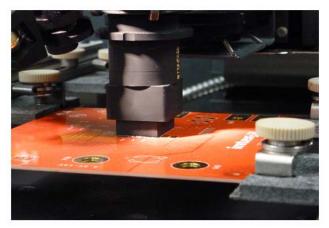

Ideally, the reflow profile for part removal should be similar to that of the component attachment. However, the time above liquidus can be reduced as long as the reflow is complete. Typical rework stations will heat the board from the bottom side using convective heaters and from the top side with a hot gas nozzle directing heat at the component to be removed (see Figure 9). An appropriate thermal profile must be developed to preheat, soak, and reflow the module on the PCB.

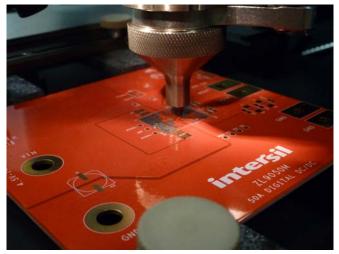

FIGURE 9. TOP AND BOTTOM PREHEAT

#### **Component Removal -- Reflow**

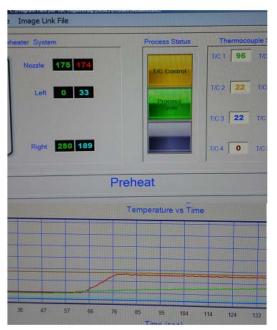

The circuit-board component being removed should reach at least  $+55^{\circ}C \pm 5^{\circ}C$  using a temperature ramp of  $+1^{\circ}C$  to  $+3^{\circ}C/min$  before ramping to reflow temperature (see Figure 10).

FIGURE 10. PREHEAT CONTROL

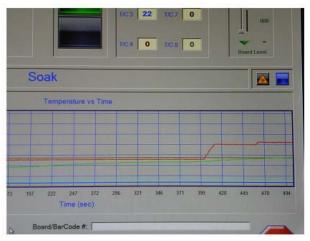

FIGURE 11. REFLOW TEMPERATURE CONTROL

Peak temperature is dependent on the solder composition. Minimize heating of adjacent components by using the lowest peak temperature needed to reflow the solder joints.

Once the joints have reflowed, the HDA is removed with a vacuum pick-up (see Figure 12).

FIGURE 12. COMPONENT REMOVED WITH VACUUM PICK-UP

#### **Site Redress**

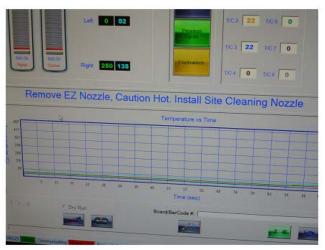

Clean the site properly, removing residual solder with an appropriate vacuum nozzle. Use the site redress program provided by the rework station (see <u>Figures 13</u> and <u>14</u>).

FIGURE 13. SITE REDRESS

FIGURE 14. REDRESS PROGRAM

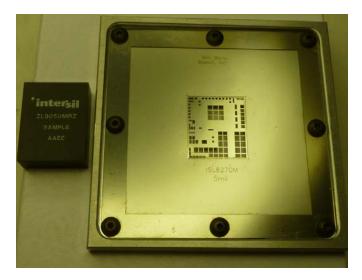

#### **Solder Paste Printing**

Use a miniature stencil specific to the HDA component (see Figure 15). Align and attach the stencil to the component using a stereo microscope (see Figure 16). Deposit a small amount of paste on the stencil and use a small squeegee blade to print the paste onto the component (see Figure 17).

FIGURE 15. MINIATURE STENCIL

FIGURE 16. ALIGN STENCIL ONTO REPLACEMENT MODULE

#### **Technical Brief 498**

FIGURE 17. DEPOSIT PASTE WITH SMALL SQUEEGEE BLADE

#### **Component Alignment and Placement**

Carefully place the HDA module in the pick-up position (see Figure 18).

FIGURE 18. PLACEMENT OF NEW DEVICE

Use the rework station's optical system overlay and align the images of the HDA terminals with the printed solder and PCB land pattern (see Figure 19).

FIGURE 19. OVERLAY IMAGE ALIGNMENT

#### **Component Reflow**

Reflow the component using the same reflow profile as originally developed for the PCBA based on the solder paste used (see Figure 20). The rework is completed (see Figure 21).

FIGURE 20. COMPONENT PLACEMENT

FIGURE 21. COMPLETED REWORK

### **Questions and Answers**

- What is HDA?

- High Density Array (HDA) is a unique, Intersil developed, module packaging technology based on a routable, copper (Cu) lead frame construction, which provides superior thermal performance compared to laminate substrate based modules.

- Can HDA modules be reworked?

- Yes, a rework station used for BGA rework is recommended. See <u>"PCBA Rework" on page 8</u>.

- Can HDA modules be mounted on the bottom side of the PCBA?

- HDAs with a maximum thickness of 2.5mm and 3.7mm may be mounted on the PCBA bottom side. HDAs with 5.3mm and 7.5mm maximum thickness are not recommended for bottom side mounting.

- · What is the maximum amount of solder voiding allowed?

- See discussion in <u>"PCBA Solder Joint Voiding</u> Recommendations" on page 7.

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com