# Implementation on Fast Fourier Transforms on Motorola's Digital Signal Processors

# Implementation of Fast Fourier Transforms on Motorola's Digital Signal Processors

by Guy R. L. Sohie and Wei Chen Digital Signal Processing Division

#### **Preface**

The human body has inherently slow perception mechanisms. For instance, when listening to music, or speech; we do not hear individual pressure variations of the sound as they occur so quickly in time. Instead, we hear a changing pitch, or frequency. Similarly, our eyes do not "see" individual oscillations of electromagnetic fields (light); rather, we see colors. In fact, we do not directly perceive any fluctuations (or oscillations) which change faster than approximately 20 times per second. Any faster changes manifest themselves in terms of the frequency or rate of change, rather than the change itself. Thus, the concept of frequency is as important and fundamental as the concept of time.

MOTOROLA APR4

| SECTION 1  Definition and  History | 1.1<br>1.2 | Introduction to the Fourier Integral Use of the Fourier Transform                  | 1-1<br>1-3 |

|------------------------------------|------------|------------------------------------------------------------------------------------|------------|

| SECTION 2 The Discrete             | 2.1        | The Discrete-Time Fourier Transform (DTFT)                                         | 2-1        |

| Fourier<br>Transform               | 2.2        | Windowing and Windowing Effects Sampling the Frequency Function                    | 2-4<br>2-7 |

| SECTION 3                          | 3.1        | Motivation                                                                         | 3-1        |

| The Fast                           | 3.2        | Divide and Conquer                                                                 | 3-2        |

| Fourier<br>Transform               | 3.3        | The Decimation-in-Time and Decimation-in-Frequency Radix-2 Fast Fourier Transforms | 3-3        |

|                                    | 3.4        | The Decimation-in-Frequency Radix-2 Fast Fourier Transforms                        | 3-9        |

| SECTION 4 Complex FFT              | 4.1        | Required Hardware Support for FFT Calculation                                      | 4-1        |

| on the                             | 4.2        | Radix-2 DIT and DIF Butterflies                                                    | 4-4        |

| Motorola DSP                       | 4.3        | Complexity of a Radix-2 DIT FFT                                                    | 4-6        |

| Family                             | 4.4        | Implementation on Motorola's DSP56001                                              | 4-6        |

|                                    |            | 4.4.1 DSP56001 Architecture                                                        | 4-6        |

|                                    |            | 4.4.2 DIT Butterfly Kernel on DSP56001                                             | 4-9        |

MOTOROLA iii

| 4.5  | Imple  | mentation on Motorola's DSP96002                       | 4-13 |

|------|--------|--------------------------------------------------------|------|

|      | 4.5.1  | DSP96002 Architecture                                  | 4-13 |

|      | 4.5.2  | DIT Butterfly Kernel on DSP96002                       | 4-15 |

| 4.6  | Imple  | mentation on Motorola's DSP56156                       | 4-17 |

|      | 4.6.1  | DSP56156 Architecture                                  | 4-17 |

|      | 4.6.2  | DIT Butterfly Kernel on DSP56156                       | 4-19 |

| 4.7  |        | ng for Fixed-Point Processors<br>56001/2 and DSP56156) | 4-19 |

|      | 4.7.1  | Scaling at the Input –<br>Guard Bits                   | 4-20 |

|      | 4.7.2  | Scaling During the Passes –<br>Auto-Scaling and        |      |

|      |        | Block Floating-Point                                   | 4-21 |

| 4.8  |        | lle Factors and On-Chip ROM                            | 4-23 |

|      | 4.8.1  | Twiddle Factors for DIT                                | 4-23 |

|      | 4.8.2  | Sine Table on the DSP56001/2                           | 4-23 |

|      | 4.8.3  | Sine and Cosine Tables on the DSP96002                 | 4-24 |

| 4.9  | Bit-Re | eversed Addressing                                     | 4-25 |

| 4.10 |        | mentation of a Radix-4 DIT FFT                         | 4.00 |

|      |        |                                                        | 4-26 |

|      |        | Radix-4 DIT Butterfly Core                             | 4-27 |

|      |        | Radix-4 DIF Butterfly Core                             | 4-31 |

| 4.11 | Invers | se FFT                                                 | 4-32 |

iv MOTOROLA

| SECTION 5              | 5.1 | Optimization                                                        | 5-1      |

|------------------------|-----|---------------------------------------------------------------------|----------|

| Optimizing             |     | 5.1.1 Minimum Memory Requirement — In-Place Calculation             | -<br>5-3 |

| Performance of the FFT |     | 5.1.2 Optimization for Faster Execution                             | 5-5      |

| of the FFT             | 5.2 | Example of Optimization                                             | 5-9      |

|                        | 0.2 | 5.2.1 Fully Optimized Complex FFT                                   | 00       |

|                        |     | for the DSP56001/2                                                  | 5-9      |

|                        |     | 5.2.2 Fully Optimized Complex FFT                                   |          |

|                        |     | for the DSP96002                                                    | 5-12     |

| SECTION 6              | 6.1 | Real-Valued Input FFT Algorithm 1                                   | 6-2      |

| Real-Valued            | 0.1 | 6.1.1 Bergland Algorithm                                            | 6-2      |

| Input FFT              |     | 6.1.2 Reordering                                                    | 6-6      |

| Algorithm              |     | 6.1.3 Performance Estimation                                        | 6-7      |

| Algoritiiii            | 6.2 | Real-Valued Input FFT Algorithm 2                                   | 6-9      |

|                        | 0.2 | 6.2.1 Separating Two Real FFT                                       | 0 0      |

|                        |     | from One Complex FFT                                                | 6-9      |

|                        |     | 6.2.2 Rebuilding the DFT of a Real                                  |          |

|                        |     | Sequence from Two DFTs                                              | 6-11     |

|                        |     | 6.2.3 Performance Estimation                                        | 6-13     |

|                        | 6.3 | Real-Valued Input FFT Algorithm 3                                   | 6-15     |

|                        | 6.4 | The Goertzel Algorithm                                              | 6-18     |

|                        | 6.5 | Real-Time Data Acquisition on                                       |          |

|                        |     | Motorola DSPs                                                       | 6-20     |

|                        |     | 6.5.1 Fast Interrupt on DSP56001 for Real-Time FFT Data Acquisition | 6-21     |

|                        |     | 6.5.2 Real-Time Data Acquisition                                    | J _ 1    |

|                        |     | on DSP96002                                                         | 6-23     |

MOTOROLA

| SECTION 7 Two Dimensional Fourier and Cosine Transforms | 7.1<br>7.2 | Two Dimensional FFTs on the DSP96002 Discrete Cosine Transform on the DSP96002 7.2.1 One Dimensional Discrete Cosine Transform (DCT) 7.2.2 Two Dimensional DCT                                                                                                                               | 7-1<br>7-2<br>7-2<br>7-5                             |

|---------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| SECTION 8 Competitive Analysis of FFT Performances      | 8.1<br>8.2 | Most Popular Digital Signal Processors Performance of FFTs on Digital Signal Processors  8.2.1 FFTs on Floating-Point DSPs 8.2.1.1 Complex FFT on Floating-Point DSPs 8.2.1.2 Real FFT on Floating-Point DSPs 8.2.2 FFT on Fixed-Point DSPs 8.2.2.1 Complex Input FFT 8.2.2.2 Real Input FFT | 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7 |

| SECTION 9 Conclusion                                    |            |                                                                                                                                                                                                                                                                                              | 9-1                                                  |

| APPENDIX A Fully Optimized Complex FFT                  | A.1        | Optimized Complex FFT for the DSP96002                                                                                                                                                                                                                                                       | A-1                                                  |

vi MOTOROLA

| APPENDIX B  | B.1 | Faster real FFT for the DSP96002 | B-1 |

|-------------|-----|----------------------------------|-----|

| Real-Valued | B.2 | Real FFT for DSP56001/2          | B-5 |

| Input FFT   |     |                                  |     |

MOTOROLA vii

## Illustrations

| Figure 2-1  | Fourier transform of a rectangular function                    |     |  |

|-------------|----------------------------------------------------------------|-----|--|

| Figure 2-2  | Windowing effects when windowing a single sine wave            | 2-6 |  |

| Figure 3-1  | The FFT principle in layman's terms                            | 3-2 |  |

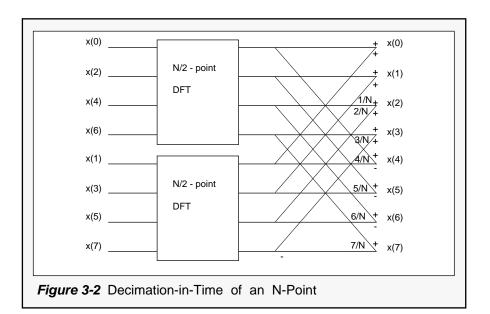

| Figure 3-2  | Decimation-in-Time of an N-Point FFT                           | 3-4 |  |

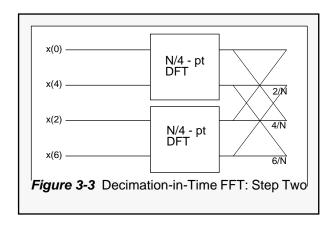

| Figure 3-3  | Decimation-in-Time FFT: step two                               | 3-4 |  |

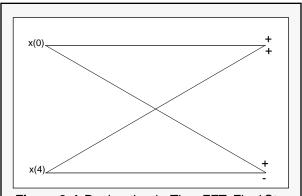

| Figure 3-4  | Decimation-in-Time FFT: final step (2-Point DFT)               | 3-5 |  |

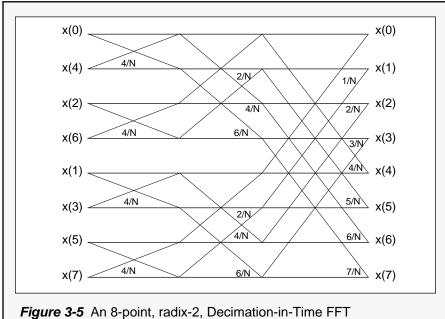

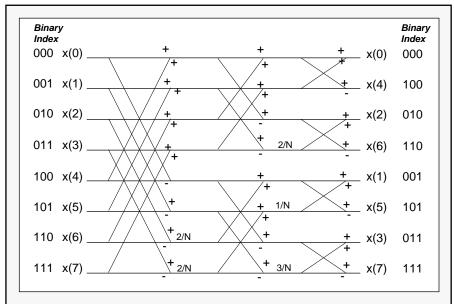

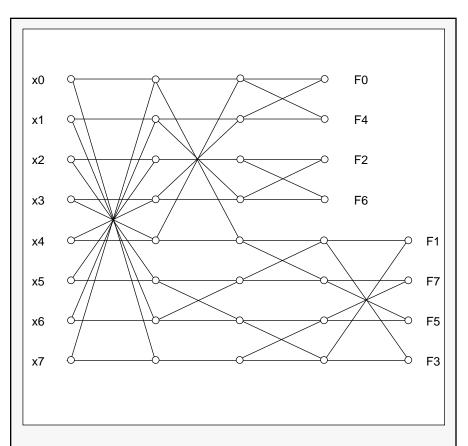

| Figure 3-5  | An 8-point, radix-2, Decimation-in-Time FFT                    | 3-5 |  |

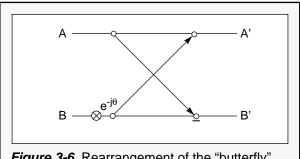

| Figure 3-6  | Rearrangement of the "Butterfly" building block of the DIT FFT | 3-6 |  |

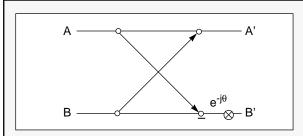

| Figure 3-7  | Rearrangement of the "Butterfly" building block of the DIF FFT | 3-6 |  |

| Figure 3-8  | Rearrangement of the DIT computation of Figure 3-6             | 3-7 |  |

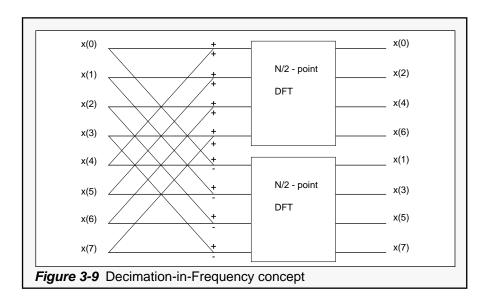

| Figure 3-9  | Decimation-in-Frequency concept                                | 3-8 |  |

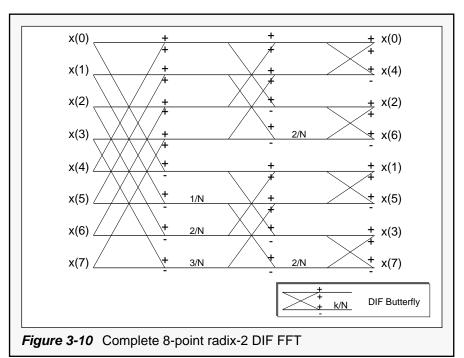

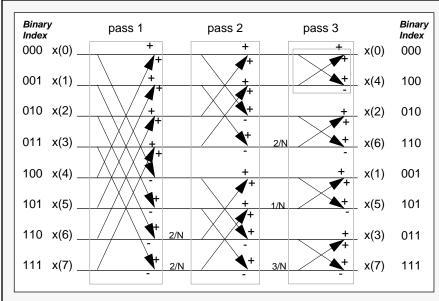

| Figure 3-10 | Complete 8-Point Radix-2 DIF FFT                               | 3-8 |  |

| Figure 4-1  | Grouping of butterflies in the FFT calculation                 | 4-5 |  |

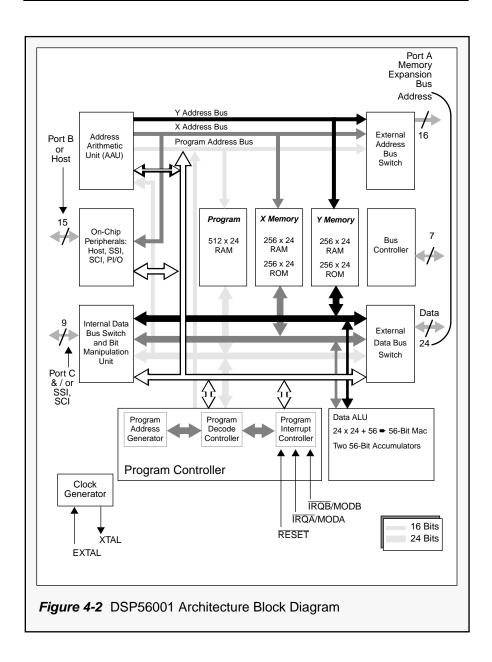

| Figure 4-2  | DSP56001 architecture block diagram                            | 4-7 |  |

MOTOROLA ix

## Illustrations

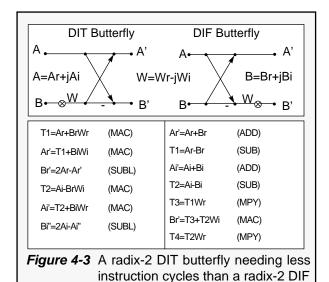

| Figure 4-3  | A radix-2 DIT butterfly that needs less instruction cycles than a radix-2 DIF butterfly | 4-8  |

|-------------|-----------------------------------------------------------------------------------------|------|

| Figure 4-4  | The radix-2, DIT butterfly kernel on the DSP56001/DSP56002                              | 4-9  |

| Figure 4-5  | A simple, triple-nested DO-loop radix-2 DIT FFT on DSP56000/DSP56001                    | 4-11 |

| Figure 4-6  | DSP96002 architectural block diagram                                                    | 4-14 |

| Figure 4-7  | The radix-2, DIT FFT Butterfly Kernel on the DSP96002                                   | 4-16 |

| Figure 4-8  | DSP56156 architectural block diagram                                                    | 4-18 |

| Figure 4-9  | The butterfly core of the DSP56156                                                      | 4-19 |

| Figure 4-10 | In-place bit-reversed to normal order conversion                                        | 4-26 |

| Figure 4-11 | A flow diagram of two stages in a radix-2 DIT butterfly                                 | 4-27 |

| Figure 4-12 | A flow diagram of a radix-4 DIT butterfly                                               | 4-29 |

| Figure 4-13 | Radix-4 DIT butterfly takes 17 instructions on the DSP96002                             | 4-30 |

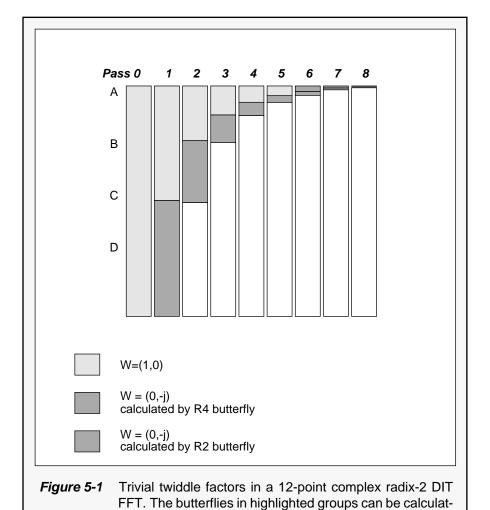

| Figure 5-1  | Trivial twiddle factors in a 512-point complex radix-2 DIT FFT                          | 5-11 |

| Figure 6-1  | Non-redundancy calculation of the Cooly-Tukey radix-2 DIT FFT with real inputs          | 6-3  |

x MOTOROLA

## Illustrations

| Figure 6-2 | Bergland algorithm has only log2(N)-1 passes and one more addition and subtraction                 | 6-5  |

|------------|----------------------------------------------------------------------------------------------------|------|

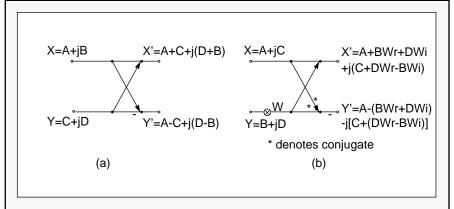

| Figure 6-3 | (a) Butterfly of Bergland Algorithm with W = 1 (b) Butterfly of Bergland Algorithm with W $\neq$ 1 | 6-6  |

| Figure 6-4 | C language code that generates Bergland order tables                                               | 6-7  |

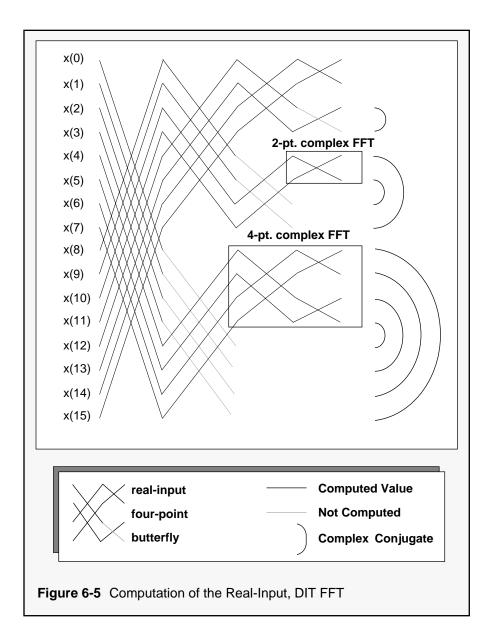

| Figure 6-5 | Computation of the real-input, DIT FFT                                                             | 6-17 |

| Figure 6-6 | DSP56001 assembly code that calculates energy of DFT coefficients by single parameter              | 6-19 |

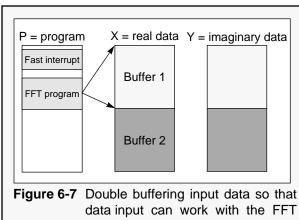

| Figure 6-7 | Double buffering input data so that data input can work with the FFT program concurrently          | 6-21 |

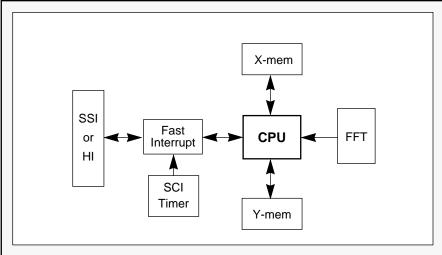

| Figure 6-8 | Block diagram of the double buffering technique                                                    | 6-22 |

| Figure 7-1 | The flow diagram of an 8-point discrete cosine transform                                           | 7-4  |

| Figure A-1 | Optimized Complex FFT for the DSP96002                                                             | A-1  |

| Figure B-1 | Faster real FFT for the DSP96002                                                                   | B-1  |

| Figure B-2 | Real FFT for DSP56001/2                                                                            | B-5  |

MOTOROLA xi

## **Tables**

| Table 8-1 | 1024-Point Complex FFT on Floating-Point DSPs    | 8-4 |

|-----------|--------------------------------------------------|-----|

| Table 8-2 | 1024-Point Real Input FFT on Floating-Point DSPs | 8-5 |

| Table 8-3 | 1024-Point Complex FFT on Fixed-Point DSPs       | 8-6 |

| Table 8-4 | 1024-Point Real Input FFT on Fixed-Point DSPs    | 8-7 |

MOTOROLA xiii

#### **SECTION 1**

# Introduction to the Fourier Integral

#### 1.1 Definition and History

"... a digital signal processor can efficiently compute the Fourier transform and perform specific frequency-domain tasks..."

The scientific and engineering communities have attempted to represent changing signals in two fundamental domains: time and frequency. Temporal changes are easily shown on oscilloscopes, for instance, where change in time is directly proportional to distance across a screen. Representation of signals in terms of frequencies falls under the general category of "spectrum analysis", and has generated a lot of attention recently, due to the increased availability of hardware which makes such representations possible. The first formal approach to spectrum analvsis probably dates back to the work of Fourier, who showed how to mathematically represent a general class of time-varying phenomena in terms of sine and cosine functions of particular frequencies. His work is best known as the Fourier Integral (inverse Fourier transform) (see Reference 1):

$$\chi(t) = \int_{+\infty}^{+\infty} X(f)e^{j2\pi ft}dt$$

Eqn. 1-1

where:  $j = \sqrt{-1}$  and  $e^{j2\pi ft} = \cos(2\pi ft) + j\sin(2\pi ft)$

MOTOROLA 1-1

When interpreted as an infinite summation, the previous integral is simply a linear combination of a number of sine and cosine functions (expressed by the complex exponential), each one of which is weighted by the complex amplitude X(f). Conversely, the complex frequency function X(f) can be derived from the time-varying signal  $\chi(t)$  by the Fourier Transform:

$$X(f) = \int_{+\infty}^{+\infty} \chi(t)e^{-j2\pi ft}dt$$

Eqn. 1-2

The two expressions shown in Eqn. 1-1 and Eqn. 1-2 define a Fourier transform pair  $\chi(t)$  and  $\chi(t)$ . The Fourier transform  $\chi(t)$  determines the frequency content of the signal in question, while  $\chi(t)$  shows the way the signal varies as a function of time. Note that, in general,  $\chi(t)$  can be directly measured (for instance, displayed on an oscilloscope).  $\chi(t)$  remains a mathematical expression which attempts to express our intuitive perception of frequency.

Unfortunately, it is not always true that the concept of frequency, as defined by the Fourier transform in Eqn. 1-2, and the intuitive concept of frequency as we perceive it, are identical. For instance, music consists of tones (frequencies) which vary over time. Although we can clearly perceive time-varying frequencies, Eqn. 1-2 does not allow for Fourier's concept of frequency to have any time-varying character— X(f) is a function of frequency only.

1-2 MOTOROLA

#### 1.2 Use of the Fourier Transform

Because of the basic nature of the frequency concept, practical applications of the Fourier transform are abundant. As more cost-efficient methods become available to compute the Fourier transform, the number of practical solutions to frequency-based problems will grow even larger. In these frequency-based applications, a digital signal processor can efficiently compute the Fourier transform (as defined in **SECTION 1.1 Definition And History**), and perform specific frequency-domain tasks such as elimination of certain frequency components, etc.

Three general types of Fourier transform applications are:

Number-Based — Most spectrum analysis applications require the direct evaluation of the Fourier transform as in Eqn. 1-2. Since the Fourier transform is a mathematical expression, these applications are based on numerical computations, and can be termed number-based. Examples range from spectrum analysis laboratory instrumentation and professional audio equipment to velocity estimation in radar. Note that in number-based applications the accuracy of the computed numbers is of vital importance to the performance of the overall system. For instance, the qualityconscious audio industry requires 16-bit or more precision in order to eliminate audible distortion.

MOTOROLA 1-3

- 2. Pattern-Based Many problems involve the recognition and detection of signals with a specific frequency content (a predefined spectral pattern). instance, speech consists of segments of sound with very specific frequency characteristics. In this type of application, the conversion to the frequency domain is often only a single step in the overall task. It is important that this conversion process be as fast as practical, to allow for sufficient time to perform computationally intensive pattern matching techniques. In providing fast addition to Fourier transform computations, the processor in question needs to be fast at generalpurpose DSP tasks so that it can perform a variety of frequency-based calculations for pattern matching.

- 3. Convolution-Based The third class of applications of Fourier transforms uses the transform as a simple mathematical tool to perform general filtering in a very efficient manner. This concept is based on the property that the Fourier transform of the convolution of two time-signals:

$$y(t) = \int_{+\infty}^{+\infty} \chi(t - \tau)h(\tau)d\tau$$

Eqn. 1-3

is equal to the product of the individual transforms:

$$Y(f) = X(f)H(f)$$

Eqn. 1-4

Eqn. 1-3 (better known as the convolution integral) represents the output of a linear filter with impulse

1-4 MOTOROLA

response h(t) and input signal x(t). Clearly, in the frequency domain, the output of a filter can be obtained by a simple multiplication, whereas in the time domain, a more complicated convolution integral needs to be solved. The amount of computation involved in evaluating the integral in Eqn. 1-3 becomes particularly large when the impulse response h(t) has a long time duration which often prevents real-time implementation. Clearly, if the Fourier transform X(f) of the signal can be computed efficiently, the filtering operation itself can be achieved by simple multiplications.

The combined number of computations (for computing the Fourier transform, for filtering in the frequency domain, and for obtaining the inverse Fourier Transform) is often less than the total number of calculations required to compute Eqn. 1-3 directly. This is especially true when the filter in question performs a simple frequency discrimination function (lowpass, bandpass, highpass, bandreject, etc.). In this case, the multiplications in the frequency domain can be replaced by a simple masking operation, which removes the stopbands and leaves the passband(s) unchanged.

Although no direct frequency information is extracted from the signal, the Fourier transform is used as a mathematical tool for fast-filtering applications. Note that again, fast Fourier transform and inverse Fourier transform "engines" are needed in order to provide the real-time filtering operation.

MOTOROLA 1-5

In summary, the basic nature of the frequency concept indicates that the number of possible frequency domain applications is as large as more conventional time domain applications. In the past, frequency domain applications were either difficult to implement or could not be realized in a cost-efficient manner because of the lack of low-cost, highperformance hardware. This application note demonstrates that the DSP56001/2 and the DSP96002 Families of digital signal processors fulfill the demanding requirements imposed by frequency domain problems. In addition to providing a fast implementation of high-precision Fourier transform computations, the general-purpose nature of the instruction set allows for a complete, single-chip, low-cost integrated solution to a wide variety of frequency domain problems.

1-6 MOTOROLA

#### **SECTION 2**

## The Discrete Fourier Transform

## 2.1 The Discrete-Time Fourier Transform (DTFT)

In order to compute the Fourier transform using digital hardware, Eqn. 1-2 needs to be approximated in a manner which makes machine computation feasible. The first step in this process consists of eliminating the theoretical integral symbol, and replacing it by a computable sum:

$$X(f) \approx \tilde{X}(f) = T \sum_{n = -\infty}^{+\infty} \chi(nT) e^{-j2\pi f nT}$$

Eqn. 2-1

The above expression uses a sampled signal  $\chi(nT)$ , where the sampling period T is made as small as possible to reduce approximation errors. Appropriately,  $\tilde{X}(f)$  is called the discrete-time Fourier transform (DT-FT). As T (the sampling period) becomes infinitely small, the previous summation approaches the original Fourier transform in Eqn. 1-2. To assess the accuracy of this approximation, note that the resulting expression for  $\tilde{X}(f)$  is a periodic function of frequency:

$$\tilde{X}(f) = \tilde{X}\left(f + \frac{1}{T}\right)$$

Eqn. 2-2

"... the results

need to be

available within

a finite time

period, and the

infinite

summation

must somehow

be reduced to a

finite

summation."

MOTOROLA 2-1

because:

$$e^{-\left(j2\pi fnT+j2\pi n\frac{T}{T}\right)} = e^{-j2\pi fnT}e^{-j2\pi n} = e^{-j2\pi fnT}$$

Eqn. 2-3

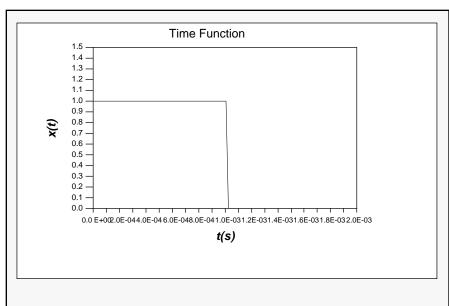

In general, the original spectrum X(f) is not periodic, and the approximation is only justified for a range of small values of f. In Figure 2-1, the DTFT magnitude and the Fourier transform magnitude of a simple rectangular function are shown for several values of the sample rate  $f_S = 1/T$ . Note the periodic nature of the resulting function, as well as the approximation errors due to the sampling process.

The Nyquist sampling theorem gives a well accepted criterion for the sampling rate. It states that a signal needs to be sampled faster than twice its highest frequency. In other words, if:

$$X(f) = 0$$

Eqn. 2-4

for  $|f| \ge B$  (B is referred to as the bandwidth of the signal), then the sampling frequency needs to satisfy:

$$f_S \ge 2B$$

Eqn. 2-5

In practice, signals rarely satisfy Eqn. 2-5, and some error, called the aliasing error, can be expected in the evaluation of X(f). The aliasing error is generated by frequency components at higher frequencies, which manifest themselves at lower frequencies because of the periodic nature of  $\tilde{X}(f)$  (aliasing). The aliasing error can be reduced by filtering out the higher-frequency components of the signal using a low-pass anti-aliasing filter and/or by increasing the sampling rate.

2-2 MOTOROLA

Figure 2-1 Fourier Transform of a Rectangular Function

MOTOROLA 2-3

## 2.2 Windowing and Windowing Effects

The discussion of aliasing errors illustrates how the Fourier transform can be approximated by an infinite summation. In practice, the results need to be available within a finite time period, and the infinite summation must somehow be reduced to a finite summation. One obvious way to reduce the infinite summation is by simply truncating the sum in Eqn. 2-2 to N terms as:

$$\tilde{X}_{W}(f) = T \sum_{n=0}^{N-1} \chi(nT) e^{-j2\pi f nT}$$

Eqn. 2-6

This truncation is frequently referred to as "windowing" because an infinite summation is viewed through a finite window. The resulting transform is called the windowed discrete-time Fourier transform (WDTFT). In mathematical terms, windowing is simply the multiplication of the signal by a window sequence of finite-length, w(n). In the simple case above, w(n)=1 for  $0 \le n \le N-1$ ; otherwise, w(n)=0. Because of its rectangular shape, the window shown above is called the rectangular window.

Unless the signal in question is of finite duration, this truncation will introduce other errors, resulting in a number of artifacts in the spectrum. To assess the effect of the windowing operation, a simple sine wave of the form:

$$\chi(t) = \sin(2\pi 1000t)$$

Eqn. 2-7

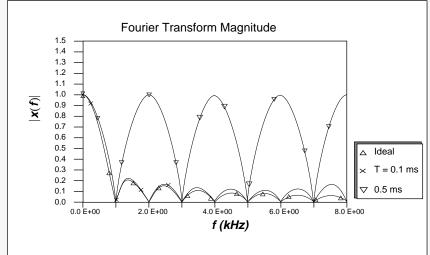

is sampled with a sampling frequency of 4000 Hz, and the windowed DTFT is computed with N=20.

2-4 MOTOROLA

Figure 2-2 shows the result of windowing a sine wave by a rectangular window. Windowing causes the following errors:

- Leakage Even though the input signal consists of a single-frequency component at 1000 Hz, the result clearly shows components at frequencies other than 1000 Hz. This is called the leakage effect: it appears as if energy has "leaked" from 1000 Hz to the rest of the spectrum.

- 2. Smoothing Although the theoretical transform exhibits an infinitely narrow, and infinitely large peak at 1000 Hz, the actual peak has finite magnitude and exhibits finite width. It appears that the narrow peak has been "smeared" out in the frequency domain as a result of the windowing function in the time domain. This effect is appropriately termed the smoothing effect.

- 3. Ripple The overall magnitude plot in Figure 2-2 shows an oscillatory character not present in the original Fourier transform: this is called the ripple effect. The origin of the ripple effect lies in the discontinuity (abrupt start and end) introduced in the signal by the window. Windows with more gradual transitions generally have lower sidelobes and less ripple.

In general, a tradeoff exists between these different effects, and the advantages of an appropriate windowing function can be chosen for a specific application. For an excellent summary of existing windowing functions and their properties, see Reference 2.

MOTOROLA 2-5

2-6 MOTOROLA

## 2.3 Sampling the Frequency Function

The windowed DTFT is now ready for machine computation, with one exception: the independent frequency variable f is still a continuous variable, and needs to be captured in discrete intervals, or sampled. Since the DTFT is periodic in the frequency domain with period f<sub>s</sub>, only values of f from 0 to fs (the sampling frequency) need to be computed. Although there are similar arguments concerning the distance between successive frequency samples as in the case of time-sampling, it turns out that when the WDTFT is sampled every f<sub>s</sub>/N Hz, fast algorithms for computing the transform can be derived. Note that in this case, the number of samples in the window (N) and the number of samples in the frequency domain (N) are equal. The resulting transform is called the discrete-time Fourier series (DTFS):

$$\tilde{X}_{N}(k) = T \sum_{n=0}^{N-1} \chi(nT) e^{-j\frac{2\pi}{N}nk}$$

Eqn. 2-8

The inverse DTFS is given by:

$$\chi_N(k) \,=\, \frac{1}{NT} \sum_{k\,=\,0}^{N\,-\,1} \tilde{X}_N(k) e^{j\frac{2\pi}{N}nk} \tag{Eqn. 2-9} \label{eq:chiN}$$

Keep in mind that the values of the frequency samples of  $f_k$  are equal to  $[f_s/N]$  k.

MOTOROLA 2-7

Note that many textbooks simply define the Discrete Fourier transform (DFT)  $X_N(k)$ :

$$X_{N}(k) = \sum_{n=0}^{N-1} \chi(nT)e^{-j\frac{2\pi}{N}nk}$$

Eqn. 2-10

with inverse transform:

$$\chi_{N}(n) = \frac{1}{N} \sum_{n=0}^{N-1} X_{N}(k) e^{j\frac{2\pi}{N}nk}$$

Eqn. 2-11

Obviously, the DFT and DTFS differ only by a scaling factor of T, making the spectrum independent of the sampling period. Consequently, explicit T dependence can be dropped from Eqn. 2-11.

Although the sequence  $x_N(n)$  corresponds to the original sampled and windowed sequence  $\chi(nT)$  for sampling instants 0 through N-1, the complete sampled sequence  $\chi(nT)$  for any n cannot necessarily be recovered from it. Indeed,  $x_N(n)$  appears to be periodic with period N due to

2-8 MOTOROLA

<sup>&</sup>lt;sup>1</sup> The error introduced in the time domain by sampling a frequency function is termed "aliasing in time" which is analogous to the "aliasing in frequency" caused by sampling a time function. (See SECTION 2.1 The Discrete-Time Fourier Transform (DTFT)). That is, if a frequency spectrum is not sampled densely or closely enough, the signal constructed in the time domain through the inverse "discrete-frequency Fourier transform" will show some distortion.

This must be kept in mind in convolution-based applications, where the forward as well as inverse transforms are used; the incoming signal stream needs to be segmented, and the computed signal segments need to be pieced together to construct the complete output stream. Most basic text-books on digital signal processing discuss techniques for piecing together the output stream (see Reference 3).

MOTOROLA 2-9

#### **SECTION 3**

# The Fast Fourier Transform

#### 3.1 Motivation

"Since there are two independent variables (time and frequency) in the Fourier transform, dividing (or decimating) the DFT into smaller ones can be done in two ways."

**U**pon closer examination of Eqn. 2-10, it becomes clear that for every frequency point, N-1 complex summations and N complex multiplications need to be evaluated. Since there are N frequency points to be evaluated, this gives a total of N(N-1) complex sums, and N<sup>2</sup> complex multiplications. Counting two real sums for every complex one, and four real multiplications plus two real summations for every complex multiplication, gives a total of 4N<sup>2</sup>- 2N real summations and 4 N<sup>2</sup> real multiplications.

The above numbers grow rapidly for increasing N. For N=1024 (1024-point DFT), 4,194,304 real multiplications are required. If this is computed on a DSP56001/DSP56002 with a 27-MHz clock, it takes 0.31 seconds just to execute that many real multiplications. Since the DFT computation needs to be completed by the time the next 1024 data points are collected for real-time performance, the sampling rate is limited to a maximum of 3.3 kHz. Obviously, faster solutions are needed.

MOTOROLA 3-1

#### 3.2 Divide and Conquer

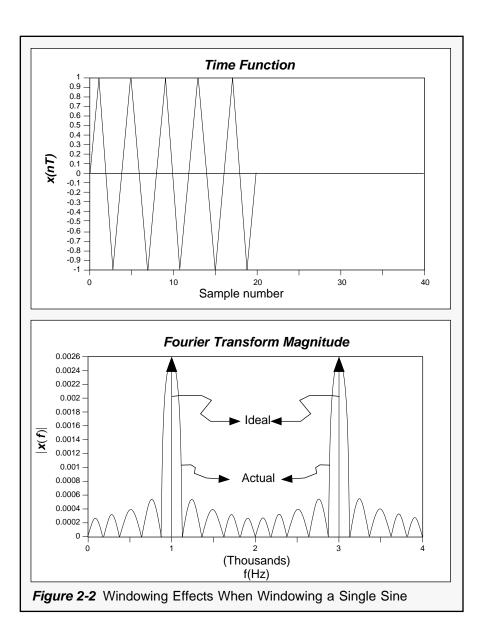

A faster algorithm for computing the DFT can easily be derived. The principle behind this is very simple. As illustrated in Figure 3-1, a square of half the linear dimension of a larger square has one-fourth the surface area. This is because the surface area is proportional to the square of the linear dimensions of the square. Similarly, the number of multiplications needed to compute the DFT is proportional to the square of the DFT's length (N). Thus, if we could replace the DFT over N points by two DFTs over N/2 points, computations would be reduced in order of magnitude of 0.5 (=0.25+0.25).

Since there are two independent variables (time and frequency) in the Fourier transform, dividing (or decimating) the DFT into smaller ones can be done in two ways. We can attempt to represent an N-point transform in terms of DFTs over half the number (N/2) of time-samples. This approach is

3-2 MOTOROLA

appropriately called the decimation-in-time or DIT approach. Alternatively, the N-point DFT can be represented in terms of DFTs with N/2 frequency samples. This approach is called the decimation-infrequency or DIF approach.

### 3.3 The Decimation-in-Time and Decimation-in-Frequency Radix-2 Fast Fourier Transforms

It is easily shown that Eqn. 2-10 can be rewritten when N is even as:

$$X_{N}(k) \ = \ \sum_{r = 0}^{(N/2) - 1} \chi(2rT) e^{-j\frac{2\pi}{(N/2)}rk} + e^{-j\frac{2\pi}{N}(N/2) - 1} \\ \sum_{r = 0} X \Big[ (2r + 1) \ T \Big] e^{-j\frac{2\pi}{(N/2)}rk}$$

Eqn. 3-1

As illustrated in Figure 3-2, this expression shows how two N/2-point DFTs can be combined to obtain one N-point DFT. If N is an integer power of 2, this process can be repeated, as shown in Figure 3-3 and Figure 3-4, until a simple, two-point DFT is obtained. This gives rise to the flow diagram of a DIT fast Fourier transform (FFT) as shown in Figure 3-5, which represents a complete 8-point FFT computation.

MOTOROLA 3-3

$\begin{tabular}{ll} \textit{NOTE:} & $k$/N$ denotes multiplication by the "twiddle factors" & $-j\frac{2\pi}{N}k$ & throughout this document & $e$ & $e$$

3-4 MOTOROLA

Figure 3-4 Decimation-in-Time FFT: Final Step (2-Point DFT)

**MOTOROLA** 3-5 The basic flow diagram of Figure 3-5 can be further simplified by rearranging the terms in the basic building block (the butterfly) as in Figure 3-6. Also, it is seen from Figure 3-5 that input samples no longer occur in normal, sequential order. When the indices are represented in their binary equivalent, however, the input samples appear in "bit-reversed" order. Figure 3-8 shows how the diagram can be rearranged for normally-ordered inputs and bit-reversed outputs.

Figure 3-6 Rearrangement of the "butterfly" building block of the DIT FFT

Figure 3-7 Rearrangement of the "butterfly" building block of the DIF FFT

3-6 MOTOROLA

Figure 3-8 Rearrangement of the DIT computation of Figure 3-6

Figure 3-9 and Figure 3-10 show how the DFT with N frequency points can be obtained in terms of DFTs with a smaller number of frequency samples (decimation-in-frequency FFT). Note that the basic building block (butterfly) is different than for the DIT case (see Figure 3-10).

MOTOROLA 3-7

3-8 MOTOROLA

#### 3.4 The Decimation-in-Frequency Radix-2 Fast Fourier Transforms

If Eqn. 2-10 is decomposed from the frequency domain, we can show the following equations exist:

$$X_{\mbox{$N$}}(2k+1) = \sum_{r=0}^{(\mbox{$N/2$})-1} [x(r) - x(r+N/2)] e^{-j\frac{2\pi rk}{N/2}} e^{-j\frac{2\pi r}{N}} \label{eq:XN}$$

Eqn. 3-3

The decimation in frequency butterfly is shown in Figure 3-9.

MOTOROLA 3-9

#### **SECTION 4**

# Complex FFT on the Motorola DSP Family

#### 4.1 Required Hardware Support for FFT Calculation

"In general, doubling the points in butterflies of FFT reduces the number of groups in each pass and the number of passes."

The basic building block of the DIT FFT routine is the butterfly computation shown in Figure 3-6. Consequently, the architecture and instruction set of a DSP device should allow efficient computation of this basic butterfly. Since the butterfly consists of additions and multiplications, a hardware adder/subtracter and multiplier is crucial. The DSP56001/2 and the DSP56156 provide a multiplication and addition instruction, or MAC, which is beneficial to most DSP applications including FFT, with no increase in silicon cost. The DSP96002 supports FFT calculation capability by adding subtraction to the MAC function, which provides the multiplication, addition and subtraction instruction, FMPY||ADD||SUB.

Since the butterfly calculation requires complex data, the architecture must easily support complex arithmetic. The input and output data to the butterflies are moved between the processor's arithmetic unit and memory. Consequently, efficient moves are needed.

MOTOROLA 4-1

DSP56001/2 and DSP96002 hardware feature two data memory modules; X and Y. The real component and imaginary component of a complex number can be stored in the X and Y memory modules respectively. Also, the DSP56001/2 and the DSP96002 can perform dual reads and dual writes in one instruction cycle. In contrast, the DSP56156 has only one data memory module, X, where both real and imaginary components of the complex data are stored. To support complex number fetch, the DSP56156 provides dual memory read, where in one instruction, it reads the X memory twice if the specified address registers are used.

The overall FFT algorithm is an array of many such butterflies, and the size of the array depends upon the number of points (N) in the FFT. In order to write general FFT routines (for any N of the power of 2), efficient implementation of the repetitive execution of the basic butterfly element is important. Although FFTs may be calculated on general-purpose microprocessors, typically, a great deal of software overhead is involved. A hardware solution, using hardware designed to efficiently implement the calculation of FFTs, would be generally preferred in a real-time system. The DSP56001/2, DSP96002, and DSP56156 feature a zero-overhead DO loop instruction. After the loop is set up (three instruction cycle time), each iteration takes no additional cost in overhead.

In real-life applications, time as well as frequency data is used in normal order, even though the diagram of Figure 3-7 delivers the frequency data in bit-reversed order. Thus, an efficient method for bit-reversed addressing is needed while avoiding time-consuming

4-2 MOTOROLA

software solutions that modify the addressing order. The DSP56001/2, DSP96002, and DSP56156 all feature a bit-reversed addressing mode.

Some FFT algorithms, (for example, radix-4 FFT) require several registers to hold immediate results. The number of registers available on the DSPs is critical for computation intensive applications since storing and restoring intermediate results to and from memory will take more processing time than if the results are available in on-chip registers.

The input data (time samples) of the FFT is usually obtained from an external source such as an A/D converter. This data collection must occur in parallel with the FFT computation to make real-time performance possible. Consequently, a DSP device must provide easy interface with a variety of A/D converters, and must support low-overhead interrupt schemes which can load data from an external device with minimal impact on the FFT computation. The DSP56001/2, DSP96002, and DSP56156 all feature a variety of peripherals on chip. More details about real-time data acquisition are discussed in **SECTION 7**.

The key points to implementing efficient FFT calculation using programmable DSPs are summarized below.

#### FFT calculation requires:

- 1. MAC or, ideally, FMPY||ADD||SUB instruction

- Dual memory read and write in one instruction cycle

- 3. Zero-overhead loop instruction

- 4. Bit-reversed addressing mode

- 5. Sufficient number of registers

- Fast I/O to provide real time data (in real-time applications)

# 4.2 Radix-2 DIT and DIF Butterflies

Theoretically, radix-2 decimation in time (DIT) butterflies and decimation in frequency (DIF) butterflies have the same computational complexity: three additions, three subtractions, and four multiplications. Since most DSPs have only one hardware multiplier, the minimum cycle time for multiplication for one DIT or DIF butterfly is four instruction cycles. However, on the DSP56001, a MAC instruction can implement one multiplication and one addition in parallel in a single instruction cycle. Four of the six additions or subtractions in a DIT butterfly can be executed in parallel with four multiplications, and two more additions are required to finish the DIT butterfly calculation. Due to data dependence, a DIF butterfly can implement only two additions in parallel with two multiplications. Thus, one DIF butterfly calculation requires four multiplications plus four additions (see Figure 4-3).

The DSP96002 features a special instruction, FMAY||ADD||SUB, which can implement either a DIT or a DIF butterfly in four instruction cycles. Although the DSP56156 has a MAC instruction, the lack of a dual memory write operation plus constraints on ad-

4-4 MOTOROLA

dress pointer updates in dual memory read operations, causes the DIT butterfly and the DIF butterfly to both take eight instruction cycles.

In short, the Motorola DSP architecture implements the more efficient DIT butterfly, since it generates shorter cycle time than the DIF. The following discussions assume a radix-2 DIT, extending to radix-4 DIT in later sections.

Figure 4-1 Grouping of Butterflies in the FFT Calculation

# 4.3 Complexity of a Radix-2 DIT FFT

The number of instructions required in a radix-2 DIT FFT is determined by the number of instructions in the butterfly core and the structural overhead of the DSP. If only arithmetic operations are counted in term of the multiplications and additions, a triplenested implementation of the FFT (see next sections) requires the following number of instruction cycles for  $N = 2^{m}$ :

$$m \times N/2 \times BFLY$$

Egn. 4-1

where BFLY is number of instructions for calculating a complex input butterfly. For the DSP56001/2, the DSP96002 and the DSP56156, BFLY is 6, 4, and 8 respectively. On the DSP96002, for example, a 1024-point complex FFT needs 10 x 512 x 4 = 20,480 instruction cycles.

# 4.4 Implementation on Motorola's DSP56001

#### 4.4.1 DSP56001 Architecture

The DSP56001 (see Reference 4) was the first member of the Motorola Digital Signal Processor line. It features 16.5 million instructions per second (MIPS) with a 33 MHz clock.

4-6 MOTOROLA

The data paths are 24 bits wide, thereby providing 144 dB of dynamic range. More importantly, intermediate results are held by a 56-bit accumulator which gives more accuracy in noise sensitive applications. The data ALU, address arithmetic units, and program controller operate in parallel so that an instruction prefetch, a 24x24-bit multiplication, a 56-bit addition, two data moves, and two address pointer updates using one of three types of arithmetic (linear, modulo, or bitreversed) can be executed in one instruction. Three on-chip peripherals (Serial Communication Interface, Synchronous Serial Interface and Host interface), a clock generator and seven buses (three address, four data) make the overall system functionally complete and powerful. The architecture of DSP56001 is shown in Figure 4-2.

4-8 MOTOROLA

butterfly

## 4.4.2 DIT Butterfly Kernel on DSP56001

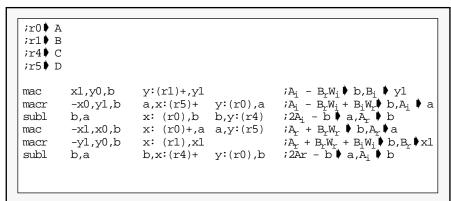

The parallel architecture and the instruction set of Motorola's DSP56001/2 lend themselves particularly well to the radix-2 DIT FFT computation. The DIT butterfly equations are programmed on Motorola's DSP56001/2 as given below:

$$\begin{aligned} &A'_r = A_r + B_r \, W_r + B_i \, W_i \\ &A'_i = A_i + B_i \, W_r - B_r \, W_i \\ &B'_r = 2A_r - A'_r \\ &B'_i = 2A_i - A'_i \end{aligned}$$

Eqn. 4-2

where:

i represents an imaginary componentr represents a real component

' symbolizes output items

The basic butterfly "core" is implemented by assembly language in Figure 4-4. Note that the previous DSP56001/2 equations are written in this particular form such that the instruction to shift left and subtract accumulators (SUBL) can be used. This SUBL instruction allows efficient implementation of the DIT butterfly in a two-accumulator ALU.

Figure 4-4 The radix-2, DIT butterfly kernel on the DSP56001/2

The kernel shown in Figure 4-4 executes in six instruction cycles, or a total of 12 clock cycles. This is made possible because of the parallel architecture of the DSP56001/2, which allows up to two data ALU operations (multiply/accumulate) in parallel with two data moves to/from memory and two pointer updates in a single instruction cycle. The dual data spaces X and Y with the appropriate X and Y buses are ideally suited for complex arithmetic; the real components are stored in X memory and the imaginary components are stored in Y memory.

The simplest way of combining all of the butterflies into a complete program is shown in Figure 4-1. The FFT diagram is first divided into FFT passes. On each pass, the data is fetched from memory, the butterfly calculations are done, and the results are moved back out to memory. It is easily shown that there are log2N passes. Within each pass, the butterflies cluster in groups. From one pass to the next, the number of groups doubles, while the number of butterflies per group is divided by two. Note that the twiddle factors are the same for all butterflies within each group, and that the order of the twiddle factors from one group to the next is bit-reversed. This is easily implemented on the DSP56001/2 by setting the appropriate modifier register (m6) equal to zero and the offset register (n6) equal to N/4 (= coefficient table size/2), such that the twiddle factors are addressed in bit-reversed manner.

This gives rise to the simple, triple-nested DO loop program shown in Figure 4-5. The outer DO loop steps through passes, the middle loop goes through all of the groups within a pass, and the inner loop cycles through all of the butterflies inside a group. The

4-10 MOTOROLA

DSP56001/2 is particularly well suited for looped program execution because it has hardware DO-loop capability. Once a loop is entered through the DO instruction, this loop is executed without any time penalty. The resulting program takes 40 words in program memory. This is the most compact implementation of the radix-2 DIT FFT. A 1024-point complex FFT using this code executes in 4.72 ms when using a 27-MHz clock.

```

;This program originally available on the Motorola DSP bulletin board.

;It is provided under a DISCLAIMER OF WARRANTY available from

;Motorola DSP Operation, 6501 Wm. Cannon Drive W., Austin, Tx., 78735.

; Radix 2, In-Place, Decimation-In-Time FFT (smallest code size).

;Last Update 30 Sept. 86 Version 1.1

points, data, coef

macro

fftr2a

ident

1,1

;Radix 2 Decimation in Time In-Place Fast Fourier Transform Routine

Complex input and output data

Real data in X memory

Imaginary data in Y memory

; Normally ordered input data

; Bit reversed output data

Coefficient lookup table

-Cosine values in X memory

-Sine values in Y memory

;Macro Call - fftr2a points,data,coef

number of points (2-32768, power of 2)

points

data

start of data buffer

start of sine/cosine table

coef

;Alters Data ALU Registers

x1 x0 y1 y0

a1

a0

а

b0

;Alters Address Registers

r0 n0

m0

n1

m1

n2

r4

n4

m4

r5

m5

nб

r6

n6

m6

```

Figure 4-5 A Simple, Triple-Nested DO Loop Radix-2 DIT FFT on DSP56001/2 (sheet 1 of 2)

```

;Alters Program Control Registers

;Uses 6 locations or System Stack

;Latest Revision

September 30, 1986

;r0 points to A

;rl points to B

;r4 points to C

;r5 points to D

;r6 points to twiddle factor

move

# points/2,n0;initialize butterflies per group

;initialize groups per pass

move

# 1,n2

# points/4,n6

;initialize C pointer offset

move

#-1,mo

move

;initialize A and B address modifiers

move

m0.m1

;for linear addressing

move

m0,m4

m0.m5

move

move

#0,m6

;initialize C address modifier for

reverse carry (bit-reversed) addressing

;Perform all FFT passes with triple nested DO loop

dО

\#(\alpha cvi(\alpha log(points)/(\alpha log(2)+0.5)_end_pass

#data,r0

move

;initialize A input pointer

move

r0,r4

;initialize A output pointer lua

(r0)+n0,r1[;initialize B input pointer move

#coef,r6;initialize C input pointer

lua

(r1)-,r5

;initialize B output pointer

move

n0,n1

;initialize pointer offsets

move

n0,n4

n0,n5

move

0.b

n2,_end_grp

x:(r1),x1y:(r6),y0

;lookup -sine and

move

;-cosine values

move

x:(r5),a

y:(r0),b

;preload data

x:(r6)+n6,x0

;update C pointer

move

dо

n0,_end_bfy

x1,y0,b

y:(r1)+,y1

;Radix 2 DIT

mac

;butterfly kernel

-x0,y1,b

y:(r0),a

macr

a,x:(r5)+

b,y:(r4)

subl

b,a

x:(r0),b

-x1,x0,b

x:(r0)+,a

a,y:(r5)

mac

macr

-y1,y0,b

tx:(r1),x1

subl

b,a

b,x:(r4)+

y:(r0),b

_end_bfy

a,x:(r5)+n5 y:(r1)+n1,y1

jupdate A and B pointers

move

move

x:(r0)+0,x1 y:(r4)+4,y1

_end_grp

n0.b1

move

lsr

b

n2,a1

; divide butterflies per group by two

lsl

а

b1.n0

;multiply groups per pass by two

move

a1,n2

end pass

endm

```

Figure 4-5 A Simple, Triple-Nested DO Loop Radix-2 DIT FFT on DSP56001/2 (sheet 2 of 2)

4-12 MOTOROLA

# 4.5 Implementation on Motorola's DSP96002

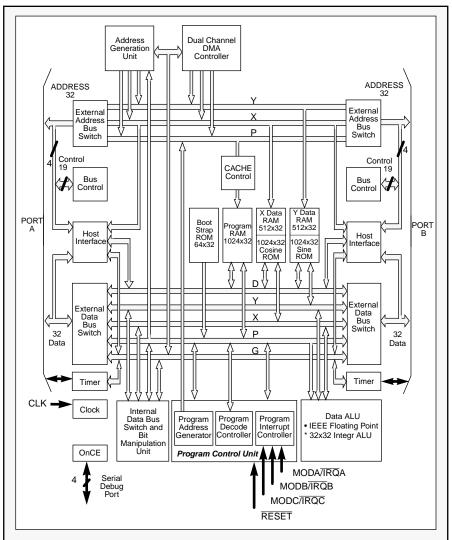

#### 4.5.1 DSP96002 Architecture

DSP96002 is a 32-bit floating-point digital signal processor with 20 million instructions execution per second using a 40 MHz clock. The data ALU provides full conformance with the IEEE 754-1985 Standard for Single Precision Binary Floating-Point Arithmetic. Single Extended precision with a 32-bit mantissa and 11-bit exponent is also implemented. The data ALU, AGU, and program controller operate in parallel within the CPU so that an instruction pre-fetch, up to three floating point operations, two data moves, and four address pointer updates using one of three types of arithmetic (linear, modulo, and reverse carry) can all be executed in one instruction cycle.

Also, an on-chip dual channel DMA controller generates two addresses, using one of the three types of address update arithmetic so that a memory-to-memory or memory-to-peripheral transfer can occur in parallel with the CPU operation during each instruction cycle. Host interface circuitry on each port provides a flexible slave interface to external processors and/or DMA controllers for easy design of a multi-master system. Designed primarily for image processing, realtime data acquisition, sonar signal processing, radar signal processing, medical image analysis, and video compression, the DSP96002 has the widest data bandwidth of any DSP currently on the market. A spe-FMAY||ADD||SUB instruction makes **FFT** calculations extremely fast on the DSP96002.

**Figure 4-6** DSP96002 Architectural Block Diagram. Two symmetric bus expansion ports with two channel DMA controller that blow away the speed limit on external memory access and data I/O.

4-14 MOTOROLA

## 4.5.2 DIT Butterfly Kernel on DSP96002

The butterfly equations implemented in the radix-2, DIT FFT on DSP96002 are the following:

$$A'_{r} = A_{r} + B_{r} W_{r} + B_{i} W_{i}$$

$A'_{i} = A_{i} + B_{i} W_{r} - B_{r} W_{i}$

$B'_{r} = A_{r} - (B_{r} W_{r} + B_{i} W_{i})$

$B'_{i} = A_{i} - (B_{i} W_{r} - B_{r} W_{i})$

where: *i* represents an imaginary component

represents a real component

symbolizes output items

The implementation of this basic butterfly in DSP96002 assembly language code is shown in Figure 4-7. The kernel in Eqn. 4-3 executes in four instruction cycles, or eight clock cycles. Since four real multiplications are needed, and only one real multiplier is available, this is the most efficient implementation possible. In addition to the features available on the DSP56001/2, this efficient execution is obtained by the FADDSUB instruction which delivers the sum and the difference of two operands, in parallel with a multiplication and two data moves. With this feature, a total of three floatingpoint operations can be executed in one instruction cycle, resulting in a peak performance of 60 million floating-point operations per second (MFLOPS) with a 40-MHz clock.

The triple-nested DO loop routine, which computes the radix-2, DIT FFT on the DSP96002 takes only 30 words in program memory. A 1024-point complex FFT is executed in only 2.31 ms, assuming a 27-MHz clock.

```

;r0 → A

;r1 ➡ B

;r4 ➡ C

;r5 ➡ D

\label{eq:continuous_section} \texttt{fmpy} \; \texttt{d8}, \texttt{d6}, \texttt{d} \quad \texttt{fadd.s} \quad \texttt{d3}, \texttt{d0} \quad \; \texttt{x:(r0)}, \texttt{d4.s} \quad \texttt{d2.s}, \texttt{y:(r5)+} \quad \texttt{;Br*sin} \; \clubsuit \; \texttt{d2}

;Bj*sin + Br*cos ➡ d0

;Ar → d4,Dj → mem.

fmpy d8,d7,d3 faddsub.sd4,d0 x:(r1)+,d6.s d5.s,y:(r4)+ ;Bj*sin \Rightarrow d3

;Ar + Br1 → d0

;Ar - Br1➡ d4

;Br ➡d6

;Cj ➡ mem.

fmpy d9,d6,d0 fsub.sd1,d2 d0.s,x:(r4) y:(r0) + d5.s; Br*cos \Rightarrow d0

;Br*sin - Bj*cos ➡ d2

;Cr ➡ mem.

;Aj ⇒ d5

fmpy d9,d7,d1 faddsub.sd5,d2 d4.s,x:(r5) y:(r1),d7.s ;Bj*cos \Rightarrow d1

;Aj + Bj1 → d2

;Aj - Bj1 ⇒ d5

;Dr →mem.

;Bj ➡ d7

```

Figure 4-7 The Radix-2, DIT FFT Butterfly Kernel on the DSP96002

4-16 MOTOROLA

# 4.6 Implementation on Motorola's DSP56156

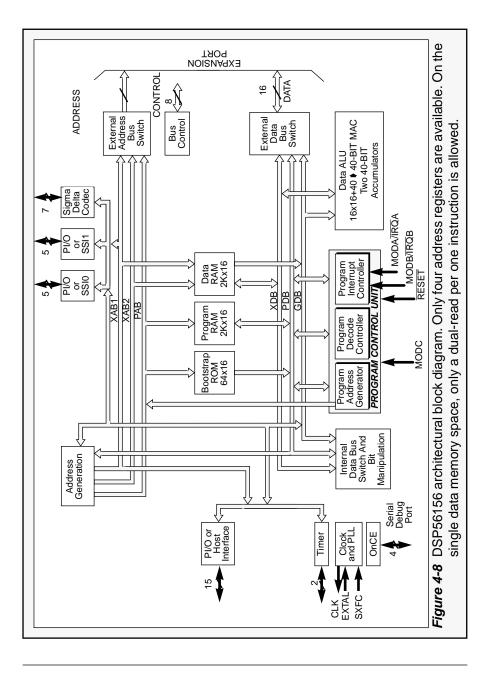

#### 4.6.1 DSP56156 Architecture

The DSP56156 is the most recent addition to the Motorola DSP line. This 16-bit fixed-point number DSP is designed primarily for speech coding and telecommunication. The on-chip sigma-delta codec functions as a bridge between the analog and digital world. The on-chip phase-locked-loop (PLL) reduces clock noise to a minimum. Operating at 60 MHz, the DSP56156 can execute 30 million instructions per second with two kilowords (2k) on-chip data RAM (which is four times larger than DSP56001's) and four address registers. Since the DSP56156 is designed for the digital cellular phone, its limited instruction operation codes must focus on telecommunication capability, and some of its advanced addressing modes and instructions that accelerates FFT calculation must be compromised due to the smaller instruction words.

Although only one memory module can be accessed in a single instruction cycle, the DSP56156 does support dual memory reads. However, it does not support dual memory writes in a single instruction cycle. Four address registers and a single write per instruction may slow down FFT performance on DSP56156, but having 2k on-chip data memory may compensate for a portion of the performance loss, i.e. dual on-chip memory reads may save time equivalent to four instruction cycles if the number of data points is between 256 and 1024 points.

4-18 MOTOROLA

## 4.6.2 DIT Butterfly Kernel on DSP56156

The butterfly equation for the DSP56156 is the same as the DIT butterfly equation for the DSP56001/2 as shown in Eqn. 4-2. However, two more instructions are required in the DSP56156 butterfly than the DSP56001/2 because of its lack of a dual-write operation and its constraints on the address register mode. Figure 4-9 shows the DSP56156 assembly language code of the butterfly core.

**Figure 4-9** The butterfly core of the DSP56156. Notice that a single write operation paralleling with an instruction always occupies a whole data move field.

# 4.7 Scaling for Fixed-Point Processors

(DSP56001/2 and DSP56156)

Whenever mathematical algorithms are implemented in digital hardware, note that results are obtained with finite precision. The precision is generally limited by the number of bits used in the number representation, and depends on how the arithmetic

limits its results to those bits. The user must use care to prevent overflows in the FFT outputs of fixed-point DSPs. Scaling via shifting or dividing can keep input data or intermediate results within the correct range, while maintaining maximum precision on the outputs.

## 4.7.1 Scaling at the Input – Guard Bits

Since data length grows with each pass, overflow can occur at any pass if there is no scaling in the input of a fixed point number DSP. The magnitude of the output by the DIT butterfly defined in Eqn. 4-2 will grow an average of one bit on the output in each pass. This is based on the observation that output A' (a complex output) can be rewritten as  $A' = A + B \times W$  where A', A, B, and W are complex numbers. Since  $W = e^{-j\theta}$ , it has a unit magnitude.

The complex operation B x W simply rotates B according to  $\theta$  and causes no magnitude growth. Complex addition is the only chance in a single butterfly calculation to make the output magnitude grow larger than a value of one. One addition can cause growth of one bit. Therefore, for N =  $2^m$  points of the FFT, m passes are required, i.e., m times a potential worst case magnitude doubling. However, the twiddle factor will reach its maximum magnitude when  $\theta = \pi/4$ . For this case, the maximum magnitude growth is 2.4 bits on real and imaginary components. Fortunately, only two groups of butterflies in each pass will use the maximum twiddle factors. No butterflies use the maximum twiddle factors twice

4-20 MOTOROLA

within an entire FFT calculation. This mutually exclusive characteristic is the base upon which block floating point arithmetic is designed.

To prevent overflows in the FFT calculations, the input data should keep m zeros in the significant part so that growth bits will not get lost during the overflow. The m zeros are called "guard bits". To obtain sufficient guard bits, divide the input data words by N. For example, if the DSP56001 is implementing a 1024point complex FFT, 10 guard bits are inserted into the most significant bits of the 24-bit data word, resulting in 14 bits of actual information. But on the 16bit DSP56156, only 6 bits contain actual information after 10 guard bits are inserted. This may make the signal-to-noise ratio unacceptably low. This method of scaling the input data is simple and effective on a smaller FFT or on a large data word processor like the DSP56001. For a larger FFT or a small data word processor, an alternative method discussed in the next subsection may result in improved signalto-noise ratio with some trade-offs.

# 4.7.2 Scaling During the Passes – Auto-Scaling and Block Floating-Point

Scaling in the input truncates valuable information contained in data words by shifting input data right by m-bits. 6.02 x m dB have already been lost before the start of the FFT calculations. As indicated in the last subsection, an average of one bit word growth occurs in each pass. Another way to prevent over-

flow in the FFT calculation is to scale down the output of the butterfly by two at each pass, regardless of whether or not an overflow occurs. Since the scaling down at the output is automatically carried out to the next pass, the amount of scaling down is known before hand. To obtain the true FFT output, simply multiply each output by N. This method is simple and has better signal-to-noise ratio than the scaling in the input method. But some passes may not have bit growth or overflows, so excessive scaling may occur, and automatic scaling may cause some information to be lost.

A more aggressive method treats one pass as one block of data, and assigns an exponent for each block. If bit growth occurs, the method scales down the output by one bit and increases the exponent by one. At the end of the FFT, the same number of scaling up operations must be carried out. In the DSP56156/DSP56002, the scaling bit (bit 7 in the status register) eases implementation of this method. The scaling bit is referred to as a "sticky" bit because once set, it retains its status until the next read of the status register. Five more instructions are added to the end of each pass to check the scaling bit in the DSP56002 and DSP56156, and to update the exponent of the complex FFT. (See program FFTBF.asm on the Motorola DSP bulletin board: Dr. BuB.) Among the methods discussed here, the sticky bit method gives the best signal-to-noise ratio.

4-22 MOTOROLA

# 4.8 Twiddle Factors and On-Chip ROM

## 4.8.1 Twiddle Factors for Decimation-in-Time

Twiddle factors,  $W_N^k = e^{-j2\pi k/N}$ , are coefficients used in FFT calculations. For normal order input radix-2 decimation-in-time FFT, the twiddle factors are always fetched in bit-reversed order, i.e.

$$W_N^0, W_N^{(N/2)-1}, W_N^{N/4}, W_N^{N/8}, W_N^{(3N)/8}, ..., W_N^{(N/4)-1}$$

Note that for an N point radix-2 FFT, two input data words share one twiddle factor, and the bit-reversed order of the twiddle factor is based on N/2 points.

#### 4.8.2 Sine Table on the DSP56001/2

When the data-ROM-enable (DE) bit in the OMR register of the DSP56001/2 is set, the Y memory from \$100 to \$1FF contains a 256-point full cycle sine-wave, and each data entry has 24-bit accuracy. As mentioned in the last subsection, for an N point FFT, N/2 complex coefficient twiddle factors are required, and these N/2 twiddle factors are a half cycle of the sine and cosine waveforms. Since only a 256-point full cycle sine-wave is stored in the DSP56001/2 data ROM, the maximum FFT length utilizing only internal twiddle factors is one full cycle

of the sine table, 256 points. However, a FFT larger than 256 points can still be implemented utilizing the on-chip sine table by calling this internal ROM during the first several passes and the first several groups in the last pass. Because DIT and normal input order FFT require bit-reversed sine and cosine tables, the DSP must be in the bit-reversed addressing mode when the on-chip sine table is invoked. A common set up for addressing this table is:

r6 = \$100 n6 = \$40m6 = 0

To address the cosine table in the FFT calculation, the following relation between sine and cosine is utilized:

$$\cos(x) = \sin(x + \pi/2)$$

Eqn. 4-4

Another address pointer, for example, r2 is used to point to the correct location.

r2 = \$140 n2 = \$40m0 = 0

This set-up can be applied for all FFTs up to 256 points with length equaling a power of two, 2<sup>N</sup>.

# 4.8.3 Sine and Cosine Tables on the DSP96002

The on-chip ROM of the DSP96002 features sine and cosine tables. When the DE bit is set to 1, X and Y memory from \$400 to \$7FF contain 512-point cosine and sine tables respectively. Therefore, the

4-24 MOTOROLA

maximum data length of the FFT without utilizing external twiddle factors is 512 points. The addressing set-up is similar to that of the DSP56001:

r6 = \$400 n6 = \$100m6 = 0

Only one set of address registers is required on the DSP96002 to access both sine and cosine values.

# 4.9 Bit-Reversed Addressing

All Motorola DSPs feature a bit-reversed or inversecarry addressing mode to accelerate FFT calculations. When bit-reversed addressing is enabled, an additional temporary data buffer is required to hold normal order outputs since bit-reversing on the fly is not an in-place method of FFT calculation. In some situations, the memory space used is more critical than the time used. To reduce the requirement for space in the second buffer, an in-place bit-reversed method is preferred. However, there is a time penalty for space-saving since the in-place bit-reversal must be carried out after the FFT is done. Program BITREVTWD56.asm on the Motorola DSP bulletin board (Dr. BuB) presents an example of in-place bit-reverse for DSP56001/2. The algorithm that performs conversion from bit-reversed order to normal order addressing is presented in Figure 4-10.

```

normal_order=output_pointer;

bitrev_order=data_buffer;

for (i=0;i<N;i++) {

normal_order+;

bitrev_order+=N/2;

\* suppose bit reverse address available *\

if (normal_order< bitrev_order)

data[normal_order]=data[bitrev_order]

}</pre>

```

Figure 4-10 In-place bit-reversed to normal order conversion

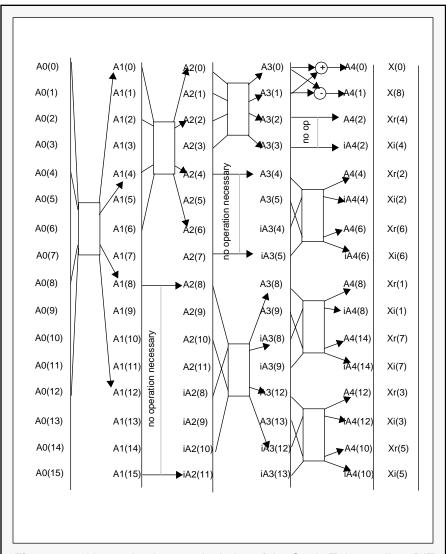

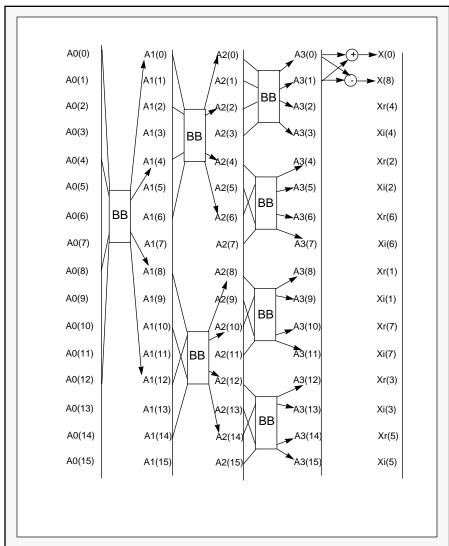

# 4.10 Implementation of a Radix-4 DIT FFT on DSP96002

In general, doubling the points in butterflies of FFT reduces the number of groups in each pass and the number of passes. A radix-4 butterfly accepts four complex inputs, thus, the number of butterflies in a pass is N/4, and the number of passes is  $log_4(N)$ . However, the number of instructions required in the radix-4 butterfly is three times that of the radix-2 butterfly. If the number of the instructions used in a radix-4 butterfly is four or more times than that of the radix-2's on a processor, there is really no advantage to adapting the radix-4 FFT on such a processor. Because the outputs or inputs of a radix-4 FFT might be digit-reversed order which is not being supported by any DSPs in the market. A software routine has to be used for converting digitreversed order data to the normal one.

4-26 MOTOROLA

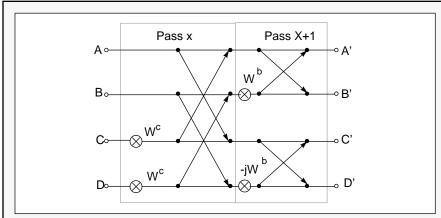

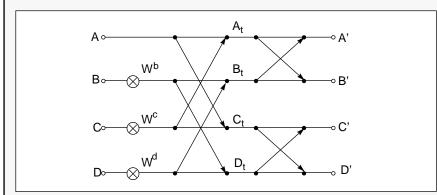

#### 4.10.1 Radix-4 DIT Butterfly Core

The butterfly equations for a radix-4 DIT FFT can be derived directly from two stages of radix-2 DIT butterflies, which are plotted in Figure 4-11. There are four butterflies with four twiddle factors involved in the calculation. In the first pass, pass x, two butterflies are in the same group (the twiddle factors for a group are identical). In the second pass, pass x+1, two adjacent butterflies share one twiddle factor but differ by -i. (See **SECTION 5.1 Optimization**).

**Figure 4-11** A flow diagram of two stages in a radix-2 DIT butterfly —four complex multiplications are involved in the computation.

There are four complex multiplications required which can be reduced to three by combining them into a radix-4 butterfly. Eqn. 4-5 shows two-stage radix-2 butterfly calculations.

$$A' = A + CW^{c} + (BW^{b} + DW^{c}W^{b})$$

$$B' = A + CW^{c} - (BW^{b} + DW^{c}W^{b})$$

$$C' = A - CW^{c} - j(BW^{b} - DW^{c}W^{b})$$

$$D' = A - CW^{c} + i(BW^{b} - DW^{c}W^{b})$$

Eqn. 4-5

Let  $W^bW^c = W^d$ , which gives us Eqn. 4-6. A new flow diagram for radix-4 DIT FFT results as shown in Figure 4-12. Three twiddle factors are needed.  $W_a$  and  $W_b$  originally come from the radix-2 DIT FFT;  $W_c$  is new for the radix-4 FFT. Note that the radix-4 DIT butterfly accesses 1/3 more twiddle factors than the radix-2 does.

$$A' = A + CW^{c} + (BW^{b} + DW^{d})$$

$$B' = A + CW^{c} - (BW^{b} + DW^{d})$$

$$C' = A - CW^{c} - j(BW^{b} - DW^{d})$$

$$D' = A - CW^{c} + j(BW^{b} - DW^{d})$$

Eqn. 4-6

Since each butterfly takes four complex inputs and generates four complex outputs, the number of groups in a pass is reduced to N/4. Also, the number of passes is reduced to log<sub>4</sub>(N). Theoretically, the lower boundary for radix-4 DIT FFT is:

$$TRIV \times N/4 + (log_4(N) - 1) \times N/4 \times BFLY$$

Twelve multiplications, fourteen additions, and eight subtractions are required for a radix-4 DIT butterfly, as Eqn. 4-7 illustrates.

4-28 MOTOROLA

**Figure 4-12** A flow diagram of a Radix-4 DIT butterfly. 12 multiplications and 22 additions or subtractions are required.

```

Atr = Ar + CrW_r^c - CiW_i^c

Ati = Ai + CrW_i^c + CiW_r^c

Btr = BrW_r^b + DrW_r^d - BiW_i^b - DiW_i^d

Bti = BrW_i^b + DrW_i^d + BiW_r^b + DW_r^d

Ctr \ = \ Ar - CrW_r^c + CiW_i^c

Cti = Ar - CiW_r^c - CrW_i^c

Dtr = BrW_r^b - DrW_r^d - BiW_i^b + DiW_i^d

Eqn. 4-7

Dti = BrW_i^b - DrW_i^d + BiW_r^b - DiW_r^d

Ar' = Atr + Btr

Ai' = Ati + Bti

Br' = Atr-Btr

Bi' = Ati - Bti

Cr' = Ctr + Dti

Ci' = Cti - Dtr

Dr' = Ctr-Dti

Di' = Cti + Dtr

```

```

;r0->A,r4->B, r1->C, r6->D;

;r1->A', r3->B', r5->C', r7'->D';

in0=n4=4,n4=2;

in2=n3=n5=n7=N/8.

x:(r4)+n4,d3.s y:,d5.s

move

x:(r4)+n4,d1.s

move

y:,d2.s

faddsub.s

d1,d3

x:(r0),d7.s

faddsub.s d5,d2

x:(r1),d0.s

d1.s,y:(r7)

faddsub.s

d3.s,d4.s

y:(r1)+n1,d1.s

d7,d0

faddsub.s

d7,d5

x:(r4),d6.s y:(r0)+n0,d3.s

faddsub.s

d0,d4

d7.s,x:(r3) y:(r4)+n4,d7.s

do

#N/4,_end_r4

faddsub.s

d3,d1

x:(r6)+,d9.sy:,d8.s

fmpy.s d6,d9,d5

d5.s,x:(r7)

fmpy

d7,d8,d3 faddsub.s

d1,d2

d4.s,x:(r5)

d3.s,d4.s

fadd.s

d5,d3

fmpy

d6,d8,d1

d0.s,x:(r2)+n2

d1.s,y:

fmpy.s d7,d9,d5

x:(r6)+,d9.s

y:,d8.s

fsub.s

d1,d5

x:(r4)+n4,d6.s

y:,d7.s

fmpy.s d6,d9,d1

y:(r7),d0.s

fmpy

d7,d8,d2 faddsub.s

d4,d0

d2.s,y:(r5)+n5

fmpy

d6,d8,d0 fadd.s

d2,d1

x:(r1),d6.s d0.s,y:(r7)+n7

d7,d9,d2 faddsub.s

d1,d3

x:(r6)+,d9.s

fmpy

y:,d8.s

d6,d9,d0 fsub.s

d0,d2

y:(r1)+n1,d7.s

fmpy

d3.s, d4.s d4.s, y:(r3)+n3

fmpy

d7,d8,d3 faddsub.s

d5,d2

d7,d9,d1 fadd.s

x:(r0),d7.s

fmpy

d3,d0

dl.s,y:(r7)

fmpy

d6,d8,d3 faddsub.s

d7,d0

faddsub.s

d7,d5

faddsub.s

d0,d4

d7.s,x:(r3)

y:(r4),d7.s

fsub.s

d3,d1

x:(r4)+n4,d6.sy:(r0)+n0,d3.s

_end_r4

faddsub.s

d3,d1

d5.s,x:(r7)

faddsub.s

d1,d2

y:(r7),d6.s

move

d0.s,x:(r2)

d1.s,y:

faddsub.s

d3,d6

d4.s,x:(r5)

d2.s,y:

d6.s,y:(r7)

move

move

d3.s,y:(r3)

```

Figure 4-13 Radix-4 DIT Butterfly takes 17 instructions on the DSP96002

4-30 MOTOROLA

For example, if there are 1024-point complex inputs, 8 x 256 + 4 x 256 x 14 =16,384 instructions may be required to improve performance by 11% if compared with 1024-point radix-2 DIT FFT. Here assume, TRIV = 8 and BFLY = 14 since eight ADD||SUB and six ADD instructions are theoretically required for such a butterfly calculation. One important fact is that BFLY, (the number of instruction cycles for butterfly calculation) in a radix-4 DIT FFT must be less than 16, otherwise, there is no advantage for using radix-4 over radix-2. Due to an insufficient number of operations code, FMPY// ADD//SUB instruction only works with destination registers D0 to D3 on the DSP96002.

## 4.10.2 Radix-4 DIF Butterfly Core

Using the same derivation, a radix-4 DIF butterfly can be obtained. Although the number of multiplications and additions is the same as the radix-4 DIT butterfly, the sequence of data appears differently. Eqn. 4-9 shows an expanded form of the radix-4 DIF butterfly. Eighteen instructions are used to code the radix-4 DIF butterfly.

$$\begin{split} & \text{Ar'} = \text{Ar} + \text{Br} + (\text{Dr} + \text{Cr}) \\ & \text{Ai'} = \text{Ai} + \text{Bi} + (\text{Di} + \text{Ci}) \\ & \text{Cr'} = [(\text{Ar} - \text{Br}) - (\text{Dr} - \text{Cr})]W_r^C + [(\text{Ai} - \text{Bi}) - (\text{Di} - \text{Ci})]W_i^C \\ & \text{Ci'} = [(\text{Ai} - \text{Bi}) - (\text{Di} - \text{Ci})]W_r^C - [(\text{Ar} - \text{Br}) - (\text{Dr} - \text{Cr})]W_i^C \\ & \text{Br'} = [(\text{Ar} + \text{Bi}) - (\text{Di} + \text{Cr})]W_r^b + [(\text{Ai} - \text{Br}) + (\text{Dr} - \text{Ci})]W_i^b \\ & \text{Bi'} = [(\text{Ai} - \text{Br}) + (\text{Dr} - \text{Ci})]W_r^b - [(\text{Ar} + \text{Bi}) - (\text{Di} + \text{Cr})]W_i^b \\ & \text{Dr'} = [(\text{Ar} - \text{Bi}) + (\text{Di} - \text{Cr})]W_r^d + [(\text{Ai} + \text{Bi}) - (\text{Dr} + \text{Ci})]W_i^d \\ & \text{Ci'} = [(\text{Ai} + \text{Br}) - (\text{Di} + \text{Cr})]W_r^d - [(\text{Ar} - \text{Bi}) + (\text{Di} - \text{Ci})]W_i^d \\ \end{split}$$

Eqn. 4-8

# 4.11 Inverse FFT

The Inverse Fast Fourier Transform (IFFT) is defined in Eqn. 4-9

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k)e^{j2\pi kn/N}$$

Eqn. 4-9

The differences between inverse FFTs and forward FFTs are in the scaling factor, N, and the conjugated twiddle factors. A common method of implementing the IFFT is to change the sign of the sine table values and use the FFT subroutine to get the IFFT. Alternatively, one can swap real and imaginary parts, use swapped inputs to the regular

4-32 MOTOROLA

FFT program, and then divide every real and imaginary output by N. Eqn. 4-10 and Eqn. 4-11 show the equality. Eqn. 4-10 shows the inverse FFT.

$$(A_r + jA_i)(W_r + jW_i) \; = \; (A_rW_r - A_iW_i) + j(A_iW_r + A_rW_i)$$

Eqn. 4-10

When swapping real and imaginary parts at the input and using forward FFT twiddle factors, we have the relation shown in Eqn. 4-11.

$$(A_i + jA_r)(W_r - jW_i) = j(A_rW_r - A_iW_i) + (A_iW_r + A_rW_i)$$

Eqn. 4-11

Eqn. 4-11 shows that the real part of the IFFT is in the space used for imaginary memory in the forward FFT and the imaginary part of the IFFT is in the real part of the forward FFT.

# **SECTION 5**

# Optimizing Performance of the FFT

# 5.1 Optimization

"Optimization saves ... 2067 instruction cycles which equals about 10% cycle time of the optimized code." Judging the performance of any program requires the consideration of both its time and space complexity. There is always a trade off between these two aspects. Time complexity indicates how fast an algorithm can be implemented on а specified microprocessor, while space complexity tells how much memory may be required. Optimization can either reduce memory requirement or minimize runtime of an algorithm. Since memory costs are continually decreasing, time optimization becomes more and more important.

One way to evaluate the time complexity of an algorithm is to compare its theoretical complexity, ideal implementation complexity, and practical complexity. Theoretical complexity refers to the number of additions and multiplications required by the given algorithm, independent of the microprocessor's architectures. This type of evaluating is only good for highlevel comparison among algorithms and does not reflect the real performance of the algorithm on a given microprocessor. Not surprisingly, an algorithm that retains a lower theoretical complexity has a higher ideal

implementation complexity. Ideal implementation complexity considers only the implementation of the core algorithm by the given microprocessor's instruction capabilities, such as available instruction type, addressing mode, parallel data move, etc. Ideal implementation complexity indicates the nonoverhead performance of a given algorithm on a microprocessor, and always provides an optimistic estimation of an algorithm's performance. Practical complexity denotes the ideal implementation complexity plus the structure overhead of the microprocessor. (Structure overhead includes all required instructions not associated with the core algorithm.) Moving pointers, setting up DO loops, jumps to subroutines, and conditional jumps are typical structure overhead in microprocessors.

By distinguishing the different complexities, one can easily determine which microprocessor is competent for each aspect, and which instruction or address mode is critical to the specific algorithms. Also, chip designers may derive clues from the complexity analysis for determining which instruction or address mode should be added to the next revision. For example, the DSP96002 supports FMPY||ADD||SUB — an instruction with two parallel moves. The theoretical complexity of a radix-2 butterfly is four real multiplications and six additions or subtractions. Thus, the ideal implementation complexity of a radix-2 FFT on the DSP96002 is four instruction cycles. If each butterfly needs an average of 0.25 instructions to set up a pointer or DO loop, etc., the practical complexity of radix-2 is 4.25 instructions. The ratio of ideal implementation com-

5-2 MOTOROLA

plexity to practical complexity reflects the efficiency of a microprocessor to perform a specific function. For example, the efficiency of the DSP96002 performing a radix-2 complex FFT could be:

efficiency =

$$\frac{\text{ideal implementation complexity}}{\text{practical complexity}} = \frac{4}{4.25} = 0.94$$

Eqn. 5-1

In other words, the structure overhead for this particular example is about 6%. For FFTs implemented on programmable DSPs, the structure overhead should be between 3% and 15%. If a DSP has structure overhead higher than 15%, it can not be called a DSP. If one claims a structure overhead lower than 3%, it is probably an application specific integrated circuit (ASIC).

# 5.1.1 Minimum Memory Requirement — In-Place Calculation