# RadHard-by-Design RHD5950 16-Channel Multiplexed 14-Bit Analog-to-Digital Converter

www.aeroflex.com/RHDseries January 14, 2016

### **FEATURES**

- □ Single power supply operation 5.0V or Dual power supply for 3.3V I/O

- □ Radiation performance

- Total dose: > 100 krad(Si); Dose rate = 50 300 rads(Si)/s

- ELDRS Immune

- SEL Immune > 100 MeV-cm<sup>2</sup>/mg - Neutron Displacement Damage > 10<sup>14</sup> neutrons/cm<sup>2</sup>

- □ 16-Channel Input Multiplexer

- □ Successive Approximation A-to-D

- □ Level Shifting Digital Output Drivers allow interfaces to 5.0 or 3.3 volt logic

- □ Tri-State digital outputs

- □ Power Down (Sleep) mode

- □ Single or continuous conversion

- □ 20us conversion period (20 clocks @ 1MHz Clock rate)

- □ Multiplexer address is latched on first clock rising edge of a cycle

- □ Busy and End-of-Conversion status outputs

- □ Full military temperature range

- □ Designed for aerospace and high reliability space applications

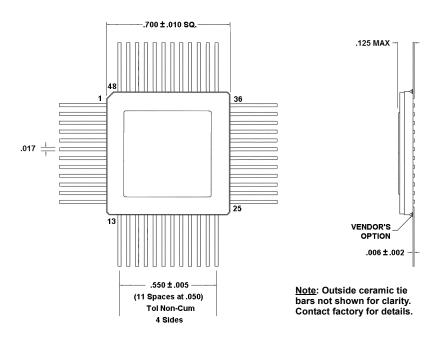

- □ Packaging Hermetic Ceramic

- 48 leads, 0.700"Sq x 0.125"Ht quad flat pack

- Weight 6 grams max

- ☐ Aeroflex Plainview's Radiation Hardness Assurance Plan is DLA Certified to MIL-PRF-38534, Appendix G.

### GENERAL DESCRIPTION

Aeroflex's RHD5950 is a radiation hardened, single supply, 16-Channel Multiplexed Analog-to-Digital converter in a 48-pin Ceramic Quad Flat Package. The RHD5950 design uses specific circuit topology and layout methods to mitigate total ionizing dose effects and single event latchup. It is guaranteed operational from -55°C to +125°C. Available screened in accordance with MIL-PRF-38534 Class K, the RHD5950 is ideal for demanding military and space applications.

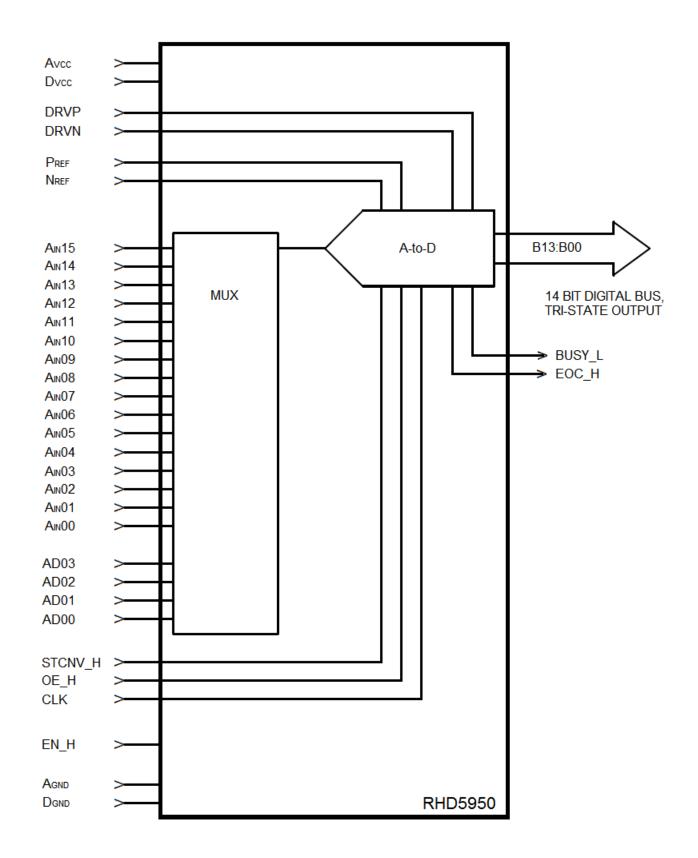

## **ORGANIZATION AND APPLICATION**

The RHD5950 takes 16 analog sensor signals and using 4 address inputs and an enable input, selects one of the 16 analog inputs and performs a 14-bit successive approximation analog-to-digital conversion in a nominal period of 20 clock cycles (20uS nominal). The 14-bit digital output has a tri-state control allowing the connection of multiple RHD5950s. This provides the ability to interface many sensor voltage readings to the digital processor data bus. The full-scale range is determined by reference input voltages. The input impedance of the reference/span terminals is typically a constant 4K ohms.

Gain compression will occur near either power supply extremes but can be avoided if the references are more than 200mV away from the respective supply terminals. The input span can be less than 4 volts at the expense of ultimate resolution

The analog channel's input impedance is primary capacitance (20pF typical). The input voltage charges a track-and-hold hold capacitor through transmission gates. The input bandwidth is determined by the slew rate of the hold amplifier and is adequate to allow input sampling in three clock periods (3uS nominal). The ultimate bandwidth is determined by the aperture uncertainty associated with the closing of the sample gate (approximately 5nS). The converter bandwidth is then determined by the sampling Nyquist frequency rather than the input signal; change rate (dv/dt) and the LSB weight in volts as would be the case if there were no sample-and-hold.

Start-Convert (STCNV\_H), Busy (BUSY\_L) and End-Of-Convert (EOC\_H) status and control lines are provided. The converter will operate in either continuous or single conversion modes. To operate in continuous mode, STCNV\_H should be tied to BUSY\_L. The digital output register changes at the end of a conversion and is latched when EOC\_H is asserted High. The output data will remain latched until the next conversion is complete and will be updated when EOC\_H is asserted High. The output circuitry operates from a voltage independent of the remainder of the chip such that I/O is compatible with digital systems from, less than 3.3 volts, to 5 volts.

The converter divides the reference voltage into 16 segments with a linear weighted resistor network. The voltage on any segment is passed to a linear 10-bit DAC for interpolation. The sampled input voltage is compared to the output of the two stage DAC for a 14-bit successive approximation conversion.

All inputs are protected to both power supply rails by semiconductor diodes. Inputs should be constrained to VCC +0.4 and GND-0.4 to avoid forward biasing protection paths.

The devices will not latch with SEU events to above 100 MeV-cm<sup>2</sup>/mg. Displacement damage environments to neutron fluence equivalents in the mid 10<sup>14</sup> neutrons per cm<sup>2</sup> range are readily tolerated. There is no sensitivity to low-dose rate (ELDRS) effects. SEU effects are application dependent.

Notes: - The STCNV H is a dynamic input (positive edge triggered) and should not be tied to a static voltage.

- The input signals should be low pass filtered to reduce high frequency noise

- If Sleep mode is enabled (EN\_H=0), when waking up (EN\_H=1), the unit has to complete an entire conversion cycle so the digital logic is in the proper state.

Ex. If using a 1MHz clock; after EN H=1 and 20us after STCNV H is applied.

**FIGURE 1: BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                 | Range                | Units |

|-------------------------------------------|----------------------|-------|

| Case Operating Temperature Range          | -55 to +125          | °C    |

| Storage Temperature Range                 | -65 to +150          | °C    |

| Junction Temperature                      | +150                 | °C    |

| Supply Voltage<br>Vcc - GND               | +7.0                 | V     |

| Input Voltage, PREF, NREF                 | Vcc +0.4<br>GND -0.4 | V     |

| Lead Temperature (soldering, 10 seconds)  | 300                  | °C    |

| Thermal Resistance, Junction to Case, ⊝jc | 2.0                  | °C/W  |

NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress rating only; functional operation beyond the "Operation Conditions" is not recommended and extended exposure beyond the "Operation Conditions" may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                           | Typical    | Units |

|--------|-------------------------------------|------------|-------|

| +Avcc  | Analog Power Supply Voltage         | 5.0        | V     |

| +Dvcc  | Digital Power Supply Voltage        | 5.0        | V     |

| DRVP   | Digital Output High Reference Level | 3.3 to 5.0 | V     |

| DRVN   | Digital Output Low Reference Level  | 0          | V     |

| PREF   | High Analog Reference Voltage       | 4.5        | V     |

| NREF   | Low Analog Reference Voltage        | 0.5        | V     |

## **ELECTRICAL PERFORMANCE CHARACTERISTICS**

(Tc = -55°C TO +125°C, +Avcc = +5.0 V, +Dvcc = +5.0 V, +DRVP = +5.0 V, unless stated otherwise)

| Parameter                                  | Symbol | Conditions                                        | Min    | Max   | Units |

|--------------------------------------------|--------|---------------------------------------------------|--------|-------|-------|

| Analog Supply Current Quiescent 1/         | Alccq  | VEN = DVCC, VOE = DVCC, CLK = DGND                | -      | 10    | mA    |

| Analog Supply Current Active 1/            | Alcca  | VEN = DVCC, VOE = DVCC                            | -      | 10    | mA    |

| Analog Supply Current Sleep 1/             | Alccs  | VEN = DGND, VOE = DGND                            | -      | 4     | mA    |

| Digital Supply Current Quiescent 1/        | DICCQ  | VEN = DVCC, VOE = DVCC, CLK = DGND                | -      | 1     | mA    |

| Digital Supply Current Active 1/           | DICCA  | VEN = DVCC, VOE = DVCC                            | -      | 2     | mA    |

| Digital Supply Current Sleep 1/            | Diccs  | VEN = DGND, VOE = DGND                            | -      | 1     | mA    |

| Digital Output Supply Current Quiescent 1/ | 05lccq | VEN = DVCC, VOE = DVCC, CLK = DGND,<br>CL = 50 pF | -      | 0.1   | mA    |

| Digital Output Supply Current Active 1/    | 05ICCA | VEN = DVCC, VOE = DVCC, CL = 50 pF                | -      | 1     | mA    |

| Digital Output Supply Current Sleep 1/     | 05ICCD | VEN = DVCC, VOE = DGND, CL = 50 pF                | -      | 1     | mA    |

| Full-scale Input Range 1/                  | Vin    |                                                   | VNREF  | VPREF | V     |

| Input Capacitance 2/                       | CIN    | Tc = +25°C                                        | -      | 50    | pF    |

| Analog Reference Impedance 1/              | ZREF   | PREF to NREF                                      | 2      | 6     | ΚΩ    |

| High Angles Reference Voltage              | VPREF  | DVRP = 5.0 V <u>1</u> /                           | VNREF  | 5.0   |       |

| High Analog Reference Voltage              | VPREF  | DVRP = 3.3 V <u>2</u> /                           | VINKER |       | V     |

| Low Analog Reference Voltage               | VNREF  | DVRP = 5.0 V <u>1</u> /                           | 0      | VPREF | V     |

| Low Analog Reference voltage               | VINKEF | DVRP = 3.3 V <u>2</u> /                           | 1 "    |       |       |

| Channel Isolation 2/                       | ISO    | Tc = +25°C                                        | 80     | -     | dB    |

## **ELECTRICAL PERFORMANCE CHARACTERISTICS**

(Tc = -55°C TO +125°C, +AVCC = +5.0 V, +DVCC = +5.0 V, +DRVP = +5.0 V, unless stated otherwise)

| Parameter                                                   | Symbol               | Conditions                                                          | Min             | Max  | Units |      |

|-------------------------------------------------------------|----------------------|---------------------------------------------------------------------|-----------------|------|-------|------|

| Integral Nonlinearity 1/                                    | INL                  | PREF-NREF = 4.0 V                                                   | -48             | 48   | LSBs  |      |

| Differential Nonlinearity 1/                                | DNL                  | PREF-NREF = 4.0 V                                                   | -8.2            | 8.2  | LSBs  |      |

| Offset Error 1/                                             | OE                   | PREF-NREF = 4.0 V                                                   |                 | -1   | 1     | %FSR |

| Gain Error 1/                                               | AE                   | PREF-NREF = 4.0 V                                                   |                 | -2   | 2     | %FSR |

| Clock Frequency 1/                                          | fc                   | PREF-NREF = 5.0 V                                                   |                 | -    | 1     | MHz  |

| Maximum Sampling Rate 2/                                    | fSAMPLE<br>(MAX)     | fc = 1 MHz, 20 clocks per conver                                    | sion            | -    | 50    | kSPS |

| High Input Leakage Current                                  | linlk <sub>hi</sub>  | Input under test = Avcc,                                            | +25°C           | -5   | 5     |      |

| (AIN00-AIN15) <u>1</u> / <u>3</u> /                         | IIINLIN              | Ven = DVcc                                                          | +125°C          | -50  | 50    | nA   |

| Low Input Leakage Current                                   | IINLK <sub>LO</sub>  | Input under test = AGND,                                            | +25°C           | -5   | 5     | IIA  |

| (AIN00-AIN15) <u>1</u> / <u>3</u> /                         | IIIVLKLO             | Ven = DVcc                                                          | +125°C          | -50  | 50    |      |

| Digital High Level Input Voltage                            | \ /···               | DVRP = 5.0 V <u>1</u> /                                             |                 | 3.5  | -     |      |

| EN_H, STCNV_H, OE_H, CLK, (AD00-AD03)                       | VIH                  | DVRP = 3.3 V <u>2</u> /                                             |                 | 2.31 | -     |      |

| Digital Low Level Input Voltage                             |                      | DVRP = 5.0 V <u>1</u> /                                             |                 | -    | 1.5   | · V  |

| EN_H, STCNV_H, OE_H, CLK, (AD00-AD03)                       | VIL                  | DVRP = 3.3 V <u>2</u> /                                             |                 | -    | 0.99  |      |

| Digital High Level Input Current                            | lıн                  | Digital input under test = 5.0 V<br>All other digital inputs = DGND | +25°C           | -5   | 5     | nA   |

| EN_H, STCNV_H, OE_H, CLK, (AD00-AD03) <u>1</u> / <u>3</u> / |                      |                                                                     | +125°C          | -50  | 50    |      |

| Digital Low Level Input Current                             | lıL                  | All digital inputs = DGND                                           | +25°C           | -5   | 5     |      |

| EN_H, STCNV_H, OE_H, CLK, (AD00-AD03) 1/ 3/                 |                      |                                                                     | +125°C          | -50  | 50    |      |

| Digital High Level Output Voltage                           |                      | DVRP = 5.0 V, VEN = DVCC, IOH = -4.0 mA                             |                 | 4.2  | -     | .,   |

| (B00-B13) <u>1</u> /                                        | Voн                  | DVRP = 3.3 V, VEN = DVCC, IOH =                                     | -4.0 mA         | 2.7  | -     | V    |

|                                                             |                      | DVRP = 5.0 V,<br>VEN = Dvcc,                                        | -55°C,<br>+25°C | -    | 0.6   | V    |

| Digital Low Level Output Voltage                            | Mai                  | IOL = +4.0 mA                                                       | +125°C          | -    | 8.0   |      |

| (B00-B13) <u>1</u> /                                        | Vol                  | DVRP = 3.3 V,<br>VEN = DVCC,<br>IOL = +4.0 mA                       | -55°C,<br>+25°C | -    | 0.6   |      |

|                                                             |                      |                                                                     | +125°C          | -    | 0.8   |      |

| Digital High Level Output Current                           | Іон                  | DVRP = 5.0 V, VEN = VIH                                             |                 | -    | -4.0  |      |

| (B00-B13) <u>1</u> /                                        | (SOURCE)             | DVRP = 3.3 V, VEN = VIH                                             | -               | -4.0 | mA    |      |

| Digital Low Level Output Current                            | IOL<br>(SINK)        | DVRP = 5.0 V, VEN = VIH                                             |                 | -    |       | 4.0  |

| (B00-B13) <u>1</u> /                                        |                      | DVRP = 3.3 V, VEN = VIH                                             | -               | 4.0  |       |      |

| High Output Leakage Current                                 | IOUT! K              | Vez. Baur                                                           | +25°C           | -5   | 5     |      |

| (B00-B13) <u>1</u> / <u>3</u> /                             | IOUTLK <sub>HI</sub> | VOE = DGND                                                          | +125°C          | -50  | 50    | nA   |

| · -/ = -                                                    | out Leakage Current  | No. Davis                                                           |                 |      |       |      |

| Low Output Leakage Current                                  | IOUTLK <sub>LO</sub> | Voe = Dgnd                                                          | +25°C           | -5   | 5     | ПА   |

Notes:

Specification derated to reflect Total Dose exposure to 100krad(Si) @ +25°C.

Not tested. Shall be guaranteed by design, characterization, or correlation to other test parameters.

These parameters for Tc = -55°C are guaranteed by design, characterization, or correlation to other test parameters.

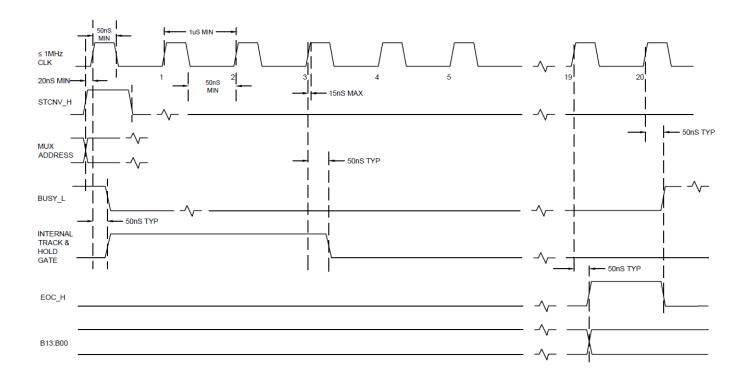

| Parameter            | Symbol | Conditions | Min | Тур | Max | Units |

|----------------------|--------|------------|-----|-----|-----|-------|

| STCNV_H to CLK       |        |            | 20  | -   | -   | ns    |

| ADDRESS to CLK Setup |        |            | 20  | ı   | -   | ns    |

| CLK to BUSY_L Low    |        |            | -   | 50  | -   | ns    |

| CLK to EOC_H High    |        |            | -   | 50  | -   | ns    |

| EOC_H to OUTPUT DATA |        |            | -   | 50  | -   | ns    |

| CLK to EOC_H Low     |        |            | -   | 50  | -   | ns    |

| CLK to BUSY_L High   |        |            | -   | 50  | -   | ns    |

| CLK Pulse Width      |        |            | 50  | 1   | -   | ns    |

| DATA Sampling Time   |        |            | 3   | -   | 5   | ns    |

**FIGURE 2: BASIC TIMING DIAGRAM**

## PACKAGE PIN-OUT AND SIGNAL DEFINITION

| Pin# | Signal  | Definition                                                          | Pin# | Signal | Definition                          |

|------|---------|---------------------------------------------------------------------|------|--------|-------------------------------------|

| 1    | AIN01   | Analog Multiplexer Input 01                                         | 25   | B11    | Digital Output 11                   |

| 2    | AIN00   | Analog Multiplexer Input 00                                         | 26   | B12    | Digital Output 12                   |

| 3    | NREF    | Low Analog Reference Voltage                                        | 27   | B13    | Digital Output 13                   |

| 4    | Avcc    | Analog Supply Voltage                                               | 28   | EOC_H  | End of Convert Output (Active High) |

| 5    | Dvcc    | Digital Supply Voltage                                              | 29   | BUSY_L | Busy Output (Active Low)            |

| 6    | AD03    | Multiplexer Address 03                                              | 30   | DRVN   | Digital Output Low Reference Level  |

| 7    | AD02    | Multiplexer Address 02                                              | 31   | DRVP   | Digital Output High Reference Level |

| 8    | AD01    | Multiplexer Address 01                                              | 32   | DGND   | Digital Supply Return               |

| 9    | AD00    | Multiplexer Address 00                                              | 33   | AGND   | Analog Supply Return                |

| 10   | STCNV_H | Start Convert: A Low-to-High transition starts the conversion cycle | 34   | PREF   | High Analog Reference Voltage       |

| 11   | EN_H    | A Low places part in SLEEP mode.<br>A High Enable the A2D converter | 35   | AIN15  | Analog Multiplexer Input 15         |

| 12   | OE_H    | A Low Tristates the outputs.<br>A High Enables the outputs          | 36   | AIN14  | Analog Multiplexer Input 14         |

| 13   | CLK     | Clock Input                                                         | 37   | AIN13  | Analog Multiplexer Input 13         |

| 14   | B00     | Digital Output 00                                                   | 38   | AIN12  | Analog Multiplexer Input 12         |

| 15   | B01     | Digital Output 01                                                   | 39   | AIN11  | Analog Multiplexer Input 11         |

| 16   | B02     | Digital Output 02                                                   | 40   | AIN10  | Analog Multiplexer Input 10         |

| 17   | B03     | Digital Output 03                                                   | 41   | AIN09  | Analog Multiplexer Input 09         |

| 18   | B04     | Digital Output 04                                                   | 42   | AIN08  | Analog Multiplexer Input 08         |

| 19   | B05     | Digital Output 05                                                   | 43   | AIN07  | Analog Multiplexer Input 07         |

| 20   | B06     | Digital Output 06                                                   | 44   | AIN06  | Analog Multiplexer Input 06         |

| 21   | B07     | Digital Output 07                                                   | 45   | AIN05  | Analog Multiplexer Input 05         |

| 22   | B08     | Digital Output 08                                                   | 46   | AIN04  | Analog Multiplexer Input 04         |

| 23   | B09     | Digital Output 09                                                   | 47   | AIN03  | Analog Multiplexer Input 03         |

| 24   | B10     | Digital Output 10                                                   | 48   | AIN02  | Analog Multiplexer Input 02         |

## **TRUTH TABLE (AIN00 – AIN15)**

| <b>A3</b> | A2 | <b>A1</b> | Α0 | EN | "ON" CHANNEL |

|-----------|----|-----------|----|----|--------------|

| Х         | Х  | Х         | Х  | L  | NONE         |

| L         | L  | L         | L  | Н  | AIN0         |

| L         | L  | L         | Н  | Н  | AIN1         |

| L         | L  | Н         | L  | Н  | AIN2         |

| L         | L  | Н         | Н  | Н  | AIN3         |

| L         | Н  | L         | L  | Н  | AIN4         |

| L         | Н  | L         | Н  | Н  | AIN5         |

| L         | Н  | Н         | L  | Н  | AIN6         |

| L         | Н  | Н         | Н  | Н  | AIN7         |

| Н         | L  | L         | L  | Н  | AIN8         |

| Н         | L  | L         | Н  | Н  | AIN9         |

| Н         | L  | Н         | L  | Н  | AIN10        |

| Н         | L  | Н         | Н  | Н  | AIN11        |

| Н         | Н  | L         | L  | Н  | AIN12        |

| Н         | Н  | L         | Н  | Н  | AIN13        |

| Н         | Н  | Н         | L  | Н  | AIN14        |

| Н         | Н  | Н         | Н  | Н  | AIN15        |

### ORDERING INFORMATION

| Model          | DLA SMD#        | Screening                                                                                                                                 | Package         |

|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| RHD5950-7      | -               | Commercial Flow, +25°C testing only                                                                                                       |                 |

| RHD5950-S      | -               | Military Temperature, -55°C to +125°C<br>Screened in accordance with the individual Test Methods<br>of MIL-STD-883 for Space Applications | 48-lead<br>COFP |

| RHD5950-201-1S | 5962-1220301KXC | In accordance with DLA SMD                                                                                                                | <b>3</b>        |

| RHD5950-901-1S | 5962R1220301KXC | In accordance with DLA Certified RHA Program Plan to RHA Level "R", 100krads(Si)                                                          |                 |

**FIGURE 3: PACKAGE OUTLINE**

### EXPORT CONTROL:

This product is controlled for export under the Export Administration Regulations (EAR), 15 CFR Parts 730-774.

A license from the Department of Commerce may be required prior to the export of this product from the United States.

www.aeroflex.com/HiRel info-ams@aeroflex.com

#### Datasheet Definitions:

Advanced Product in Development

Preliminary Shipping Non-Flight Prototypes

Datasheet Shipping QML and Reduced HiRel

Aeroflex Plainview, Inc. reserves the right to make changes to any products and services described herein at any time without notice. Consult Aeroflex or an authorized sales representative to verify that the information in this data sheet is current before using this product. Aeroflex does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by Aeroflex; nor does the purchase, lease, or use of a product or service from Aeroflex convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of Aeroflex or of third parties.

Our passion for performance is defined by three attributes.

Solution-Minded

Performance-Driven

Customer-Focused