# Standard Products UT7R2XLR816 Clock Network Manager

Datasheet November 2015

The most important thing we build is trust

| FE | ATURES:                                                                        |

|----|--------------------------------------------------------------------------------|

|    | +3.3V Core Power Supply                                                        |

|    | Independent power supply for each clock bank                                   |

|    | - Power supply range from +2.25V to +3.6V                                      |

|    | 8 Output clock banks with flexible I/O signaling                               |

|    | - Up to 16 LVCMOS3.3 outputs with                                              |

|    | 12mA slew-rate limited, break-before-make, buffers, or                         |

|    | - Up to 16 LVCMOS2.5 outputs with                                              |

|    | 8mA slew-rate limited, break-before-make, buffers, or                          |

|    | - Up to 8 standard drive LVDS outputs                                          |

|    | Input clock multiplication of any integer from 1 - 32                          |

|    | PLL Operation                                                                  |

|    | - Low frequency range: 24MHz to 50MHz                                          |

|    | - Mid frequency range: 48MHz to 100MHz                                         |

|    | - High frequency range: 96MHz to 200MHz                                        |

|    | Input reference clock signaling and control:                                   |

|    | - LVCMOS3.3/LVTTL (Cold-Spared),                                               |

|    | LVDS (Cold-Spared), &                                                          |

|    | Parallel Resonant Quartz Crystal                                               |

|    | - Reference input divide-by-1 or divide-by-2                                   |

| _  | - Input frequency range from 2MHz to 200MHz                                    |

|    | Dedicated feedback Input/Output module                                         |

|    | - Independent feedback power supply (+3.0V to +3.6V)                           |

|    | - 1-to-32 divider options with/without inverting                               |

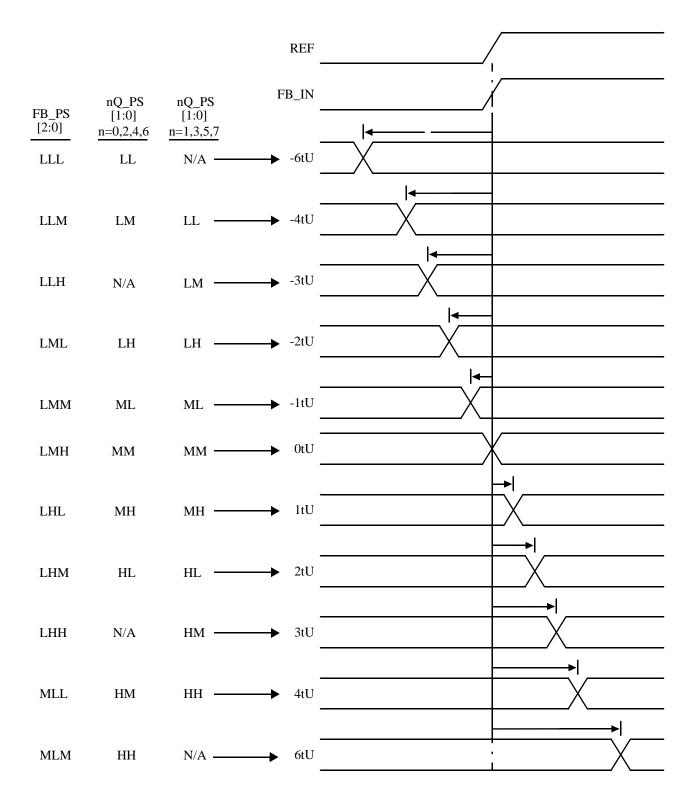

|    | - Phase control -6, -4, -3, -2, -1, 0, 1, 2, 3, 4, 6 tU                        |

|    | - FB_IN: Not affected by RST/DIV state - FB_OUT = LOW when RST/DIV=LOW (RESET) |

|    | - No Synchronous Output Enable (sOE) control in order to maintai               |

|    | PLL lock                                                                       |

|    | Output clock bank signaling and control:                                       |

| _  | - Output frequency range from 750KHz to 200MHz                                 |

|    | - 1-to-32 divider options with/without inverting                               |

|    | - Odd bank phase control -4, -3, -2, -1, 0, 1, 2, 3, 4 tU                      |

|    | - Even bank phase control -6, -4, -2, -1, 0, 1, 2, 4, 6 tU                     |

|    | - Disable HIGH, LOW, or HIGH-Z (See Table 1, page 6)                           |

|    | - Synchronous Output Enable (sOE) control                                      |

|    | - Outputs (0-7)Q0, 1 = HIGH-Z/Tri-state when RST/DIV= LOW                      |

|    | (RESET)                                                                        |

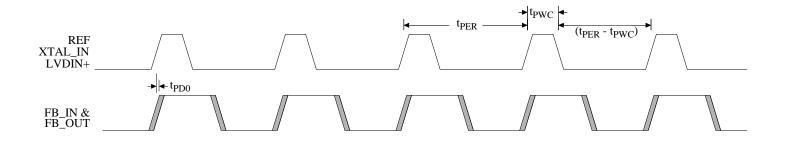

|    | Guaranteed reference input to output edge                                      |

|    | synchronization                                                                |

|    | Low inherent output bank skew (e.g. $SKEW = 0*tU$ )                            |

|    | - < 50ps intrabank skew (typical)                                              |

|    | - < 100ps interbank skew without dividing or inverting (typ)                   |

|    | - < 250ps interbank skew across divided or inverted banks (typ)                |

|    | Power dissipation can be reduced by powering down unused                       |

|    | output banks (See Note 2, page 37)                                             |

| Temperature range:                                   |

|------------------------------------------------------|

| - Commercial: 0°C to +70°C                           |

| - Industrial: -40°C to +85°C                         |

| - HiRel: -55°C to +125°C                             |

| Operational environment:                             |

| - Total-dose: 100 krad (Si)                          |

| - SEL Immune to a LET of 109 MeV-cm <sup>2</sup> /mg |

| - SEU Immune to a LET of 109 MeV-cm <sup>2</sup> /mg |

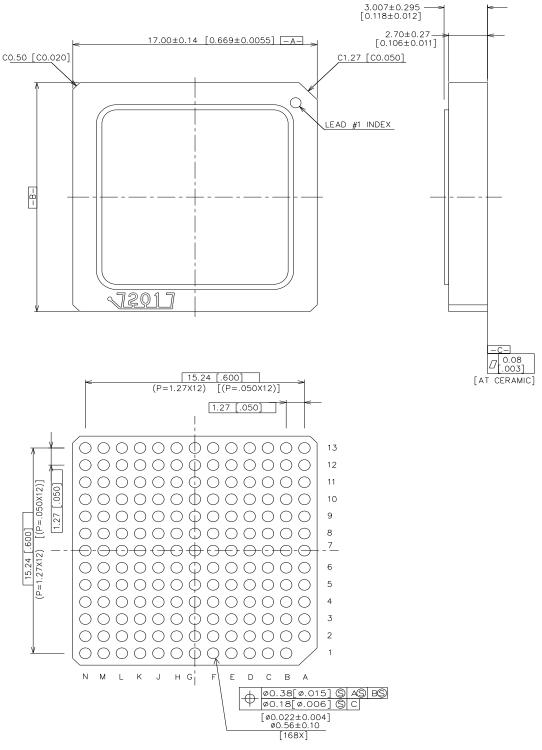

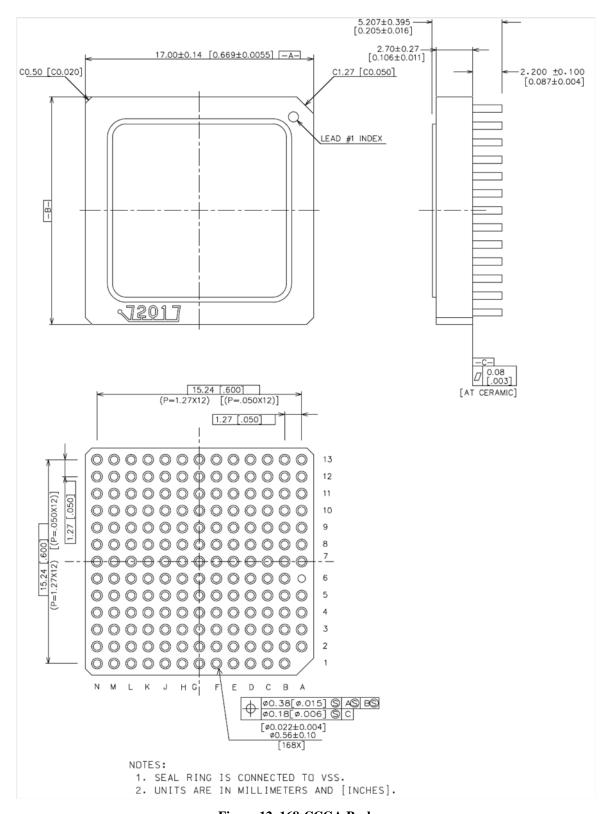

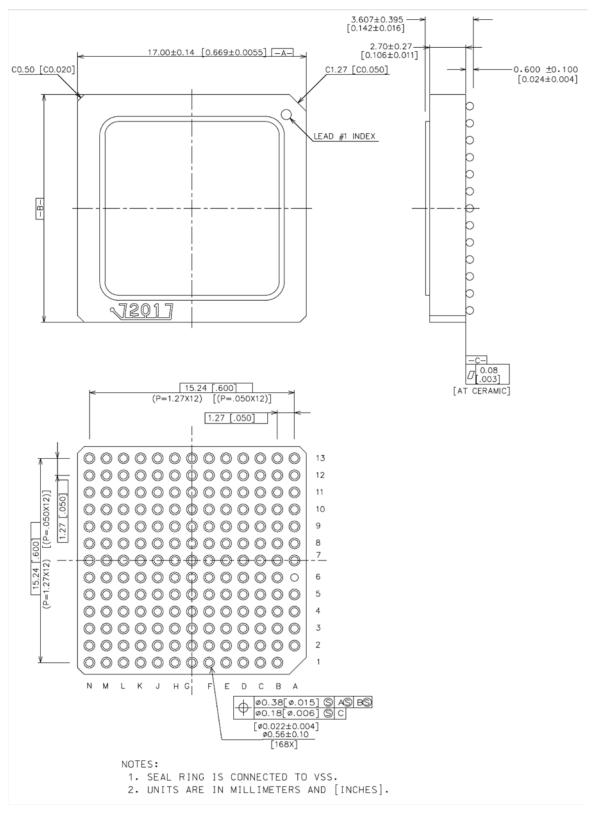

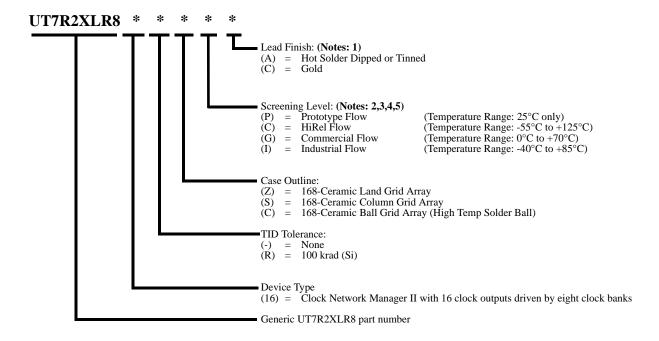

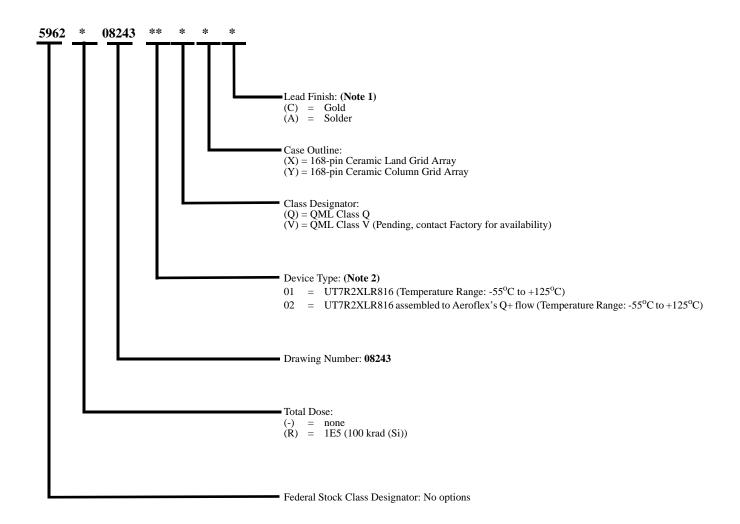

| Packaging options (1.27mm pitch, 17mm sq. body):     |

| - 168-CLGA                                           |

| - 168-CBGA                                           |

| - 168-CCGA                                           |

| Standard Microcircuit Drawing 5962-08243             |

| - QML Q and Q+                                       |

| Applications                                         |

| - High altitude avionics                             |

| - X-ray Cargo Scanners                               |

| - Test and Measurement                               |

| - Networking, telecommunications and mass storage    |

|                                                      |

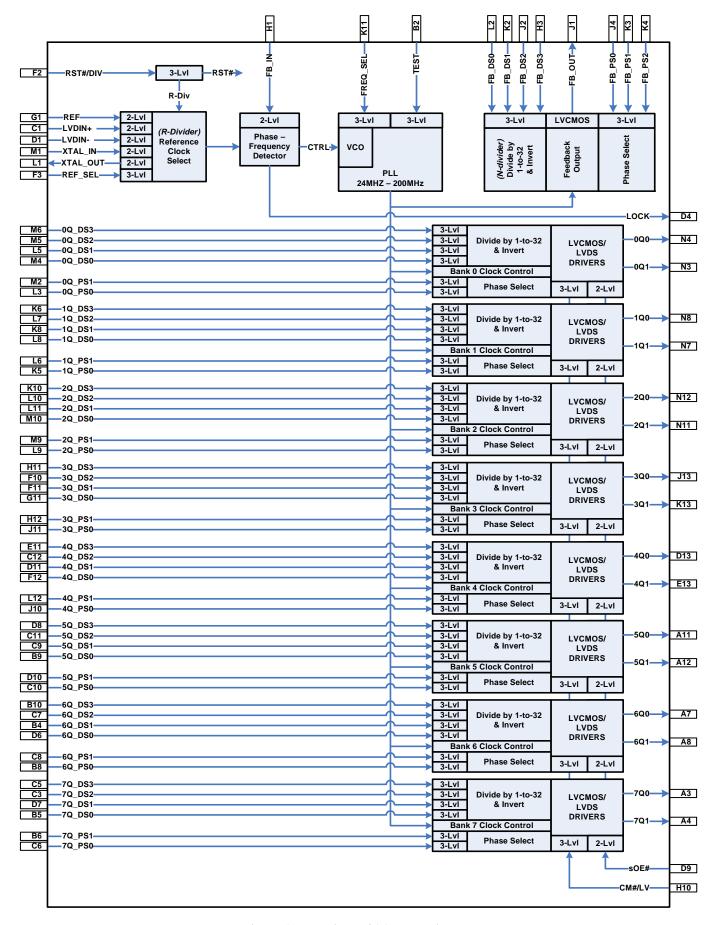

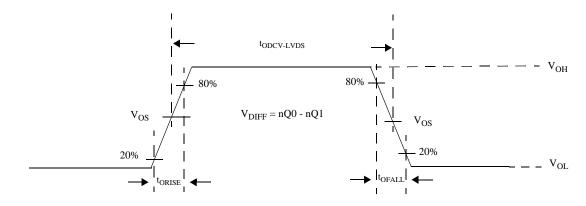

The UT7R2XLR816 is a low voltage, low power, clock network manager. The device features 16-outputs in 8 banks of 2. Independent power supplies for each bank (+2.25V to +3.6V) give the user great flexibility in multi- voltage systems. Outputs can be configured as LVCMOS (2.5V/8mA or 3.3V/12mA) or standard LVDS pairs. Independent output bank division and

**INTRODUCTION:**

phase skewing empower the system designer to optimize output phase and frequency relationships throughout a clock network.

The skew controls enable outputs to lead or lag the reference clock while the ternary output divider control can divide the PLL oscillator frequency by any integer from 1 to 32 before driving the clock out of the desired bank. Regardless of output divider settings, input and output clock edges are synchronized at start-up and whenever the device is removed from power down mode. Power down mode is controlled by the  $\overline{RST}/DIV$  ternany input which also controls input division of the reference clock. Time units for skew control ( $t_U$ ) are 22.5° of the clock cycle for low and mid frequency oscillators and 45° of the clock cycle for the high frequency oscillator.

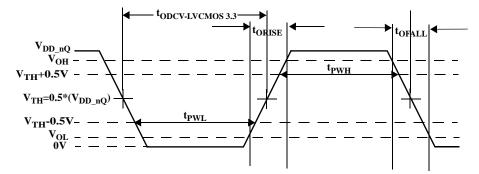

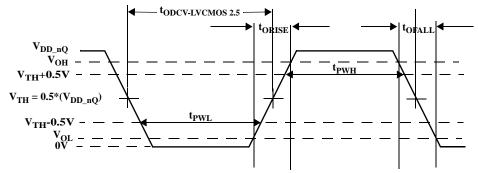

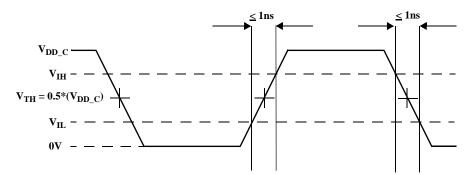

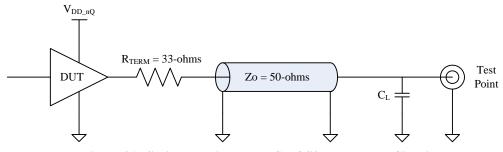

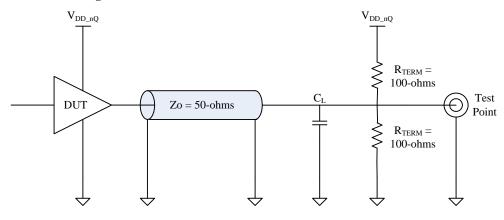

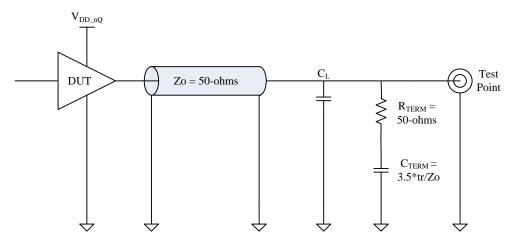

Slew rate optimization of outputs is determined by the PLL oscillator range selected and thus is controlled by the FREQ\_SEL input. Output rise times decrease as higher frequency range oscillators are selected. The input reference clock can be LVCMOS/LVTTL/ LVDS or a quartz crystal. The LVCMOS/LVTTL and LVDS inputs are cold-spared. Input reference frequencies can range from 2MHz to 200MHz. Using the RST/DIV pin and FB\_DS[3:0] feedback divider settings for the reference clock can be multiplied by 0.5x-32x in steps of 0.5 through a multiplication factor of 16 and integer steps for multiplication factors 17 through 32.

To provide further clock network optimization, the feedback output bank includes independent skew and division control. PLL lock is identified by the active high LOCK signal. LOCK will only become true when the REFERENCE and FB\_IN clocks are stable and aligned to within  $t_{\rm LOCKRES}$ , which is variable based on the state of the FREQ\_SEL pin. At all other times, LOCK will remain LOW.

Clock outputs are deterministic in that if either the reference input clock or feedback clock are absent, the outputs will oscillate at a frequency near the midpoint of the selected PLL operating range. Test modes are available for user diagnostics. The TEST ternary input enables the test modes. When TEST is low, normal operation occurs. Floating the TEST pin to a mid-range value disables the PLL oscillators and drives the clock output banks with the REF clock input. Setting TEST high disables the PLL oscillators and drives the clock output banks with the FB\_IN input.

Figure 1. UT7R2XLR816 Block Diagram

## 1.0 Functional Description

The UT7R2XLR816, clock network manager, has an array of special features designed to overcome many of the clock management and clock distribution challenges common in today's high-performance electronic systems. This section of the datasheet provides an overview of the primary features within and is intended to acquaint the designer with their basic capabilities.

Although discussed in more detail below, the user should understand that many features within the UT7R2XLR816 are selected by ternary control signals. These ternary controls recognize three separate logic levels on a single pin. The L(ow) state means that the control input pin is driven below the  $V_{ILL}$  level specified in the DC electrical table of this datasheet. Conversely, a H(igh) means that the control input is driven above the  $V_{IHH}$  voltage described in the DC electrical table. While a M(id) state requires that the input pin be floated, allowing the internal resistor divider network to place the pin into a level compliant with the  $V_{IMM}$  voltage listed in the DC electrical table, or externally driven/biased to the  $V_{IMM}$  level.

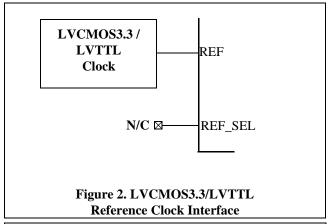

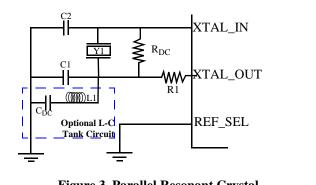

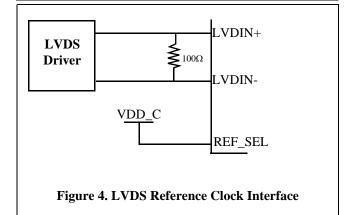

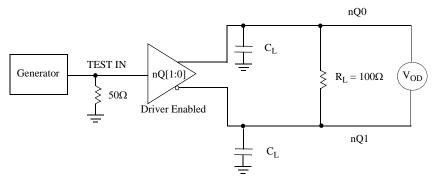

#### 1.1 Reference Clocks

The UT7R2XLR816 is capable of receiving its reference clock from one of three sources. The REF input allows for a single ended, LVTTL/LVCMOS clock source. The LVDIN+ and LVDIN- pins combine to receive an LVDS reference clock. The LVDIN+ should be driven by the positive half of the LVDS clock signal while the LVDIN- should be driven by the negative half of the LVDS clock signal. A  $100\Omega$ terminating resistor should be connected directly between the LVDIN+ and LVDIN- terminals. Finally, the XTAL IN and XTAL OUT terminals provide for a quartz crystal resonator reference clock input. The XTAL IN pin is the input to the on-chip pierce oscillator and should be connected directly to one side of an external quartz crystal that is tuned to operate in the parallel resonance mode. The XTAL OUT pin drives out the 180° phase shifted version of the reference clock received on XTAL\_IN. The XTAL OUT pin should drive the other end of the external quartz crystal resonator circuit. Reference figure 3 for an example quartz crystal oscillator circuit.

The REF, LVDIN+ and LVDIN- inputs are cold-spared. The cold-sparing capability of these reference pins make them ideal for receiving an off-board clock source that may be active while the UT7R2XLR816 is unpowered.

The UT7R2XLR816 provides a ternary reference select pin (REF\_SEL) that is used to control which of the three available clock sources the UT7R2XLR816 will use as its

timing reference. Since REF\_SEL ensures that only one reference source can drive the internal circuitry of the UT7R2XLR816 the remaining two clock sources may be driven simultaneously allowing the REF\_SEL pin to select between these reference sources. As mentioned above, REF\_SEL is a ternary, or three level input. Setting REF\_SEL L(ow) selects the XTAL\_IN/XTAL\_OUT crystal resonator source. Placing REF\_SEL into a M(id) level (left floating), sets the REF input as the UT7R2XLR816 reference clock source. Finally, driving REF\_SEL H(igh), enables the LVDS (LVDIN+/LVDIN-) clock source. These available REF\_SEL configurations are shown in figures 2, 3 and 4.

#### 1.2 Feedback Clock

The UT7R2XLR816 contains a dedicated feedback I/O module that is completely separate from the eight (8) output clock banks. The FB\_IN feedback input can be driven directly from the FB\_OUT pin, or from a digital circuit having the FB\_OUT pin as its source.

The FB\_IN signal connects to the internal Phase-Frequency Detector (PFD), which compares the FB\_IN signal with the clock reference source as selected by the REF\_SEL control. Phase shifts associated with board trace delays from routing, in-line circuitry, or intentional phase skewing within the feedback path are adjusted by the PFD to advance or delay the Phase-Locked Loop (PLL), as necessary, to ensure that the clock arriving at FB\_IN is phase aligned with the selected reference clock source.

The FB\_OUT is an LVCMOS3 output signal driven by the PLL. As discussed in Tables 1 and 2, the frequency and phase of the FB\_OUT signal may be adjusted by the FB\_DS[3:0] output divider settings and the FB\_PS[2:0] phase selection settings, respectively. Both pin groups, FB\_DS[3:0] and FB\_PS[2:0], are ternary inputs. The FB\_DS[3:0] settings are used to multiply the frequency of the internal PLL by dividing the frequency of the FB\_OUT signal.

FB\_OUT may be divided by any integer from 1 to 32, as-well-as inverted following the division operation. Inversion provides a 180° phase shift of the PLL from the incoming reference source, effectively synchronizing the PLL to the opposite edge of the reference clock. To ensure stable locking of the PLL and to free the output clock banks to drive the system clock, FB\_OUT should always be used as the originating clock source for the FB\_IN pin.

The FB\_PS[2:0] feedback phase selection pins allow the FB\_OUT signal to be phase shifted by -6, -4, -3, -2, -1, 0, 1,

- 2, 3, 4, or 6 tu (time units). The value of tu is determined by the FREQ\_SEL setting and the PLL's operating frequency. Examples of tu calculation are shown in Equation 1 and Table 5. Phase shifting FB\_OUT has the effect of advancing or delaying the PLL and, by extension, the nominal phase of all output clock banks. A positive phase shift (i.e. delay) in FB\_OUT advances the PLL and clock output banks so they lead the reference clock by the same phase shift amount. Conversely, a negative shift (i.e. advancement) of FB\_OUT causes the PLL and output clock banks to lag the reference clock source by the same amount of phase shift.

- 1.3 Phase-Locked Loop (PLL) and Frequency Generation The UT7R2XLR816's PLL circuitry consists of the previously mentioned reference and feedback input clock sources, a Phase–Frequency Detector (PFD), and a Voltage-Controlled Oscillator (VCO). The voltage controlled oscillator consists of three separate oscillators that are optimized to run in three specific frequency bands. The ternary FREQ\_SEL input is used to select the appropriate VCO based upon the nominal PLL frequency required by the application. The nominal PLL frequency range selected by FREQ\_SEL are 24 – 50MHz (FREQ\_SEL=Low), 48 – 100MHz (FREQ\_SEL=Mid) and 96 – 200MHz (FREQ\_SEL=High).

The UT7R2XLR816 includes an internal reset signal to ensure that the selected VCO starts-up and the PLL establishes lock with the stable reference clock sources whenever power is applied to the device, or the device is dynamically reconfigured to select a different VCO. However, Aeroflex recommends that dynamic reconfiguration be performed while the device is held in RESET (e.g. RST/DIV=Low) to ensure a smooth re-start and avoid uncontrolled behavior from the device during the reconfiguration process.

An additional start-up feature provided by the UT7R2XLR816 is the inclusion of a PLL pre-charge circuit that places the selected VCO into a mid-band frequency of operation in the event that either one, or both, of the reference and feedback clocks are removed or drop to a frequency below f<sub>REFDET</sub>. The intent of this feature is to ensure that the PLL demonstrates deterministic behavior if the device is out of reset and the PFD does not receive valid, stable, input clocks. By controlling the active VCO when the PFD does not have a valid set of input clocks to compare ensures that any active output clock bank oscillates at a manageable frequency for downstream electronics. It is also recommended that the sOE pin be used in conjunction with the UT7R2XLR816 startup by disabling the output banks

until the device has completed its PLL locktime (tLOCK) and the LOCK output is stable high.

When valid, stable, reference and feedback clocks are available to the PFD, it will override the pre-charge circuitry and begin to control the VCO. Although the PFD works to maintain frequency and phase alignment between the reference and FB IN to an ideal Ons difference, it will inform the user that the PLL is locked onto the incoming clocks when they are phase aligned to within 2ns (typical) for the low and mid VCO selections, and within 1.5ns (typical) for the high VCO. When this condition is met, the UT7R2XLR816 will drive the LOCK output high, indicating to the system the PLL is locked. When the LOCK pin is LOW, the PLL is not locked and the clock outputs may not be stable or synchronized to the reference clock source. The LOCK will de-assert LOW when the reference clock and the FB IN are separated by greater than the defined alignments, unless the device is reset.

## 2.0 DEVICE CONFIGURATION:

# Table 1: Output Divider Settings FB (N-factor) & Bank 0Q through Bank 7Q ( $M_{nO}$ -factor)

|         |                   | 1       | 1                 | ~       | <i>'</i>          |

|---------|-------------------|---------|-------------------|---------|-------------------|

| DS[3:0] | Output<br>Divider | DS[3:0] | Output<br>Divider | DS[3:0] | Output<br>Divider |

| LLLL    | 1                 | MLLL    | 28                | HLLL    | 23+INV            |

| LLLM    | 2                 | MLLM    | 29                | HLLM    | 24+INV            |

| LLLH    | 3                 | MLLH    | 30                | HLLH    | 25+INV            |

| LLML    | 4                 | MLML    | 31                | HLML    | 26+INV            |

| LLMM    | 5                 | MLMM    | 32                | HLMM    | 27+INV            |

| LLMH    | 6                 | MLMH    | 1+INV             | HLMH    | 28+INV            |

| LLHL    | 7                 | MLHL    | 2+INV             | HLHL    | 29+INV            |

| LLHM    | 8                 | MLHM    | 3+INV             | HLHM    | 30+INV            |

| LLHH    | 9                 | MLHH    | 4+INV             | HLHH    | 31+INV            |

| LMLL    | 10                | MMLL    | 5+INV             | HMLL    | 32+INV            |

| LMLM    | 11                | MMLM    | 6+INV             | HMLM    | Note 1            |

| LMLH    | 12                | MMLH    | 7+INV             | HMLH    | Note 1            |

| LMML    | 13                | MMML    | 8+INV             | HMML    | Note 1            |

| LMMM    | 14                | MMMM    | 9+INV             | HMMM    | Note 1            |

| LMMH    | 15                | MMMH    | 10+INV            | НММН    | Note 1            |

| LMHL    | 16                | MMHL    | 11+INV            | HMHL    | Note 1            |

| LMHM    | 17                | MMHM    | 12+INV            | НМНМ    | Note 1            |

| LMHH    | 18                | ММНН    | 13+INV            | НМНН    | Note 1            |

| LHLL    | 19                | MHLL    | 14+INV            | HHLL    | DIS_LO<br>Note 2  |

| LHLM    | 20                | MHLM    | 15+INV            | HHLM    | Note 1            |

| LHLH    | 21                | MHLH    | 16+INV            | HHLH    | DIS_HI<br>Note 2  |

| LHML    | 22                | MHML    | 17+INV            | HHML    | Note 1            |

| LHMM    | 23                | MHMM    | 18+INV            | ннмм    | Note 1            |

| LHMH    | 24                | МНМН    | 19+INV            | ННМН    | Note 1            |

| LHHL    | 25                | MHHL    | 20+INV            | HHHL    | Note 1            |

| LHHM    | 26                | МННМ    | 21+INV            | НННМ    | Note 1            |

| LHHH    | 27                | МННН    | 22+INV            | нннн    | HI-Z<br>Note 2    |

### Notes:

Table 2: Feedback Bank or Output Bank Phase Select Setting<sup>1</sup>

| FB_PS [2:0] | Skew<br>FB         | nQ_PS<br>[1:0] | Skew<br>EVEN<br>Banks | Skew<br>ODD<br>Banks |

|-------------|--------------------|----------------|-----------------------|----------------------|

| LLL         | -6t <sub>U</sub>   | LL             | -6t <sub>U</sub>      | -4 $t_{ m U}$        |

| LLM         | -4t <sub>U</sub>   | LM             | -4t <sub>U</sub>      | -3t <sub>U</sub>     |

| LLH         | -3t <sub>U</sub>   | LH             | -2t <sub>U</sub>      | -2t <sub>U</sub>     |

| LML         | -2t <sub>U</sub>   | ML             | -1t <sub>U</sub>      | -1 $t_{ m U}$        |

| LMM         | -1t <sub>U</sub>   | MM             | Zero Skew             | Zero Skew            |

| LMH         | Zero Skew          | МН             | +1t <sub>U</sub>      | +1t <sub>U</sub>     |

| LHL         | +1t <sub>U</sub>   | HL             | +2t <sub>U</sub>      | +2t <sub>U</sub>     |

| LHM         | +2t <sub>U</sub>   | НМ             | +4t <sub>U</sub>      | +3t <sub>U</sub>     |

| LHH         | $+3t_{\mathrm{U}}$ | НН             | +6t <sub>U</sub>      | +4t <sub>U</sub>     |

| MLL         | +4t <sub>U</sub>   |                |                       |                      |

| MLM         | +6t <sub>U</sub>   |                |                       |                      |

| MLH         | Note 2             |                |                       |                      |

| MML         | Note 2             |                |                       |                      |

| MMM         | Note 2             |                |                       |                      |

| MMH         | Note 2             |                |                       |                      |

| MHL         | Note 2             |                |                       |                      |

| MHM         | Note 2             |                |                       |                      |

| МНН         | Note 2             |                |                       |                      |

| HLL         | Note 2             |                |                       |                      |

| HLM         | Note 2             |                |                       |                      |

| HLH         | Note 2             |                |                       |                      |

| HML         | Note 2             |                |                       |                      |

| HMM         | Note 2             |                |                       |                      |

| НМН         | Note 2             |                |                       |                      |

| HHL         | Note 2             |                |                       |                      |

| ННМ         | Note 2             |                |                       |                      |

| ннн         | Note 2             |                |                       |                      |

- 1. Skew accuracy is within +/- 300ps of  $n\mbox{*t}_U$  where "n" is the selected number of skew steps.

- These skew settings are for engineering modes only and will default to the ZERO SKEW state when selected by a user.

<sup>1.</sup> These DS[3:0] settings are for engineering modes only and will default to the DS[3:0] = LLLL state when selected by a user.

<sup>2.</sup> These DS[3:0] settings are not available on the FB\_OUT clock. If selected by the user, the FB\_OUT clock will default to the DS[3:0] = LLLL state.

**Table 3: Calculating Output Frequency Settings** <sup>1, 2</sup>

|                                                   | <b>Output Frequency</b>  |                        |  |

|---------------------------------------------------|--------------------------|------------------------|--|

| PLL Operating<br>Frequency<br>(f <sub>PLL</sub> ) | FB_OUT                   | nQ[1:0]                |  |

| (N/R) * f <sub>REFERENCE</sub>                    | (1/N) * f <sub>PLL</sub> | $(1/M_{nQ}) * f_{PLL}$ |  |

#### Notes:

- Reference Table 1 for N-factor and MnQ-factor. Reference RST/DIV pin description for R-factor.

- The N-factor, R-factor, and Reference frequency should be selected such that the PLL oscillates within a range defined by the Frequency Selection shown in Table 4.

**Table 4: Frequency Range Select**

| FREQ_SEL | Nominal PLL<br>Frequency Range (f <sub>PLL</sub> ) |

|----------|----------------------------------------------------|

| L        | 24 MHz to 50 MHz                                   |

| M        | 48 MHz to 100 MHz                                  |

| Н        | 96 MHz to 200 MHz                                  |

Selectable output skew is in discrete increments of time unit  $(t_U)$ . The value of  $t_U$  is determined by the FREQ\_SEL setting and the PLL's operating frequency  $(f_{PLL})$ . Use the following equation to calculate the time unit  $(t_U)$ :

Equation 1.

$$t_u = \frac{1}{(f_{PLL} * MF)}$$

The  $f_{PLL}$  term, which is calculated with the help of Table 3, must be compatible with the nominal frequency range selected by the FREQ\_SEL signal as defined in Table 4. The multiplication factor (MF), also determined by FREQ\_SEL, is shown in Table 5. The UT7R2XLR816 output skew steps have a typical accuracy of +/- 300ps of the calculated time unit ( $t_U$ ).

**Table 5: MF Calculation**

| FREQ_SEL | MF | $ m f_{PLL}$ examples that result in a $ m t_{U}$ of 1.0ns |

|----------|----|------------------------------------------------------------|

| L        | 32 | 31.25 MHz                                                  |

| M        | 16 | 62.5 MHz                                                   |

| Н        | 8  | 125 MHz                                                    |

## 2.1 Reference Clock Interface

Figure 3. Parallel Resonant Crystal Reference Interface

## 3.0 OPERATIONAL ENVIRONMENT

**Table 6: Operational Environment Design Specifications**

| Parameter                                                                                                   | Limit                   | Units                   |

|-------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|

| Total Ionizing Dose (TID)                                                                                   | min = none<br>max = 1E5 | rads(Si)                |

| Single Event Latchup (SEL) 1, 2                                                                             | >109                    | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Upset (SEU) LET Threshold <sup>3</sup>                                                   | >109                    | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Transient (SET) LET Threshold <sup>4</sup> @ 50 MHz; FREQ_SEL = L @ 24 MHz; FREQ_SEL = L | >60<br>>50              | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence                                                                                             | 1.0E14                  | n/cm <sup>2</sup>       |

- The UT7R2XLR816 is latchup immune to particle LETs >109 MeV-cm²/mg.

Worst case temperature and voltage of T<sub>C</sub> = +125°C, VDD\_A/C = 3.6V, V<sub>DD\_nQ</sub> = 3.6V for SEL.

Worst case temperature and voltage of T<sub>C</sub> = +25°C, VDD\_A/C = 3.0V, V<sub>DD\_nQ</sub> = 3.0V for SEU.

Worst case temperature and voltage of T<sub>C</sub> = +25°C, VDD\_A/C = 3.0V, V<sub>DD\_nQ</sub> = 2.25V for SET.

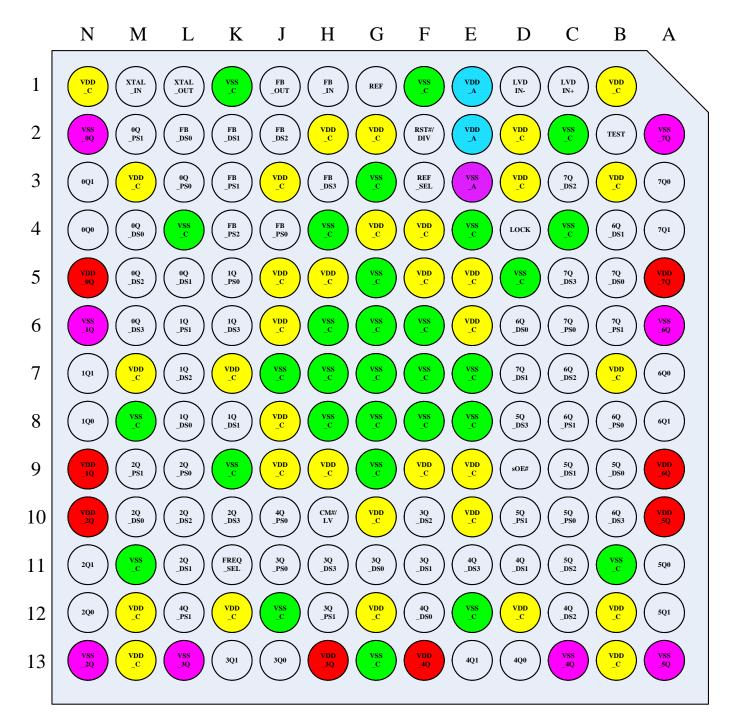

Figure 5. 168-CLGA Pinout (view looking through top of package)

## 4.0 PIN DESCRIPTION

| 168 CLGA<br>Pin No. | Name            | I/O   | Туре                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------------------|-----------------|-------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                     | REFERENCE BLOCK |       |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| G1                  | REF             | IN    | COLD<br>SPARED<br>LVCMOS<br>or LVTTL | Digital reference clock input.  This cold spared input should be driven by a single-ended LVTTL/LVCMOS clock source.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                     |                 |       |                                      | Because REF_SEL selects which reference clock drives the PLL, this input may be actively driven when not selected, but it should never be left floating.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| M1                  | XTAL_IN         | IN    | CRYSTAL                              | This pin is the input to the on-chip pierce oscillator. This input should be connected to the output of an external quartz crystal that is tuned to operate in the parallel mode of resonance.  Because REF_SEL selects which reference clock drives the PLL, this input may be actively driven when not selected, but it should never be                                                                       |  |  |  |  |  |

|                     |                 | 0.7.7 |                                      | left floating.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| L1                  | XTAL_OUT        | OUT   | CRYSTAL                              | Quartz crystal resonator reference clock output.  This pin drives the 180° phase shifted version of the reference signal received on XTAL_IN. This pin should be connected to the input of the external quartz crystal resonator circuit.                                                                                                                                                                       |  |  |  |  |  |

| C1                  | LVDIN+          | IN    | COLD<br>SPARED<br>LVDS               | Positive LVDS reference clock input terminal. This cold spared input should be driven by the positive half of an LVDS clock signal. A $100\Omega$ terminating resistor should be connected directly between this terminal and its complement LVDIN Because REF_SEL selects which reference clock drives the PLL, this input may be actively driven when not selected or left floating in the fail-safe state.   |  |  |  |  |  |

| DI                  | LVDIN-          | IN    | COLD<br>SPARED<br>LVDS               | Negative LVDS reference clock input terminal. This cold spared input should be driven by the negative half of an LVDS clock signal. A $100\Omega$ terminating resistor should be connected directly between this terminal and its complement LVDIN+. Because REF_SEL selects which reference clock drives the PLL, this input may be actively driven when not selected or left floating in the fail-safe state. |  |  |  |  |  |

| 168 CLGA<br>Pin No. | Name    | I/O | Туре    |                                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|---------------------|---------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| F3                  | REF_SEL | IN  | 3-LEVEL | Reference selection input.  This ternary input selects one of the three user reference sources to drive the internal PLL.  Note: The input buffers on the reference sources that are <i>NOT</i> selected by REF_SEL are disabled LOW.  Note: When the device is placed into the reset mode of operation (e.g., RST/DIV = LOW), the XTAL_IN/XTAL_OUT buffers will remain enabled if REF_SEL = LOW. |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|                     |         |     |         | REF_SEL                                                                                                                                                                                                                                                                                                                                                                                           | Selected Sou                                                                                                                                                                                                                                        | ırce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

|                     |         |     |         | LOW                                                                                                                                                                                                                                                                                                                                                                                               | XTAL_IN                                                                                                                                                                                                                                             | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

|                     |         |     |         | MID                                                                                                                                                                                                                                                                                                                                                                                               | REF                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|                     |         |     |         | HIGH                                                                                                                                                                                                                                                                                                                                                                                              | LVDIN+, LV                                                                                                                                                                                                                                          | DIN-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

| F2                  | RST/DIV | IN  | 3-LEVEL | LOW MID No                                                                                                                                                                                                                                                                                                                                                                                        | es as a dual function p<br>input reference divid<br>ce will directly drive<br>lected reference source<br>ag power up and refer<br>LR816 startup that<br>reference clock. The<br>e a reset to the PLL<br>placed into the reset<br>XTAL_IN/XTAL_OLOW. | ter. When driven the PLL. All ce being divided to being divided to be performed to the control of the control o | wen HIGH, lowing this ded in half abilization ent of the bedriven out divider ration (e.g. will remain blled by the |

| 168 CLGA<br>Pin No.  | Name                                 | I/O | Туре                                 | Description                                                                                                                                                                                                                                                                              |

|----------------------|--------------------------------------|-----|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                      |     | FEED                                 | BACK BLOCK                                                                                                                                                                                                                                                                               |

| H1                   | FB_IN                                | IN  | COLD<br>SPARED<br>LVCMOS<br>or LVTTL | Feedback input clock source.  This cold spared LVCMOS/LVTTL input can be driven directly from the FB_OUT pin or from a digital circuit which has the FB_OUT pin at its source.                                                                                                           |

| J1                   | FB_OUT                               | OUT | LVCMOS                               | Feedback output clock source.  This LVCMOS3.3 output is driven from the PLL. The FB_DS[3:0] and FB_PS[2:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  The FB_OUT pin should be used as the originating clock source for the FB_IN pin. |

| H3<br>J2<br>K2<br>L2 | FB_DS3<br>FB_DS2<br>FB_DS1<br>FB_DS0 | IN  | 3-LEVEL                              | Feedback output division selector and controller.  These four ternary inputs are used to control the FB_OUT clock divider, inverter, and enable control. Table 1 lists the output behavior resulting from each combination of these pins.                                                |

| K4<br>K3<br>J4       | FB_PS2<br>FB_PS1<br>FB_PS0           | IN  | 3-LEVEL                              | Feedback output phase selector.  These three ternary inputs are used to control the FB_OUT phase alignment. Table 2 lists the output phase selections resulting from each combination of these pins.                                                                                     |

| 168 CLGA<br>Pin No.  | Name                                 | I/O | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|----------------------|--------------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                      | CLOCK BANK 0                         |     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| N4                   | 0Q0                                  | OUT | LVCMOS  | Bank 0 clock output 0.  This LVCMOS output is driven from the PLL. The 0Q_DS[3:0] and 0Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                      |                                      |     | LVDS    | Bank 0 positive LVDS output terminal.  This LVDS output is driven from the PLL. The OQ_DS[3:0] and OQ_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the positive LVDS input terminal on the receiving device and is the complement of the OQ1 LVDS output terminal.  This terminal is enabled as an LVDS output when the CM/LV pin is MID or HIGH.                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| N3                   | 0Q1                                  | OUT | LVCMOS  | Bank 0 clock output 1.  This LVCMOS output is driven from the PLL. The 0Q_DS[3:0] and 0Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin is LOW.  Bank 0 negative LVDS output terminal.  This LVDS output is driven from the PLL. The 0Q_DS[3:0] and 0Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the negative LVDS input terminal on the receiving device and is the complement of the 0Q0 LVDS output terminal.  This terminal is enabled as an LVDS output when the CM/LV pin is MID or HIGH. |  |  |  |  |  |  |

| M6<br>M5<br>L5<br>M4 | 0Q_DS3<br>0Q_DS2<br>0Q_DS1<br>0Q_DS0 | IN  | 3-LEVEL | <b>OQ</b> bank output division selector and controller.  These four ternary inputs are used to control the OQ[1:0] output clock divider, inverter, and enable control. Table 1 lists the output behavior resulting from each combination of these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| M2<br>L3             | 0Q_PS1<br>0Q_PS0                     | IN  | 3-LEVEL | <b>0Q</b> bank output phase selector.  These two ternary inputs are used to control the 0Q[1:0] output phase alignment. Table 2 lists the output phase selections resulting from each combination of these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| N5                   | $V_{\mathrm{DD}\_0\mathrm{Q}}$       | PWR | POWER   | <b>0Q bank power supply.</b><br>+2.5V +/-10% or +3.3V +/-0.3V power source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N2                   | V <sub>SS_0Q</sub>                   | PWR | POWER   | <b>0Q bank ground reference supply.</b> 0.0V ground reference source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 168 CLGA<br>Pin No.  | Name                                 | I/O | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|----------------------|--------------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                      | CLOCK BANK 1                         |     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| N8                   | 1Q0                                  | OUT | LVCMOS  | Bank 1 clock output 0.  This LVCMOS output is driven from the PLL. The 1Q_DS[3:0] and 1Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin is LOW or MID.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                      |                                      |     | LVDS    | Bank 1 positive LVDS output terminal.  This LVDS output is driven from the PLL. The 1Q_DS[3:0] and 1Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the positive LVDS input terminal on the receiving device and is the complement of the 1Q1 LVDS output terminal.  This terminal is enabled as an LVDS output when the CM/LV pin is HIGH.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| N7                   | 1Q1                                  | OUT | LVCMOS  | Bank 1 clock output 1.  This LVCMOS output is driven from the PLL. The 1Q_DS[3:0] and 1Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin is LOW or MID.  Bank 1 negative LVDS output terminal.  This LVDS output is driven from the PLL. The 1Q_DS[3:0] and 1Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the negative LVDS input terminal on the receiving device and is the complement of the 1Q0 LVDS output terminal.  This terminal is enabled as an LVDS output when the CM/LV pin is HIGH. |  |  |  |  |  |  |  |

| K6<br>L7<br>K8<br>L8 | 1Q_DS3<br>1Q_DS2<br>1Q_DS1<br>1Q_DS0 | IN  | 3-LEVEL | 1Q bank output division selector and controller.  These four ternary inputs are used to control the 1Q[1:0] output clock divider, inverter, and enable control. Table 1 lists the output behavior resulting from each combination of these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| L6<br>K5             | 1Q_PS1<br>1Q_PS0                     | IN  | 3-LEVEL | 1Q bank output phase selector.  These two ternary inputs are used to control the 1Q[1:0] output phase alignment. Table 2 lists the output phase selections resulting from eac combination of these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| N9                   | V <sub>DD_1Q</sub>                   | PWR | POWER   | 1Q bank power supply.<br>+2.5V +/-10% or +3.3V +/-0.3V power source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| N6                   | V <sub>SS_1Q</sub>                   | PWR | POWER   | 1Q bank ground reference supply. 0.0V ground reference source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 168 CLGA                 | Name                                 | I/O | Type    | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|--------------------------|--------------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin No.                  | Name                                 | 1/0 | Туре    | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                          | CLOCK BANK 2                         |     |         |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| N12                      | 2Q0                                  | OUT | LVCMOS  | Bank 2 clock output 0.  This LVCMOS output is driven from the PLL. The 2Q_DS[3:0] and 2Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin is LOW.                                                                                |  |  |  |  |  |  |  |

|                          |                                      |     | LVDS    | Bank 2 positive LVDS output terminal.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                          |                                      |     | EVDS    | This LVDS output is driven from the PLL. The 2Q_DS[3:0] and 2Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the positive LVDS input terminal on the receiving device and is the complement of the 2Q1 LVDS output terminal.                                        |  |  |  |  |  |  |  |

|                          |                                      |     |         | This terminal is enabled as an LVDS output when the $\overline{\text{CM}}/\text{LV}$ pin is MID or HIGH.                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| N11                      | 2Q1                                  | OUT | LVCMOS  | Bank 2 clock output 1.  This LVCMOS output is driven from the PLL. The 2Q_DS[3:0] and 2Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output.  This terminal is enabled as an LVCMOS output when the CM/LV pin                                                                                        |  |  |  |  |  |  |  |

|                          |                                      |     |         | is LOW.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                          |                                      |     | LVDS    | Bank 2 negative LVDS output terminal.  This LVDS output is driven from the PLL. The 2Q_DS[3:0] and 2Q_PS[1:0] inputs determine the divider, inverter, enable/disable, and phase settings for this output. This terminal should drive the negative LVDS input terminal on the receiving device and is the complement of the 2Q0 LVDS output terminal. |  |  |  |  |  |  |  |

|                          |                                      |     |         | This terminal is enabled as an LVDS output when the $\overline{\text{CM}}/\text{LV}$ pin is MID or HIGH.                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| K10<br>L10<br>L11<br>M10 | 2Q_DS3<br>2Q_DS2<br>2Q_DS1<br>2Q_DS0 | IN  | 3-LEVEL | <b>2Q</b> bank output division selector and controller.  These four ternary inputs are used to control the 2Q[1:0] output clock divider, inverter, and enable control. Table 1 lists the output behavior resulting from each combination of these pins.                                                                                              |  |  |  |  |  |  |  |

| M9<br>L9                 | 2Q_PS1<br>2Q_PS0                     | IN  | 3-LEVEL | 2Q bank output phase selector.  These two ternary inputs are used to control the 2Q[1:0] output phase alignment. Table 2 lists the output phase selections resulting from eacombination of these pins.                                                                                                                                               |  |  |  |  |  |  |  |

| N10                      | V <sub>DD_2Q</sub>                   | PWR | POWER   | <b>2Q bank power supply.</b><br>+2.5V +/-10% or +3.3V +/-0.3V power source.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |