#### **Lime Microsystems**

Surrey Tech Centre Occam Road The Surrey Research Park Guildford Surrey GU2 7YG United Kingdom

# LMS7002EVB Quick Start Manual

The information contained in this document is subject to change without prior notice. Lime Microsystems assumes no responsibility for its use, nor for infringement of patents or other rights of third parties. Lime Microsystems' standard terms and conditions apply at all times.

© Copyright Lime Microsystems Proprietary and Confidential

## **REVISION HISTORY**

The following table shows the revision history of this document:

| Date       | Version | Description of Revisions                                                 |  |

|------------|---------|--------------------------------------------------------------------------|--|

| 05/06/2014 | 2.0     | Initial version                                                          |  |

| 2/07/2014  | 2.1     | Updated GUI pictures and new control descriptions                        |  |

| 8/08/2014  | 2.2     | Updated GUI pictures and new control descriptions and 7.23 section added |  |

| 23/10/2014 | 2.3     | Updated Figure 2                                                         |  |

| 05/11/2014 | 2.4     | Updated GUI controls description. GUI version 3.6.3159.7344              |  |

| 24/08/2015 | 2.5     | Updated description of Introduction, Development System Content,         |  |

|            |         | Overview of the Development Board,                                       |  |

| 30/10/2015 | 2.6     | Updated new GUI software 'LMS 7 Suite' description on all tabs and       |  |

|            |         | changed all screen shots. Updated section 4.3                            |  |

Version: 2.6

# **Contents**

| REVISION         | HISTORY                                  | 2  |

|------------------|------------------------------------------|----|

| 1. Introduc      | tion                                     | 8  |

| 2. Developn      | nent System Content                      | 9  |

| 3. Overview      | v of the Development Board               | 11 |

|                  | g the LMS 7 Suite Software               |    |

|                  | ction to installing the software         |    |

|                  | vs USB Setup                             |    |

|                  | ining Serial Port                        |    |

|                  | etup                                     |    |

|                  | g LMS 7 Suite Software                   |    |

|                  | ting                                     |    |

|                  | started with the EVB                     |    |

|                  | ction to using the EVB7                  |    |

|                  |                                          |    |

|                  | nitter Setup and Basic Testing           |    |

| 5.2.1.<br>5.2.2. | SXT/SXR tab setupTRF tab setup           |    |

| 5.2.3.           | TBB tab setup                            |    |

|                  | the TX Output                            |    |

| 5.3.1.           | TX Basic Operation Checks                |    |

| 5.4 Receive      | r Setup and Basic Testing                |    |

| 5.4.1.           | SXT/SXR tab setup                        | 25 |

| 5.4.2.           |                                          |    |

| 5.4.3.           |                                          |    |

| 5.5 Testing      | the RX Output                            | 29 |

| 5.5.1.           | RX Basic Operation Checks                |    |

| 5.6 Testing      | With Minimal Equipment                   | 30 |

| 6. EVB7 Co       | onnectors and Options                    | 31 |

| 6.1 Introdu      | ction to the EVB7 Connectors and Options | 31 |

| 6.2 Board C      | Connections                              | 31 |

| 6.2.1.           | FMC connector pin description            |    |

| 6.2.2.           | Digital I/O connector pin description    |    |

|                  | are options                              |    |

|                  |                                          |    |

| 6.3.1.             | TCXO's Configuration                  | 37 |

|--------------------|---------------------------------------|----|

| 6.3.2.             | EVB7 synchronization                  |    |

| 6.3.3.             | SPI Control Configuration             |    |

| 6.3.4.             | Baseband Digital Interface Voltage    |    |

| 6.3.5.             | EVB7 Matching networks                |    |

|                    | Guide to LMS 7 Suite                  |    |

| 7.1 LMS 7 S        | Suite – Software Description          | 40 |

| 7.2 LMS 7 S        | Suite – Window Panels                 | 40 |

| 7.2.1.             | GUI Control panel                     | 40 |

| 7.2.2.             | Configuration panel                   |    |

| 7.2.3.             | Log panel                             |    |

| 7.3 The Mei        | nu Bar                                | 43 |

| 7.3.1.             | The File Menu                         |    |

| 7.3.2.             | The Option Menu                       |    |

| 7.3.3.             | The Modules Menu                      |    |

| 7.3.4.<br>7.3.5.   | The Help Menu The Button Menu         |    |

| 7.3.5.<br>7.3.6.   | The Configuring Channel Controls      |    |

|                    | tions                                 |    |

|                    | Setup (Si5351C and ADF4002)           |    |

|                    | <u> </u>                              |    |

| 7.7 RBB            |                                       | 51 |

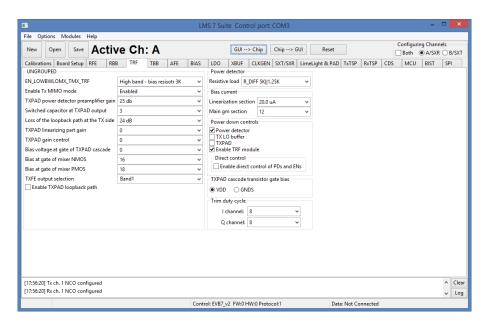

| 7.8 TRF            |                                       | 53 |

|                    |                                       |    |

|                    |                                       |    |

|                    |                                       |    |

| 7.12 LDO           |                                       | 60 |

|                    |                                       |    |

|                    | EN                                    |    |

| 7.15 SXT/S         | XR                                    | 65 |

| 7.16 Applica       | ation Note on Tuning PLLs on LMS7002M | 67 |

| 7.17 LimeL         | ight & PAD                            | 68 |

| 7.18 TxTSP         | )                                     | 72 |

| 7.19 <b>R</b> xTSP | )                                     | 74 |

| 7.20 CDS           |                                       | 76 |

## LMS7002M Quick Starter Manual for EVB7 kit

| 7.21 BIST   |                                                 | 77 |

|-------------|-------------------------------------------------|----|

| 7.22 SPI    |                                                 | 78 |

| 8. Appendix | x A: Test Equipment Setup                       | 80 |

| 8.1 Introdu | ction                                           | 80 |

| 8.2 Recomn  | nended Test Equipment                           | 80 |

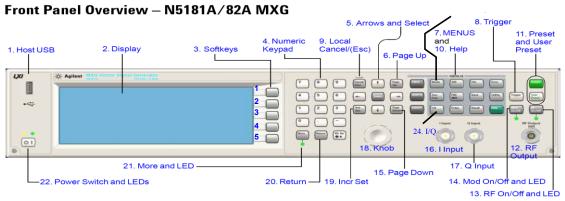

| 8.3 Agilent | MXG Setup                                       | 81 |

| 8.3.1.      | Setting Common Mode Voltage                     | 81 |

| 8.3.2.      | Enabling the Arbitrary Waveform Generator       |    |

| 8.3.3.      | Downloading *.wfm Files to the Signal Generator | 83 |

| NOTICE O    | OF DISCLAMER                                    | 86 |

# Table of Figures

| Figure 1 Development System Content                                | 9  |

|--------------------------------------------------------------------|----|

| Figure 2 Board block diagram                                       |    |

| Figure 3 Device Manager content                                    | 15 |

| Figure 4 Device properties                                         | 16 |

| Figure 5 Update Driver Wizard.                                     | 16 |

| Figure 6 Hardware wizard. Install driver manually                  | 17 |

| Figure 7 Check for new communication port                          |    |

| Figure 8 GUI communication settings                                | 19 |

| Figure 9 GUI detected device and firmware version                  | 19 |

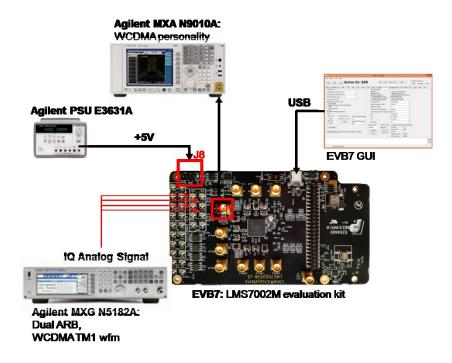

| Figure 10 Tx Test Setup                                            | 21 |

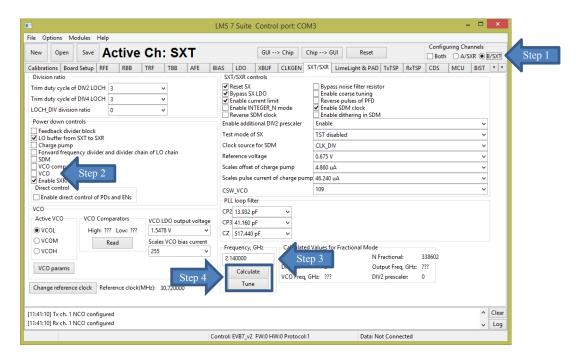

| Figure 11 SXT register setup procedure                             | 22 |

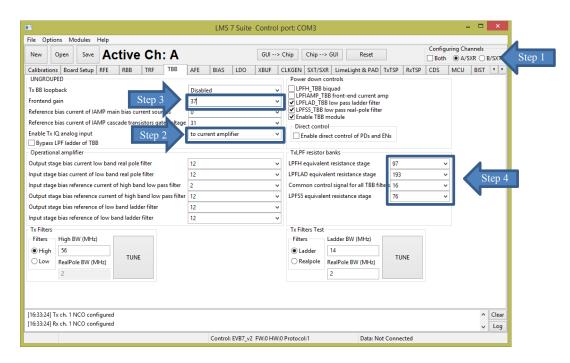

| Figure 12 TBB register setup procedure                             | 23 |

| Figure 13 Basic TX testing using DC offset resulting in LO leakage | 23 |

| Figure 14 Basic TX testing using WCDMA modulation                  | 24 |

| Figure 15 Rx Test Setup                                            | 25 |

| Figure 16 SXR register setup procedure                             | 26 |

| Figure 17 SXR register setup procedure                             | 27 |

| Figure 18 SXR register setup procedure                             | 28 |

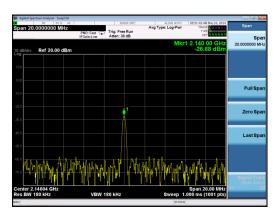

| Figure 19 RX analog output on Spectrum Analyser.                   | 29 |

| Figure 20 Design kit connection descriptions, Top view.            | 31 |

| Figure 21 Design connection descriptions, Bottom view.             | 32 |

| Figure 22 GUI window diagram                                       |    |

| Figure 23 GUI Control Panel window                                 | 41 |

| Figure 24 GUI Configuration Board Setup window                     | 42 |

| Figure 25 GUI Log panel                                            | 42 |

| Figure 26 GUI Message Log tab                                      | 43 |

| Figure 27 GUI Modules Menu window                                  | 44 |

| Figure 28 GUI Calibrations tab                                     |    |

| Figure 29 GUI Board Setup tab                                      | 47 |

| Figure 30 GUI RFE tab                                              | 49 |

| Figure 31 GUI RXBB tab                                             | 51 |

| Figure 32 GUI TRF page                                             |    |

| Figure 33 GUI TBB page                                             | 55 |

| Figure 34 GUI AFE tab                                              |    |

| Figure 35 GUI BIAS tab                                             |    |

| Figure 36 GUI LDO Power downs & Bias & Noise filter tab            |    |

| Figure 37 GUI LDO Voltages tab                                     |    |

| Figure 38 GUI XBUF tab                                             |    |

| Figure 39 GUI CLKGEN tab                                           |    |

| Figure 40 GUI SXT/SXR tab                                          |    |

| Figure 41 GUI Limelight & PAD Modes tab                            |    |

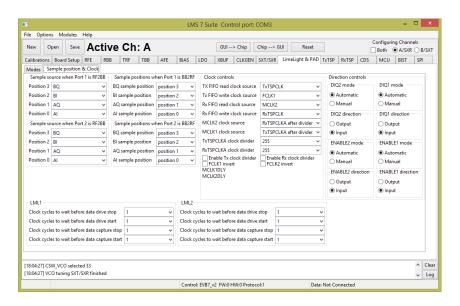

| Figure 42 GUI Limelight & PAD Sample position tab                  |    |

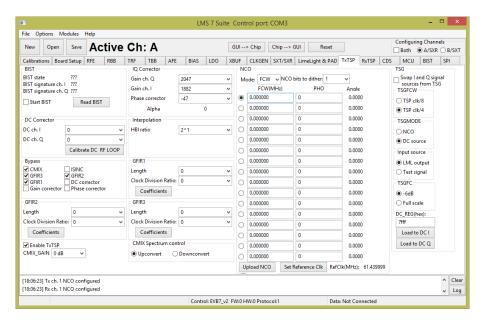

| Figure 43 GUI TxTSP tab                                            | 72 |

## LMS7002M Quick Starter Manual for EVB7 kit

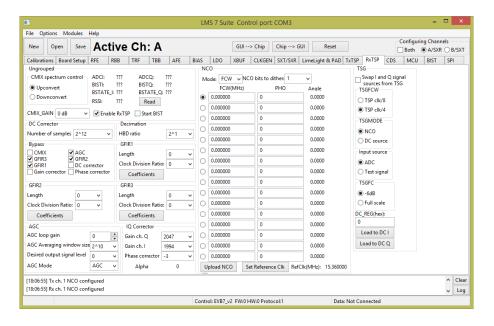

| Figure 44 GUI RxTSP tab                      | 74 |

|----------------------------------------------|----|

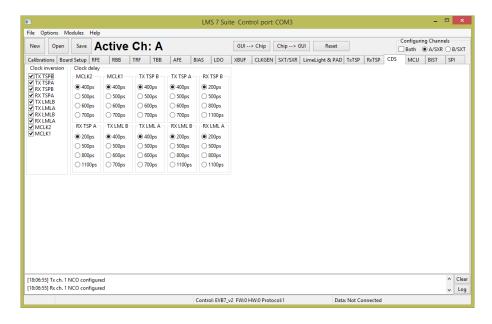

| Figure 45 GUI CDS tab                        | 76 |

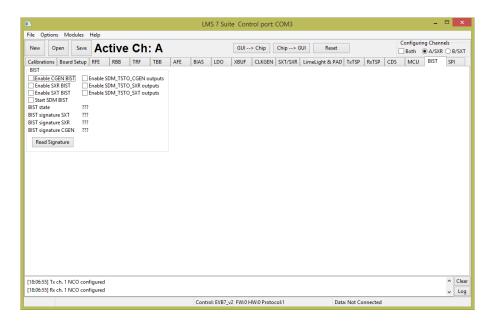

| Figure 46 GUI BIST tab                       | 77 |

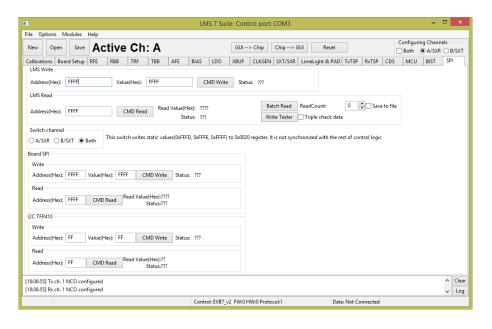

| Figure 47 GUI SPI tab                        | 78 |

| Figure 48 Agilent N5181A/82A MXG Front Panel | 81 |

| Figure 49 CMD window showing successful ping | 84 |

| Figure 50 CMD window with ftp connection     | 84 |

| Figure 51 CMD window ftp file transfer       | 85 |

Version: 2.6

1

# Introduction

The Lime Development System is a comprehensive hardware and software combination that allows users to evolve and refine a wireless sub-system. It can be combined with a baseband processor such as an FPGA or DSP processor to develop a comprehensive wireless solution.

The EVB7 module is a high-speed wireless communication module, based on the LMS7002M fully programmable RF transceiver. It is designed to support 2G, 3G, 4G/LTE radio systems with both time-division duplex (TDD) and frequency-division duplex (FDD) applications, M2M and software defined radios. The wireless communication module covers the frequency range of 100 kHz to 3.8 GHz, including licensed and unlicensed bands. The channel bandwidth is programmable from less than 100 kHz to 108 MHz through a combination of analog and digital filtering via the easy-to-use GUI software.

The EVB7 provides system designers with the ability to connect the board to any type of baseband, FPGA or CPU and allow them to implement their ideas for various wireless communication applications.

This document describes how to make a quick start with the LMS7002M using the EVB7 module. Section 2 begins by listing the contents of the Quick Start kit. Section o gives a general description of the evaluation board features. Section 4 describes the procedure for obtaining and installing the 'LMS 7 Suite' software for both Windows and Linux platforms. Section 5 describes how to connect and use the EVB and 'LMS 7 Suite' software for the Quick Start example configurations. Section 6 describes in detail the EVB connectors and hardware options. Section 7 describes in detail how to use the 'LMS 7 Suite' software. Appendix A in section 8 details the recommended test and measurement equipment, and how to set up the test equipment to work with RF-ESPARK and the LMS7002M.

2

# **Development System Content**

Figure 1 Development System Content

Last modified: 30/10/2015

Complete development kit content consists of:

- Hardware

- 1 LMS7002EVB v3 board

- 1 Power supply cable that connects the EVB7 board to any lab power supply unit

- o 1 USB-A to Micro-USB-B cable

- o USB stick with software

- o 4 x SMA to U.FL RF cables

- Software:

Version: 2.6

- o LMS7002M GUI "lms7suite"

- o Waveforms example files

9 | P a g e

- Windows drivers

- Documentation:

- o Quick Starter Manual

- o LMS7002M datasheet

- Board schematics

- o LMS7002M Programming and Calibration Guide

# 3

# Overview of the Development Board

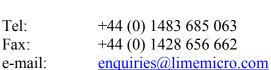

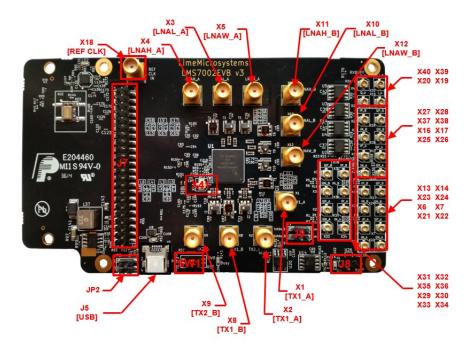

Figure 2 Board block diagram

A photograph of the development board is shown in *Figure 1*. A block diagram of the board is shown in *Figure 2*. The connections are shown in blue, the LMS7002M chip is shown in green,

11 | Page

and the other parts are shown in orange. The core of the board is the LMS7002M transceiver chip, which has multiple RF, analogue and digital interfaces.

The evaluation board includes RF matching networks for the LMS7002M. These matching networks include wideband transformers to allow operation over the entire frequency range. However, the matching networks have been optimized for operation over selected frequency bands and offer the best performance in these bands. Connectors are provided for 4 RF transmitter outputs and 6 RF receiver inputs. Further details of the matching networks are provided in section 6.3.5.

The evaluation board includes connectors for the baseband analogue differential receiver outputs and differential transmitter inputs. Additionally, on board high speed differential to single ended converters allow the EVB7 receivers to indirectly drive 50 Ohm test equipment such as spectrum analysers for baseband testing.

The evaluation board includes a clock generation block, which by default, is a standalone 30.72 MHz low phase noise TXCO. TXCOs at other frequencies can also be fitted and three different footprints are supported. The EVB7 can be easily modified to operate with external clock sources. It can also be synchronized to the standard 10 MHz reference of measurement equipment via an on board PLL. Details of the required changes on EVB7 are given in section 6.3.1 and 6.3.2.

EVB7 includes two kinds of digital I/O, one for control only, and two for data and control.

The USB interface is used to control the LMS7002M SPI via the LMS 7 Suite software. The USB port is converted to SPI by an on board microcontroller.

The FMC connector or the 44 pin header can be used for the buffered digital interface and can be connected to compatible platforms such as the Lime "Stream" board. The Lime "Stream" board also provides connections to general purpose lab equipment such as pattern generators and logic analysers. A pin list for the digital interface can be found in section 6.2. The logic level for the digital interface can be set by modifying EVB7 and is described in section 6.3.4. Additionally these connectors can be used to control the SPI but require the board modifications described in 6.3.3.

A 7<sup>th</sup> order LC filter can be selected between the analogue output of the LMS7002M and its digital inputs by using the LMS 7 Suite software. This allows additional filtering at 100 kHz (IF BW) for 2G applications.

The board includes memory to work with the LMS7002M internal microcontroller. This is intended to provide calibration support for the LMS7002M. The memory is programmed via the LMS 7 Suite software and the USB/SPI interface.

Test points are provided for various test signals including the LMS7002M internal peak and RSSI detectors as well as various PLL test signals.

More detailed information on the connectors for the evaluation board can be found in section *6.1*. Information about PCB options supported is in section *6.3*.

Last modified: 30/10/2015

Version: 2.6

4

# **Installing the LMS 7 Suite Software**

## 4.1 Introduction to installing the software

To operate the EVB7 board, the LMS 7 Suite software has to be downloaded from <a href="http://www.limemicro.com/resources/">http://www.limemicro.com/resources/</a> under the section 'LMS7002EVB7 Software' and installed. The software consists of four parts.

- The main LMS 7 Suite Software, which provides a GUI to control the chip.

- Waveforms to generate either CW test signal or W-CDMA Test mode 1 signal

- The USB driver "USB to LMS7002M", which provides an interface between the PC and the EVB7 SPI microcontroller.

- The EVB7 microcontroller firmware, which is preinstalled on the board prior to shipping.

Section 4.1 describes the how to download the software from the Lime Microsystems web page.

Sections 4.2, 4.3 and 4.4 describe the set up for the Windows Operating System. Section 4.2 describes the installing of the "USB to LMS7002M" driver. Section 4.3 describes how to identify which USB port is being used. Section 4.4 describes how to run the kit on Linux OS. Section 4.5 describes how to start running the 'LMS 7 Suite' on Windows. Section 4.6 describes how to connect the UNITE7002 with the 'LMS 7 Suite' via the USB interface.

A simple demonstration of the "LMS 7 Suite' is given in section 5. A detailed description of the "LMS 7 Suite' is given in section 7.

Last modified: 30/10/2015

14 | P a g e

Version: 26

#### 4.2 Windows USB Setup

The steps to setup 'LMS 7 Suite' software are as follows (please note that these steps may vary based on the specific version of Windows software being used and you may need to be logged in as Administrator to accomplish them):

- 1. Connect EVB7 board to your PC via the USB cable.

- 2. Go to Control Panel > System > Device Manager

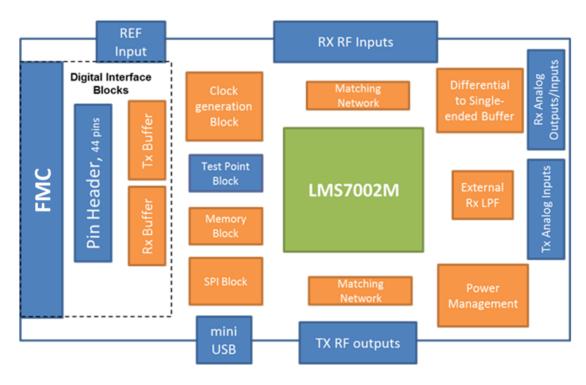

- 3. Locate **USB to LMS7002M** under **Other devices** and press right click to select **Properties** *Figure 3*

Figure 3 Device Manager content

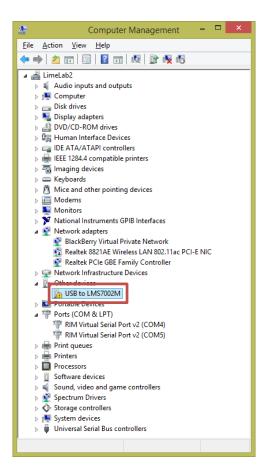

4. When a new window pops-up press Update driver Figure 4

Figure 4 Device properties

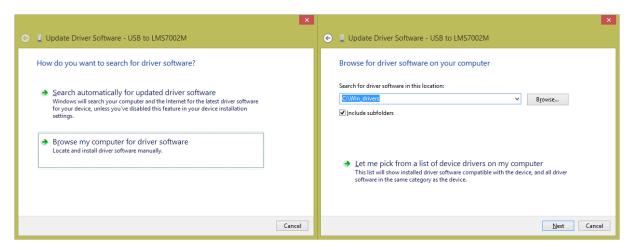

5. Select **Browse my computer for driver software,** locate the driver provided with EVB7 board and press **Next** *Figure 5*

Figure 5 Update Driver Wizard.

6. If the **Windows Security** window appears, select **Install this driver software** anyway Figure 6

16 | P a g e

© Copyright Lime Microsystems Proprietary and Confidential

Figure 6 Hardware wizard. Install driver manually

Windows should proceed to install drivers at this stage. Generally, once the above steps have been taken for the EVB7, these steps do not need to be repeated.

#### **IMPORTANT:**

Version: 2.6

Before running the control software, unplug then plug your device back into your computer.

17 | Page

© Copyright Lime Microsystems Proprietary and Confidential

#### 4.3 Determining Serial Port

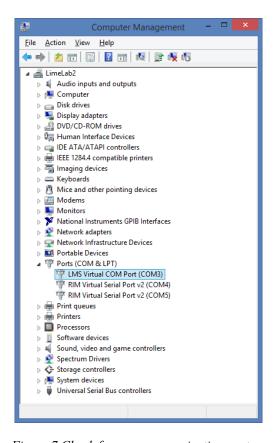

After driver installation, Windows will assign to your EVB7 board a serial port. To check your board serial port number, please follow these steps:

- 1. Go to Control Panel > System > Device Manager

- 2. Locate USB Virtual Serial Port under Ports (COM & LPT)

Note that in this system example it has enumerated as COM3 Figure 7.

Figure 7 Check for new communication port

**NOTE:** If you are using Windows 7 64 bit OS, you must disable **Driver Signature Enforcement.** To do this, Restart you PC, press F8 at startup and choose **Disable Driver Signature Enforcement**. This step is required to done once.

**NOTE:** If you are using Windows 8 or later, to disable driver signature enforcement manual can be found in this [<u>link</u>].

## 4.4 Linux Setup

For Linux users, there is no need to install USB drivers, as the system will assign drivers automatically once the EVB7 board is connected to PC.

To determine port number the easiest is via the command line and type command:

\$ setserial -g /dev/ttyS[0123]

#### 4.5 Starting LMS 7 Suite Software

Apply +5V to the board and start 'LMS 7 Suite' software. The application must be run under administrator privileges. To do that, right click on the 'LMS 7 Suite' icon and select **Run as an Administrator**. This will provide administrator privileges, which are required for EVB7 board communication via USB.

#### 4.6 Connecting

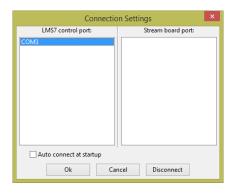

Once the Windows driver is installed and the control software has been lunched, click on **Options>Connection Settings.** The **Connection Setting** windows will pop-up *Figure 8*.

Figure 8 GUI communication settings.

Select the dedicated USB port number of the EVB board. In this case, it is COM3, and press OK.

The GUI device name and firmware version will appear in the bottom (Figure 9), once connection with the board is established.

Figure 9 GUI detected device and firmware version

19 | Page

© Copyright Lime Microsystems Proprietary and Confidential

5

# Getting started with the EVB

#### 5.1 Introduction to using the EVB7

The EVB7 allows powerful demonstrations of the LMS7002M transceiver. In this quick start guide, we demonstrate the board operating with analogue inputs and outputs. The Lime "Stream" board is used to demonstrate the board operating with digital inputs and outputs.

Section 5.2 describes the set up of the transmitter, with section 5.2.1 describing how to set up the SXT (TX PLL) and section 5.2.2 describing how to set up the TX analogue baseband and RF tabs of the LMS 7 Suite software. Section 5.4 describes the set up of the transceiver for basic tests, with section 5.4.1 describing how to set up the SXR (RX PLL) and section 5.4.2 and 5.4.3 describing how to set up the RX analogue baseband and RF tabs of the LMS 7 Suite software.

The analogue quick start demonstration assumes the user has all the equipment listed in Appendix 8.2. Users with less equipment can use the set up of Section 5.6.

Last modified: 30/10/2015

Version: 26

#### 5.2 Transmitter Setup and Basic Testing

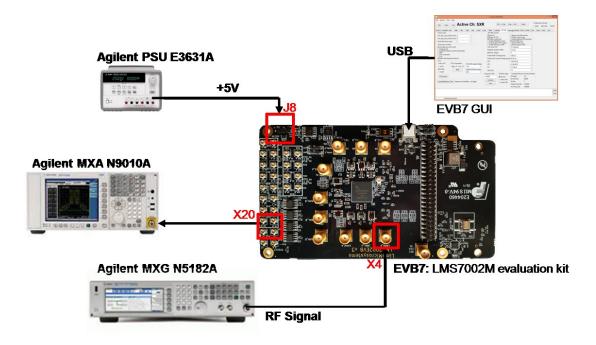

To test the Tx path, the Keysight (formerly Agilent) MXG N5182A generator is used as an external baseband source. This is connected to the Tx path via the analog inputs and generates a WCDMA modulation signal at socket X1 (TX1\_A) as shown in *Figure 10*. To generator settings are described in section 8.3 (Appendix A).

Figure 10 Tx Test Setup

#### 5.2.1. SXT/SXR tab setup

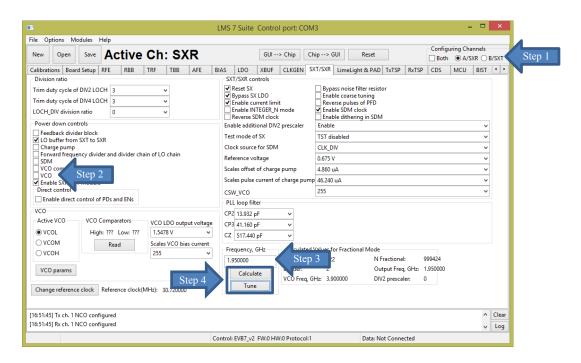

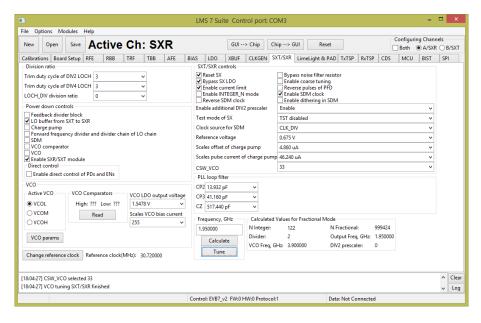

After power up, connect the GUI to the board and select the **SXT/SXR** tab. To configure the Tx LO to 2140 MHz, do the following:

- 1. Select the **B/SXT** in the configuration channels window to control TxPLL

- 2. Enable Tx PLL **VCO** (Deselect)

- 3. Type the wanted frequency in **Frequency, GHz** box. In this case, 2140 MHz

- 4. Press Calculate followed by Tune

See *Figure 11* below to check selections.

Figure 11 SXT register setup procedure

#### 5.2.2. TRF tab setup

The TRF tab controls the TX RF gain and output path. By default the Tx RF gain is set to maximum (**TXPAD gain control** set to '0') and **TXFE output selection** set to **Band 1** (to X1 on EVB7 board) as the output path. For this test, we are not going to change these settings.

#### 5.2.3. TBB tab setup

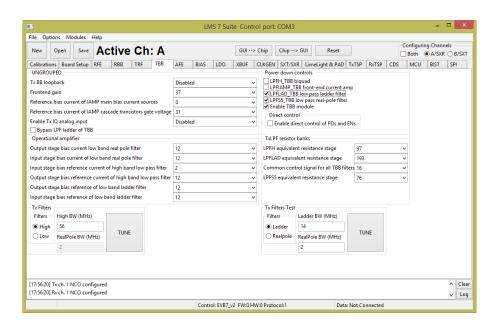

In the **TBB** tab the baseband gain and filter bandwidth are controlled. Follow the instructions below set up TBB:

- 1. Select the A/SXR to control channel A

- 2. Enabled Tx IQ analog input path to current amplifier

- 3. Set Frontend gain to your wanted

- 4. Configure the base band filter settings. By default, high band filter (LPFH\_TBB) is power on

See Figure 12 below to check selections.

22 | P a g e

Figure 12 TBB register setup procedure

<u>Note</u>: the register preset file for Tx test ' $TX_2140\_MHz\_demo\_setup.ini$ ' is supplied with design kit. You can load it by clicking menu button **Open>>** locate and select the file in ../**LMS7GUI** folder/ ' $TX_2140\_MHz\_demo\_setup.ini$ ' >> select **Open**, followed by **GUI-->** Chip button. The select **SXT/SXR** tab and return synthesizer.

## 5.3 Testing the TX Output

When the transmitter is configured as shown in section 5.2, the TX1\_A output (socket X1) can be connected to a spectrum analyzer (SA). With the SA you can now observe the results of this basic operational test *Figure 13*. The test is looking at the DC offset from the un-programmed data DAC as LO leakage and the example shown below is measuring a value of -26.8 dBm.

Figure 13 Basic TX testing using DC offset resulting in LO leakage

23 | P a g e

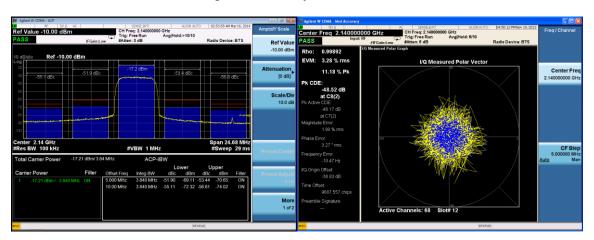

When the baseband is enabled, the WCDMA modulation can be tested and the results of *Figure 14* can be obtained with the MXG Spectrum Analyser.

Figure 14 Basic TX testing using WCDMA modulation

#### **5.3.1.** TX Basic Operation Checks

To check the basic TX frequency and gain control, conduct some tests changing frequencies and gain settings. The following tests are recommended:

TRF – TXPAD gain change setting from 0 to 31 and observe results. LO should vary by approx. 1 dB steps, 31dB range.

Change frequency from 2.14 GHz to 2.11 GHz and press 'Calculate'/'Tune' (CAP value should change), check the Spectrum Analyzer.

Change frequency from 2.11 GHz to 2.17 GHz and press 'Calculate'/'Tune' (CAP value should change), check the Spectrum Analyzer.

## 5.4 Receiver Setup and Basic Testing

The test bench for the receiver is shown in *Figure 15*. Basic functionality checks on the receiver side are achieved by using the Analog output from connector X20.

Figure 15 Rx Test Setup

#### 5.4.1. SXT/SXR tab setup

Version: 26

Select the **SXT/SXR** tab. To configure the Rx LO to 1950 MHz, do the following:

- 1. Select the A/SXR in the configuration channels window to control RxPLL

- 2. Enable Rx PLL **VCO** (Deselect)

- 3. Type the wanted frequency in **Frequency**, **GHz** box. In this case, 1950 MHz.

Last modified: 30/10/2015

4. Press Calculate followed by Tune

See Figure 16 below to check selections.

Figure 16 SXR register setup procedure

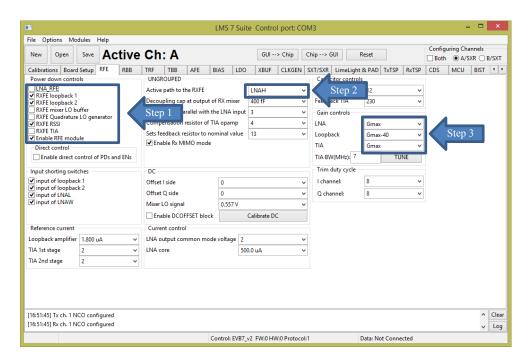

#### 5.4.2. RFE tab setup

Select the RFE tab to configure the receiver RF front–end. Follow the configuration steps below:

- 1. Enable LNA\_RFE, RXFE mixer LO buffer and RFFE Quadrature LO generator

- 2. Select **Active path to the RXFE**. Select **LNAH** for this test. The LNAH is a default setting

- 3. The LNA and TIA gain are preset to maximum

See *Figure 17* below to check selections.

Figure 17 SXR register setup procedure

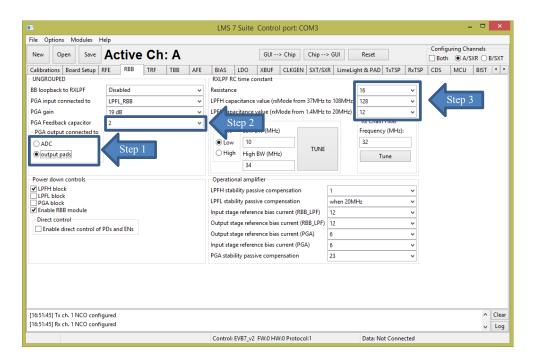

#### 5.4.3. RBB tab setup

Version: 2.6

Select the TBB tab to configure the PGA gain and baseband filter bandwidths. Follow the configuration steps below:

1. Select PGA output to **output pads**. This selection enables receiver analog outputs

Last modified: 30/10/2015

- 2. Set **PGA** gain to 19 dB

- 3. Configure filter bandwidth. By default the LPFL is selected

See Figure 18 below to check selections.

27 | Page

Figure 18 SXR register setup procedure

<u>Note</u>: the register preset file for Rx test 'RX\_1950MHz\_demo\_setup.ini' is supplied with design kit. You can load it by clicking menu button **Open>>** locate and select the file in ../LMS7GUI folder/ 'RX\_1950MHz\_demo\_setup.ini' >> select **Open**, followed by GUI--> Chip button. The select SXT/SXR tab and return synthesizer.

#### 5.5 Testing the RX Output

Set the signal generator to 1955 MHz (i.e. 5 MHz offset from PLL frequency selected) and input a sine wave at -70 dBm into the evaluation board antenna connector (LNAH\_A, connector X4). Configure the receiver as showed in section 5.3. Connect an Analyser to X20 or X19. If everything is correctly setup, you should see the 1 MHz peak. See *Figure 19* below.

Figure 19 RX analog output on Spectrum Analyser.

#### 5.5.1. RX Basic Operation Checks

To check the basic Rx frequency and gain control, conduct some tests changing frequencies and gain settings. The following six tests are recommended:

- a. RBB change PGA gain setting from 19 to -12, observe results, gain should decrease

- b. RFE change TIA gain settings from Gmax to Gmin, observe results, gain should decrease

- c. RFE LNA gain change from Gmax to Gmax -30, observe results, gain should decrease

- d. Change frequency from 1.95 GHz to 1.92 GHz and press 'Calculate'/'Tune'. Change Signal Generator to 1.925 GHz (1MHz offset from PLL). Observe results

- e. Change frequency from 1.92 GHz to 1.98 GHz and press 'Calculate'/'Tune'. Change Signal Generator to 1.985 GHz (1MHz offset from PLL). Observe results

29 | P a g e © Copyright Lime Microsystems Proprietary and Confidential

## 5.6 Testing With Minimal Equipment

For users without all the equipment specified in section 8.2 (Appendix A) it is possible to link the TX1\_A output (X1) to the receiver input LNAH\_A input (X4) and rely on the LO leakage to provide an input signal to the RX.

Using the methods of section 5.2 and section 5.4 set the SXT to 2140 MHz and SXR to 2145 MHz and measure a 5 MHz signal with an oscilloscope to observe the RXI output at X19. The magnitude of the output signal can be controlled with the various gain controls in the RFE and TRF.

6

# **EVB7 Connectors and Options**

## 6.1 Introduction to the EVB7 Connectors and Options

Section 6.2 describes the various connectors available on the EVB7. Section 6.3 describes the hardware options available on the EVB7, including reference clocks and the SPI control. The top and bottom of the board are shown in *Figure 20* and Figure 21 respectively.

#### **6.2 Board Connections**

Figure 20 Design kit connection descriptions, Top view.

31 | P a g e

Figure 21 Design connection descriptions, Bottom view.

Table 1 describes the high level pin assignment for each connector on the design kit.

Table 1 Design kit connectors and switches

| Connector   Schematic name   Description |                          |                                                                                                                                                                     |

|------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector                                | Schematic name           | -                                                                                                                                                                   |

| JP2                                      | BB supply                | This jumper enables the supply to the EVB7 board from an FPGA development kit. U16 is a voltage regulator that converts +12 V to +5 V                               |

| J5                                       | USB                      | USB Connector to PC                                                                                                                                                 |

| Ј6                                       | FMC                      | The FMC (HPC) is a standard connector used to interface the Lime board directly to an FPGA design kit. The signal pin description is shown in <i>6.2.1</i> section. |

| Ј7                                       | Digital I/O<br>Connector | This connector provides access to externally buffered, LMS70002M digital interface and SPI interface. Signal pin description showed in <i>6.2.2</i> section.        |

| Ј8                                       | +5V Power<br>Supply      | +5 V supply connector                                                                                                                                               |

| Ј9                                       | ATP                      | Analog Test Point                                                                                                                                                   |

| X41                                      | TP                       | Test Point                                                                                                                                                          |

| X1                                       | TX1_A                    | Transmitter TX1 output, channel A. Wideband transmitter output                                                                                                      |

| X2                                       | TX2_A                    | Transmitter TX2 output, channel A. Lower bands transmitter output                                                                                                   |

| Х3                                       | LNAL_A                   | Receiver LNA_L input, channel A. Lower bands receiver input                                                                                                         |

| X4                                       | LNAH_A                   | Receiver LNA_H input, channel A. Higher bands                                                                                                                       |

|                                   |           | receiver input                                                                                                                                                              |

|-----------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X5                                | LNAW_A    | Receiver LNA_W input, channel A. Wideband receiver input                                                                                                                    |

| X8                                | TX1_B     | Transmitter TX1 output, channel B. Wideband transmitter output                                                                                                              |

| X9                                | TX2_B     | Transmitter TX2 output, channel B. Lower bands transmitter output                                                                                                           |

| X10                               | LNAL_B    | Receiver LNA_L input, channel B. Lower bands receiver input                                                                                                                 |

| X11                               | LNAH_B    | Receiver LNA_H input, channel B. Higher bands receiver input                                                                                                                |

| X12                               | LNAW_B    | Receiver LNA_W input, channel B. Wideband receiver input                                                                                                                    |

| X18                               | CLK I/O   | Reference clock input used to synchronize test equipment with EVB7 board to calibrate frequency error. A 10 MHz reference from the test equipment connects to X18 connector |

| X19, X20,<br>X39, X40             | RXBUFFI/Q | Receiver analog single-ended outputs                                                                                                                                        |

| X16, X17,<br>X25-X28,<br>X37, X38 | RXOUTI/Q  | Receiver analog differential outputs                                                                                                                                        |

| X6, X7,<br>X21-X23,<br>X13, X14   | ADCINI/Q  | Receiver analog differential inputs                                                                                                                                         |

| X29-X36                           | TXINI/Q   | Transmitter analog differential inputs                                                                                                                                      |

| SW1                               | U1 Reset  | Switch to reset AT90USB162-16U and load new software. By default set to off                                                                                                 |

Last modified: 30/10/2015

Version: 2.6

#### **6.2.1.** FMC connector pin description

The digital baseband interface can be established via the FMC connector J6. The signal pin description is shown in *Table 2*.

<u>Note</u>: FMC HPC connector has 400 pins, but not all pins are used. Some pins are not connected and some are connected to GND. Please refer to EVB7 schematic for more details.

Table 2 FMC connector signal pin description

| Pin number | Schematic name | Function                                                          |

|------------|----------------|-------------------------------------------------------------------|

| D8         | SyntCLK1       | Clock Out, CMOS                                                   |

| D9         | SyntCLK2       | Clock Out, CMOS                                                   |

| H7         | IQSEL2_DIR     | IQSEL direction control for port 2. If '1' – input, '0' – output  |

| Н8         | DIO_DIR_CTRL1  | Data direction control for port 2. If '1' – input, '0' – output   |

| G9         | SDIO           | Serial port data in/out, CMOS                                     |

| G10        | DIG_RST        |                                                                   |

| H10        | INTR           | I2C port interrupt line, CMOS                                     |

| H11        | SCLK           | Serial port clock, positive edge sensitive, CMOS                  |

| H13        | RXFCLK         | Clock from BBIC to RFIC during JESD207 mode, Port 2               |

| H14        | RXEN           | RX hard power off                                                 |

| G12        | RXMCLK         | Clock from RFIC to BBIC during JESD207 mode, Port 2               |

| G13        | RXIQSEL        | IQ flag in RXTXIQ mode enable flag in JESD207 mode, Port 2        |

| D14        | RESET          | Hardware reset, active low, CMOS                                  |

| D15        | IQSEL1_DIR     | IQSEL direction control for port 1. If '1' – input, '0' – output. |

| C14        | SDO            | Serial port data out, CMOS                                        |

| C15        | DIO_DIR_CTRL2  | Data direction control for port 1. If '1' – input, '0' – output.  |

| H16        | RXD11          | DIQ bus, bit 11, Port 2                                           |

| H17        | RXD8           | DIQ bus, bit 8, Port 2                                            |

| G15        | TXNRX1         | LimeLight protocol control                                        |

| G16        | RXD10          | DIQ bus, bit 10, Port 2                                           |

| D17        | SAEN           | Serial port A enable, active low, CMOS                            |

| H19        | RXD7           | DIQ bus, bit 7, Port 2                                            |

| H20        | RXD4           | DIQ bus, bit 4, Port 2                                            |

| G18        | RXD9           | DIQ bus, bit 9, Port 2                                            |

| G19        | RXD6           | DIQ bus, bit 6, Port 2                                            |

| H22        | RXD3           | DIQ bus, bit 3, Port 2                                            |

| H23        | RXD2           | DIQ bus, bit 2, Port 2                                            |

| G21        | TXNRX2         | LimeLight protocol control                                        |

| G22        | RXD5           | DIQ bus, bit 5, Port 2                                            |

| H25        | TXMCLK         | Clock from RFIC to BBIC during JESD207 mode, Port 1               |

| H26        | TXIQSEL        | IQ flag in RXTXIQ mode enable flag in JESD207 mode, Port 1        |

| G24        | RXD0           | DIQ bus, bit 0, Port 2                                            |

| G25        | RXD1           | DIQ bus, bit 1, Port 2                                            |

| D24        | SBEN           | Serial port B enable, active low, CMOS                            |

| H28 | TXFCLK      | Clock from BBIC to RFIC during JESD207 mode, Port 1             |

|-----|-------------|-----------------------------------------------------------------|

| H29 | TXD10       | DIQ bus, bit 10, Port 1                                         |

| G27 | TXEN        | TX hard power off                                               |

| G28 | TXD11       | DIQ bus, bit 11, Port 1                                         |

| H31 | TXD8        | DIQ bus, bit 8, Port 1                                          |

| H32 | TXD6        | DIQ bus, bit 6, Port 1                                          |

| G30 | TXD9        | DIQ bus, bit 9, Port 1                                          |

| G31 | TXD7        | DIQ bus, bit 7, Port 1                                          |

| H35 | TXD4        | DIQ bus, bit 4, Port 1                                          |

| G33 | TXD5        | DIQ bus, bit 5, Port 1                                          |

| H37 | TXD2        | DIQ bus, bit 2, Port 1                                          |

| H38 | TXD0        | DIQ bus, bit 0, Port 1                                          |

| G36 | TXD3        | DIQ bus, bit 3, Port 1                                          |

| G37 | TXD1        | DIQ bus, bit 1, Port 1                                          |

| F10 | G_PWR_DWN   |                                                                 |

| F11 | DIO_BUFF_OE | DIO port buffer enable/disable. If '1' – disable, '0' – enable. |

| C31 | SDA         | I2C port data line, CMOS                                        |

| C30 | SCL         | I2C port clock line, CMOS                                       |

| D12 | RSSI_ADC0   | Analog test point                                               |

| C10 | RSSI ADC1   | Analog test point                                               |

#### 6.2.2. Digital I/O connector pin description

The DIO card can be connected to EVB 7 via Digitail I/O connector J7. Connectr has 44 pins. The pin description showed in the *Table 3*.

Table 3 Digital I/O connector pin description

| Pin number | Schematic name | Function                                            |

|------------|----------------|-----------------------------------------------------|

| 1          | TXD0           | DIQ bus, bit 0, Port 1                              |

| 2          | TXD1           | DIQ bus, bit 1, Port 1                              |

| 3          | TXD2           | DIQ bus, bit 2, Port 1                              |

| 4          | TXD3           | DIQ bus, bit 3, Port 1                              |

| 5          | TXD4           | DIQ bus, bit 4, Port 1                              |

| 6          | TXD5           | DIQ bus, bit 5, Port 1                              |

| 7          | TXD6           | DIQ bus, bit 6, Port 1                              |

| 8          | TXD7           | DIQ bus, bit 7, Port 1                              |

| 9          | TXD8           | DIQ bus, bit 8, Port 1                              |

| 10         | TXD9           | DIQ bus, bit 9, Port 1                              |

| 11         | TXD10          | DIQ bus, bit 10, Port 1                             |

| 12         | TXD11          | DIQ bus, bit 11, Port 1                             |

| 13         | TXFCLK         | Clock from BBIC to RFIC during JESD207 mode, Port 1 |

| 14         | SyntCLK2       | Clock Out, CMOS.                                    |

| 15         | VDIO           | +3.3V supply                                        |

Last modified: 30/10/2015

Version: 2.6

| 16 | TXIQSEL | IQ flag in RXTXIQ mode enable flag in JESD207 mode, Port 1 |

|----|---------|------------------------------------------------------------|

| 17 | TXMCLK  | Clock from RFIC to BBIC during JESD207 mode, Port 1        |

| 18 | TXEN    | TX hard power off                                          |

| 19 | GND     | GND                                                        |

| 20 | GND     | GND                                                        |

| 21 | RXD0    | DIQ bus, bit 0, Port 2                                     |

| 22 | RXD1    | DIQ bus, bit 1, Port 2                                     |

| 23 | RXD2    | DIQ bus, bit 2, Port 2                                     |

| 24 | RXD3    | DIQ bus, bit 3, Port 2                                     |

| 25 | RXD4    | DIQ bus, bit 4, Port 2                                     |

| 26 | RXD5    | DIQ bus, bit 5, Port 2                                     |

| 27 | RXD6    | DIQ bus, bit 6, Port 2                                     |

| 28 | RXD7    | DIQ bus, bit 7, Port 2                                     |

| 29 | RXD8    | DIQ bus, bit 8, Port 2                                     |

| 30 | RXD9    | DIQ bus, bit 9, Port 2                                     |

| 31 | RXD10   | DIQ bus, bit 10, Port 2                                    |

| 32 | RXD11   | DIQ bus, bit 11, Port 2                                    |

| 33 | TXNRX1  | LimeLight protocol control                                 |

| 34 | SynCLK1 | Clock Out, CMOS                                            |

| 35 | RXFCLK  | Clock from BBIC to RFIC during JESD207 mode, Port 2        |

| 36 | RXIQSEL | IQ flag in RXTXIQ mode enable flag in JESD207 mode, Port 2 |

| 37 | RXMCLK  | Clock from RFIC to BBIC during JESD207 mode, Port 2        |

| 38 | RXEN    | RX hard power off                                          |

| 39 | TXNRX2  | LimeLight protocol control                                 |

| 40 | SAEN    | Serial port A enable, active low, CMOS                     |

| 41 | SCLK    | Serial port clock, positive edge sensitive, CMOS           |

| 42 | SDIO    | Serial port data in/out, CMOS                              |

| 43 | SDO     | Serial port data out, CMOS                                 |

| 44 | RESET   | Hardware reset, active low, CMOS                           |

## 6.3 Hardware options

This section describes the configuration options and set up procedures for:

- TCXO's and data clocks distribution

- EVB7 Synchronization

- SPI connection options

The board is shipped with the default mode which means a basic operation using an external digital I/O source via the FMC connector. Various configurations are available depending on the system requirements for development work. The configurations are summarized and the following sections describe the board modifications required to achieve these configurations.

### 6.3.1. TCXO's Configuration

The LMS7002M device provides a flexible clocking scheme which allows the PLL reference clock and digital interface clock to be independently clocked. In addition, the digital interface clock can be generated internally in LMS7002M.

The EVB7 board is shipped with a 30.72 MHz TCXO. In order to meet the demanding phase noise specifications of the various standards, Lime Microsystems has worked with Rakon to develop a new part, called E6245LF that enables the board to meet the required specifications.

The board can accept three different types of TCXO's as described in *Table 4*.

**Table 4 TCXO Configurations**

| Size         | Reference<br>number | Part<br>Number | Description                                                                                          |

|--------------|---------------------|----------------|------------------------------------------------------------------------------------------------------|

| 14.7 x 9.2   | XO2                 | E5405LF        | 61.44 MHz Crystal oscillator, used in combination with divider /2 (U10) for performance improvements |

| 7 x 5 (4pin) | XO1                 | E5280LF        | 30.72 MHz crystal shipped with the board as a default                                                |

| 7 x 5 (6pin) | XO3                 | E6245LF        | 30.72 MHz high performance crystal oscillator.                                                       |

#### 6.3.2. EVB7 synchronization

Version: 26

The LMS7002M board provides options to synchronize the on-board TCXO with the base band or test equipment systems. To do that, connect a 10 MHz reference clock generated by the test equipment to EVB7 board X18 SMA connector. Program the on-board PLL via the GUI ADF4002 page. When the board is synchronized the LED (LD2) will be lit.

A board that is synchronized with the test equipment or any other RF device will not have frequency error.

Last modified: 30/10/2015

### 6.3.3. SPI Control Configuration

The LMS7002M SPI interface is controlled from a USB connection by default. The SPI interface can also be controlled from baseband interface connectors J6 and J7. Please note only one SPI master can be connected to the bus at the time.

If the SPI is controlled via the baseband connector J6 do not connect either a USB cable to J5 and do not use J7 connector. This removes any possible bus contention. Please note that NF denotes component is Not Fitted.

**Table 5 SPI Control Options**

| SPI control   |                                                           |                                          |

|---------------|-----------------------------------------------------------|------------------------------------------|

| Configuration | DEFAULT MODE<br>USB connector or baseband<br>connector J7 | SPI controlled via J6 baseband connector |

| Description   | SPI controlled via USB or J7                              | SPI connected to BB via connector        |

| Component     | connector                                                 | J6 FMC                                   |

| R91           | NF                                                        | 0R                                       |

| R92           | NF                                                        | 0R                                       |

| R93           | NF                                                        | 0R                                       |

| R94           | NF                                                        | 0R                                       |

| R95           | NF                                                        | 0R                                       |

| R96           | NF                                                        | 0R                                       |

All of these components are located on the underside of the board.

Note. The USB interface must be left disconnected when the external SPI control is being used to prevent bus contention. Additionally the components R91-R96 should be fitted as listed in *Table 5*.

### 6.3.4. Baseband Digital Interface Voltage

The default digital interface voltage is 3.3 V. It can be adjusted by changing R183 to the values listed in *Table 6*.

**Table 6 Digital IO Voltage Control**

Version: 26

| R183  | Interface Voltage |

|-------|-------------------|

| 0.8 k | 1.8V              |

| 1.5k  | 2.5V              |

| 2.32k | 3.3V              |

Last modified: 30/10/2015

# 6.3.5. EVB7 Matching networks

The matching networks that are fitted to EVB7 at manufacture are listed in *Table 7*.

Table 7 Default bands matched to EVB7

| Connector | Schematic name | Matching network                                       |

|-----------|----------------|--------------------------------------------------------|

| X1, X42   | TX1_A          | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

| X2, X43   | TX2_A          | Broadband from 4.5 – 3000 MHz, using TC1-1-13MA+ Balun |

| X3, X44   | LNAL_A         | Broadband from 4.5 – 3000 MHz, using TC1-1-13MA+ Balun |

| X4, X45   | LNAH_A         | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

| X5, X46   | LNAW_A         | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

| X8, X47   | TX1_B          | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

| X9, X48   | TX2_B          | Broadband from 4.5 – 3000 MHz, using TC1-1-13MA+ Balun |

| X10, X49  | LNAL_B         | Broadband from 4.5 – 3000 MHz, using TC1-1-13MA+ Balun |

| X11, X50  | LNAH_B         | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

| X12, X51  | LNAW_B         | Broadband from 10 – 6000 MHz, using TCM1-63AX+ Balun   |

Last modified: 30/10/2015

Version: 2.6

7

# **Detailed Guide to LMS 7 Suite**

# 7.1 LMS 7 Suite – Software Description

This section describes the LMS 7 Suite software GUI and each of the menus, buttons and embedded controls. Most of the pages in the tool corresponds to the top level sections of the SPI programming map, with the exception of the 'Board Setup' and the 'SPI' page.

### 7.2 LMS 7 Suite – Window Panels.

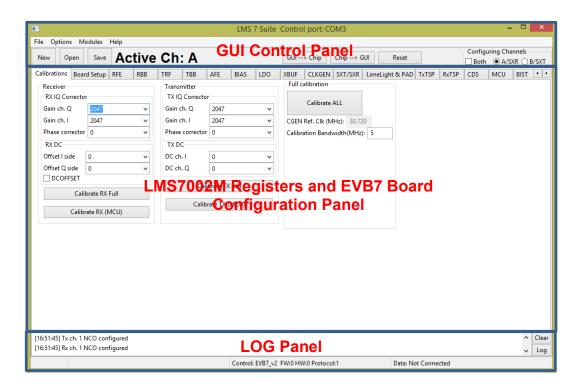

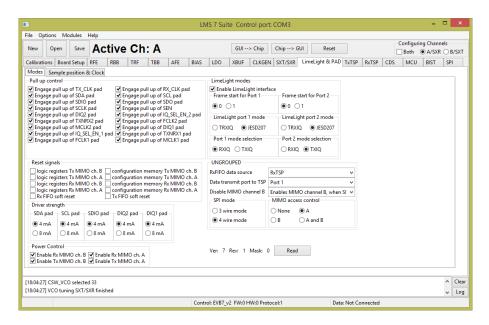

The 'LMS 7 Suite' GUI is comprised in three main pieces: GUI control panel, LMS7002M register and EVB7 board configuration panel, and LOG panel. These are shown in *Figure 22*.

#### 7.2.1. GUI Control panel

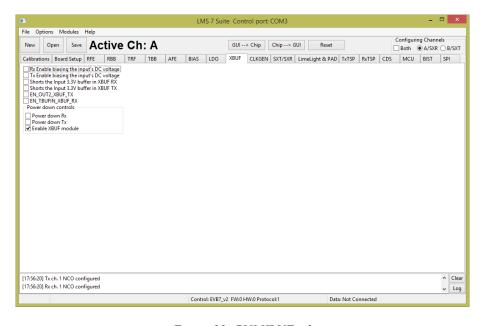

GUI Control panel includes menu bar and various control buttons for controlling the software. These will be described in detail in section 7.3. The GUI control panel is shown in *Figure 23*.

#### 7.2.2. Configuration panel

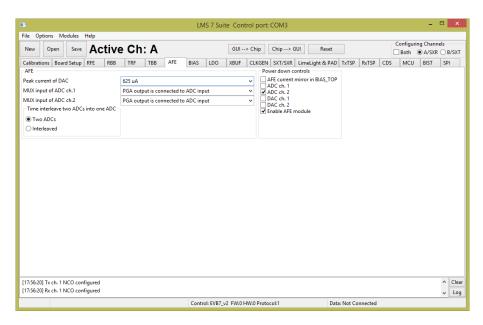

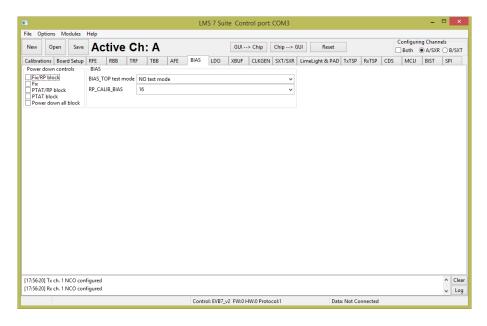

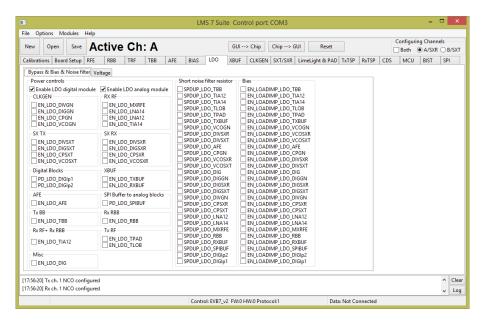

Configuration panel controls the LMS7002M registers and some evaluation board setup and is shown in *Figure 24*.

Each configuration panel has specific register control on internal LMS7002M blocks. There are 17 different configuration panels for controlling the LMS7002M chip and 2 for controlling other devices on the EVB7. Every control of the panel is described in sections 7.4 to 7.22.

40 | P a g e

Figure 22 GUI window diagram

Figure 23 GUI Control Panel window

Figure 24 GUI Configuration Board Setup window

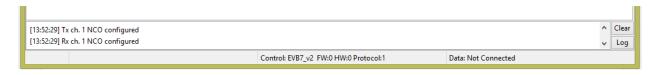

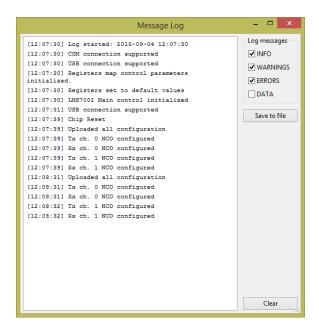

#### **7.2.3. Log panel**

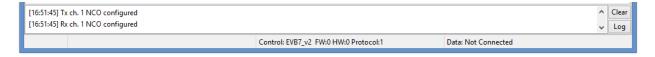

**Log panel** section logs all activity executed with the GUI and is shown in *Figure 25*.

Figure 25 GUI Log panel

The Clear button deletes previously registered activity.

When Log button pressed, the Message Log configuration pop-up, as shown in

Figure 26.

42 | P a g e

Figure 26 GUI Message Log tab

This allows you to select the type of the information you want to log. The logged messages can be saved into \*.txt file.

In the lower left corner of the log tab, the evaluation board version and firmware version is displayed.

### 7.3 The Menu Bar

#### 7.3.1. The File Menu

In the **File** menu, you can select to start new projects, save current GUI project (saved in \*.ini or \*.txt format), or open previously saved project. Saved project file contains complete register setup for LMS7002M. These files can be transferred to any other computer or used as a register initialization setup for LMS7002M in baseband.

The .ini format is machine readable only.

The .txt format is human and machine readable.

#### 7.3.2. The Option Menu

In the **Options** menu, you can select the COM port to which evaluation board is attached.

43 | P a g e

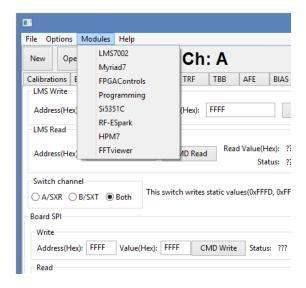

#### 7.3.3. The Modules Menu

This section has few extra control options for different RF and BB platforms, which are related with LMS7002M transceiver. When the **Modules** option is selected, new window will pop-up showing all module options available on GUI, as it is shown *Figure 27*

Figure 27 GUI Modules Menu window

### 7.3.4. The Help Menu

The help menu contains one option giving the software version and build date. It also contains the contact details for Lime Microsystems.

#### 7.3.5. The Button Menu

The button menu contains 6 buttons controls and 3 other minor controls.

The **NEW** button, enables to start new projects.

The **OPEN** button, opens previously saved project.

The **SAVE** button allows to save current GUI project (saved in \*.ini or \*.txt format). Saved project file contains complete register setup for LMS7002M. These files can be transferred to any other computer or used as a register initialization setup for LMS7002M in baseband.

The .ini format is machine readable only.

The .txt format is human and machine readable.

To write register configuration from the "LMS 7 Suite" software to the chip, press **GUI→Chip** button.

44 | P a g e

To read register configuration from the chip to the "LMS 7 Suite" software, press Chip→GUI button.

The **RESET** button performs a manual reset on the chip and updates the "LMS 7 Suite" software.

### 7.3.6. The Configuring Channel Controls

**Configuring Channels** window select which channel or PLL is currently controlled. The activated channel is always displayed in a front panel:

If selected **Both**, front panel will display: **Active Ch: SXR&SXT** or **Active Ch: A&B**.

If selected A/SXR, front panel will display: Active Ch: SXR or Active Ch: A.

If selected B/SXT, front panel will display: Active Ch: SXT or Active Ch: B.

The display shows information depending which configuration tab you are currently and which channel is selected.

The SXR option is used for setting the receive synthesizer parameters in the SXT/SXR tab (see section 7.15). The SXT option is used for setting the transmitter synthesizer parameters in the SXT/SXR tab. The A and B channel to the A and B channels for the TX and RX MIMO channels of the RFE, RBB, TRF, TBB and AFE tabs.

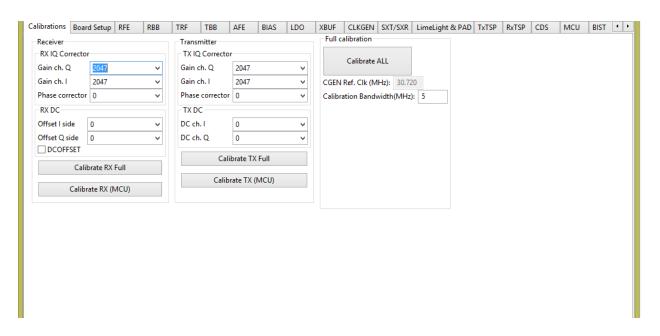

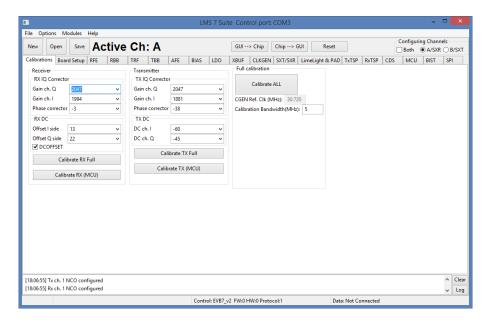

### 7.4 Calibrations

**Calibration** page has 'Receiver', 'Transmitter', 'Full Calibration' tabs as it is shown in *Figure* 28.

Figure 28 GUI Calibrations tab

Tabs 'Receiver' and 'Transmitter' has almost identical functions of calibrating Image and LO Leakage levels on respectful paths. An Image can be calibrated by controlling IQ Correction in 'Gain ch. Q' and 'Gain ch. I' fields and also changing Phase on 'Phase corrector'. LO Leakage can be calibrated be controlling 'Offset I side' and 'Offset Q side' on subtab 'RX DC' subtab and controlling 'DC ch. I' and 'DC ch. Q' on 'TX DC' subtab.

On RX DC subtab there is an option 'DCOFSET'. Selecting it enables DC Offset correction.

There are 2 additional buttons on both TX and RX paths dedicated to perform full automatic calibration routine on wanted path.

Button CALIBRATE RX FULL performs automatic calibration of Image and LO Leakage signals on RX path

Button CALIBRATE TX FULL performs automatic calibration of Image and LO Leakage signals on TX path

Button CALIBRATE RX (MCU) performs automatic calibration of Image and LO Leakage signals on RX path directly from internal MCU of LMS7002M.

Button CALIBRATE TX (MCU) performs automatic calibration of Image and LO Leakage signals on TX path directly from internal MCU of LMS7002M.

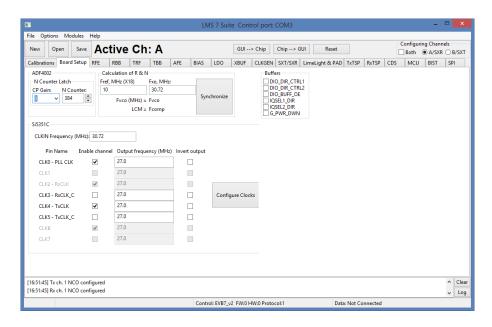

# 7.5 Board Setup (Si5351C and ADF4002)

These tabs control two other devices on the EVB7 board.

The ADF4002 is a PLL to lock an external reference (usually 10MHz on X18) with the on board TXCO (usually 30.72MHz or 52.00MHz). This 30.72MHz reference is supplied to the LMS7002M synthesizers. This is normally used to synchronize the measurement equipment with the EVB7 board remove very minor frequency differences typically a few kHz. To synchronize board:

Press 'Synchronize' button to program the ADF4002, if all is correct the green PLL locked LED (LD2) on the interface board should illuminate. LD2 is located in the upper left hand corner of the interface board

Make sure that the Fxo value corresponds to the frequency of TCXO.

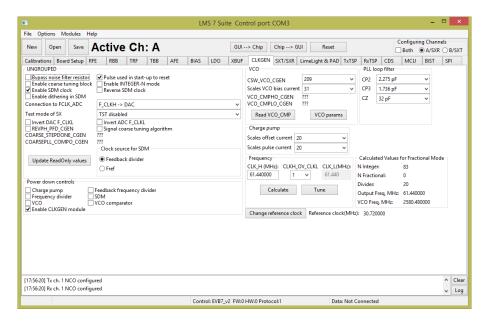

The Si5351C is a dual PLL for frequency conversion in the 10-100MHz range. It can be used to provide programmable clock signals to external hardware through the external digital interfaces and also to the LMS7002M RX and TX PLL Clocks. This allows the clock rates to be independent of the TXCO frequency. The tab is shown in *Figure 29*.

Figure 29 GUI Board Setup tab

By default, the EVB7 is configured to supply LMS7002M RX and TX PLL reference clock pins directly from TCXO. With a simple board modification, remove R10, R73 and fit R11 and R76, RX and TX PLL clocks can be supplied directly from the Si5351C clock generator.

Using this feature:

- Type to CLKIN Frequency (MHz) window the onboard TCXO frequency

- Enable clock channel

- Enter the desired output frequency

- Press "Configure Clocks"

The Buffers controls on board buffer directions for the LMS7002M digital interface. As well, LOGIC\_RESET pin and CORE\_LDO \_EN pins are controlled from this window.

Table 8 GUI SPI control description

| Parameter Description |                                                                                           |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|--|--|

|                       | Buffers                                                                                   |  |  |

| DIO_DIR_CTRL1         | On board buffers direction control for Port 1. If selected, Port 1 is receiver.           |  |  |

| DIO_DIR_CTRL2         | On board buffers direction control for Port 2. If selected, Port 2 is receiver.           |  |  |

| DIO_BUFF_OE           | If selected, sets onboard buffers to Hi-Impedance state.                                  |  |  |

| IQSEL1_DIR            | On board buffers IQSEL pin direction control for Port 1. If selected, Port 1 is receiver. |  |  |

| IQSEL2_DIR            | On board buffers IQSEL pin direction control for Port 2. If selected, Port 2 is receiver. |  |  |

| G_PWR_DWN             | External enable control signal for the internal LDO's.                                    |  |  |

| DIG_RST               | Controls hardware pin logic reset.                                                        |  |  |

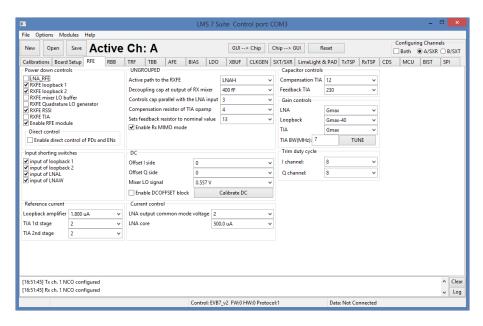

### **7.6 RFE**

Version: 26

RFE tab controls the RX Front End stages, including LNA selection, LNA gain, TIA gain and RX LO cancellation. A picture of the tab is shown in *Figure 30*. A description of each function available in this tab is shown below in *Table 9*.

Last modified: 30/10/2015

48 | P a g e

Figure 30 GUI RFE tab

Table 9 GUI RFE control description

| Parameter                       | Description                                                                                                                                   |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power down controls             |                                                                                                                                               |  |  |

| LNA_RFE                         | Power control for LNA. Must be deselected in normal operation.                                                                                |  |  |

| RXFE loopback1                  | Power control signal for RXFE loopback to LNAL from TXRF. Used only for RF loopback.                                                          |  |  |

| RXFE loopback2                  | Power control signal for RXFE loopback to LNAW from TXRF. Used only for RF loopback.                                                          |  |  |

| RXFE mixer LO buffer            | Power control signal for RXFE mixer lo buffer. Must be deselected in normal operation.                                                        |  |  |

| RXFE Quadrature<br>LO generator | Power control signal for RXFE quadrature LO generator. Must be deselected in normal operation.                                                |  |  |

| RXFE RSSI                       | Power control signal for RXFE RSSI. Enables RSSI readings when powered on.                                                                    |  |  |

| RXFE TIA                        | Power control signal for RXFE TIA. Must be deselected in normal operation.                                                                    |  |  |

| Enable RFE module               | Major power down for RXFE modules. All modules will be power down when deselected.                                                            |  |  |

| Direct control                  | Enables direct control of PDs and ENs for RFE. Enabled when selected.                                                                         |  |  |

|                                 | Input shorting switches                                                                                                                       |  |  |

| Input of loopback 1             | Enables the input shorting switch at the input of the loopback with LNAL. Should be selected when RXFE Loopback1 is NOT active.               |  |  |

| Input of loopback 2             | Enables the input shorting switch at the input of the loopback with LNAW. Should be selected when RXFE Loopback2 is NOT active.               |  |  |

| Input of LNAL                   | Enables the input shorting switch at the input of the LNAL. Should be selected when LNAH is NOT active or during very high signal conditions. |  |  |

| Input of LNAW                   | Enables the input shorting switch at the input of the LNAW. Should be selected when LNAW is NOT active or during very high signal conditions. |  |  |

| Reference current               |                                                                                                                                               |  |  |

| Loopback amplifier              | Controls reference current of the RXFE loopback amplifier. Recommended value is 1.8 uA.                                                       |  |  |

| TIA 1st Stage                   | Controls reference current of the RXFE TIA first stage. Recommended value is 2.                                                               |  |  |

| TIA 2 <sup>nd</sup> Stage       | Controls reference current of the RXFE TIA second stage. Recommended value is 2.                                                              |  |  |

|                                 | Capacitor controls                                                                                                                            |  |  |

| Compensation TIA                | Compensation capacitor for TIA. Recommended value is 15.                                                                                      |  |  |

| Feedback TIA                    | Feedback capacitor for TIA. Controls the 3 dB BW of the TIA. Recommended value is 230.                                                        |  |  |

|                                                                                         | Trim Duty Cycle                                                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I channel                                                                               | Trims the duty cycle in I channel. Default value set to 8.                                                                                                           |  |  |

| Q channel Trims the duty cycle in Q channel. Default value set to 8.                    |                                                                                                                                                                      |  |  |

|                                                                                         | UNGROUPED                                                                                                                                                            |  |  |

| Active path to the Selects the active LNA of the RXFE between LNAL, LNAH and LNAW. Defa |                                                                                                                                                                      |  |  |

| RXFE                                                                                    | no path active.                                                                                                                                                      |  |  |

| Decoupling cap at the output of RX                                                      | Control the decoupling cap at the output of the RX Mixer. The capacitor range is from 80 fF to 2560 fF, with step size of 80 fF (32 steps). Default value is 640 fF. |  |  |

| mixer                                                                                   | (* ************************************                                                                                                                              |  |  |

| Controls cap parallel                                                                   | Controls the Q of the input LNA matching circuit and provides tradeoff between gain/NF                                                                               |  |  |

| with the LNA input                                                                      | and IIP2/3. The higher the frequency, the lower value should be. Also, the higher value lower the Q. Default value is 6.                                             |  |  |

| Compensation                                                                            | Controls the compensation resistors of the TIA operational amplifier. Recommended value                                                                              |  |  |

| resistor of TIA opamp                                                                   | is 5.                                                                                                                                                                |  |  |

| Sets feedback                                                                           | Sets the TIA feedback resistor value. Default vale is 13.                                                                                                            |  |  |

| resistor value                                                                          |                                                                                                                                                                      |  |  |

| Enable Rx MIMO                                                                          | Enables MIMO mode when MIMO is selected. If SISO mode is selected only Channel A is                                                                                  |  |  |

|                                                                                         | in operation.  DC                                                                                                                                                    |  |  |

| Offset I side                                                                           | Controls DC offset of the I channel at the output of the TIA by injecting current to the input                                                                       |  |  |

|                                                                                         | of the TIA. Control range from 0 to 127. Default value is 0.                                                                                                         |  |  |

| Offset Q side                                                                           | Controls DC offset of the Q channel at the output of the TIA by injecting current to the input of the TIA. Control range from 0 to 127. Default value is 0.          |  |  |

| Mixer LO signal                                                                         | Controls DC voltage of the mixer LO signal. Control range from 0.44 V to 0.621 V. Default value is 0.557 V.                                                          |  |  |

| Enable DCOFFSET block                                                                   | Enables the DC offset block for the RXFE. Select before calibrating DC offset of the Rx path                                                                         |  |  |

|                                                                                         | Current Control                                                                                                                                                      |  |  |

| LNA output common                                                                       | Controls the LNA output common mode voltage. Control range from 0 to 31. Default value                                                                               |  |  |

| mode voltage                                                                            | is 2.                                                                                                                                                                |  |  |

| LNA Core                                                                                | Controls the current of the LNA core. Control range from 0uA to 1291.7 uA. Default value is 500 uA.                                                                  |  |  |

| Gain Controls                                                                           |                                                                                                                                                                      |  |  |

| LNA                                                                                     | Controls selected LNA gain. Control range from Gmax to Gmax-30. Default value is Gmax.                                                                               |  |  |

| Loopback                                                                                | Controls RXFE loopback gain. Control range from Gmax to Gmax-40. Default value is Gmax-40 dB.                                                                        |  |  |

| TIA                                                                                     | Controls TIA Gain. Three gain stages: Gmax, Gmax-3 dB and Gmax-12 dB. Default value is Gmax.                                                                         |  |  |

Last modified: 30/10/2015

Version: 2.6

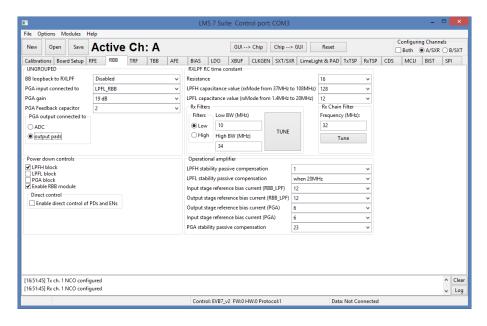

### **7.7 RBB**

RBB tab controls the receiver IF stage bandwidth, PGA gain and loopback.

Figure 31 GUI RXBB tab

A picture of the tab is shown in *Figure 31*. A description of each function available in this tab is shown below in *Table 10*.

Table 10 GUI RXBB control description

| Table 10 GUI KABB control description |                                                                                          |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Parameter Description                 |                                                                                          |  |  |

| UNGROUPED                             |                                                                                          |  |  |