## logil2S Audio Data Receiver/Transmitter

December 3<sup>rd</sup> 2014 Data Sheet Version: v2.2

## Xylon d.o.o.

Fallerovo setaliste 22 10000 Zagreb, Croatia Phone: +385 1 368 00 26 Fax: +385 1 365 51 67

E-mail: support@logicbricks.com URL: www.logicbricks.com

#### **Features**

- Supports all Xilinx® FPGA families and Zynq®-7000 All Programmable SoC

- Supports up to eight individual I<sup>2</sup>S instances with the following features:

- Configurable as receiver or transmitter

- Configurable as clock master or slave

- Configurable as word select master or slave

- Configurable active clock edge

- Supports three different justification modes:

normal (corresponds to the mode specified in the I2S specification by Philips), left and right

- Configurable TX and RX FIFO depth, from 512 up to 4096 samples (L+R word)

- · Supports word length up to 16 bits

- ARM® AMBA® AXI4-Lite compliant register interface

- Prepared for Xilinx Vivado® Design Suite (IP Integrator) and ISE® Design Suite (XPS)

| Core Facts                |                                     |  |  |

|---------------------------|-------------------------------------|--|--|

| Provided with Core        |                                     |  |  |

| Documentation             | User's Manual                       |  |  |

| Design File Formats       | Encrypted VHDL                      |  |  |

| Constraints Files         | Reference design ucf                |  |  |

| Verification/Validation   | Hardware validated                  |  |  |

| Reference Designs &       | Reference designs available for the |  |  |

| Application Notes         | Xilinx ZC702 development platform   |  |  |

| Additional Items          |                                     |  |  |

| Simulation Tool Used      |                                     |  |  |

| Mentor Graphics' Modelsim |                                     |  |  |

| Support                   |                                     |  |  |

| Support provided by Xylon |                                     |  |  |

Table 1: Example Implementation Statistics for Xilinx® FPGAs

| Family<br>(Device)                     | Fmax (MHz) | LCs  | Slices <sup>1</sup><br>(FFs/ LUTs) | IOB <sup>2</sup> | BRAM | MULT/<br>DSP48/E | DCM/<br>PLL | BUFG | GTx | Design<br>Tools  |

|----------------------------------------|------------|------|------------------------------------|------------------|------|------------------|-------------|------|-----|------------------|

| Artix <sup>®</sup> -7<br>(XC7A35T-2)   | 200        | 1293 | 202 (601/525)                      | 6                | 2    | 0                | 0           | 2    | N/A | Vivado<br>2014.3 |

| Kintex®-7<br>(XC7K70T-2)               | 200        | 1344 | 210<br>(601/522)                   | 6                | 2    | 0                | 0           | 2    | N/A | Vivado<br>2014.3 |

| ZYNQ <sup>®</sup> -7000<br>(XC7Z010-2) | 200        | 1274 | 199<br>(601/524)                   | 6                | 2    | 0                | 0           | 2    | N/A | Vivado<br>2014.3 |

#### Notes:

<sup>1)</sup> Assuming logil2S is configured to have one RX and one TX instance, clock and ws masters, normal FIFO size.

<sup>2)</sup> Assuming only audio inputs and outputs are routed off-chip and register interface is connected internally.

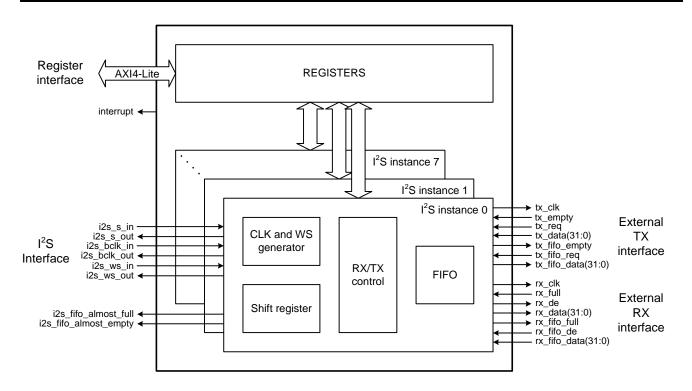

Figure 1: logil2S Architecture

## **Applications**

Human Machine Interfaces (HMI) for industrial and medical, car infotainment, defense systems, etc.

## **General Description**

The logil2S is an audio receiver and transmitter IP core from the Xylon logicBRICKS<sup>TM</sup> IP core library. It enables rapid integration of multi-channel audio functionality in Xilinx All Programmable devices and supports IP configurations with up to eight I<sup>2</sup>S transmitters and receivers, stereo audio transport between processors and codecs, configurable clock master and slave modes, etc. The logil2S IP core is fully embedded into Xilinx Vivado IP Integrator and ISE Xilinx Platform Studio implementation tools, and its integration with the on-chip AXI4 bus is very simple. Parametrizable VHDL design allows for tuning of slice consumption and features set through an easy-to-use GUI interface. The logil2S can be smoothly integrated with other logicBRICKS, Xilinx or third-partyIP cores for building of advanced GUI embedded systems.

### **Functional Description**

The Figure 1 presents internal logil2S architecture. The logil2S functional blocks are: I<sup>2</sup>S Instance and Registers. I<sup>2</sup>S Instance consists of the Clock and Word select generator, Shift register, TX and RX control logic and FIFO.

### I<sup>2</sup>S Instance

I<sup>2</sup>S instance can be configured either as an audio receiver or audio transmitter. The I<sup>2</sup>S instance configured as the audio receiver performs serial to parallel audio data conversion and stores the audio data to RX FIFO. The I<sup>2</sup>S instance configured as the audio transmitter takes data from TX FIFO and performs parallel to serial audio data conversion.

Additionally, I<sup>2</sup>S instance supports word length of up to 16 bits per channel, three sample justifications modes, four different FIFO depths, bit clock master or slave and active edge, word select master or slave and invert, left/right channel swap and configurable FIFO almost full/empty flag levels.

#### Registers

The logil2S Registers are used for configuration, data streaming and interrupt handling. The logil2S's register interface is ARM AMBA AXI4-Lite compatible.

#### **Core Modifications**

The core is supplied in an encrypted VHDL format compatible with Xilinx Vivado IP Integrator and ISE Platform Studio implementation tools. The logil2S has configuration parameters that are selectable prior to VHDL synthesis, and the following table presents a selection from a list of available parameters:

Table 2: logil2S VHDL Configuration Parameters

| Parameter                             | Description                                           |

|---------------------------------------|-------------------------------------------------------|

| C_NUM_OF_I2S                          | Number of I <sup>2</sup> S instances (1-8)            |

| C_I2S_n_DIRECTION <sup>0)</sup>       | I <sup>2</sup> S instance direction (RX, TX)          |

| C_I2S_n_CLOCKMASTER <sup>0)</sup>     | I <sup>2</sup> S instance clock slave or master       |

| C_I2S_n_WSMASTER <sup>0)</sup>        | I <sup>2</sup> S instance word select slave or master |

| C_I2S_n_CLOCKEDGE <sup>0)</sup>       | I <sup>2</sup> S instance active clock edge           |

| C_I2S_ <b>n</b> _WS_INV <sup>0)</sup> | I <sup>2</sup> S instance word select invert          |

| C_I2S_n_LR_SWAP <sup>0)</sup>         | I <sup>2</sup> S instance left/right channel swap     |

| C_I2S_n_FIFO_SIZE <sup>0)</sup>       | I <sup>2</sup> S instance FIFO size (512-4096)        |

| C_I2S_n_ALMOST_FULL <sup>0)</sup>     | I <sup>2</sup> S instance FIFO almost full level      |

| C_I2S_n_ALMOST_EMPTY <sup>0)</sup>    | I <sup>2</sup> S instance FIFO almost empty level     |

| C_I2S_n_EXT_INTERFACE <sup>0)</sup>   | I <sup>2</sup> S instance external interface usage    |

<sup>1.</sup> n is the number of I<sup>2</sup>S instance. Range is from 1 to 8.

There may be instances where source code modification is necessary. If you wish to adopt the logil2S IP core to your specific needs and/or to supplement the IP core's features set, you can allow us to tailor the logil2S IP core to your requirements.

# Core I/O Signals

The core I/O signals have not been fixed to any specific device pins to provide flexibility for interfacing with user logic. Descriptions of all I/O signals are provided in Table 3.

Table 3: Core I/O Signals

| Signal                                            | Signal<br>Direction | Description                                            |  |  |  |

|---------------------------------------------------|---------------------|--------------------------------------------------------|--|--|--|

| Global Signals                                    |                     |                                                        |  |  |  |

| interrupt                                         | Output              | logil2S interrupt signal, level sensitive, high active |  |  |  |

|                                                   | Register Interface  |                                                        |  |  |  |

| AXI4-Lite Slave Interface                         | Bus                 | Refer to ARM AMBA AXI4 specification                   |  |  |  |

| I <sup>2</sup> S Interface                        |                     |                                                        |  |  |  |

| i2s_ <b>n</b> _s_out <sup>0, 2)</sup>             | Output              | Serial I <sup>2</sup> S data output                    |  |  |  |

| i2s_ <b>n</b> _s_in 0, 3)                         | Input               | Serial I <sup>2</sup> S data input                     |  |  |  |

| i2s_ <b>n</b> _bclk_out 0, 4)                     | Output              | I <sup>2</sup> S bit clock output                      |  |  |  |

| i2s_ <b>n</b> _bclk_in 0, 5)                      | Input               | I <sup>2</sup> S bit clock input                       |  |  |  |

| i2s_ <b>n</b> _ws_out <sup>0, 6)</sup>            | Output              | I <sup>2</sup> S word select output                    |  |  |  |

| i2s_ <b>n</b> _ws_in 0,7)                         | Input               | I <sup>2</sup> S word select input                     |  |  |  |

| i2s_ <b>n</b> _fifo_almost_empty 0)               | Output              | I <sup>2</sup> S FIFO almost empty status              |  |  |  |

| i2s_n_fifo_almost_full 0)                         | Output              | I <sup>2</sup> S FIFO almost full status               |  |  |  |

|                                                   |                     | External TX interface                                  |  |  |  |

| tx_clk_ <b>n</b> 0, 2, 8)                         | Output              | External TX interface clock                            |  |  |  |

| tx_empty_ <b>n</b> 0, 2, 8)                       | Input               | External TX interface empty input                      |  |  |  |

| tx_req_ <b>n</b> 0, 2, 8)                         | Output              | External TX interface request output                   |  |  |  |

| tx_data_ <b>n</b> [31:0] <sup>0, 2, 8)</sup>      | Input               | External TX interface data input                       |  |  |  |

| tx_fifo_empty_n 0, 2, 8)                          | Output              | External TX interface FIFO empty status                |  |  |  |

| tx_fifo_req_ <b>n</b> 0, 2, 8)                    | Input               | External TX interface FIFO request input               |  |  |  |

| tx_fifo_data_ <b>n</b> [31:0] <sup>0, 2, 8)</sup> | Output              | External TX interface FIFO data output                 |  |  |  |

| External RX interface                             |                     |                                                        |  |  |  |

| rx_clk_ <b>n</b> 0, 3, 8)                         | Output              | External RX interface clock                            |  |  |  |

| rx_full_ <b>n</b> <sup>0, 3, 8)</sup>             | Input               | External RX interface full input                       |  |  |  |

| rx_de_ <b>n</b> 0, 3, 8)                          | Output              | External RX interface data enable output               |  |  |  |

| rx_data_ <b>n</b> [31:0] 0, 3, 8)                 | Output              | External RX interface data output                      |  |  |  |

| rx_fifo_full_ <b>n</b> <sup>0, 3, 8)</sup>        | Output              | External RX interface FIFO full status                 |  |  |  |

| rx_fifo_de_ <b>n</b> 0, 3, 8)                     | Input               | External RX interface FIFO data enable input           |  |  |  |

| rx_fifo_data_ <b>n</b> [31:0] <sup>0, 3, 8)</sup> | Input               | External RX interface FIFO data input                  |  |  |  |

- n is the number of I<sup>2</sup>S instances. Range is from 1 to 8.

- Valid only for transmitter I<sup>2</sup>S instances

- Valid only for receiver I<sup>2</sup>S instances

- Valid only when 12S instance is configured as clock master

Valid only when 12S instance is configured as clock slave

Valid only when 12S instance is configured as word select master

- Valid only when I<sup>2</sup>S instance is configured as word select slave Valid only if generic parameter C\_I2S\_n\_EXT\_INTERFACE is set to 1

#### **Verification Methods**

The logil2S is fully supported by the Xilinx Vivado and ISE Design Suites. This tight integration tremendously shortens IP integration and verification. A full logil2S implementation does not require any particular skills beyond general Xilinx tools knowledge. The ISE compatible version of the encrypted IP is shipped with compiled simulation libraries for Mentor Graphics' ModelSim.For information about Vivado compatible IP core simulations, please contact Xylon.

The logil2S evaluation IP core can be downloaded from Xylon web site and fully evaluated in hardware:

URL: www.logicbricks.com/Products/logil2S.aspx

## **Recommended Design Experience**

The user should have experience in the following areas:

- Xilinx design tools

- ModelSim

## **Available Support Products**

Xylon provides free pre-verified reference designs to showcase the logiBITBLT graphics accelerator, other Xylon's logicBRICKS 2D and 3D graphics hardware accelerators and display controller IP cores on the most popular Xilinx Zynq-7000 AP SoC based development kits. Reference designs include evaluation logicBRICKS IP cores and hardware design files, OS image, software drivers, demo applications and documentation.To check a full list of Xylon reference designs please visit the web:

URL: http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx

The logiREF-ZHMI-FMC Human Machine Interfaces pre-verified logicBRICKS reference design showcases the logil2S audio data receiver/transmitter and other logicBRICKS IP solutions on the Xilinx ZC702 Evaluation Kit.

To download this reference designs, learn more about the design's availability for the ZedBoard development kit, contact Xylon or visit the web:

Email: support@logicbricks.com

URL: <a href="http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/HMI-for-Xilinx-Zynq-">http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/HMI-for-Xilinx-Zynq-</a>

7000.aspx

## **Ordering Information**

This product is available directly from Xylon under the terms of the Xylon's IP License. Please visit our web shop or contact Xylon for pricing and additional information:

Email: sales@logicbricks.com www.logicbricks.com

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. Xylon products are not intended for use in the life support applications. Use of the Xylon products in such appliances is prohibited without written Xylon approval.

## **Related Information**

## Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124

Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: <u>www.xilinx.com</u>

# **Revision History**

| Version | Date        | Note                                                                                                                                                                                                                           |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00    | 23.05.2012. | Initial Xylon release – new doc template                                                                                                                                                                                       |

| 1.01    | 29.06.2012. | Added possibility to independently select master/slave for clock and word select.                                                                                                                                              |

| 2.00    | 06.12.2012. | Up to eight I <sup>2</sup> S TX or RX instances, external interface support, FIFO depth configurable up to 8x, interrupt handling changed (mask and status), almost full and empty configurable per I <sup>2</sup> S instance. |

| 2.01    | 23.01.2013. | Added tx_empty and rx_full signals to the external interfaces.                                                                                                                                                                 |

| 2.02    | 09.06.2014. | Data sheet corrections.                                                                                                                                                                                                        |

| 2.2     | 03.12.2014. | New versioning scheme introduced for Vivado packaged IP core.                                                                                                                                                                  |