# IogiADAK-VDF-SDSoC

# Video Design Framework - Reference Designs for Xylon logiADAK and logiVID-Z Development Kits

Prepared for the Xilinx<sup>®</sup> SDSoC<sup>™</sup> Development Environment

# User's Manual Version: 2.00.a

logiADAK\_VDF\_SDSoC\_v2\_00\_a.docx

October 21<sup>st</sup>, 2016

Version: v2.00.a

Designed by **XYLON**

All rights reserved. This manual may not be reproduced or utilized without the prior written permission issued by Xylon.

Copyright © Xylon d.o.o. logicBRICKS<sup>™</sup> is a registered Xylon trademark.

All other trademarks and registered trademarks are the property of their respective owners.

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure to take appropriate action so that their use of our products does not infringe upon any patents.

logic<sup>BRICKS™</sup>

Designed by XYLON

SDSoC Video Design Framework User's Manual

October 21<sup>st</sup>, 2016

Version: v2.00.a

| 1      | ABOUT THE FRAMEWORK                                                                                                                                   | 5   |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | 1.1 PROGRAMMABLE LOGIC UTILIZATION                                                                                                                    |     |

|        | 1.2 ABOUT XILINX SDSOC DEVELOPMENT ENVIRONMENT                                                                                                        |     |

|        | 1.3 HARDWARE REQUIREMENTS                                                                                                                             |     |

|        | 1.3.1 HDMI Input/Output FMC Module                                                                                                                    |     |

|        | 1.3.2 Xylon Camera<br>1.4 SOFTWARE REQUIREMENTS                                                                                                       |     |

|        | 1.5 DESIGN DELIVERABLES                                                                                                                               |     |

|        | 1.5.1 SDSoC platform                                                                                                                                  |     |

|        | 1.5.2 Software                                                                                                                                        |     |

|        | 1.5.3 Binaries                                                                                                                                        |     |

| 2      | 1.6 REFERENCE DESIGNS                                                                                                                                 |     |

| 2      |                                                                                                                                                       |     |

|        | 2.1 ABOUT LOGICBRICKS IP LIBRARY                                                                                                                      |     |

|        | <ul> <li>2.2 EVALUATION LOGICBRICKS IP CORES</li> <li>2.3 LOGICBRICKS IP CORES USED IN THIS DESIGN</li> </ul>                                         |     |

|        | 2.3.1 logiCVC-ML Compact Multilayer Video Controller                                                                                                  |     |

|        | 2.3.2 logiWIN Versatile Video Input                                                                                                                   |     |

|        | 2.3.3 logil2C I2C Bus Master                                                                                                                          |     |

|        | 2.3.4 logiVLINK Vanilla Multimedia Data Link Receiver                                                                                                 |     |

| ~      | 2.4 LOGICBRICKS IP CORES FOR VIDEO PROCESSING                                                                                                         |     |

| 3      | GET AND INSTALL THE DESIGN FRAMEWORK                                                                                                                  | .17 |

|        | 3.1 INSTALLATION PROCESS                                                                                                                              |     |

|        | 3.1.1 Filesystem Permissions of the Installed Folder (Windows 7)                                                                                      |     |

| 4      | FOLDER STRUCTURE                                                                                                                                      |     |

| -<br>5 | LOGIADAK-VDF-SDSOC REFERENCE DESIGN                                                                                                                   |     |

| Э      |                                                                                                                                                       |     |

|        | 5.1 CAM-HDMI SDSOC DESIGN AND MEMORY LAYOUT                                                                                                           |     |

|        | <ul> <li>5.2 FOUR-CAM SOC DESIGN AND MEMORY LAYOUT.</li> <li>5.3 USING THE LOGIADAK-VDF-SDSOC PLATFORMS AND THE HARDWARE ACCELERATOR BASED</li> </ul> |     |

|        | ON THE C-CODE DESCRIPTION                                                                                                                             |     |

|        | 5.4 Using and configuring Hardware Accelerator as C-code Based IP core                                                                                |     |

|        | 5.5 SOFTWARE DESCRIPTION                                                                                                                              | .28 |

|        | 5.5.1 Main function                                                                                                                                   |     |

|        | <ul><li>5.5.2 The Video input Library</li><li>5.5.3 The VideoOutput Library</li></ul>                                                                 |     |

|        | 5.5.3 The VideoOutput Library<br>5.5.4 Application control                                                                                            |     |

|        | 5.5.5 Input resolution and the framerate                                                                                                              |     |

|        | 5.5.6 Application functional and timing diagram                                                                                                       |     |

| 6      | QUICK START                                                                                                                                           | .31 |

|        | 6.1 RUN THE PRECOMPILED LINUX DEMO EXAMPLES                                                                                                           | .31 |

|        | 6.2 DEMO CONTROLS                                                                                                                                     |     |

|        | 6.3 Change the Delivered Software                                                                                                                     |     |

|        | 6.3.1 Xilinx Development Software                                                                                                                     |     |

|        | <ul><li>6.3.2 Set Up Linux System Software Development Tools</li><li>6.3.3 Set Up git Tools</li></ul>                                                 |     |

|        | 6.3.4 Setting up the SDSoC workspace                                                                                                                  |     |

|        |                                                                                                                                                       |     |

| LOGICBRICKS <sup>M</sup>        | SDSoC Video Design Framework<br>User's Manual | Xylon            |

|---------------------------------|-----------------------------------------------|------------------|

| October 21 <sup>st</sup> , 2016 |                                               | Version: v2.00.a |

|                                 | STRUCTIONS – LINUX SOFTWARE                   | -                |

| 8 REFERENCES                    |                                               |                  |

# **1 ABOUT THE FRAMEWORK**

The logiADAK-VDF-SDSoC Video Design Framework enables Xylon logiADAK Automotive Driver Assistance Kit and logiVID-Z Vision Development Kit users to quickly utilize the provided hardware platform for their own development of multi-camera computer vision systems based on the Xilinx<sup>®</sup> Zynq<sup>®</sup>-7000 All Programmable SoC.

The framework includes pre-verified logicBRICKS reference designs for video capture from Xylon video cameras and the HDMI video input, and the display output under the Linux operating system running on the Xilinx<sup>®</sup> Zynq<sup>®</sup>-7000 All Programmable SoC. Reference designs are prepared for both, hardware-centric Vivado<sup>®</sup> Design Suite and software-centric SDSoC<sup>™</sup> Development Environment. This document describes the reference designs prepared for the Xilinx SDSoC Development Environment. Xilinx Vivado compatible designs are described in the logiADAK-VDF document.

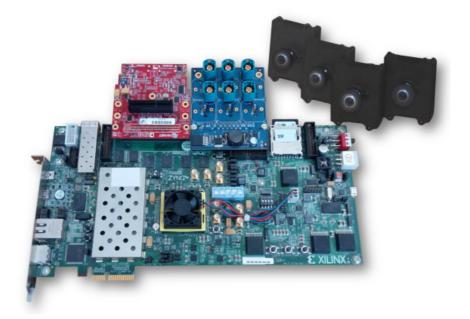

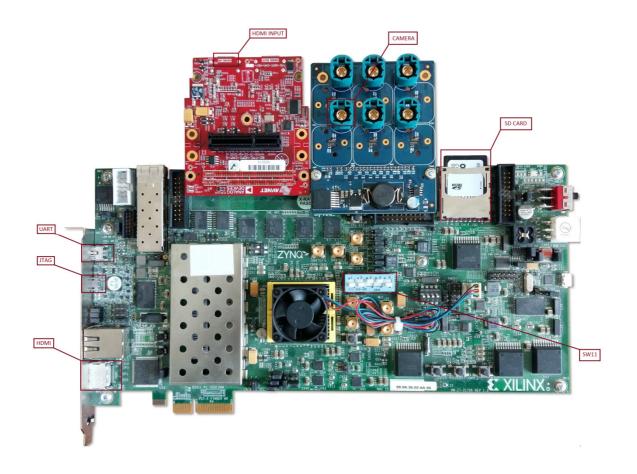

Figure 1: Xylon logiADAK Automotive Driver Assistance Kit

The complete camera-to-display SoC designs, which are compact and use just a fraction of available programmable logic, significantly save the design time. Instead of starting from scratch and having to spend months designing and building a new design framework, logiADAK-VDF-SDSoC design framework users can immediately focus on specific vision-based parts of their next SoC design for ADAS. Supported hardware platforms can be installed on test vehicles (cars, robots...) and used in exhaustive tests, i.e. for testing of the new ADAS developments in the test vehicle and under different road conditions.

The logiADAK-VDF-SDSoC reference designs include Xylon logicBRICKS IP cores and hardware design files prepared for Xilinx SDSoC Development Environment. To provide the SDSoC users the complete embedded C/C++ development experience, the supplied SDSoC reference designs include the Sobel video filter example. This example shows kit users how to integrate their own vision processing logic between video input and video output IP cores, and how to implement it in software or in programmable logic. The Linux OS and software drivers for logicBRICKS IP cores enable

software developers to efficiently work with the framework, without knowing the hardware implementation details.

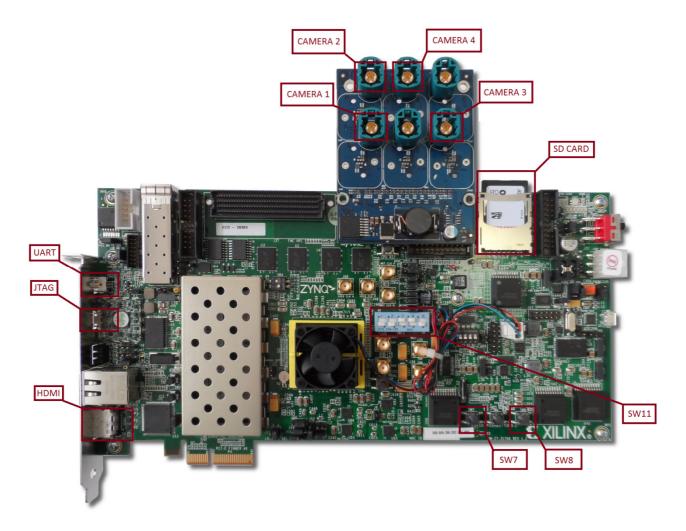

#### Figure 2: Xylon logiVID-Z Vision Development Kit

The logiADAK-VDF-SDSoC Video Design Framework is functionally equal to Xylon's logiADAK-VDF Video Design Framework reference design, which is implemented fully in the Xilinx Vivado® Design Suite.

# **1.1 Programmable Logic Utilization**

The logiADAK-VDF-SDSoC reference designs utilize just small fractions (Table 3) of available programmable logic in the Xilinx Zynq-7000 AP SoC XC7Z045 device. Free resources can be utilized by users who can also alter the pre-defined logicBRICKS configurations and change the programmable logic utilization.

| E                                     |           | F (MHz)  |      |       | 01:1                   |                  |     | BRAM Tile       | MULT/ | DCM      |     | Design           |

|---------------------------------------|-----------|----------|------|-------|------------------------|------------------|-----|-----------------|-------|----------|-----|------------------|

| Family<br>(Device)                    | mclk⁴     | vclk⁴    | rclk | LCs   | Slices¹<br>(FFs/ LUTs) | IOB <sup>2</sup> | СМТ | (RAMB36/RAMB18) |       | /<br>СМТ | GTx |                  |

| Zynq-7000 <sup>3</sup><br>(XC7Z045-2) | (150/100) | (80/100) | 100  | 14803 | 2313<br>(7464/ 5835)   | 60               | 0   | 11<br>(5/12)    | 7     | 0        | 0   | Vivado<br>2016.2 |

#### Table 1: CAM-HDMI Reference Design Programmable Logic Utilization

#### Table 2: FOUR-CAM Reference Design Programmable Logic Utilization

| Family                                |                   | F (MHz)                                                                                  |     |       | Sliege <sup>1</sup>    |         |          | BRAM Tile     | MULT/ | DCM |   | Design           |

|---------------------------------------|-------------------|------------------------------------------------------------------------------------------|-----|-------|------------------------|---------|----------|---------------|-------|-----|---|------------------|

| Family<br>(Device)                    | mclk <sup>4</sup> | clk <sup>4</sup> vclk <sup>4</sup> rclk     LCs     Slices <sup>1</sup> IOB <sup>2</sup> |     | СМТ   |                        | DSP48/E | /<br>СМТ | GTx           |       |     |   |                  |

| Zynq-7000 <sup>3</sup><br>(XC7Z045-2) | (150/100)         | (80/100)                                                                                 | 100 | 46048 | 7195<br>(23754/ 18551) | 49      | 0        | 65<br>(17/96) | 28    | 0   | 0 | Vivado<br>2016.2 |

Notes:

1) Assuming the following configuration: ITU656, RGB565 output, 32-bit AXI4-Lite register interface, 64-bit AXI4 memory interface with max. burst size of 64 words, scaling in both directions with multipliers (DSP48s), output stride set to 1024 pixels

2) Assuming only video inputs are routed off-chip, register and memory interfaces are connected internally

3) Only burst size of 16 words is supported on HP ports in the Xilinx Zynq-7000 SoC

4) logiCVC/logiWIN clock frequencies

#### **Table 3: Free Programmable Logic Resources**

|                        | Available in XC7Z045  | Used Res | ources   |

|------------------------|-----------------------|----------|----------|

|                        | Available III AC72045 | CAM-HDMI | FOUR-CAM |

| Logic Cells (LCs)      | 350K                  | ~ 4%     | ~ 13%    |

| Flip Flops (FFs)       | 437,200               | ~ 2%     | ~ 5%     |

| Look-Up Tables (LUTs)  | 218,600               | ~ 3%     | ~ 8%     |

| Block RAM (36 kB BRAM) | 545                   | ~ 3%     | ~ 20%    |

| DSP slices (MULT/DSP)  | 900                   | ~ 1%     | ~ 3%     |

### 1.2 About Xilinx SDSoC Development Environment

The Xilinx SDSoC development environment is a member of the Xilinx SDx<sup>™</sup> family that provides a greatly simplified ASSP-like C/C++ programming experience including an easy to use Eclipse IDE and a comprehensive design environment for heterogeneous Zyng® All Programmable SoC and MPSoC deployment.

Complete with the industry's first C/C++ full-system optimizing compiler, SDSoC delivers system level profiling, automated software acceleration in programmable logic, automated system connectivity generation, and libraries to speed programming.

To access the capabilities of SDSoC, please visit www.xilinx.com/sdsoc

Xylon is an SDSoC development environment-qualified Xilinx Alliance Member and offers logicBRICKS IP cores, complete Xilinx All Programmable based solutions and design services.

### **1.3 Hardware Requirements**

The logiADAK Automotive Driver Assistance Kit (Figure 1) includes the following hardware, which is utilized by reference designs provided in the logiADAK-VDF-SDSoC design framework:

- 1x Xilinx Zynq-7000 SoC ZC706 Development Kit<sup>1</sup> with XC7Z045 FFG900 -2 AP SoC

- 1x Xylon FMC add-on board for up to 6 camera connections

- 5x Xylon Cameras

- 1x SD card

- 5x Rosenberger cables

Learn more about the logiADAK kit: http://www.logicbricks.com/Products/logiADAK.aspx

The logiVID-Z Vision Development Kit (Figure 2) includes the following hardware, which is utilized by reference designs provided in the logiADAK-VDF design framework:

- 1x Xilinx Zynq-7000 SoC ZC706 Development Kit<sup>1</sup> with XC7Z045 FFG900 -2 AP SoC

- 1x Xylon FMC add-on board for up to 6 camera connections

- 1x Avnet HDMI Input/Output FMC Module

- 4x Xylon Cameras

- 1x SD card

- 4x Rosenberger cables

- Power supply

Learn more about the logiVID-Z kit: <u>http://www.logicbricks.com/Products/logiVID-Z.aspx</u>

<sup>1</sup> – OEM kit version without the Xilinx Vivado Design Suite seat

#### **1.3.1 HDMI Input/Output FMC Module**

The CAM-HDMI reference design delivered with the logiADAK-VDF-SDSoC requires the HDMI Input/Output FMC module (Figure 3), which is available with the logiVID-Z kit and not included with the Xylon logiADAK Kit. In order to use this reference design, the logiADAK kit users needs to purchase the HDMI Input/Output FMC module from Avnet (Part Number: AES-FMC-HDMI-CAM-G).

Figure 3: Avnet HDMI Input/Output FMC Module

#### 1.3.2 Xylon Camera

For transmissions of the high-definition uncompressed video and camera control data, Xylon kits include hardware and software that is completely developed by Xylon: the LVDS-based serial interface, the Xylon video camera and an add-on LVDS FMC receiver board for up to six camera connections to the video processor implemented in the Xilinx Zynq-7000 AP SoC.

Each Xylon video camera (Figure 1) includes the OmniVision OV10635 1-megapixel camera sensor that combines high-definition 1280x800p30 WXGA (HD) video with the color high dynamic range (HDR) functionality, LVDS serializer (transmitter) board, the Sunex DSL219 miniature fish-eye Wide FOV lens and a short cable lead with a connector. The logiADAK kit also includes the 5th camera equipped with the Sunex DSL947 Narrow Field of View (FOV) miniature lens, which is in Xylon ADAS demos used for the forward-looking collision avoidance and in-cabin driver status monitoring.

All camera parts are enclosed in the waterproof aluminium housing. The housing is sealed with rubber gaskets to ensure a weather-proof rating of IP67. Its rugged metal construction provides excellent lens and imager module protection and enables safe and easy test vehicle installations.

### **1.4 Software Requirements**

The logiADAK-VDF-SDSoC reference designs and Xylon logicBRICKS IP cores are fully compatible with Xilinx SDSoC Development Environment 2016.2. Future design releases shall be synchronized with the newest Xilinx development tools.

# 1.5 Design Deliverables

#### 1.5.1 SDSoC platform

• Two reference designs prepared for Xilinx SDSoC Development Environment

Designed by XYLON

SDSoC Video Design Framework User's Manual

October 21<sup>st</sup>, 2016

Version: v2.00.a

- Contains the pre-built hardware files for faster software development

- Supports Linux applications

- Includes software drivers for included logicBRICKS IP cores

- Xylon evaluation logicBRICKS IP cores:

- logiCVC-ML Compact Multilayer Video Controller

- logiWIN Versatile Video Input

- logil2C I2C Bus Master Controller

- logiVLINK Vanilla LVDS Multimedia Data Link Receiver

#### 1.5.2 Software

- Linux user space drivers with driver examples

- Demo application sources

- Bare-metal software drivers for logicBRICKS IP cores

#### 1.5.3 Binaries

- Precompiled SD Card image for the fastest demo startup

- Camera/HDMI demoes

- Four Camera demoes

# **1.6 Reference Designs**

The logiADAK-VDF-SDSoC video design framework includes two reference designs:

- FOUR-CAM reference design implements four parallel video inputs from Xylon cameras, and the display output with RGB graphic overlay. All video inputs are stored in the video memory, and by mean of the on-board push buttons, the design user can select each of them for the full screen display output. The design also includes the Sobel filter example to show framework users how to add their own vision processing logic.

- CAM-HDMI reference design implements a single video input, and the display output with the RGB graphic overlay. The video input can be sourced from the attached Xylon video camera, or through the HDMI video input. The HDMI video input is particularly suited for use with PC and playback of prepared test videos, such as the video recordings of road and traffic situations that make test cases for the video ADAS processing. The design displays out a single video source, filtered with the Sobel filter, and automatically switches to the HDMI video input upon detection of the plugged-in HDMI cable. The Sobel example shows kit users how to integrate their own vision processing logic between video input and video output IP cores, and how to implement it in software or in programmable logic.

# 2 LOGICBRICKS IP CORES

# 2.1 About logicBRICKS IP Library

Xylon's logicBRICKS IP core library provides IP cores optimized for Xilinx All Programmable FPGA and SoC devices. The logicBRICKS IP cores shorten development time and enable fast design of complex embedded systems based on Xilinx All Programmable devices.

The key features of the logicBRICKS IP cores are:

- logicBRICKS can be used in the same ways as Xilinx IP cores within the Xilinx Vivado Design Suite and require no skills beyond general tools knowledge. IP users can setup feature sets and programmable logic utilization through implementation tools' Graphical User Interface (GUI).

- Each logicBRICKS IP core comes with the extensive documentation, reference design examples and can be evaluated on reference hardware platforms. Xylon provides evaluation logicBRICKS IP cores to enable risk-free evaluation prior to purchase.

- Broad software support from bare-metal software drivers to standard software drivers for different operating systems (OS). Standard software support allows graphics designers and software developers to use logicBRICKS in a familiar and comfortable way.

- Xylon assures skilled technical support.

| Search: Q                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Name ^ 1                                                                                                                                                                                                                                                                                                                                                                                                              | AXI4                                                                                                                                                                         | Status                                                                                     | License                                                                | VLNV                                                                                                                                |

| Alliance Partners                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| 🖻 🗁 Xylon                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| 2D Graphics Accelerator Bit Block Transfer                                                                                                                                                                                                                                                                                                                                                                            | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logibitblt:5.3                                                                                          |

| # Audio I2S Transmitter/Receiver                                                                                                                                                                                                                                                                                                                                                                                      | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logii2s:0.0                                                                                             |

| Bitmap 2.5D Graphics Accelerator                                                                                                                                                                                                                                                                                                                                                                                      | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logibmp:0.0                                                                                             |

| 📲 I2C Bus Master Controller                                                                                                                                                                                                                                                                                                                                                                                           | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logii2c:0.0                                                                                             |

| Multilayer Video Controller                                                                                                                                                                                                                                                                                                                                                                                           | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logicvc:4.1                                                                                             |

| Perspective Transformation and Lens Correction                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                              |                                                                                            | Included                                                               | logicbricks.com:logicbricks:logiview:0.0                                                                                            |

| Scalable 3D Graphics Accelerator                                                                                                                                                                                                                                                                                                                                                                                      | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logi3d:1.5                                                                                              |

| P SD Card Host Controller                                                                                                                                                                                                                                                                                                                                                                                             | AXI4                                                                                                                                                                         | Production                                                                                 | Included                                                               | logicbricks.com:logicbricks:logisdhc:0.0                                                                                            |

| 🗄 🗁 Automotive & Industrial                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| AXI Infrastructure                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| BaseIP                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| 🗄 🗁 Basic Elements                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Communication & Networking                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| 🗄 🗁 Debug & Verification                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Digital Signal Processing                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Embedded Processing                                                                                                                                                                                                                                                                                                                                                                                                   | W                                                                                                                                                                            |                                                                                            |                                                                        |                                                                                                                                     |

| Details                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Name: Multilaver Video Controller                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Version: 4.1 (Rev. 2)                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |                                                                                            |                                                                        |                                                                                                                                     |

| Version: 4.1 (Rev. 2)                                                                                                                                                                                                                                                                                                                                                                                                 | I as a standalone graphics IP core, or as<br>, supported by the Xilinx Vivado IP Integ<br>and feature set can be easily adjusted t<br>driver, documentation and an example d | a part of larger gra<br>rator (IPI) integrat<br>rrough IP drag and<br>esign. Higher resolu | phics systems<br>ed software so<br>drop IPI interf<br>itions are avail | along other Xylon logicBRICKS IP cores.<br>lution, and designers familiar with this tool<br>ace. The logiCVC-ML comes readya-to-use |

| Version: 4.1 (Rev. 2)<br>Interfaces: AX14<br>Description: The loc/IC-VML IP core is an advanced display<br>Zymq-7000 AP SoC and PFGA.1 Ic and e used<br>The loc/IC-VML is a real blug-and-play IP core<br>can immediately start designing. The IP's size<br>and with rich set of deverables including SW                                                                                                              | I as a standalone graphics IP core, or as<br>, supported by the Xilinx Vivado IP Integ<br>and feature set can be easily adjusted t<br>driver, documentation and an example d | a part of larger gra<br>rator (IPI) integrat<br>rrough IP drag and<br>esign. Higher resolu | phics systems<br>ed software so<br>drop IPI interf<br>itions are avail | along other Xylon logicBRICKS IP cores.<br>lution, and designers familiar with this tool<br>ace. The logiCVC-ML comes readya-to-use |

| Version: 4.1 (Rev. 2)<br>Interfaces: AU14<br>Description: The log/ICVAIL IP core is an advanced display<br>Zymq-2000 AP SoC and FPGAs. It can be used<br>The log/ICVAIL is are all outpa-and-pair. The IP's size<br>and with rinds set of deversables induding SW<br>software drivers for use with Linux, Android a                                                                                                   | I as a standalone graphics IP core, or as<br>, supported by the Xilinx Vivado IP Integ<br>and feature set can be easily adjusted t<br>driver, documentation and an example d | a part of larger gra<br>rator (IPI) integrat<br>rrough IP drag and<br>esign. Higher resolu | phics systems<br>ed software so<br>drop IPI interf<br>itions are avail | along other Xylon logicBRICKS IP cores.<br>lution, and designers familiar with this tool<br>ace. The logiCVC-ML comes readya-to-use |

| Version: 4.1 (Rev. 2)<br>Interfaces: AX14<br>Description: The log(CIC:ML IP core is an advanced display<br>Zymq-7000 AP SoC and FPGAs. It can be used<br>The log(CIC:ML is a real plug-and-play IP core<br>can immediately start desgring. The IP's see<br>and with rich set of deliverables induding SW<br>software drivers for use with Linux, Android a<br>Status: <u>Production</u>                               | I as a standalone graphics IP core, or as<br>, supported by the Xilinx Vivado IP Integ<br>and feature set can be easily adjusted t<br>driver, documentation and an example d | a part of larger gra<br>rator (IPI) integrat<br>rrough IP drag and<br>esign. Higher resolu | phics systems<br>ed software so<br>drop IPI interf<br>itions are avail | along other Xylon logicBRICKS IP cores.<br>lution, and designers familiar with this tool<br>ace. The logiCVC-ML comes readya-to-use |

| Version: 4.1 (Rev. 2)<br>Interfaces: AX14<br>Description: The log/CVC-ML IP core is an advanced display<br>20mg -2000 AP SoC and FPGAs. It can be used<br>The log/CVC-ML is a real plug-and-play IP core<br>can immediately start desgring. The IP's size i<br>and with rich set of deliverables including SW of<br>software drivers for use with Linux, Android an<br>Status: <u>Production</u><br>License: Included | I as a standalone graphics IP core, or as<br>, supported by the Xilinx Vivado IP Integ<br>and feature set can be easily adjusted t<br>driver, documentation and an example d | a part of larger gra<br>rator (IPI) integrat<br>rrough IP drag and<br>esign. Higher resolu | phics systems<br>ed software so<br>drop IPI interf<br>itions are avail | along other Xylon logicBRICKS IP cores.<br>lution, and designers familiar with this tool<br>ace. The logiCVC-ML comes readya-to-use |

Figure 4: logicBRICKS IP Cores Imported into the Vivado IP Catalog

The Figure 4 shows imported logicBRICKS IP cores into Vivado Design Suite, while the Figure 5 shows a typical logicBRICKS IP core's configuration GUI.

#### Figure 5: Example of logicBRICKS IP Configuration GUI

To access logicBRICKS IP cores' user's manuals, double-click on the specific IP core's icon to open the IP core GUI and click on the Documentation icon. Choose either Product guide to open the manual or Change Log to open IP core's change log.

logicBRICKS User's Manuals contain all necessary information about the IP cores' features, architecture, registers, modes of operation, etc.

# 2.2 Evaluation logicBRICKS IP Cores

Xylon offers free evaluation logicBRICKS IP cores which enable full hardware evaluation:

- Import into the Xilinx Vivado tools (IP Integration)

- IP parameterization through the GUI interface

- Simulation (if Xilinx tools support it)

- Bitstream generation

| logicBRICKS <sup>™</sup>     |

|------------------------------|

| Designed by XYLON            |

| October 21 <sup>st</sup> 201 |

The logicBRICKS evaluation IP cores are run-time limited and cease to function after some time. Proper operation can be restored by reloading the bitstream. Besides this run-time limitation, there are no other functional differences between the evaluation and fully licensed logicBRICKS IP cores.

Evaluation logicBRICKS IP cores are distributed as parts of the Xylon reference designs: http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx.

Specific IP cores can be downloaded from Xylon's web shop: <u>http://www.logicbricks.com/Products/IP-Cores.aspx</u>.

# 2.3 IogicBRICKS IP Cores Used in This Design

#### 2.3.1 logiCVC-ML Compact Multilayer Video Controller

The logiCVC-ML IP core is an advanced display graphics controller for LCD and CRT displays, which enables an easy video and graphics integration into embedded systems with Xilinx Zynq-7000 All Programmable SoC and FPGAs.

This IP core is the cornerstone of all 2D and 3D GPUs. Though its main function is to provide flexible display control, it also includes hardware acceleration functions: three types of alpha blending, panning, buffering of multiple frames, etc.

- Supports all Xilinx FPGA families

- Supports LCD and CRT displays (easily tailored for special display types)

- 64x1 to 2048x2048 display resolutions

- Available SW drivers for: Linux, Android, QNX and Microsoft Windows Embedded Compact OS

- Support for higher display resolutions available on request

- Supports up to 5 layers; the last one configurable as a background layer

- Configurable layers' size, position and offset

- Alpha blending and Color keyed transparency

- Pixel, layer, or Color Lookup Table (CLUT) alpha blending mode can be independently set for each layer

- Packed pixel layer memory organization:

- RGB 8bpp, 8bpp using CLUT, 16bpp Hi-color RGB 565 and True-color 24bpp

- YCbCr 16bpp (4:2:2) and 24bpp (4:4:4)

- Configurable CoreConnect<sup>™</sup> PLBv4.6, Xylon XMB or ARM<sup>®</sup> AMBA<sup>®</sup> AXI4 memory interface data width (32, 64 or 128)

- Programmable layer memory base address and stride

- Simple programming due to small number of control registers

- Support for multiple output formats:

- Parallel display data bus (RGB): 12x2-bit, 15-bit, 16-bit, 18-bit or 24-bit

- YCbCr 4:4:4 or 4:2:2 output format

- Digital Video ITU-656: PAL and NTSC

- LVDS output format: 3 or 4 data pairs plus clock

- Camera link output format: 4 data pairs plus clock

October 21<sup>st</sup>, 2016

Version: v2.00.a

- DVI output format

- Supports synchronization to external parallel input

- HW cursors

- Versatile and programmable sync signals timing

- Double/triple buffering enables flicker-free reproduction

- Display power-on sequencing control signals

- Parametrical VHDL design that allows tuning of slice consumption and features set

- Prepared for Xilinx Vivado tools

More info: <u>http://www.logicbricks.com/Products/logiCVC-ML.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiCVC-ML\_hds.pdf</u>

#### 2.3.2 logiWIN Versatile Video Input

.

The logiWIN IP core enables easy implementation of video frame grabbers. Input video can be decoded, real-time scaled, de-interlaced, cropped, antialiased, positioned on the screen... Multiple logiWIN instances enable processing of multiple video inputs by a single Xilinx device.

- Supports versatile digital video input formats:

- ITU656 and ITU1120 (PAL and NTSC)

- RGB

- YUV 4:2:2

- Maximum input and output resolutions are 2048 x 2048 pixels

- Built-in YcrCb to RGB converter, YUV to RGB converter and RGB to YcrCb converter

- Embedded image color enhancements: contrast, saturation, brightness and hue for ITU and YUV separately

- Real-time video scale-up (zoom in) up to 64x

- Real-time video scale-down (zoom out) down to 16 times

- Lossless scaling down to 2x, or 4x in cascade scaling mode

- Supports video input cropping and smooth image positioning

- Configurable register interface: CoreConnect<sup>™</sup> OPB or PLBv46 and ARM® AMBA® AXI4-Lite

- ARM<sup>®</sup> AMBA<sup>®</sup> AXI4 and AXI4-Lite bus compliant

- Compressed stencil buffer in BRAM (mask over output buffer)

- Supports pixel alpha blending

- Provides "Bob" and "Weave" de-interlacing algorithms

- Supported big and little Endianness memory layout

- Double or triple buffering for flicker-free video

- Prepared for Xilinx Vivado tools

More info: <u>https://www.logicbricks.com/Products/logiWIN.aspx</u> Datasheet: <u>https://www.logicbricks.com/Documentation/Datasheets/IP/logiWIN\_hds.pdf</u>

October 21<sup>st</sup>, 2016

Version: v2.00.a

### 2.3.3 logil2C I2C Bus Master

The logil2C is Xylon logicBRICKS IP core compatible with the I2C serial bus interface standard. The IP core supports single master I2C communications and enables bug-free data transfers.

- Master I2C serial bus controller

- Supports single master operation

- ARM<sup>®</sup> AMBA<sup>®</sup> AXI4-Lite bus compliant

- 16 locations deep TX and RX data FIFO

- Supported transmission speeds:

- Normal 100 Kbps

- Fast 400 Kbps

- High speed 3.5 Mbps

- Prepared for Xilinx Vivado tools

More info: https://www.logicbricks.com/Products/logiWIN.aspx Datasheet: https://www.logicbricks.com/Documentation/Datasheets/IP/logiWIN hds.pdf

#### 2.3.4 logiVLINK Vanilla Multimedia Data Link Receiver

The logiADAK and the logiVID-Z kits integrate proprietary logicBRICKS LVDS Camera Interface serial link for joint transmissions of high-speed video, audio and control data. Xylon ADAS solutions have been already successfully used in projects incorporating other video links (examples: TI FPD-Link III, Ethernet...) for video transmissions between different video cameras and the Zyng-7000 AP SoC or FPGA device. More info: info@logicbricks.com

# 2.4 logicBRICKS IP Cores for Video Processing

Xylon offers several logicBRICKS IP cores for video processing on Xilinx FPGA and SoC programmable devices:

#### **IogiVIEW Perspective Transformation and Lens Correction Image Processor**

Removes fish-eye lens distortions and executes programmable transformations on multiple video inputs in a real time. Programmable homographic transformation enables: cropping, resizing, rotating, transiting and arbitrary combinations. Arbitrary non-homographic transformations are supported by programmable Memory Look-Up Tables (MLUT).

More info: http://www.logicbricks.com/Products/logiVIEW.aspx Datasheet: http://www.logicbricks.com/Documentation/Datasheets/IP/logiVIEW hds.pdf

Xylon

Version: v2.00.a

#### logilSP Image Signal Processing (ISP) Pipeline

The logiISP Image Signal Processing Pipeline IP core is a full high-definition ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx Zynq-7000 All Programmable SoC and 7 Series FPGA devices.

More info: <u>http://www.logicbricks.com/Products/logiISP.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiISP\_hds.pdf</u>

#### logiHDR High Dynamic Range (HDR) Pipeline

Ultra High Definition (UHD, including 4K2Kp60) HDR pipeline for camera image quality enhancements. Enables extraction of the maximum detail from high-contrast scenes, i.e. scenes with objects highlighted by a direct sunlight and objects placed in extreme shades.

More info: <u>http://www.logicbricks.com/Products/logiHDR.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiHDR\_hds.pdf</u>

# **3 GET AND INSTALL THE DESIGN FRAMEWORK**

To download the evaluation version and to purchase the design framework, please visit our online catalog: <u>http://www.logicbricks.com/Products/logiADAK-VDF.aspx</u>

#### 3.1 Installation Process

Installation process is quick and easy. The logiADAK-VDF-SDSoC framework can be downloaded as a cross-platform Java JAR self-extracting installer. Please make sure that you have a copy of the JRE (Java Runtime Environment) version 6 or higher on your system to run Java applications and applets. Double-click on the installer's icon to run the installation.

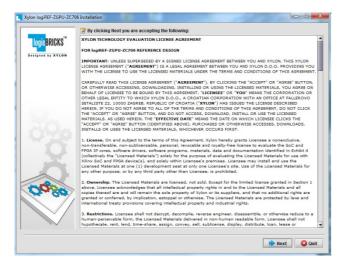

At the beginning, you will be requested to accept the design framework license – Figure 6. For installation in Linux OS, please follow instructions:

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/Xylon-Reference-Designs-Linux-Installation.aspx.

If you agree with the conditions from the Xylon license, click NEXT and select the installation path for your logicBRICKS reference design (Figure 7). The installation process takes several minutes. It generates the folder structure described in the paragraph 3.1.1 Folder Structure.

Xylon logiREF-ZGPU-ZC70

Figure 6: Installation Process – Step 1

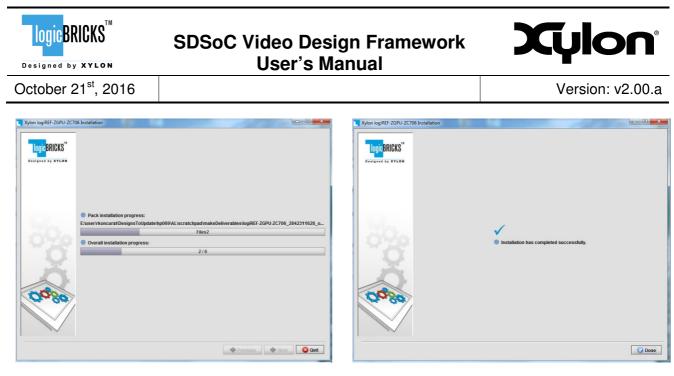

Figure 7: Installation Process – Step 2

Figure 8: Installation Process – Step 3

Figure 9: Installation Process – Step 4

### 3.1.1 Filesystem Permissions of the Installed Folder (Windows 7)

The reference design installed in the default path C:\Program Files\xylon will inherit read-only filesystem permissions from the parent folder. This will block you in opening the hardware project file in Xilinx Vivado tools. Therefore it is necessary to change the filesystem permissions for the current user to "Full control" preferably.

To change the user permissions for C:\Program Files\xylon folder and all of its subdirectories, right click on the C:\Program Files\xylon folder and select "Properties". Under "Security" tab select "Edit". Select "Users" group in the list and check "Full control" checkbox in the "Allow" column.

# Folder Structure

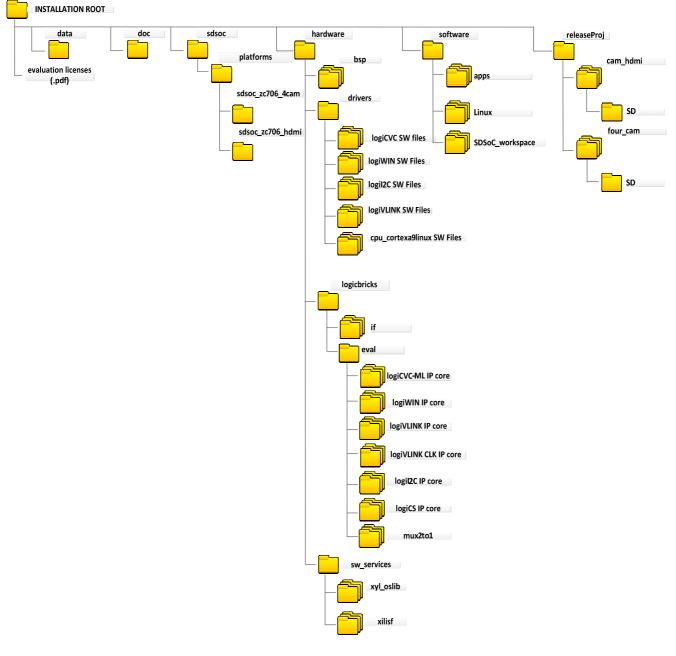

Figure 10 gives a top level view of the directories and files included with the logiADAK-VDF-SDSoC video design framework. Table 4 explains the purpose of directories.

Figure 10: Folder Structure

October 21<sup>st</sup>, 2016

Version: v2.00.a

|                  | Folder           | Purpose                                                                                                                                                                                                 |  |  |  |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INSTALLATIO      | N ROOT           | This folder contains the <i>start.html</i> page – the jump-start                                                                                                                                        |  |  |  |

|                  |                  | navigation page through the reference design.                                                                                                                                                           |  |  |  |

| doc              |                  | Project documentation.                                                                                                                                                                                  |  |  |  |

| sdsoc/platf      | orms             | SDSoC platform files                                                                                                                                                                                    |  |  |  |

| sdsoc_zc706_hdmi |                  | Cam/hdmi platform files                                                                                                                                                                                 |  |  |  |

|                  | sdsoc_zc706_4cam | Four cam platform files                                                                                                                                                                                 |  |  |  |

| hardware         |                  |                                                                                                                                                                                                         |  |  |  |

|                  | bsp              | Xylon Linux user space Board Support Package (BSP);<br>custom Xylon BSP compatible with the Xilinx SDK. It<br>enables users to quickly build Linux User space<br>applications within the SKD workspace. |  |  |  |

|                  | drivers          | Standalone (bare-metal) drivers for logicBRICKS IP cores with documentation and examples.                                                                                                               |  |  |  |

|                  | logicbricks/if   | Xylon custom IP core interfaces (bus definitions).                                                                                                                                                      |  |  |  |

|                  | logicbricks/eval | Evaluation logicBRICKS IP cores. IP cores' User's Manuals are stored in doc subdirectories.                                                                                                             |  |  |  |

|                  | sw_services      | xyl_oslib - Xylon OS abstraction library for Xilinx<br>Xilkernel embedded kernel - use in standalone (non-OS)<br>applications.                                                                          |  |  |  |

| software         | <b>-</b>         |                                                                                                                                                                                                         |  |  |  |

|                  | apps             | Demo applications source code files                                                                                                                                                                     |  |  |  |

|                  | Linux/kernel     | Linux kernel and device tree configuration files.                                                                                                                                                       |  |  |  |

|                  | SDSoC_workspace  | Xilinx SDSoC workspace folder for building bare-metal applications.                                                                                                                                     |  |  |  |

| releaseProj      |                  | Prepared binaries ready for download to SD card.                                                                                                                                                        |  |  |  |

|                  | cam_hdmi/SD      | Cam/hdmi platform with hardware implemented sobel filter                                                                                                                                                |  |  |  |

|                  | four_cam/SD      | Four cam platform with hardware implemented sobel filter                                                                                                                                                |  |  |  |

#### Table 4: Explanation of the logiADAK-VDF folder structure

# 4 GETTING LOGICBRICKS IP LICENSES

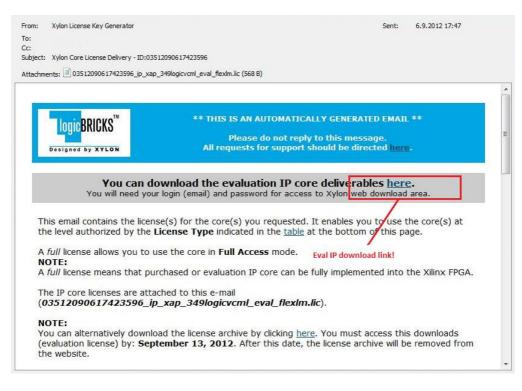

The logiADAK-VDF-SDSoC installation comes with the evaluation versions of the logicBRICKS IP cores, and in order to be able to change the provided reference designs, you need to request the proper licenses from Xylon.

Please contact Xylon Technical Support Service <u>support@logicbricks.com</u> and immediately provide your Ethernet MAC ID number or Sun Host ID.

For instructions how to find your Ethernet MAC or host ID, please visit: <a href="http://www.logicbricks.com/Documentation/Article.aspx?articleID=KBA-01186-M0JXKD">http://www.logicbricks.com/Documentation/Article.aspx?articleID=KBA-01186-M0JXKD</a>.

For each logicBRICKS IP core used in the logiADAK-VDF-SDSoC reference designs Xylon will generate and send to you separated e-mails with the license keys (file) and full instructions for setting up the license key and downloading the logicBRICKS IP core. Please follow the provided instructions.

If you experience any troubles during the registration process, please contact Xylon Technical Support Service – <u>support@logicbricks.com</u>.

#### Figure 11: E-mail with logicBRICKS License and Download Instructions

Designed by XYLON

# 5 LOGIADAK-VDF-SDSOC REFERENCE DESIGN

The logiADAK-VDF- SDSoC referent design contains two SDSoC platform designs:

- sdsoc\_zc706\_hdmi

- sdsoc\_zc706\_4cam

Xylon's platforms for the targeted hardware kit are designed following Xilinx's SDSoC platform design specifications [REF 2].

Platform designs are based on the logiADAK-VDF reference designs functionality with an addition of the Sobel filter implementation. The Sobel filter is implemented between an active input and the display output. Filter implementation provides a simple example how to implement C-code based accelerator in the Programmable Logic within the SDSoC design environment.

The sdsoc\_zc706\_hdmi and sdsoc\_zc706\_4cam platforms support Linux applications and include precompiled Linux drivers for all logicBRICKS IP cores. Linux and Bare-metal software drivers source files are included within the reference design deliverables – please see the Table 4.

The provided platforms also include the pre-built SoC hardware folder for faster user workflow described in [REF 3]. The SoC configuration bitstream, which is contained in the platform hardware folder, enables users to run and verify custom developed applications, entirely in software and without engaging in the lengthy process of hardware implementation. However, that process cannot be used with the provided demo application when the Sobel filter is marked for hardware acceleration. Alternatively, user can generate bitstream for the Cam/HDMI and Four-Cam applications and then uncheck the **Generate Bit Stream**. It will enable the tools to rebuild only software portions of the design.

# 5.1 CAM-HDMI SDSoC Design and Memory Layout

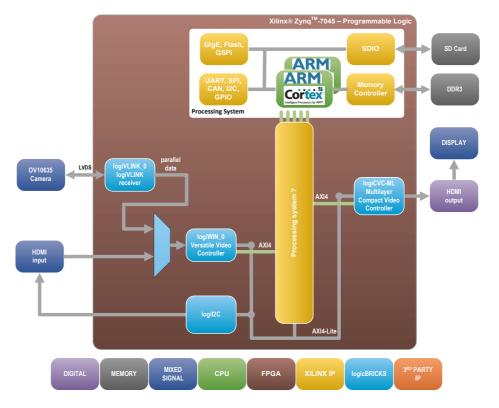

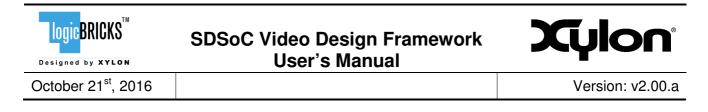

This platform design (Figure 12) supports a single video camera or a single HDMI video input (only one active at a time), and the single display output.

The following Zynq SoC resources are not used by the **sdsoc\_zc706\_hdmi** platform and can be used for other purposes within the SDSoC development environment:

- Clocks:

- Clock id 1 (default): 100 MHz

- Clock id 2: 200 MHz

- Clock id 3: 142.86 MHz

- PS-PL ports:

- M\_AXI\_GP1

- S\_AXI\_HP1

Version: v2.00.a

October 21<sup>st</sup>, 2016

- S\_AXI\_HP3

- S\_AXI\_ACP

- Interrupts:

- Over xlconcat IP, ports from 3 to 15

#### Figure 12: CAM-HDMI SoC Design – Block Diagram (Pre-Defined Platform)

#### (Clock Generator Module and other utility IP cores are not shown)

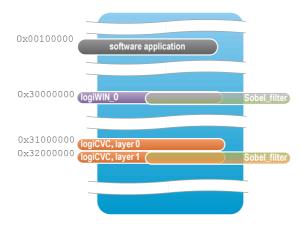

Figure 13: CAM-HDMI Design Memory Layout

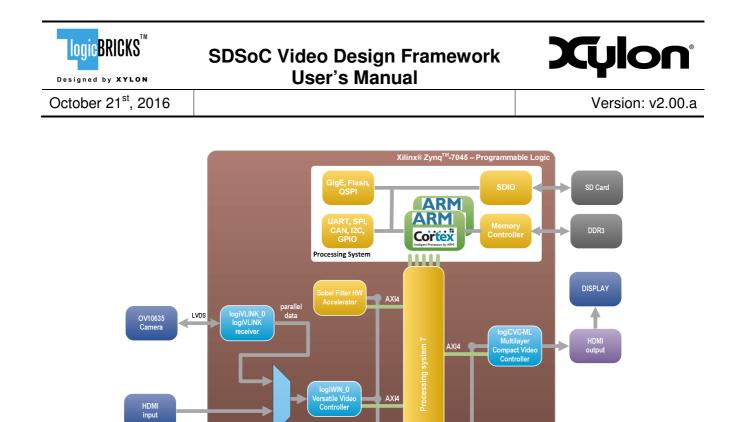

Figure 14: CAM-HDMI SoC Design – Block Diagram (Platform with the Sobel Filter IP)

FPGA

CPU

MIXED SIGNAL

MEMORY

AXI4-Lite

logicBRICKS

3<sup>RD</sup> PARTY

(Clock Generator Module and other utility IP cores are not shown)

October 21<sup>st</sup>, 2016

Version: v2.00.a

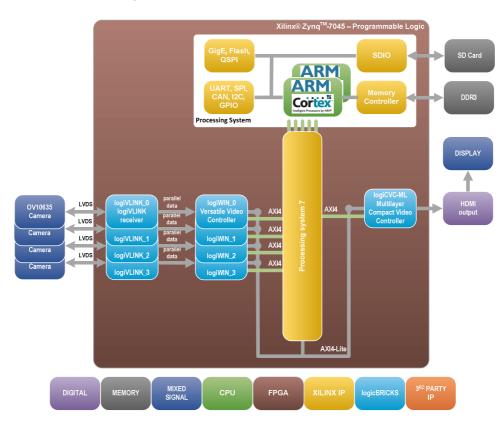

# 5.2 FOUR-CAM SoC Design and Memory Layout

This platform design (Figure 15) supports four camera inputs, and the single display output. The following Zynq SoC resources are not used by the sdsoc\_zc706\_4cam platform and can be used for other purposes within the SDSoC development environment:

- Clocks:

- Clock id 1 (default): 100 MHz

- Clock id 2: 200 MHz

- Clock id 3: 142.86 MHz

- PS-PL ports:

- M\_AXI\_GP0

- S\_AXI\_HP2

- S\_AXI\_ACP

- Interrupts:

- Over xlconcat IP, ports from 5 to 15

Figure 15: FOUR-CAM SoC Design– Block Diagram (Pre-Defined Platform)

(Clock Generator Module and other utility IP cores are not shown)

#### Figure 16: FOUR-CAM SoC Design– Block Diagram (Platform with the Sobel Filter IP)

#### (Clock Generator Module and other utility IP cores are not shown)

Figure 17: FOUR-CAM Design Memory Layout

<mark>logic</mark>BRICKS<sup>™</sup>

Designed by XYLON

### 5.3 Using the logiADAK-VDF-SDSoC Platforms and the Hardware Accelerator Based on the C-code Description

Please copy the *sdsoc\_zc706\_hdmi* and *sdsoc\_zc706\_4cam* platform folders to folder *<SDSoC\_install\_dir>/platforms* within your SDSoC installation folders.

### 5.4 Using and configuring Hardware Accelerator as C-code Based IP core

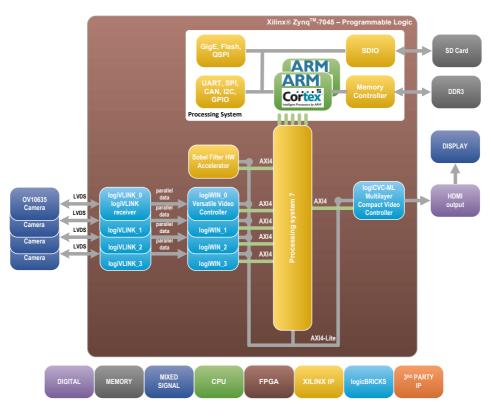

The provided software demo includes the Sobel filter algorithm as the C++ function sds\_sobel()(sds\_sobel.cpp). The function is used as a simple example of the C-code based hardware accelerator implementation generated by the SDSoC tool.

The HLS generated Sobel filter accelerator connects to the AXI-Stream accelerator adapter that drives all inputs and captures all outputs. The adapter has two FIFO interfaces for streaming video data to and from the accelerator, converts video data streams to the AXI-Stream format, and connect the AXI DMA Rx and Tx channels via the AXI-Stream router. The instantiated data mover is the AXI DMA in a scatter-gather mode. The width, height, and stride parameters are simple control signals (scalars) driven by the adapter.

Note that the m2m pipeline is not video-timing accurate. The DMA reads and writes video frames without inserting any horizontal blanking between video lines. An interrupt is issued by the DMA engine separately for the read and write channels upon completion of a frame read/write operation.

The DMA engine translates AXI-Stream data to AXI-Memory-mapped data. The output is connected to the SDSoC available HP high performance PS/PL interface via the AXI interconnect.

The AXI-Lite control interfaces is connected to the SDSoC available GP general purpose PS/PL interface.

# Figure 18: Hardware Accelerator and Data Motion Network entirely generated by the SDSoC tool based on a C-code description

<mark>logic</mark>BRICKS<sup>™</sup>

October 21<sup>st</sup>, 2016

# 5.5 Software Description

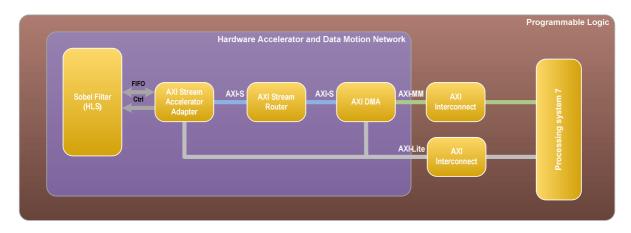

### 5.5.1 Main function

The main.cpp, which is the main application file in CAM-HDMI and FOUR-CAM reference designs, uses the hw\_Init function to initialize the hardware platform, and the main\_loop function to implement the Sobel video filter and to allocate memory for video framebuffers. Both reference designs use the double buffering synchronization between video inputs and the video outputs in order to avoid unwanted video display artifacts, such as random stripes caused by framebuffers overrun, i.e. the video input data is written in the memory framebuffer currently shown on the display. While the CAM-HDMI demo application initializes memory buffers for a single video channel, the FOUR-CAM application need to initialize buffers for every video camera. The same applies to video processing and panning functions.

Software code for double buffering synchronization mechanism uses several functions organized in the *VideoInput* and the *VideoOutput* mini libraries. Two video input and two video output framebuffers per video camera input are initialized before the infinite while loop (see Figure 19). All Xylon drivers, such as logiWIN and logiCVC software drivers, are User Space I/O (UIO) drivers. Current input framebuffer and output framebuffer are exchanged on the UIO interrupt of a logiWIN driver, which is initiated before each new video input frame. The example Sobel filter, which is implemented in the startProcessing function, filters video from the last refreshed output framebuffer, currently defined by the VideoInput\_waitNewBuff function. The processed video is written to the current display output framebuffer. All framebuffers are deinitialized by VideoInput\_deintialize and VideoOutput\_deintialize functions that release the allocated memory space.

The startProcessing function applies Sobel filter on an input image, which is read from input buffer, and writes it to output framebuffer. By removing sds\_sobel function user can easily put its own image processing function.

```

void startProcessing(InputBuffT *pInBuff, OutputBuffT *pOutBuff)

{

sds_sobel((unsigned short *)pInBuff->pVirtBase, (unsigned short

*)pOutBuff->pVirtBase, pInBuff->vres, pInBuff->hres, pInBuff->stride/2);

}

```

### 5.5.2 The Video input Library

The VideoInput\_initBuffers function maps input framebuffer, fills input buffer structure with used parameters and returns value of the UIO identifier.

The <code>VideoInput\_waitNewBuff</code> function waits for the UIO interrupt and switches the video input framebuffer at the end of the new video frame signalized by the UIO interrupt.

The VideoInput\_deintialize function deinitializes input framebuffers.

<mark>logic</mark>BRICKS<sup>™</sup>

Designed by XYLON

SDSoC Video Design Framework User's Manual

```

typedef struct

{

void *pVirtBase; // pointer to input framebuffer

int vres; // vertical resolution

int hres; // horizontal resolution

int stride; // image stride in pixels

}InputBuffT;

```

The InputBuffT structure is used to store information about input framebuffer and to send it to Sobel filter.

### 5.5.3 The VideoOutput Library

The VideoOutput\_initBuffers function maps output framebuffer, fills output buffer structure with used parameters and reads all vinfo data.

The VideoOutput\_waitVsync function waits for V-sync if it hasn't appeared since the last call of VideoOutput\_showBuffer function.

The VideoOutput\_showBuffer function reads panning offset and pan the screen so the right framebuffer is shown.

The VideoOutput\_deintialize function deinitializes output framebuffers.

```

typedef struct

ł

void *pVirtBase;

// pointer to input framebuffer

int phAddr;

// phisical address of a framebuffer

// vertical resolution

int vres;

// horizontal resolution

int hres;