# MV78230, MV78260, and MV78460

ARMADA<sup>®</sup> XP Family of Highly Integrated Multi-Core ARMv7 Based SoC Processors

Functional Specifications – Unrestricted

Doc. No. MV-S107021-U0, Rev. A May 29, 2014, Preliminary

Document Classification: Proprietary Information

| Docum                                               | Document Conventions                  |                                           |  |  |

|-----------------------------------------------------|---------------------------------------|-------------------------------------------|--|--|

|                                                     | Note: Provides related information or | information of special importance.        |  |  |

| !                                                   | Caution: Indicates potential damage   | to hardware or software, or loss of data. |  |  |

| J                                                   | Warning: Indicates a risk of personal | injury.                                   |  |  |

| Docum                                               | Document Status                       |                                           |  |  |

| Doc Status: Preliminary Technical Publication: 0.xx |                                       | Technical Publication: 0.xx               |  |  |

For more information, visit our website at: www.marvell.com

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

- 1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

- 2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,

- 3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 2014. Marvell International Ltd. All rights reserved. Alaska, ARMADA, CarrierSpan, Kinoma, Link Street, LinkCrypt, Marvell logo, Marvell, Moving Forward Faster, PISC, Prestera, Qdeo (for chips), QDEO logo (for chips), QuietVideo, Virtual Cable Tester, Xelerated, and Yukon are registered trademarks of Marvell or its affiliates. Avanta, Avastar, DragonFly, HyperDuo, Kirkwood, Marvell Smart, Qdeo, QDEO logo, The World as YOU See It, Vmeta and Wirespeed by Design are trademarks of Marvell or its affiliates.

Patent(s) Pending—Products identified in this document may be covered by one or more Marvell patents and/or patent applications.

Doc. No. MV-S107021-U0 Rev. A

Copyright © 2014 Marvell

Page 2

Document Classification: Proprietary Information

May 29, 2014, Preliminary

## **Revision History**

| Revision | Date      | Comments             |

|----------|-----------|----------------------|

| Α        | 29-May-14 | Unrestricted Release |

## **Table of Contents**

| Revis | Revision History 3                                     |    |  |

|-------|--------------------------------------------------------|----|--|

| Prefa | Preface                                                |    |  |

| Part  |                                                        |    |  |

| 1     | Product Overview                                       | 35 |  |

| 2     | Functional Overview                                    | 41 |  |

| 2.1   | Marvell® Core Processor                                | 41 |  |

| 2.2   | Level-2 Cache                                          | 42 |  |

| 2.3   | System Considerations                                  | 42 |  |

| 2.4   | BootROM Firmware                                       | 42 |  |

| 2.5   | Coherency Fabric                                       | 43 |  |

| 2.6   | Multiprocessor Interrupt Controller (MPIC)             | 44 |  |

| 2.7   | Timers, Counters, and Watchdog                         | 44 |  |

| 2.8   | CPU Debug Capabilities                                 | 44 |  |

| 2.9   | DDR3 SDRAM Controller                                  | 45 |  |

| 2.10  | NAND Flash Controller (NFC)                            | 45 |  |

| 2.11  | Device Bus Controller                                  | 46 |  |

| 2.12  | Ethernet Networking Controller                         | 47 |  |

| 2.13  | Hardware Buffer Management (BM) Controller             | 48 |  |

| 2.14  | PCI Express Interface                                  | 48 |  |

| 2.15  | Universal Serial Bus (USB 2.0) Interface               | 49 |  |

| 2.16  | Serial-SATA (SATA) II Interface                        | 49 |  |

| 2.17  | Serial Peripheral Interface (SPI)                      | 50 |  |

| 2.18  | Time-Division Multiplexing (TDM) Controller            | 50 |  |

| 2.19  | Secure Digital Input/Output (SDIO) Controller          | 50 |  |

| 2.20  | Inter-Integrated Circuit Interface (I <sup>2</sup> C)  | 51 |  |

| 2.21  | UART Interface                                         | 51 |  |

| 2.22  | Real Time Clock (RTC)                                  | 51 |  |

| 2.23  | General Purpose I/Os (GPIO) Ports                      | 51 |  |

| 2.24  | Power Management                                       | 52 |  |

| 2.25  | High-Speed Integrated SERDES Interface                 | 53 |  |

| 2.26  | Cryptographic Engines and Security Accelerators (CESA) | 53 |  |

| 2.27  | XOR Engines                                            | 53 |  |

| 2.28  | Independent DMA (IDMA) Controller                      | 54 |  |

| 3    | Address Map                                                  | 55   |

|------|--------------------------------------------------------------|------|

| 3.1  | Marvell® Core Processor Address Decoding                     | . 55 |

| 3.2  | PCI Express Address Decoding                                 | . 62 |

| 3.3  | IDMA Address Decoding                                        | . 66 |

| 3.4  | XOR DMA Address Decoding                                     | . 66 |

| 3.5  | Ethernet Networking Controllers Address Decoding             | . 66 |

| 3.6  | USB Address Decoding                                         | . 67 |

| 3.7  | SATA Address Decoding                                        | . 67 |

| 3.8  | Security Accelerator Address Decoding                        | . 67 |

| 3.9  | Buffer Management Address Decoding                           | . 67 |

| 3.10 | SDIO Address Decoding                                        | . 68 |

| 3.11 | TDM Address Decoding                                         | . 68 |

| 3.12 | I2C Address Decoding                                         | . 68 |

| 3.13 | Accessing the L2/SRAM from Mbus Masters                      | . 69 |

| 4    | Internal Architecture                                        | 70   |

| 4.1  | Coherency Fabric                                             | . 72 |

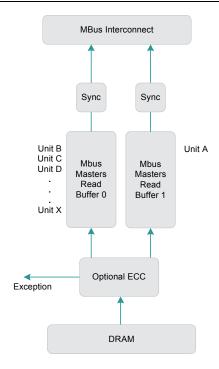

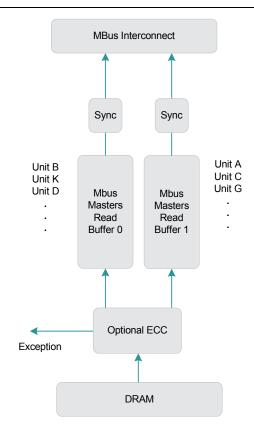

| 4.2  | DRAM Controller Interface Interconnect                       | . 74 |

| 4.3  | Mbus Interconnect                                            | . 74 |

| 4.4  | Transaction Ordering                                         | . 78 |

| 5    | System Considerations                                        | 82   |

| 5.1  | Data Integrity                                               | . 82 |

| 5.2  | PCI Express Reference Clock Output                           | . 89 |

| 5.3  | Big and Little Endian Byte Ordering                          | . 90 |

| 6    | BootROM Firmware                                             | 93   |

| 6.1  | Features                                                     | . 94 |

| 6.2  | Functional Description                                       | . 95 |

| 6.3  | General Considerations                                       | . 95 |

| 6.4  | Address Decoding and Memory Management Unit (MMU) Operations | . 95 |

| 6.5  | Boot Image Format                                            | . 96 |

| 6.6  | BootROM Firmware Boot Sequence                               | 102  |

| 6.7  | BootROM Firmware Boot Options                                | 115  |

| 6.8  | BootROM Behavior When Recovering from Deep Idle Mode         | 118  |

| Part | 2: CPU Subsystem1                                            | 19   |

| 7    | Marvell® Core Processor 1                                    | 121  |

| 8    | Level-2 Cache 1                                              | 122  |

| 8.1  | Features                                                     | 123  |

| 8.2  | L2 Cache Requests Types                                      | 124  |

| 8.3   | L2 Cache Functional Description                           | 128 |

|-------|-----------------------------------------------------------|-----|

| 8.4   | Error Handling                                            | 133 |

| 8.5   | Events Monitor Counters                                   | 136 |

| 8.6   | Power Management                                          | 137 |

| 9     | Multiprocessor Interrupt Controller (MPIC)                | 139 |

| 9.1   | Features                                                  | 140 |

| 9.2   | Functional Description                                    | 140 |

| 10    | Timers, Counters, and Watchdog                            | 157 |

| 10.1  | Features                                                  | 158 |

| 10.2  | Functional Description                                    | 158 |

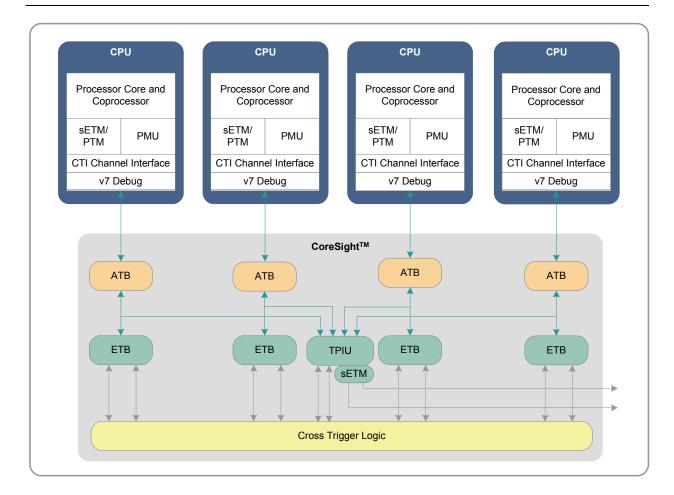

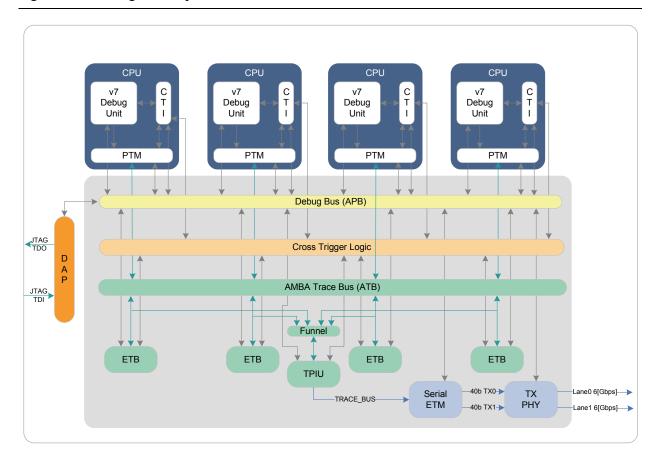

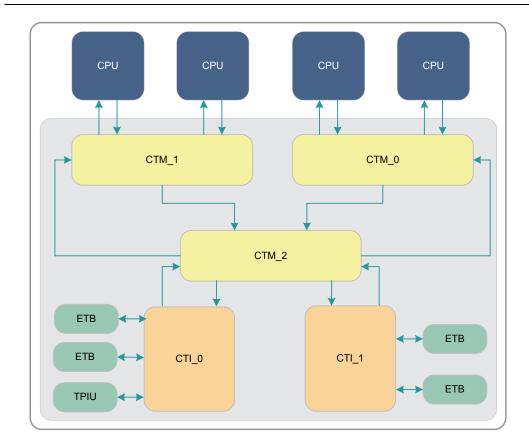

| 11    | Debug Capabilities                                        | 161 |

| 11.1  | Debug and Power Saving Modes                              | 165 |

| 11.2  | Serial Tracing                                            | 166 |

| 11.3  | System Debug Management                                   | 166 |

| 11.4  | Timestamp Mechanism                                       | 167 |

| 11.5  | Memory Map for CoreSight Components                       | 168 |

| Part  | 3: External Memory Interfaces                             | 171 |

| 12    | DRAM Controller                                           | 173 |

| 12.1  | Feature List                                              | 173 |

| 12.2  | Functional Description                                    | 174 |

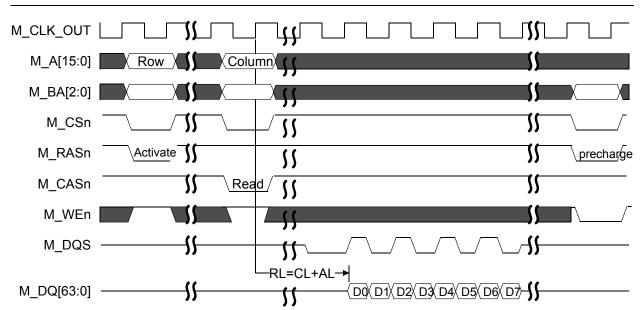

| 12.3  | Transaction Data Path                                     | 175 |

| 12.4  | Arbitration and Ordering                                  | 179 |

| 12.5  | DRAM Timing Parameters                                    | 184 |

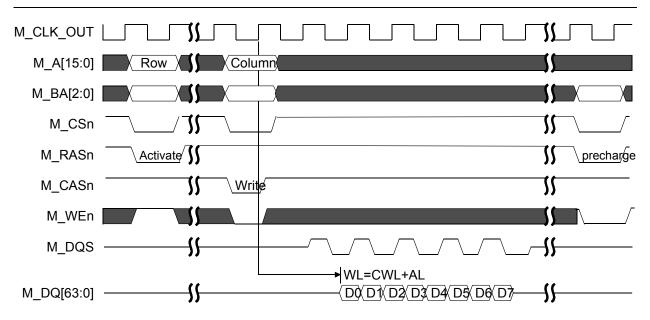

| 12.6  | DRAM Burst                                                | 186 |

| 12.7  | DRAM Bank Interleaving                                    | 187 |

| 12.8  | DRAM Open Pages                                           | 188 |

| 12.9  | Error Checking and Correction (ECC) and Read Modify Write | 188 |

| 12.10 | DRAM Refresh                                              | 189 |

| 12.11 | DRAM Initialization                                       | 189 |

| 12.12 | DRAM Operation Mode Register                              | 191 |

| 12.13 | Power Save Options                                        | 192 |

| 12.14 | DIMM Support                                              | 194 |

| 12.15 | DRAM Topologies                                           | 195 |

| 12.16 | DRAM Clocking                                             | 198 |

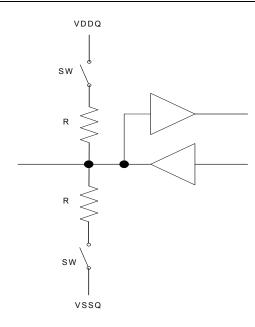

| 12.17 | DRAM Address/Data Drive                                   | 199 |

| 12.18 | DRAM Read Data Sample                                     | 199 |

| 12 19 | On-Die Termination (ODT)                                  | 200 |

| 12.20  | DRAM Calibration                                       | 201 |

|--------|--------------------------------------------------------|-----|

| 13     | NAND Flash Controller (NFC)                            | 203 |

| 13.1   | Features                                               | 203 |

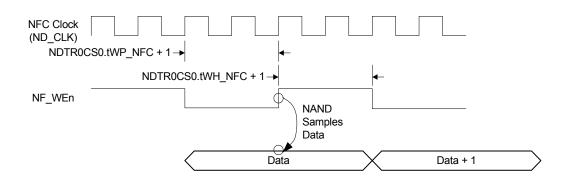

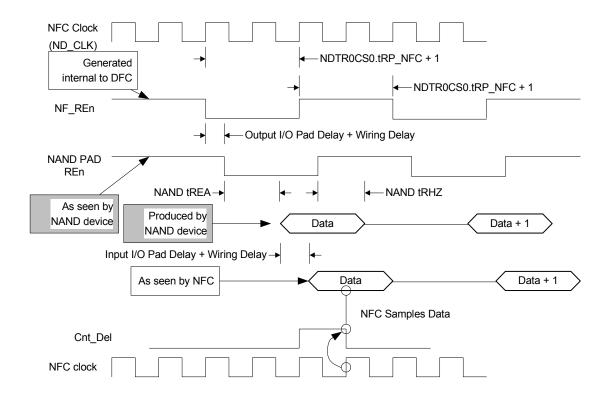

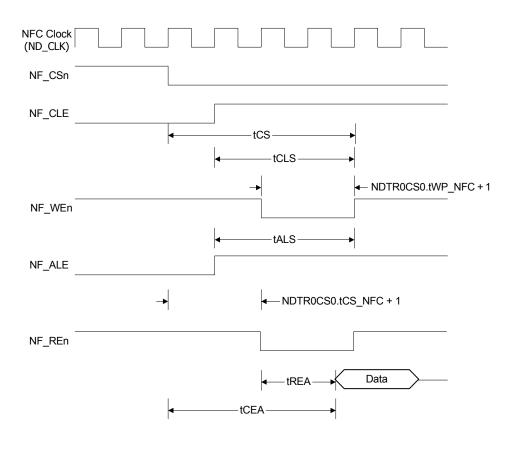

| 13.2   | NAND Flash Interface                                   | 205 |

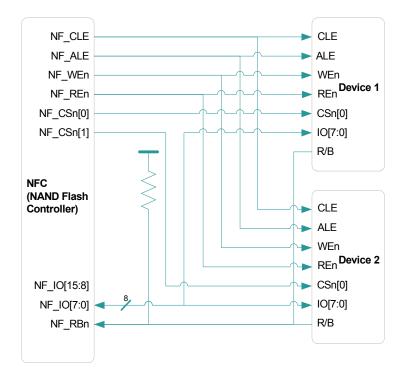

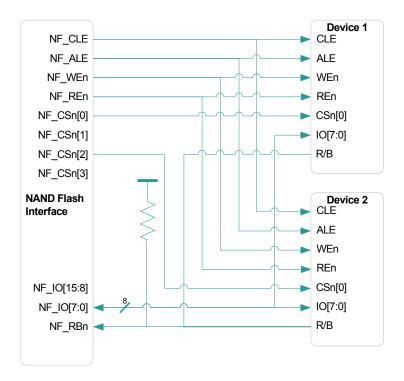

| 13.3   | NAND Flash Connectivity                                | 205 |

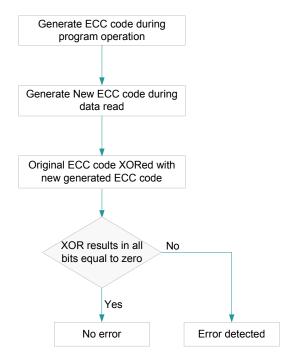

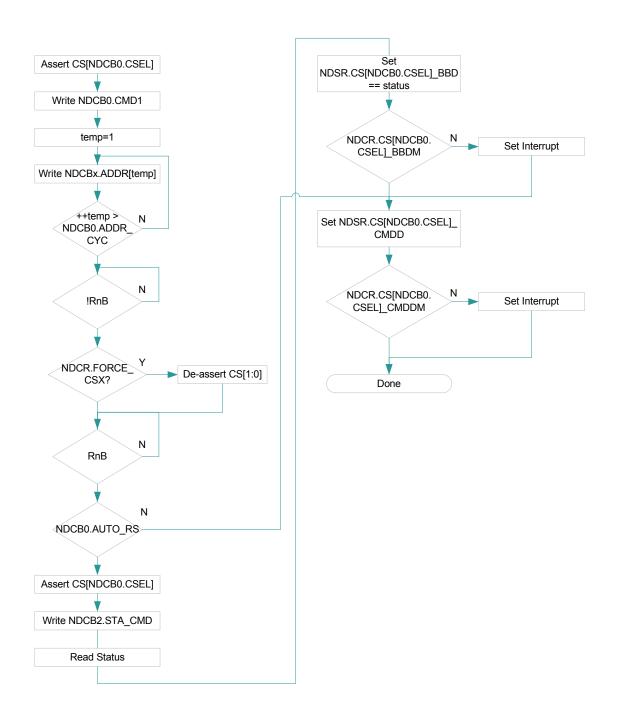

| 13.4   | Operation                                              | 207 |

| 13.5   | Usage Models                                           | 224 |

| 14     | Device Bus Controller                                  | 237 |

| 14.1   | Features                                               | 238 |

| 14.2   | Functional Description                                 | 238 |

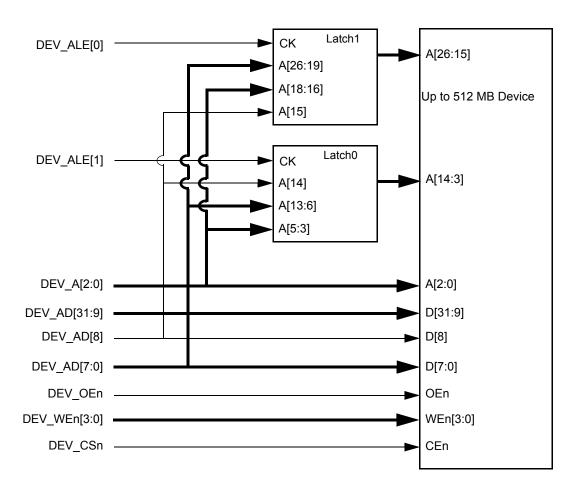

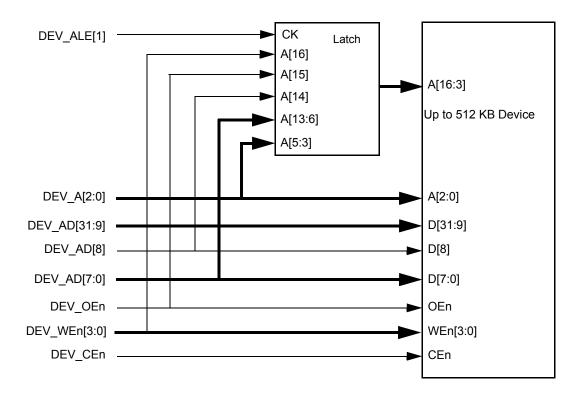

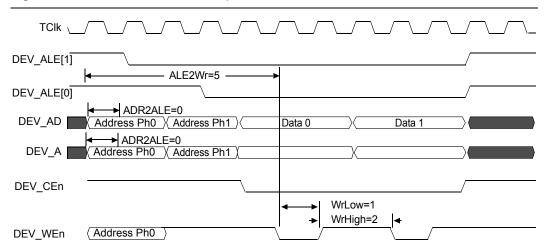

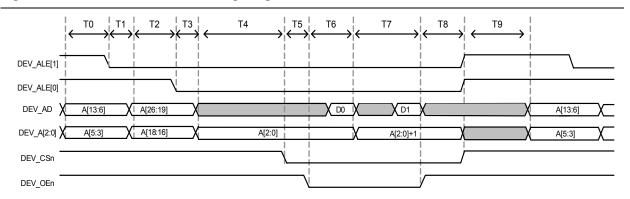

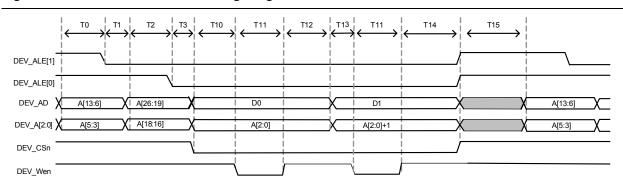

| 14.3   | Address Multiplexing                                   | 241 |

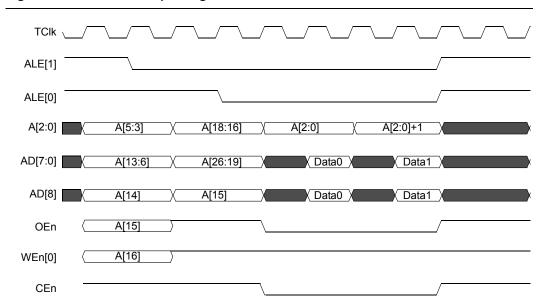

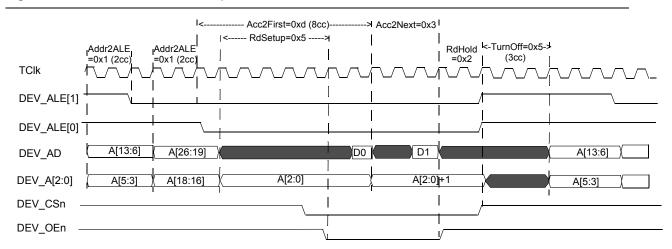

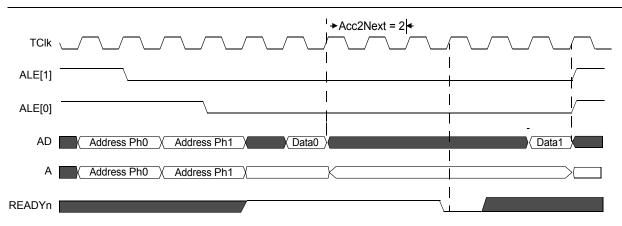

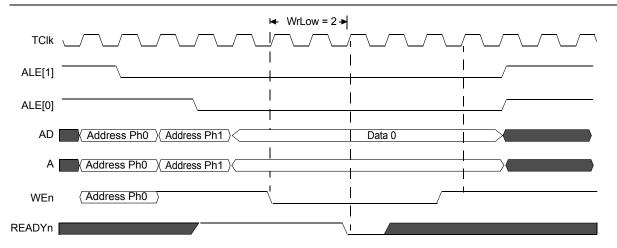

| 14.4   | Device Bus Timing                                      | 242 |

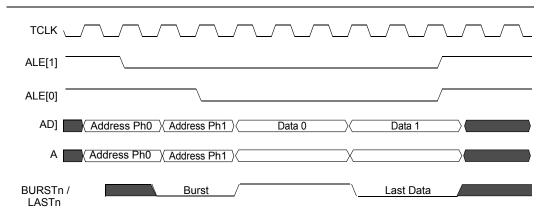

| 14.5   | Data Pack/Unpack and Burst Support                     | 248 |

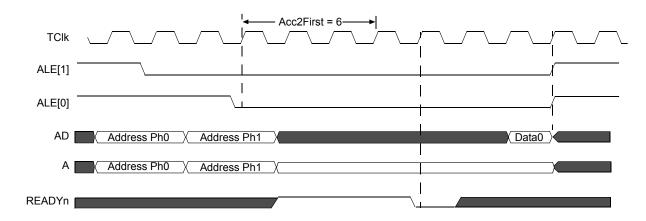

| 14.6   | READYn Support                                         | 248 |

| 14.7   | Additional Device Interface Signaling                  | 250 |

| Part 4 | 4: Ethernet Networking Subsystem                       | 251 |

| 15     | Ethernet Networking Controller                         | 253 |

| 15.1   | Features                                               | 254 |

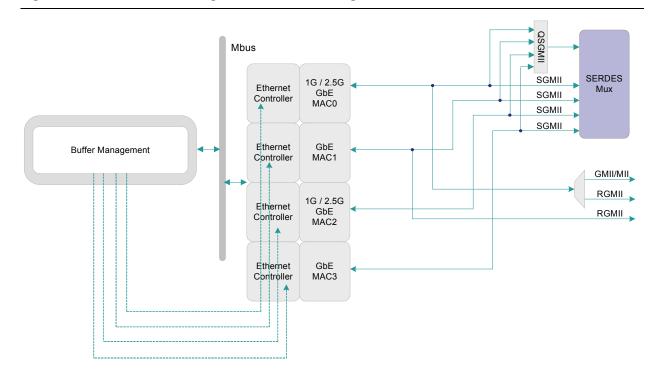

| 15.2   | Networking Controller Modes Overview                   | 255 |

| 15.3   | Functional Description                                 | 256 |

| 15.4   | Queues Management                                      | 262 |

| 15.5   | Hardware Buffer Management                             | 275 |

| 15.6   | Receive Frame Processing—Hardware Parser Mode          | 276 |

| 15.7   | Marvell® Header Support                                | 279 |

| 15.8   | Distributed Switching Architecture (DSA) Tag Support   | 282 |

| 15.9   | Wake On LAN (WOL) Modes and Events                     | 287 |

| 15.10  | Interrupts                                             | 289 |

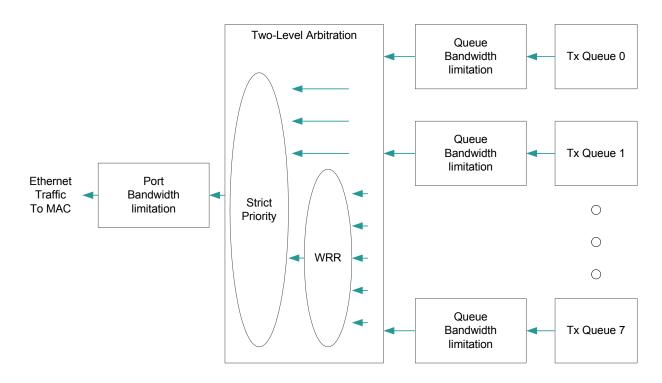

| 15.11  | Transmit Queues Arbitration and Bandwidth Limitation   | 290 |

| 15.12  | Transmit Queues Egress Jitter Pacing (EJP) Arbitration | 296 |

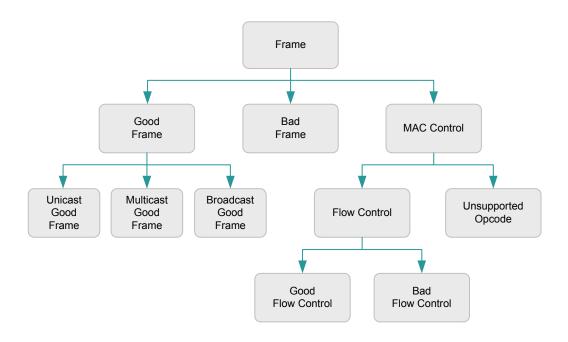

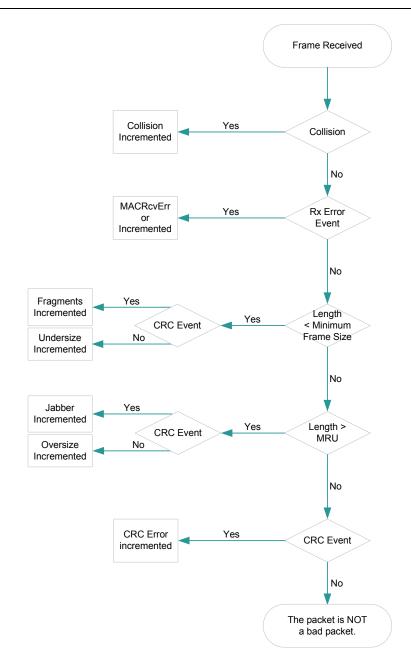

| 15.13  | Illegal Received Frames                                | 299 |

| 15.14  | Multi-CPU Support                                      | 299 |

| 15.15  | L2-Cache Prefetch Engine Support                       | 299 |

| 16     | Hardware Buffer Management Controller                  | 301 |

| 16.1   | Features                                               | 301 |

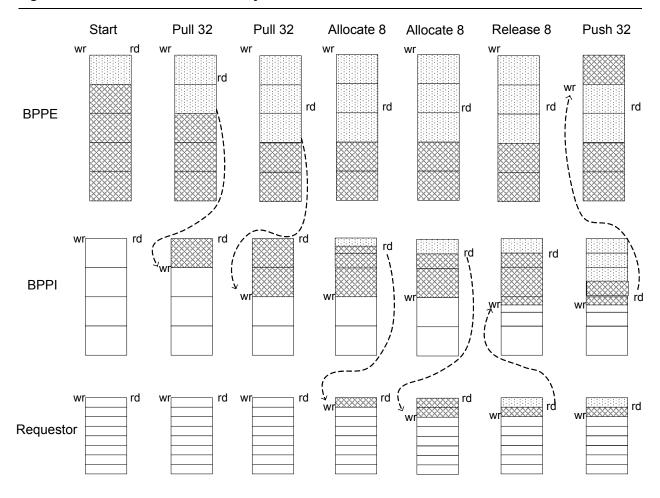

| 16.2   | Functional Description and Data Flow                   | 302 |

| 16.3   | Activation and Usage                                   | 305 |

| 17    | 1G/2.5G Ethernet MAC                               | 308 |

|-------|----------------------------------------------------|-----|

| 17.1  | Functional Description                             | 308 |

| 17.2  | Retransmission (Collision)                         | 309 |

| 17.3  | CRC Generation                                     | 309 |

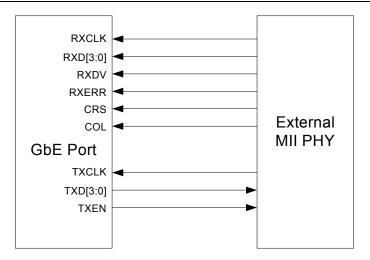

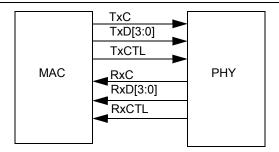

| 17.4  | Network Interface (10/100/1000 Mbps)               | 309 |

| 17.5  | Input Signal Forcing                               | 312 |

| 17.6  | Auto-Negotiation in Different MII/GMII/RGMII Modes | 312 |

| 17.7  | Data Blinder                                       | 312 |

| 17.8  | Inter-Packet Gap                                   | 313 |

| 17.9  | Backpressure Mode                                  | 313 |

| 17.10 | Flow Control                                       | 313 |

| 17.11 | Serial Management Interface (SMI)—Ethernet MAC     | 315 |

| 17.12 | Port MIB Counters                                  |     |

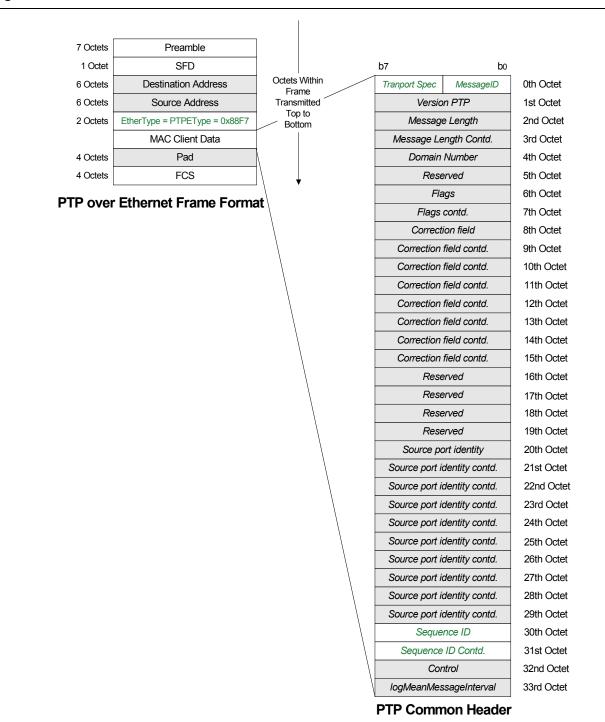

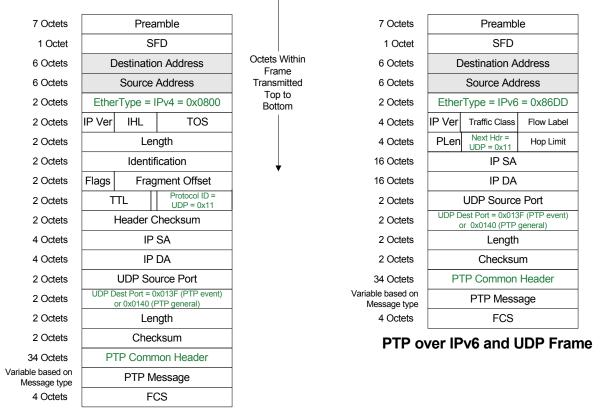

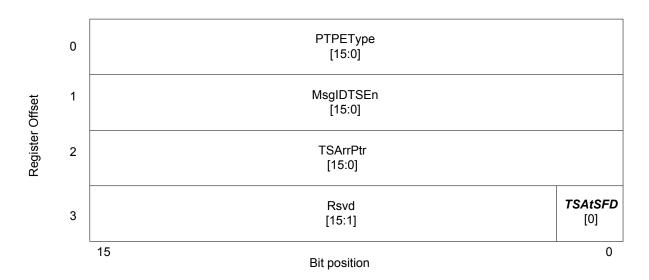

| 18    | Precise Time Protocol (PTP)                        | 320 |

| 18.1  | Frame Format                                       | 321 |

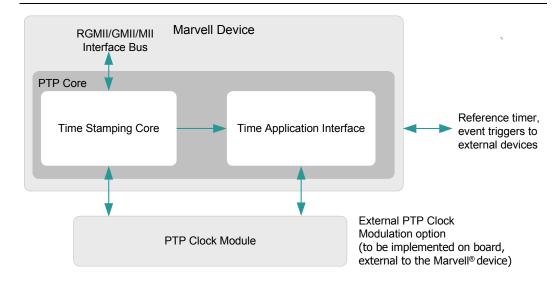

| 18.2  | PTP Frame Time Stamping Clock                      | 322 |

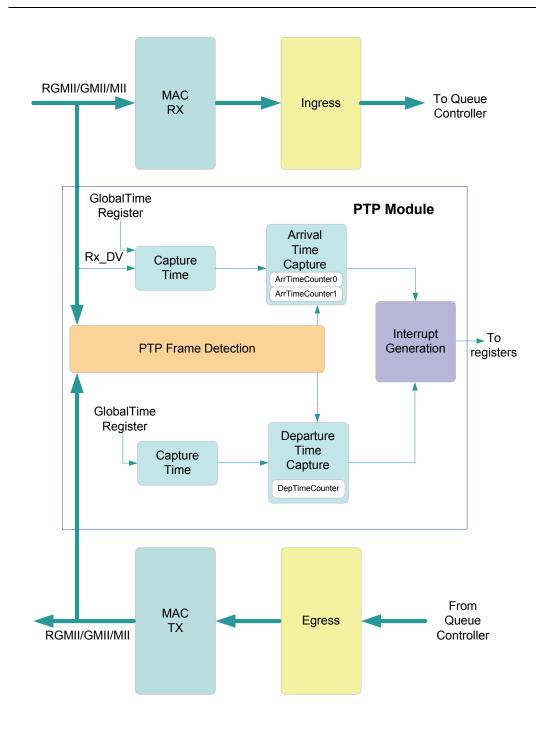

| 18.3  | Pipeline Stages                                    | 323 |

| 18.4  | Time Stamping Block                                | 323 |

| 18.5  | Timing Application Interface (TAI) Block           | 326 |

| 18.6  | Software Initialization Procedure                  | 328 |

| Part  | 5: External Interfaces                             | 331 |

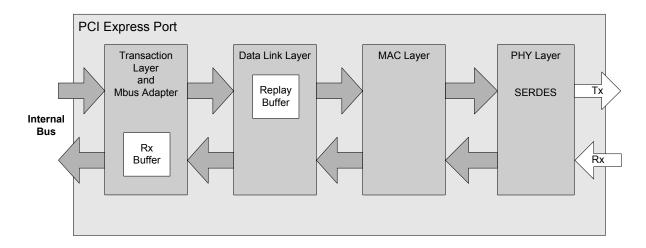

| 19    | PCI Express Interface (PCIe) 2.0                   | 333 |

| 19.1  | Features                                           |     |

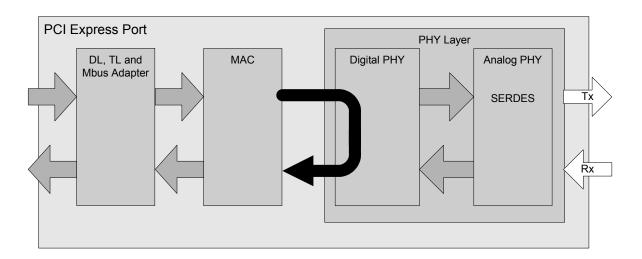

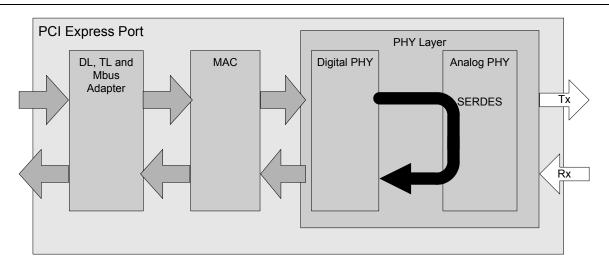

| 19.2  | Functional Description                             | 335 |

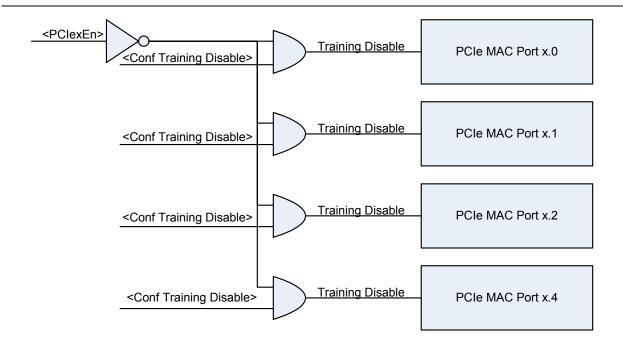

| 19.3  | Link Initialization                                | 337 |

| 19.4  | Master Memory Transactions                         | 337 |

| 19.5  | Master I/O Transactions                            |     |

| 19.6  | Master Configuration Transactions                  | 338 |

| 19.7  | Target Memory Transactions                         | 338 |

| 19.8  | Target I/O Transactions                            | 339 |

| 19.9  | Target Configuration Transactions                  | 339 |

| 19.10 | Target Special Cases                               | 339 |

| 19.11 | Messages                                           | 339 |

| 19.12 | Message Signaled Interrupt (MSI) Support           | 341 |

| 19.13 | Locked Transactions                                | 341 |

| 19.14 | Arbitration and Ordering                           | 342 |

| 19.15 | PCI Express Register Access                        | 342 |

| 10.10 |                                                    |     |

| 19.16 | Hot Reset                                          | 344 |

| 19.18              | Power Management                                      | 346 |

|--------------------|-------------------------------------------------------|-----|

| 19.19              | Loopback Modes                                        |     |

| 19.20              | Peer-to-Peer Traffic                                  |     |

| 19.21              | Force Link Down                                       |     |

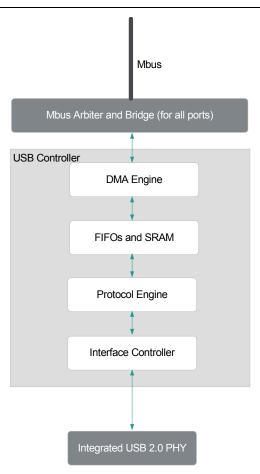

| 20                 | Universal Serial Bus (USB 2.0) Interface              | 252 |

| 2 <b>0</b><br>20.1 | USB Controller Features                               |     |

| 20.1<br>20.2       | USB PHY Features                                      |     |

| 20.2               | Power Management                                      |     |

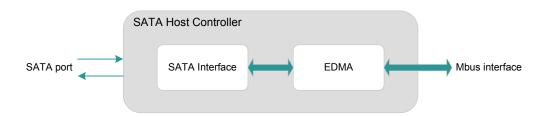

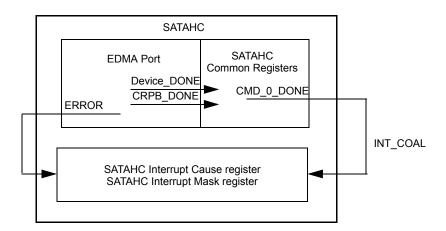

| 21                 | Serial-ATA (SATA) II Interface                        | 354 |

| <b>- ·</b><br>21.1 | Features                                              |     |

| 21.2               | SATA Functional Description                           |     |

| 21.3               | EDMA Functional Description                           |     |

| 21.4               | Built-In Self Test (BIST)                             |     |

| 21.5               | Vendor Unique Frames                                  |     |

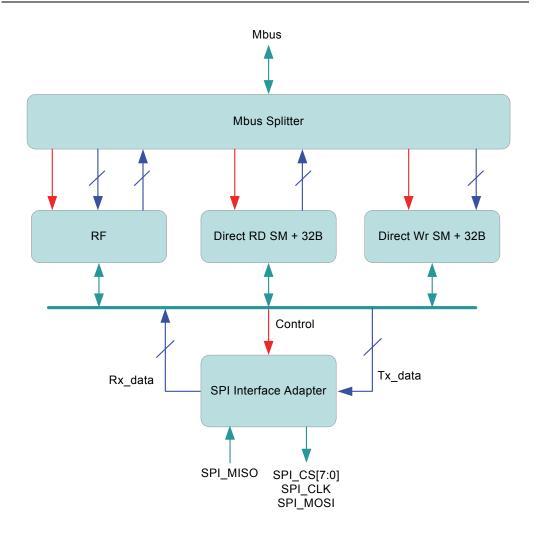

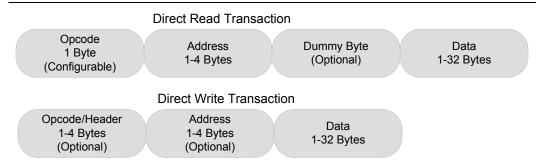

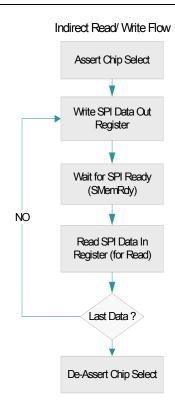

| 22                 | Serial Peripheral Interface (SPI)                     | 378 |

| 22.1               | Features                                              |     |

| 22.2               | Functional Description                                | 379 |

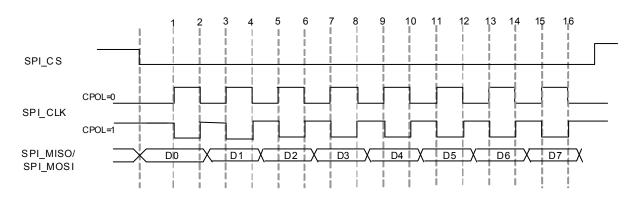

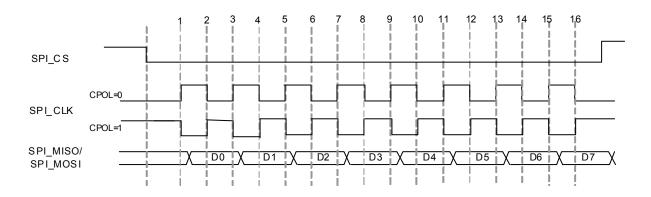

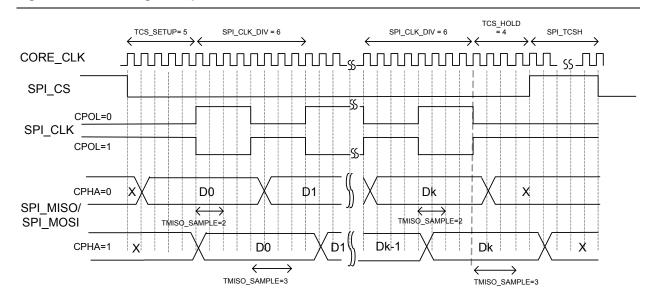

| 22.3               | SPI Modes                                             | 380 |

| 22.4               | Indirect Access                                       | 381 |

| 22.5               | Direct Mode                                           |     |

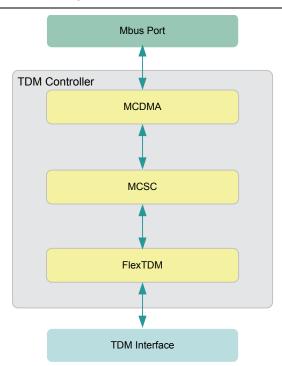

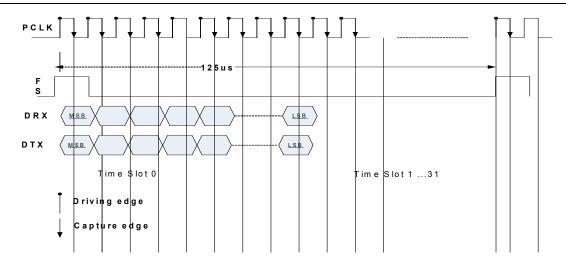

| 23                 | Time-Division Multiplexing (TDM) Controller           | 386 |

| 23.1               | Features                                              | 386 |

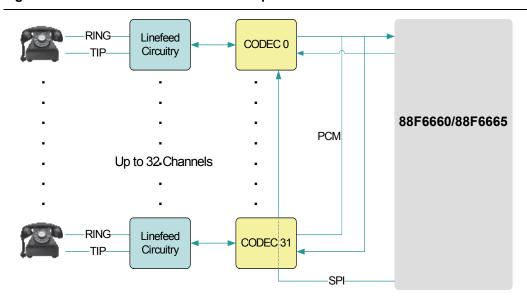

| 23.2               | Functional Description                                | 387 |

| 23.3               | FlexTDM Controller (FTDM)                             | 388 |

| 23.4               | Multi-Channel Serial Controller (MCSC)                | 390 |

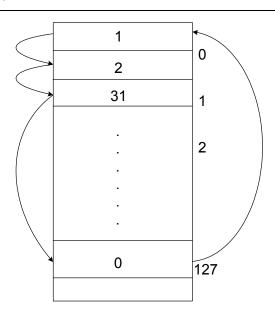

| 23.5               | Multi-Channel Direct Memory Access (MCDMA)            | 393 |

| 23.6               | Interrupts                                            | 404 |

| 23.7               | Voice Application Flows                               | 408 |

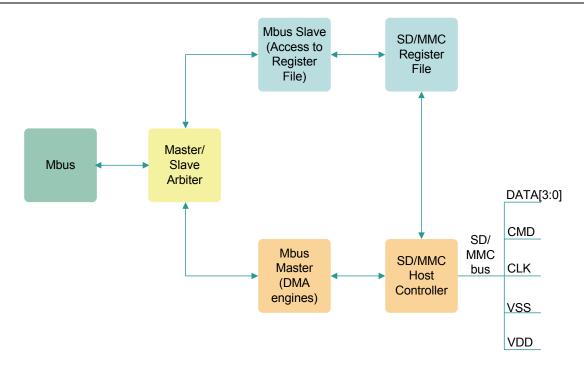

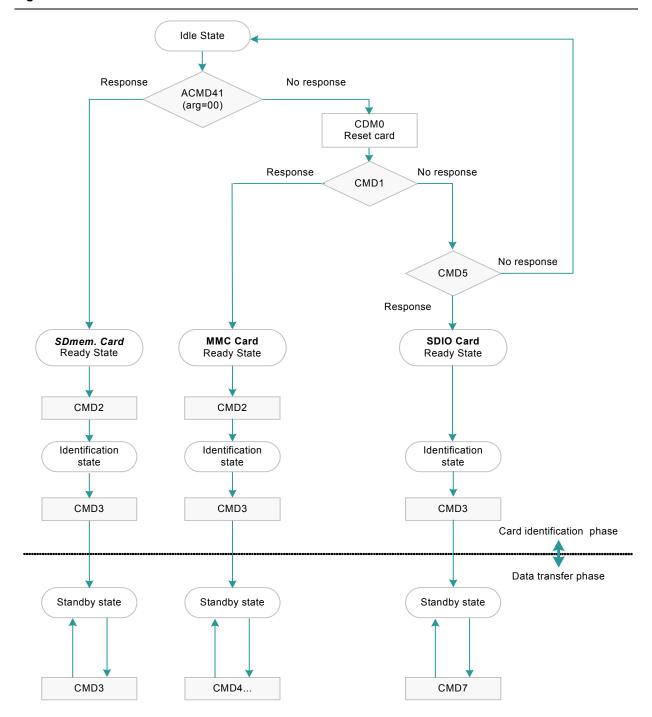

| 24                 | Secure Digital Input/Output (SDIO) Controller         | 413 |

| 24.1               | Features                                              | 414 |

| 24.2               | Functional Description                                | 415 |

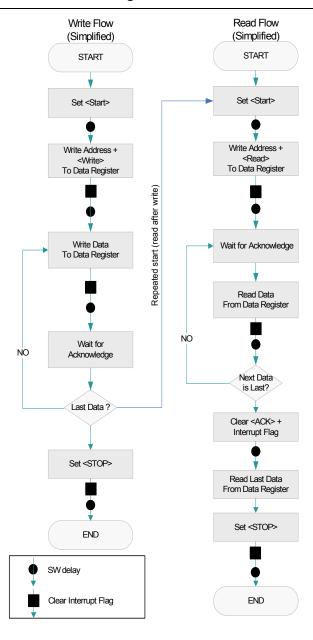

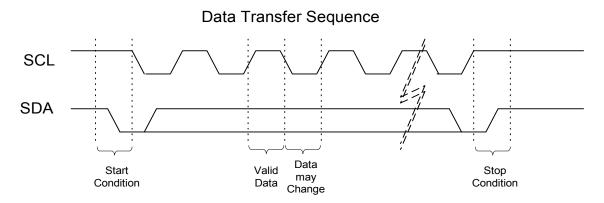

| 25                 | Inter-Integrated Circuit Interface (I <sup>2</sup> C) | 420 |

| 25.1               | Features                                              | 421 |

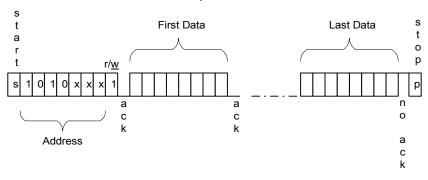

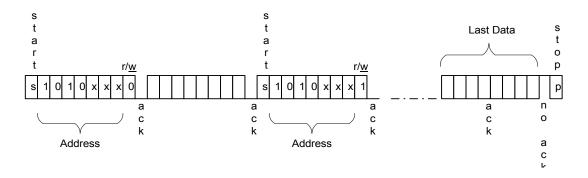

| 25.2               | I <sup>2</sup> C Bus Operation                        | 421 |

| 25.3               | I <sup>2</sup> C Functional Description               | 423 |

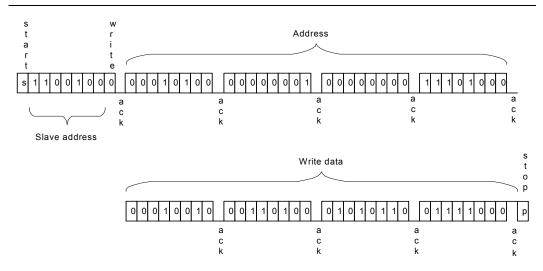

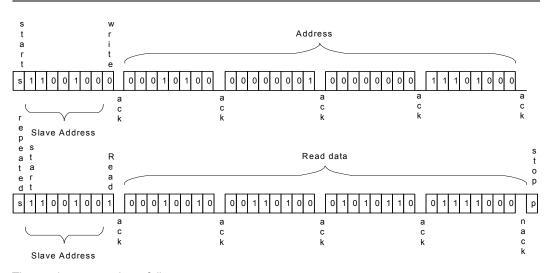

| 25.4               | I <sup>2</sup> C Serial ROM Initialization            | 430 |

| 25.5               | I <sup>2</sup> C Hardware Slave                       | 430 |

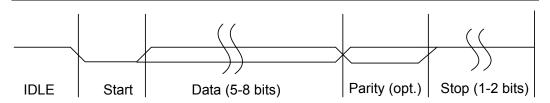

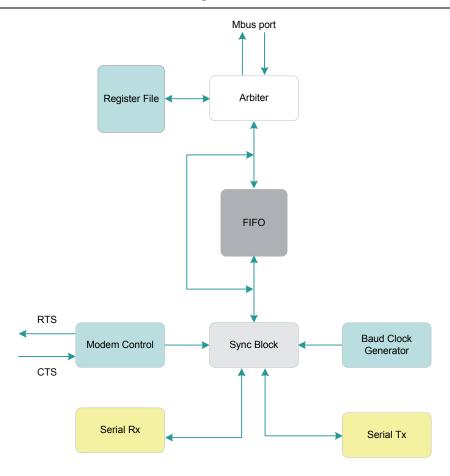

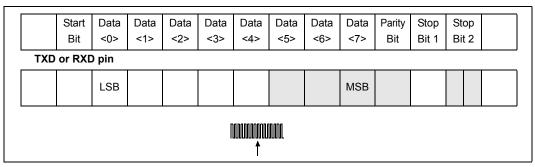

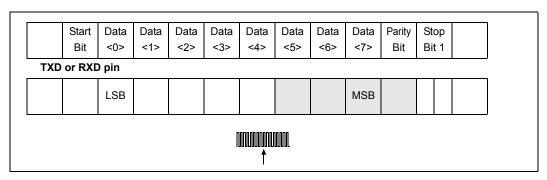

| 26   | Universal Asynchronous Receiver/Transmitter (UART) Interface | 432 |

|------|--------------------------------------------------------------|-----|

| 26.1 | Features                                                     | 433 |

| 26.2 | Functional Description                                       | 434 |

| 26.3 | Programmable Baud-Rate Generator                             | 435 |

| 26.4 | DMA-Based UART                                               | 436 |

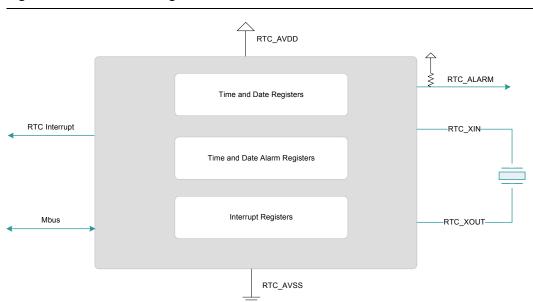

| 27   | Real-Time Clock (RTC)                                        | 439 |

| 27.1 | Features                                                     | 439 |

| 27.2 | Functional Description                                       | 440 |

| 28   | General Purpose Input/Output Ports                           | 444 |

| 28.1 | Features                                                     | 444 |

| 28.2 | Functional Description                                       | 444 |

| 28.3 | GPIO Control Registers                                       | 444 |

| 28.4 | GPIO Interrupts                                              | 445 |

| 28.5 | Multi-CPU Support                                            | 446 |

| Part | 6: System Functions and Engines                              | 447 |

| 29   | High-Speed Integrated SERDES Interface                       | 449 |

| 29.1 | Features                                                     | 449 |

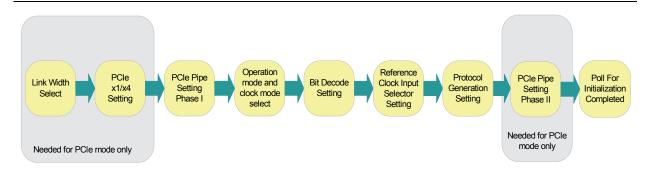

| 29.2 | Configuring a MAC-SERDES Interface for PCIe Mode             | 449 |

| 29.3 | Assigning a SERDES Lane to the Relevant MAC                  | 450 |

| 29.4 | Configure a SERDES for sETM Mode                             | 456 |

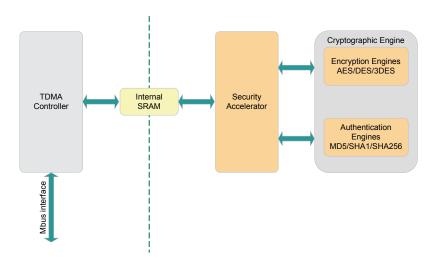

| 30   | Cryptographic Engines and Security Accelerators (CESA)       | 457 |

| 30.1 | Features                                                     | 457 |

| 30.2 | Theory of Operation                                          | 459 |

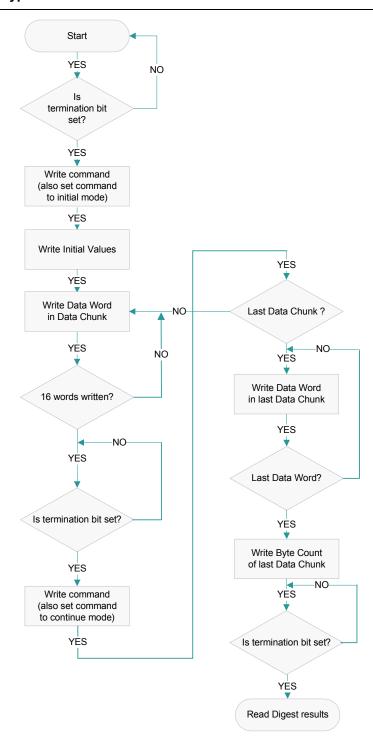

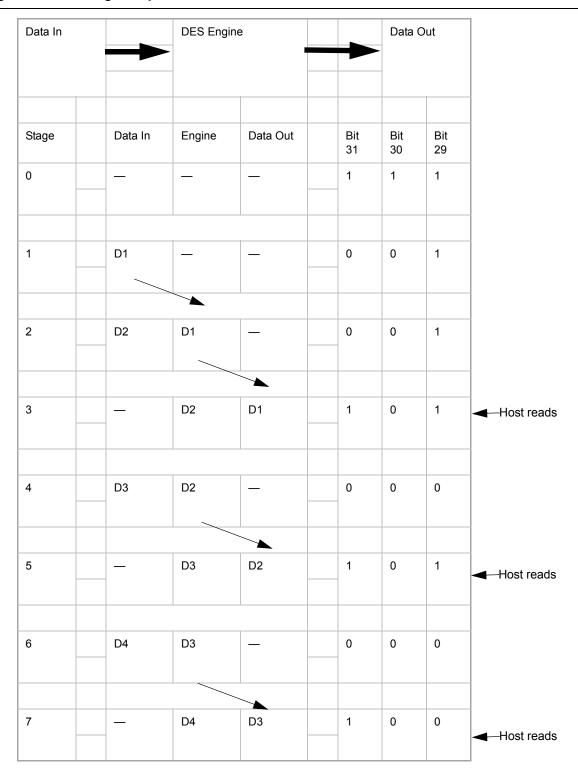

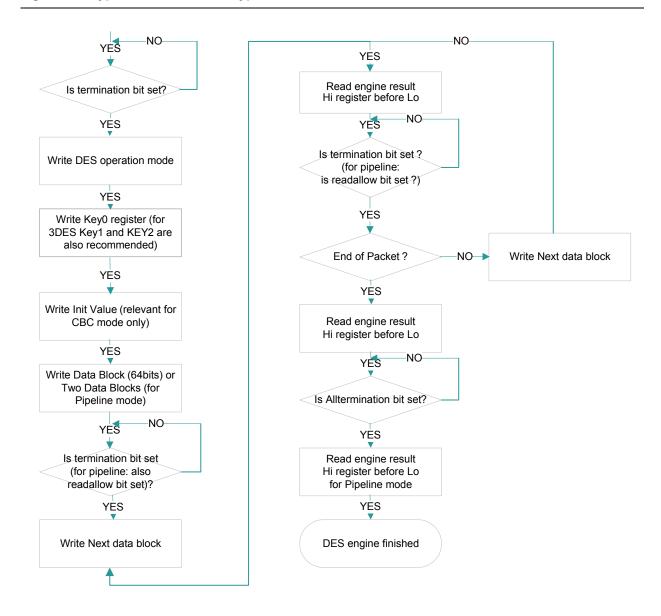

| 30.3 | Functional Description—Cryptographic Engine                  | 459 |

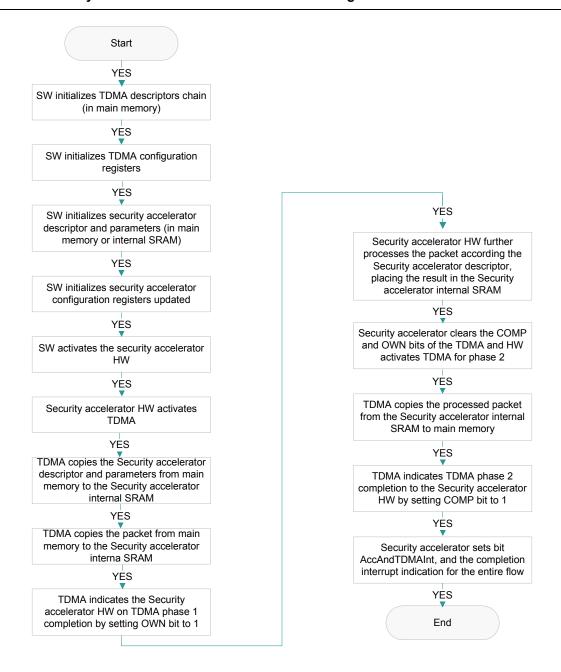

| 30.4 | Functional Description—TDMA Engine                           | 475 |

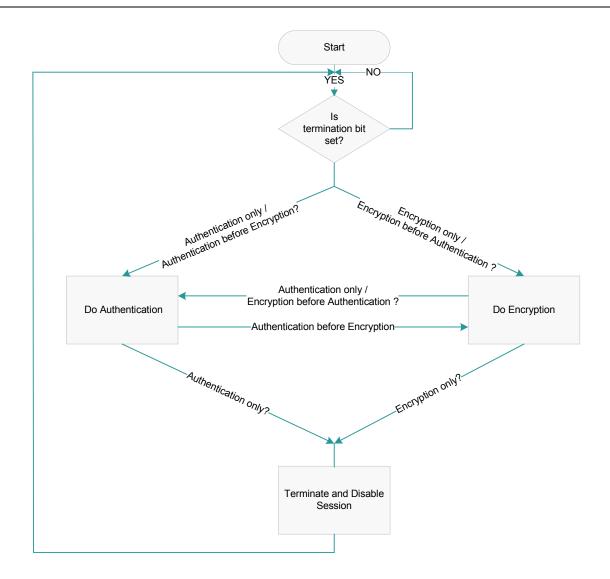

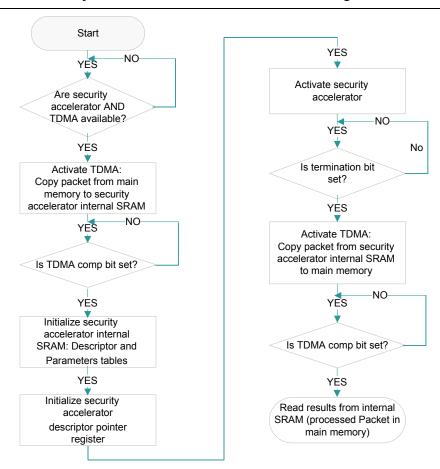

| 30.5 | Functional Description—Security Accelerator                  | 479 |

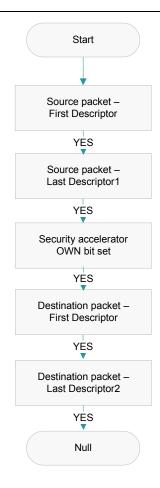

| 30.6 | Enhanced Flow Description                                    | 488 |

| 30.7 | Interrupt Coalescing                                         | 491 |

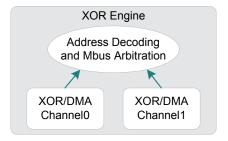

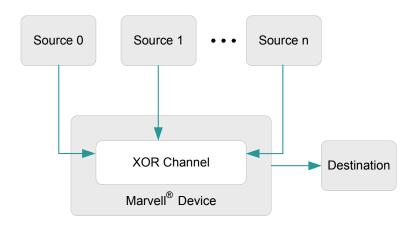

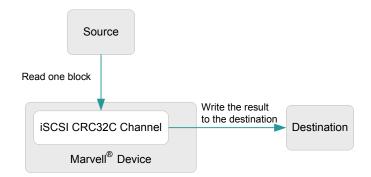

| 31   | XOR Engines                                                  | 492 |

| 31.1 | Features                                                     | 492 |

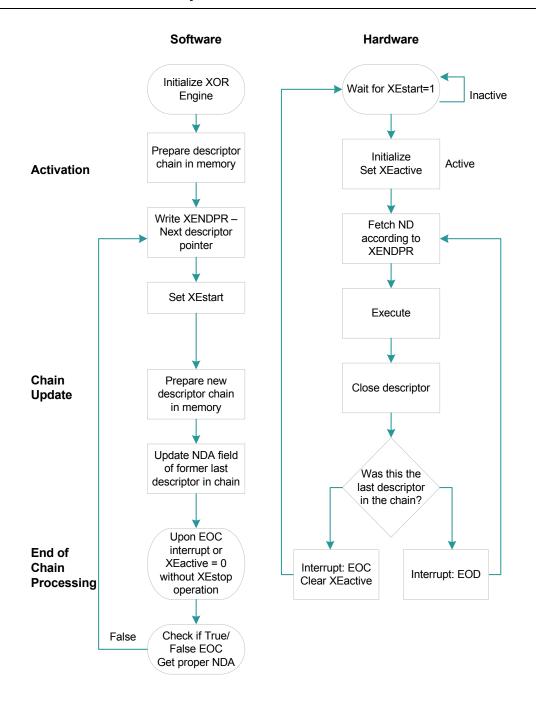

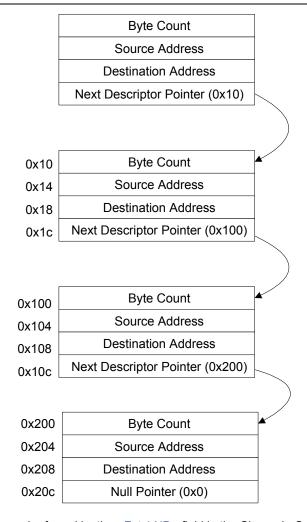

| 31.2 | Functional Description                                       | 493 |

| 31.3 | XOR Engine Modes of Operation                                | 494 |

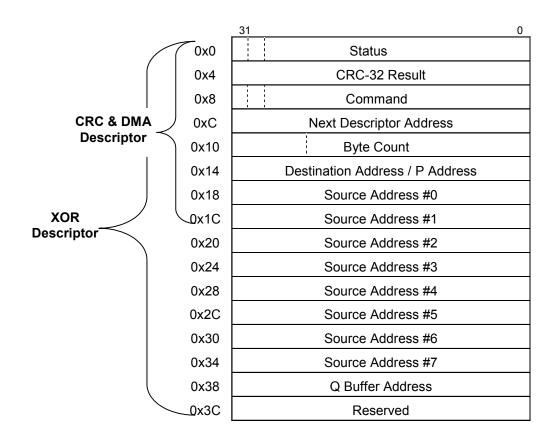

| 31.4 | Descriptor Chain Format                                      |     |

| 31.5 | Address Decoding                                             | 502 |

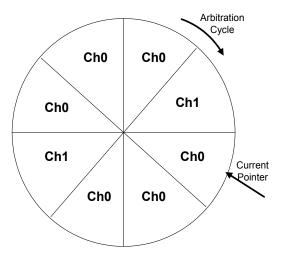

| 31.6 | Arbitration                                                  | 503 |

| 31.7 | XOR Engine Programming                                       | 504 |

| 31.8 | Burst Limit                                                  | 509 |

| 31.9         | Errors and Interrupts                                   | 509 |

|--------------|---------------------------------------------------------|-----|

| 31.10        | Performance Optimization                                |     |

|              | ·                                                       |     |

| 32           | Independent DMA (IDMA) Controller                       |     |

| 32.1         | Features                                                |     |

| 32.2         | Functional Description                                  |     |

| 32.3         | IDMA Address Decading                                   |     |

| 32.4<br>32.5 | IDMA Channel Control                                    |     |

| 32.5<br>32.6 | IDMA Channel Control                                    |     |

|              | Arbitration                                             |     |

| 32.7         | DMA Interrupts                                          | 518 |

| 33           | Electronic Fuse (eFuse)                                 | 520 |

| 33.1         | Unique Device ID Read                                   | 520 |

| 33.2         | eFuse Fields and Mapping to Secured Boot Register Space | 520 |

| 33.3         | Protection Bit Mapping                                  | 521 |

| 33.4         | eFuse Programming                                       | 521 |

| 34           | Power Management                                        | 524 |

| 34.1         | Features                                                | 524 |

| 34.2         | Functional Description                                  | 525 |

| 34.3         | Individual CPU Power Management                         |     |

| 34.4         | Multiprocessor Subsystem Power Management               |     |

| 34.5         | Dynamic Frequency Scaling (DFS)                         |     |

| 34.6         | Waking Options                                          | 531 |

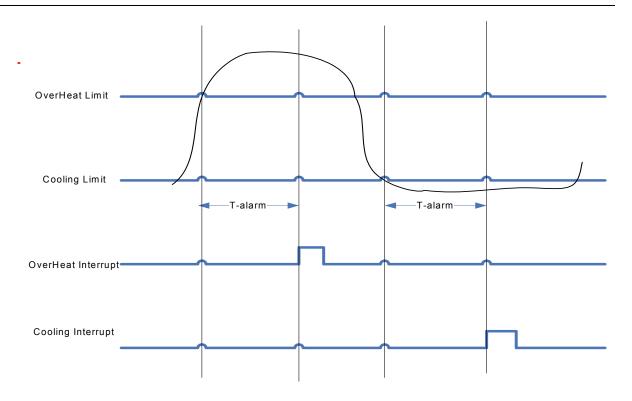

| 34.7         | Thermal Management                                      | 532 |

| 34.8         | Hardware Idle Profiling                                 | 534 |

| 34.9         | Unit Specific Power Management Options                  | 534 |

| 34.10        | Debug During Power Management (CoreSight)               | 534 |

| 34.11        | Power Management Registers                              | 535 |

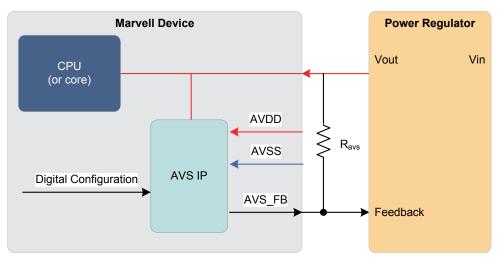

| 35           | Adaptive Voltage Scaling (AVS)                          | 537 |

| 35.1         | Features                                                |     |

| 35.2         | High-Level Functional Description                       |     |

| A            | andin A. Daniatan Cat                                   | 520 |

| Appe         | endix A: Register Set                                   | 539 |

| Α            | MV78230/78x60 Register Set                              | 598 |

| A.1          | Register Description                                    |     |

| A.2          | CPU Sub-System Registers                                |     |

| A.3          | DRAM Controller Registers                               |     |

| A.4          | NAND Flash Registers                                    |     |

| A.5          | Device Bus Registers                                    | 889 |

| A.6  | Ethernet Networking Controller and MAC Registers               | 897  |

|------|----------------------------------------------------------------|------|

| A.7  | Buffer Management Controller Registers                         | 1035 |

| A.8  | Precise Time Protocol (PTP) Registers                          | 1052 |

| A.9  | PCI Express 2.0 Registers                                      | 1078 |

| A.10 | USB 2.0 Registers                                              | 1207 |

| A.11 | Serial-ATA Host Controller (SATAHC) Registers                  | 1216 |

| A.12 | Serial Peripheral Interface (SPI) Registers                    | 1278 |

| A.13 | Time Division Multiplexing (TDM) Controller Registers          | 1288 |

| A.14 | Secure Digital Input-Output (SDIO) Registers                   | 1360 |

| A.15 | Inter-Integrated Circuit (I2C) Registers                       | 1391 |

| A.16 | UART Registers                                                 | 1401 |

| A.17 | Real Time Clock (RTC) Registers                                | 1414 |

| A.18 | General Purpose Input/Output (GPIO) Registers                  | 1420 |

| A.19 | Multi-Purpose Ports (MPP) Registers                            | 1432 |

| A.20 | Power Management Unit (PMU) Registers                          | 1435 |

| A.21 | Cryptographic Engine and Security Accelerator (CESA) Registers | 1439 |

| A.22 | XOR Registers                                                  | 1471 |

| A.23 | IDMA Registers                                                 | 1489 |

| A.24 | Electronic Fuse (eFuse) Registers                              | 1501 |

| A.25 | Core and CPU AVS Registers                                     |      |

| A.26 | System Registers                                               | 1510 |

| A.27 | Clock Complex Registers                                        |      |

## **List of Tables**

| Re  | vision Hist | ory                                                                 | 3   |

|-----|-------------|---------------------------------------------------------------------|-----|

| Pre | eface       |                                                                     | 25  |

|     | Table 1:    | Related Documents                                                   | 27  |

|     | Table 2:    | Terms and Abbreviations                                             | 29  |

| Pa  | rt 1: Ove   | rview                                                               | 33  |

| 1   | Product (   | Overview                                                            |     |

|     | Table 3:    | ARMADA® XP Device Differences and Similarities                      | 36  |

| 2   | Function    | al Overview                                                         | 41  |

| _   | Table 4:    | Four 10/100/1000 Mbps Network Ethernet Ports—Configuration Options  |     |

|     | Table 5:    | Three 10/100/1000 Mbps Network Ethernet Ports—Configuration Options |     |

| 3   | Address     | Мар                                                                 | 55  |

|     | Table 6:    | CPU Interface Mbus Decoding Units IDs and Attributes                |     |

|     | Table 7:    | Marvell® Core Processor Default Address Map                         | 59  |

|     | Table 8:    | Units IDs and Attributes                                            | 63  |

| 4   | Internal A  | Architecture                                                        | 70  |

|     | Table 9:    | Primary Clock Domains                                               | 70  |

| 5   | System 0    | Considerations                                                      | 82  |

|     | Table 10:   | ECC Code Matrix                                                     | 82  |

| 6   | BootRON     | M Firmware                                                          | 93  |

|     | Table 11:   | MMU Virtual-to-Physical Address Translation Table                   | 96  |

|     | Table 12:   | Main Header Format                                                  | 98  |

|     | Table 13:   | Secured Header Format                                               | 99  |

|     | Table 14:   | Binary (BIN) Header                                                 | 101 |

|     | Table 15:   | Register Set (REG) Header Format                                    | 101 |

|     | Table 16:   | BootROM Error Messages                                              | 114 |

|     | Table 17:   | Bad Block Indicators per NAND Flash Cell Type                       | 117 |

| Pa  | rt 2: CPU   | J Subsystem                                                         | 119 |

| 7   | Marvell®    | Core Processor                                                      | 121 |

| 8   | Level-2 C   | Cache                                                               | 122 |

|     | Table 18:   | General Memory Level-2 Cache Requests                               | 125 |

|     | Table 19:   | Core Special Maintenance Instruction L2 Requests                    | 127 |

|     | Table 20:   | Shared L2 Events                                                    | 137 |

| 9  | Multiprod  | cessor Interrupt Controller (MPIC)                                         | 139 |

|----|------------|----------------------------------------------------------------------------|-----|

|    | Table 21:  | Internal Interrupts Mapping                                                | 151 |

|    | Table 22:  | SoC Errors Mapping                                                         | 155 |

| 10 | Timers, C  | Counters, and Watchdog                                                     | 157 |

| 11 | _          | apabilities                                                                |     |

|    | Table 23:  | Trigger In Trigger Out of CTI0                                             |     |

|    | Table 24:  | Trigger In Trigger Out of CTI1                                             |     |

|    | Table 25:  | Timestamp Register Summary                                                 |     |

|    | Table 26:  | Summary of CoreSight Memory Mapped Registers—v7 Mode                       | 168 |

| Pa | rt 3: Exte | rnal Memory Interfaces                                                     | 171 |

| 12 | DRAM Co    | ontroller                                                                  | 173 |

|    | Table 27:  | DDR3 DRAM Addressing                                                       |     |

|    | Table 28:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 0</csxaddrsel> | 181 |

|    | Table 29:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 1</csxaddrsel> | 181 |

|    | Table 30:  | DDR3 Address Multiplex for 32-bit Interface, <csxaddrsel> = 0</csxaddrsel> | 181 |

|    | Table 31:  | DDR3 Address Multiplex for 32-bit Interface, <csxaddrsel> = 1</csxaddrsel> | 182 |

|    | Table 32:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 0</csxaddrsel> | 182 |

|    | Table 33:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 1</csxaddrsel> | 183 |

|    | Table 34:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 0</csxaddrsel> | 183 |

|    | Table 35:  | DDR3 Address Multiplex for 64-bit Interface, <csxaddrsel> = 1</csxaddrsel> |     |

|    | Table 36:  | DRAM Timing Parameters                                                     | 185 |

|    | Table 37:  | DDR3 Address Mirroring Mapping Table                                       | 197 |

| 13 | NAND Fla   | ash Controller (NFC)                                                       | 203 |

|    | Table 38:  | NAND Attribute Definitions                                                 |     |

|    | Table 39:  | Chip Select Assignment                                                     | 205 |

|    | Table 40:  | Command Format                                                             | 208 |

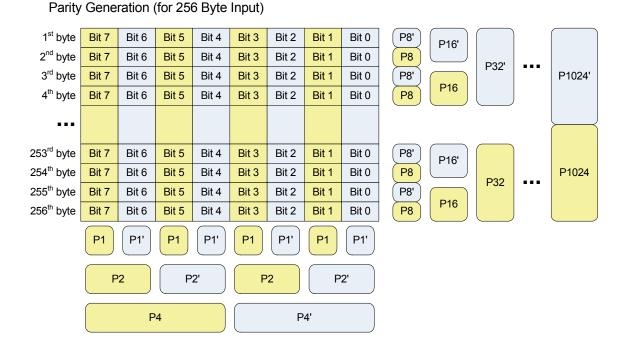

|    | Table 41:  | Spare Area Used for ECC                                                    | 209 |

|    | Table 42:  | Even Data Stream                                                           | 210 |

|    | Table 43:  | Odd Data Stream                                                            | 210 |

|    | Table 44:  | ECC Byte Placement                                                         | 211 |

|    | Table 45:  | Small Block Page Allocation                                                | 213 |

|    | Table 46:  | Large Block Page Allocation                                                | 214 |

|    | Table 47:  | 4-KB Physical or Logical Page Allocation Using 2-KB Chunks                 | 215 |

|    | Table 48:  | Read 2 KB MLC Page                                                         | 219 |

|    | Table 49:  | Read 4 KB MLC Page                                                         |     |

|    | Table 50:  | Program (Write) 2 KB MLC Page                                              |     |

|    | Table 51:  | Program (Write) 4 KB MLC Page                                              |     |

| 14 | Device B   | us Controller                                                              | 237 |

|    | Table 52:  | Read Timing Parameters                                                     | 246 |

|    | Table 53:  | Write Timing Parameters                                                    | 247 |

| Pa | rt 4: Ethe | ernet Networking Subsystem                                           | 251 |

|----|------------|----------------------------------------------------------------------|-----|

| 15 | Ethernet   | Networking Controller                                                | 253 |

|    | Table 54:  | Networking Controller Modes and Features                             |     |

|    | Table 55:  | Transmit Descriptor—Offset 0                                         | 264 |

|    | Table 56:  | Transmit Descriptor—Offset 4                                         | 266 |

|    | Table 57:  | Transmit Descriptor—Offset 8                                         | 266 |

|    | Table 58:  | Transmit Descriptor—Offset C                                         | 267 |

|    | Table 59:  | Transmit Descriptor—Offset 10                                        | 268 |

|    | Table 60:  | Transmit Descriptor—Offset 14                                        | 268 |

|    | Table 61:  | Transmit Descriptor—Offset 18                                        | 268 |

|    | Table 62:  | Transmit Descriptor—Offset 1C                                        | 268 |

|    | Table 63:  | Receive Descriptor—Offset 0                                          | 271 |

|    | Table 64:  | Receive Descriptor—Offset 4                                          | 273 |

|    | Table 65:  | Receive Descriptor—Offset 8                                          | 274 |

|    | Table 66:  | Receive Descriptor—Offset C                                          | 274 |

|    | Table 67:  | Receive Descriptor—Offset 10                                         | 274 |

|    | Table 68:  | Receive Descriptor—Offset 14                                         | 274 |

|    | Table 69:  | Receive Descriptor—Offset 18                                         | 275 |

|    | Table 70:  | Receive Descriptor—Offset 1C                                         | 275 |

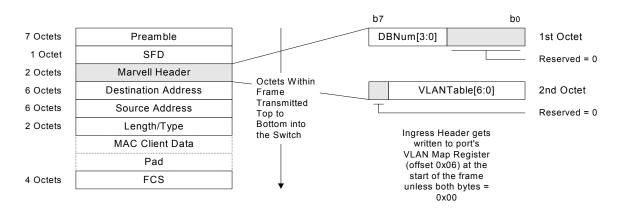

|    | Table 71:  | Marvell Header Fields                                                | 280 |

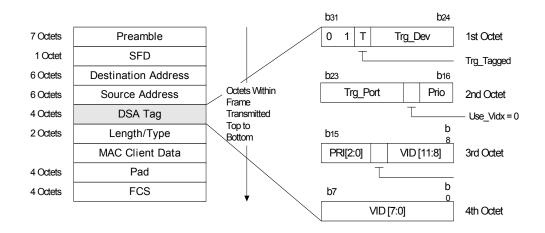

|    | Table 72:  | DSA Tag Fields (TO_CPU Format)                                       | 283 |

|    | Table 73:  | DSA Tag Fields (FORWARD Format)                                      | 284 |

|    | Table 74:  | Token Rate Configuration Examples                                    | 293 |

|    | Table 75:  | Token Bucket Attributes                                              | 294 |

|    | Table 76:  | Bandwidth Limitation Configuration Example for a 5-ns (200 MHz) TCLK | 295 |

| 16 | Hardwar    | e Buffer Management Controller                                       | 301 |

| 17 | 1G/2.5G    | Ethernet MAC                                                         | 308 |

|    | Table 77:  | Definitions for MAC MIB Counters                                     | 316 |

| 18 | Precise 1  | Time Protocol (PTP)                                                  | 320 |

|    |            |                                                                      |     |

| Pa | rt 5: Exte | ernal Interfaces                                                     | 331 |

| 19 | PCI Expr   | ress Interface (PCIe) 2.0                                            |     |

|    | Table 78:  | Supported Message Groups—Root Complex Mode                           |     |

|    | Table 79:  | Supported Message Groups—Endpoint Mode                               |     |

|    | Table 80:  | Physical Layer Error List                                            |     |

|    | Table 81:  | Data Link Layer Error List                                           |     |

|    | Table 82:  | Transaction Layer Error List                                         | 345 |

| 20 | Universa   | Il Serial Bus (USB 2.0) Interface                                    | 352 |

| 21 |            | ΓA (SATA) II Interface                                               |     |

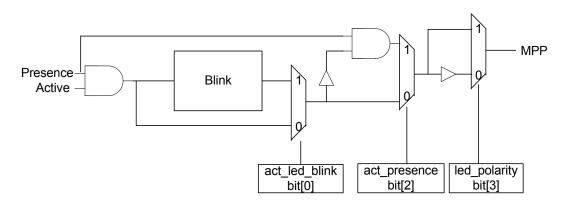

|    | Table 83:  | Disc Status LED State Settings                                       | 356 |

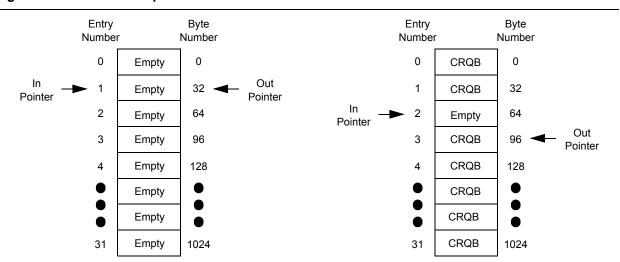

|    | Table 84:   | EDMA CRQB Data Structure Map                                   | 369 |

|----|-------------|----------------------------------------------------------------|-----|

|    | Table 85:   | CRQB DW0—cPRD Descriptor Table Base Low Address                | 369 |

|    | Table 86:   | CRQB DW1—cPRD Descriptor Table Base High Address               |     |

|    | Table 87:   | CRQB DW2—Control Flags                                         | 370 |

|    | Table 88:   | CRQB DW3—Data Region Byte Count                                | 370 |

|    | Table 89:   | CRQB DW4—ATA Command                                           | 371 |

|    | Table 90:   | CRQB DW5—ATA Command                                           | 371 |

|    | Table 91:   | CRQB DW6—ATA Command                                           | 371 |

|    | Table 92:   | CRQB DW7—ATA Command                                           | 372 |

|    | Table 93:   | ePRD Table Data Structure Map                                  | 373 |

|    | Table 94:   | ePRD DWORD 0                                                   | 373 |

|    | Table 95:   | ePRD DWORD 1                                                   | 373 |

|    | Table 96:   | ePRD DWORD 2                                                   | 373 |

|    | Table 97:   | ePRD DWORD 3                                                   | 374 |

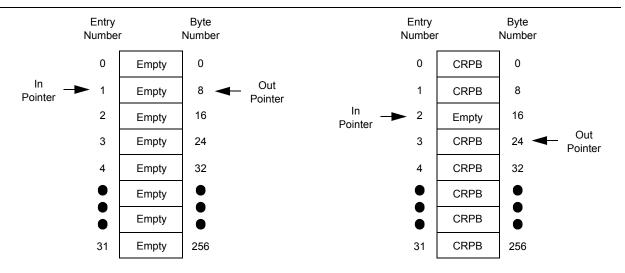

|    | Table 98:   | EDMA CRPB Data Structure Map                                   | 374 |

|    | Table 99:   | CRPB ID Register                                               | 375 |

|    | Table 100:  | CRPB Response Flags Register                                   | 375 |

|    | Table 101:  | CRPB Time Stamp Register                                       | 375 |

| 22 | Serial Per  | ipheral Interface (SPI)                                        | 378 |

| 23 | Time-Divi   | sion Multiplexing (TDM) Controller                             | 386 |

|    |             | IOM2-LC (connected to channel 3) GCI                           |     |

|    | Table 103:  | MCDMA Descriptor—Command/Status Word                           | 395 |

|    | Table 104:  | MCDMA Channel-x Command/Status Field for HDLC Mode             | 396 |

|    | Table 105:  | MCDMA Channel-x Command/Status Field for Transparent Mode      | 397 |

|    | Table 106:  | MCDMA Descriptor—Buffer Size, Byte Count (Rx Descriptor)       | 398 |

|    | Table 107:  | MCDMA Descriptor—Byte Count, Shadow Byte Count (Tx Descriptor) | 398 |

|    | Table 108:  | MCDMA Descriptor—Buffer Pointer (Rx Descriptor)                | 398 |

|    | Table 109:  | MCDMA Descriptor—Buffer Pointer (Tx Descriptor)                | 399 |

|    | Table 110:  | MCDMA Descriptor—Next Descriptor Pointer                       | 399 |

|    | Table 111:  | MCDMA Definitions                                              | 402 |

|    | Table 112:  | IQC Interrupt Entry Structure                                  | 405 |

| 24 | Secure Di   | gital Input/Output (SDIO) Controller                           | 413 |

|    | Table 113:  | Software Flow                                                  | 417 |

| 25 | Inter-Integ | grated Circuit Interface (I <sup>2</sup> C)                    | 420 |

|    |             | I <sup>2</sup> C Control Register Bits                         |     |

|    | Table 115:  | I <sup>2</sup> C Status Codes                                  | 424 |

| 26 | Universal   | Asynchronous Receiver/Transmitter (UART) Interface             | 432 |

|    | Table 116:  | Typical Baud Rates, TCLK = 200 MHz                             | 435 |

|    | Table 117:  | Typical Baud Rates, TCLK = 250 MHz                             | 436 |

| 27 | Real-Time   | e Clock (RTC)                                                  | 439 |

|    | Table 118:  | Alarm Interrupt Valid Bit Usage                                | 441 |

|    | Table 119: | External Alarm Real Time Calculation NSM Definition                           | 443 |

|----|------------|-------------------------------------------------------------------------------|-----|

| 28 | General P  | urpose Input/Output Ports                                                     | 444 |

| Pa | rt 6: Syst | em Functions and Engines                                                      | 447 |

| 29 | • .        | ed Integrated SERDES Interface                                                |     |

|    |            | PCIe Pipe Configurations                                                      |     |

|    |            | PHY MODE and REF_FREF_SEL Setting                                             |     |

|    |            | SEL_BITS Setting                                                              |     |

|    |            | REFCLK_SEL Setting                                                            |     |

|    |            | PIN_PHY_GEN Setting                                                           |     |

|    |            | PCIe Pipe Configurations                                                      |     |

|    | Table 126: | Completion Indications                                                        | 455 |

| 30 |            | aphic Engines and Security Accelerators (CESA)                                |     |

|    |            | DES Command Register Status Bits and Their Meaning                            |     |

|    | Table 128: | DES Encryption / Decryption Write Operation Result                            | 466 |

|    | Table 129: | AES128 Encryption Write Operation Result                                      | 470 |

|    | Table 130: | TDMA Descriptor Definitions                                                   | 475 |

|    | Table 131: | Security Accelerator Data Structure DWORD 0—Configuration                     | 484 |

|    | Table 132: | Security Accelerator Data Structure DWORD 1—Encryption Pointers               | 485 |

|    | Table 133: | Security Accelerator Data Structure DWORD 2— Encryption Data Length           | 485 |

|    | Table 134: | Security Accelerator Data Structure DWORD 3—Encryption Keys Pointer           | 486 |

|    | Table 135: | Security Accelerator Data Structure DWORD 4—Encryption Initial Values Pointer | 486 |

|    | Table 136: | Security Accelerator Data Structure DWORD 5—MAC Source Pointer                | 486 |

|    | Table 137: | Security Accelerator Data Structure DWORD 6—MAC Digest                        | 487 |

|    | Table 138: | Security Accelerator Data Structure DWORD 7—MAC Initial Values Pointers       | 487 |

| 31 | XOR Engi   | nes                                                                           | 492 |

|    | Table 139: | Descriptor Status Word Definition                                             | 499 |

|    | Table 140: | Descriptor CRC-32 Result Word Definition                                      | 499 |

|    | Table 141: | Descriptor Command Word Definition                                            | 499 |

|    | Table 142: | Descriptor Next Descriptor Address Word                                       | 501 |

|    | Table 143: | Descriptor Byte Count Word                                                    | 501 |

|    | Table 144: | Descriptor Destination Address Word                                           | 501 |

|    | Table 145: | Descriptor Source Address #N Words                                            | 502 |

|    | Table 146: | EOC/EOD interpretation                                                        | 509 |

| 32 | Independ   | ent DMA (IDMA) Controller                                                     | 511 |

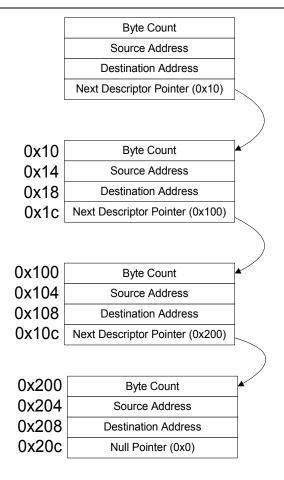

|    | Table 147: | DMA Descriptor Definitions                                                    | 512 |

| 33 | Electronic | Fuse (eFuse)                                                                  | 520 |

|    | Table 148: | Internal eFuse Mapping                                                        | 520 |

|    | Table 149: | Secured Boot Register Space                                                   | 520 |

|    | Table 150: | Protection Bits Mapping                                                       | 521 |

| 34 | Power Management                                                                               | 524     |

|----|------------------------------------------------------------------------------------------------|---------|

|    | Table 151: CPU Core Power Modes                                                                | 525     |

|    | Table 152: CPU Core Power Management Registers Pointers                                        | 535     |

| 35 | Adaptive Voltage Scaling (AVS)                                                                 | 537     |

| Аp | pendix A: Register Set                                                                         | 539     |

| Α  | MV78230/78x60 Register Set                                                                     | 598     |

|    | Table 153: Standard Register Field Type Codes                                                  | 598     |

|    | Table 154: Summary Map Table for the CPU Sub-System Registers                                  | 600     |

|    | Table 438: Summary Map Table for the DRAM Controller Registers                                 | 763     |

|    | Table 533: Summary Map Table for the NAND Flash Registers                                      | 856     |

|    | Table 547: Summary Map Table for the Device Bus Registers                                      | 889     |

|    | Table 557: Summary Map Table for the Ethernet Networking Controller and MAC Registers          | 897     |

|    | Table 732: Summary Map Table for the Buffer Management Controller Registers                    | 1035    |

|    | Table 763: Summary Map Table for the PTP Registers                                             | 1052    |

|    | Table 797: Summary Map Table for the PCI Express 2.0 Registers                                 | 1078    |

|    | Table 922: Summary Map Table for the USB 2.0 Registers                                         | 1207    |

|    | Table 938: Summary Map Table for the Serial-ATA Host Controller (SATAHC) Registers             | 1216    |

|    | Table 1020: Shadow Register Block Registers Map                                                | 1277    |

|    | Table 1021: Summary Map Table for the SPI Registers                                            | 1278    |

|    | Table 1036: Summary Map Table for the Time Division Multiplexing (TDM) Controller Registers    | 1288    |

|    | Table 1148: Summary Map Table for the SDIO Registers                                           | 1360    |

|    | Table 1200: Summary Map Table for the Inter-Integrated Circuit (I2C) Registers                 |         |

|    | Table 1218: Summary Map Table for the UART Registers                                           | 1401    |

|    | Table 1235: Summary Map Table for the RTC Registers                                            | 1414    |

|    | Table 1246: Summary Map Table for the General Purpose Input/Output (GPIO) Registers            | 1420    |

|    | Table 1283: Summary Map Table for the Multi-Purpose Ports (MPP) Registers                      | 1432    |

|    | Table 1288: Summary Map Table for the Power Management Unit Registers                          | 1435    |

|    | Table 1298: Summary Map Table for the Cryptographic Engine and Security Accelerator (CESA) Res | gisters |

|    | Table 1374: Summary Map Table for the XOR Registers                                            | 1471    |

|    | Table 1397: Summary Map Table for the IDMA Registers                                           | 1489    |

|    | Table 1415: Summary Map Table for the Electronic Fuse (eFuse) Registers                        | 1501    |

|    | Table 1426: Summary Map Table for the Core and CPU AVS Registers                               | 1507    |

|    | Table 1431: Summary Map Table for the System Registers                                         | 1510    |

|    | Table 1470: Summary Man Table for the Clock Complex Registers                                  | 1541    |

# **List of Figures**

| Pa | rt 1: Ove  | rview                                                     | 33  |

|----|------------|-----------------------------------------------------------|-----|

| 1  | Product (  | Overview                                                  | 35  |

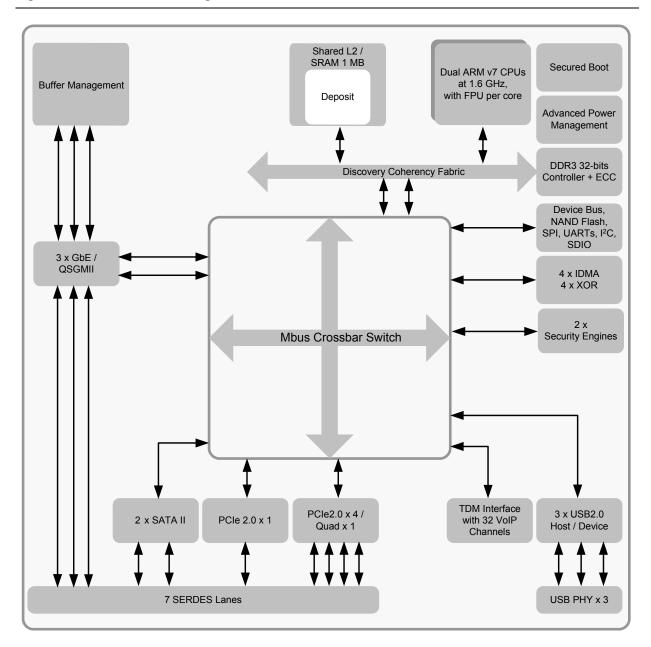

|    | Figure 1:  | MV78230 Block Diagram                                     |     |

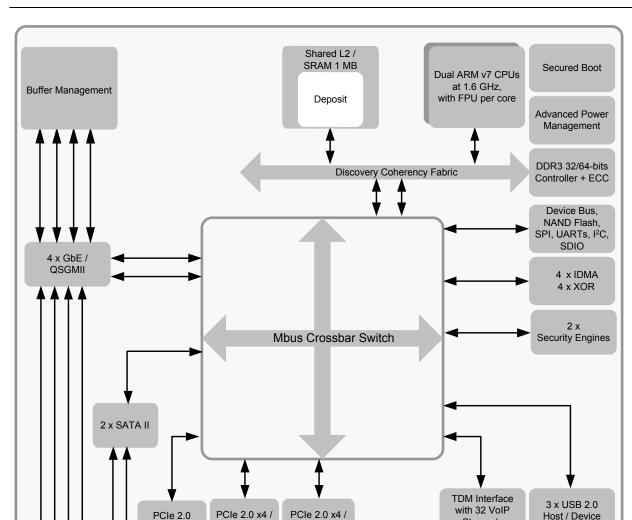

|    | Figure 2:  | MV78260 Block Diagram                                     | 39  |

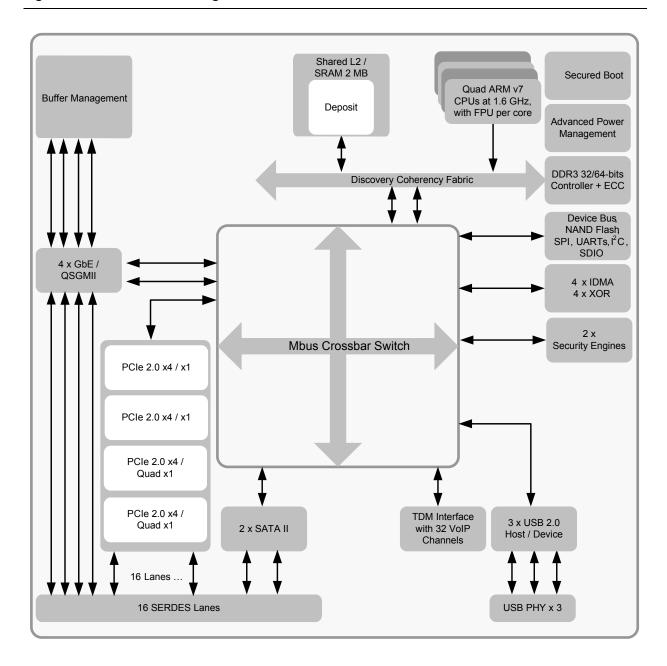

|    | Figure 3:  | MV78460 Block Diagram                                     | 40  |

| 2  | Function   | al Overview                                               | 41  |

| 3  | Address    | Мар                                                       | 55  |

| 4  | Internal A | Architecture                                              | 70  |

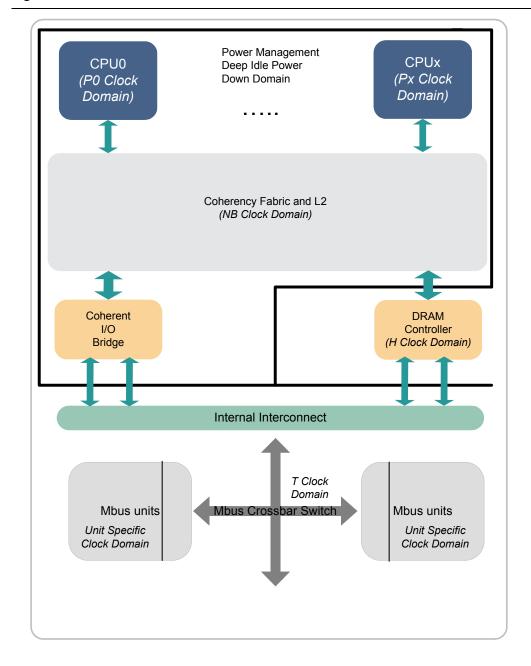

|    | Figure 4:  | ARMADA® XP Clock and Power Domains                        | 71  |

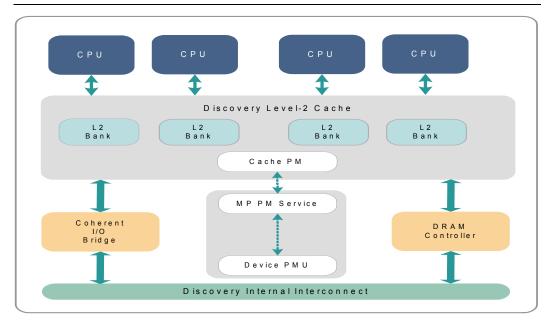

|    | Figure 5:  | Coherency Fabric Interconnect to Mbus and DRAM Controller | 73  |

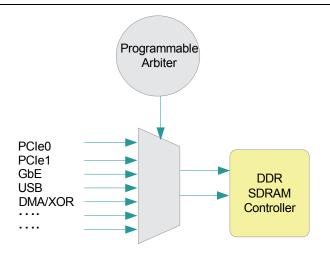

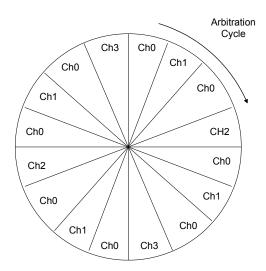

|    | Figure 6:  | SDRAM Interface Arbitration                               | 76  |

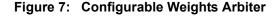

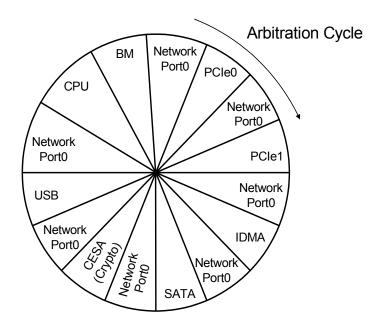

|    | Figure 7:  | Configurable Weights Arbiter                              | 77  |

| 5  | System C   | Considerations                                            | 82  |

| 6  | BootROM    | // Firmware                                               | 93  |

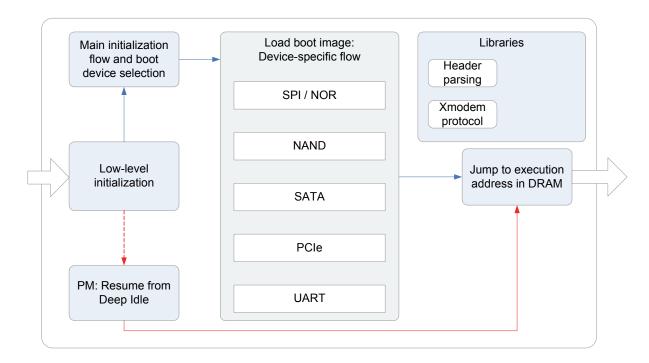

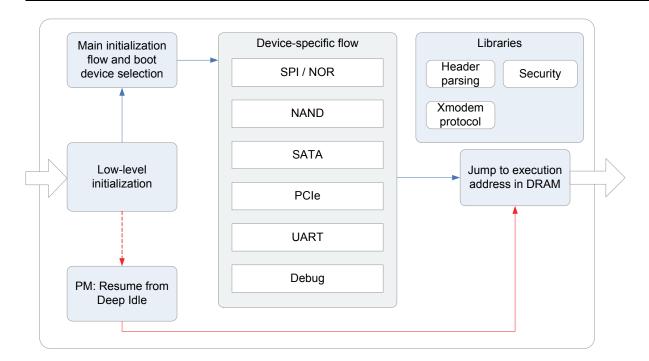

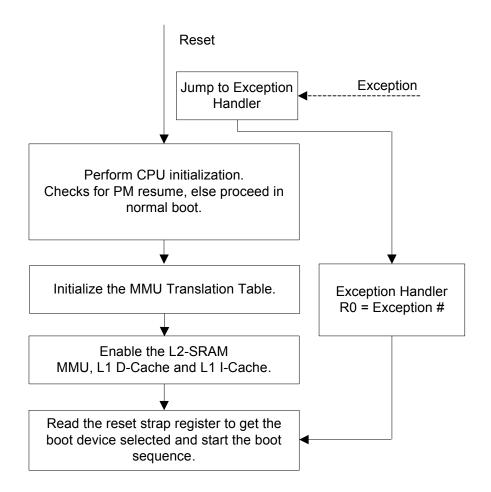

|    | Figure 8:  | BootROM Firmware Flow                                     | 93  |

|    | Figure 9:  | BootROM Firmware Block Diagram                            | 94  |

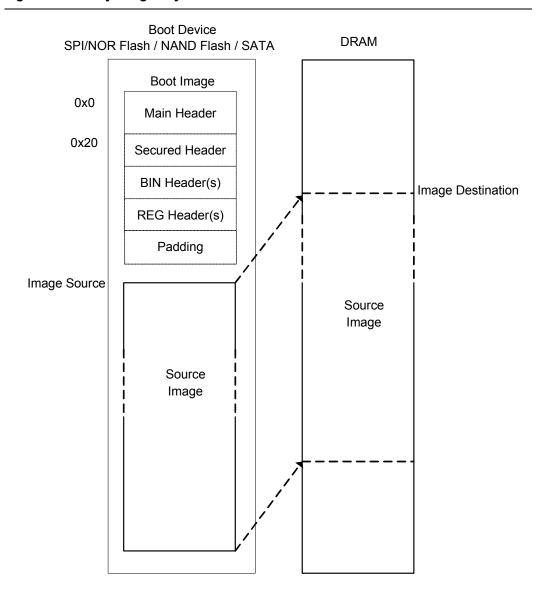

|    | Figure 10: | Binary Image Layout in the Boot Device                    | 97  |

|    | Figure 11: | Initialization and Boot Method Selection Flow             | 104 |

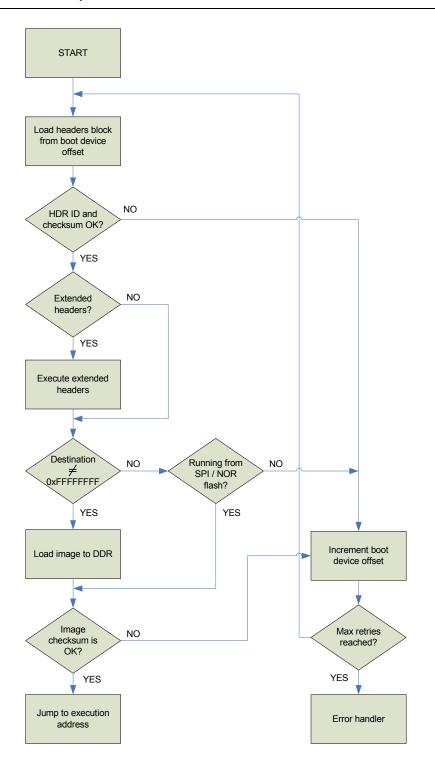

|    | Figure 12: | Boot Sequence                                             | 109 |

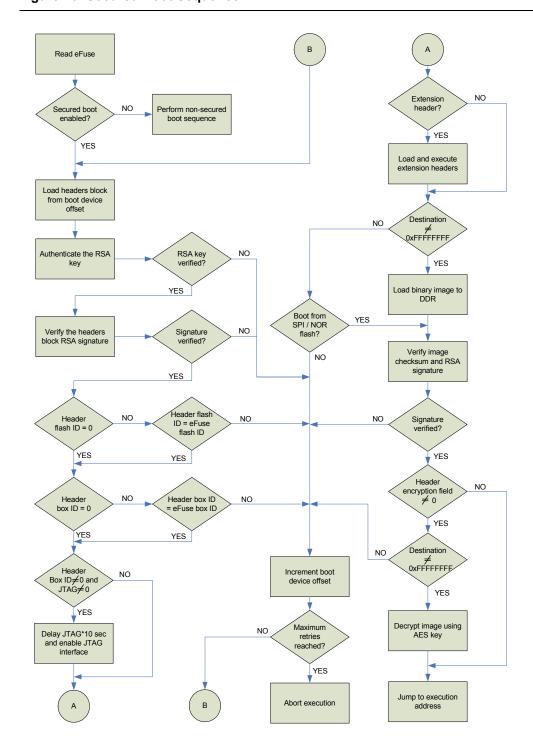

|    | Figure 13: | Secured Boot Sequence                                     | 112 |

| Pa | rt 2: CPU  | J Subsystem                                               | 119 |

| 7  | Marvell®   | Core Processor                                            | 121 |

| 8  | Level-2 C  | Cache                                                     | 122 |

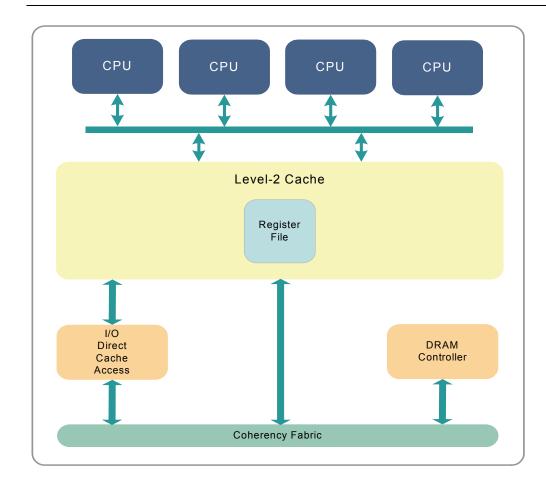

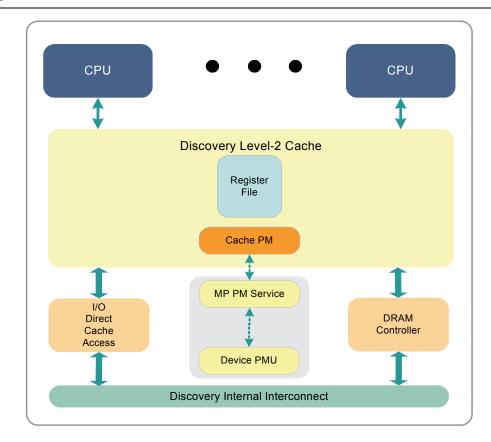

|    | Figure 14: | Quad Core Level-2 Cache High-Level Block Diagram          | 123 |

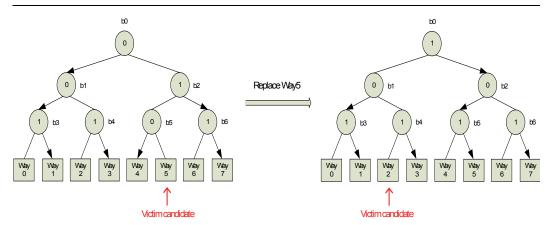

|    | Figure 15: | pLRU 8-Way Tree Example                                   | 131 |

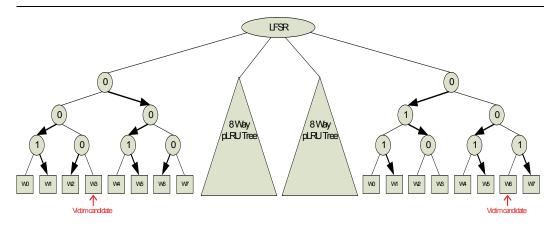

|    | Figure 16: | Semi-pLRU for 32 Ways                                     | 131 |

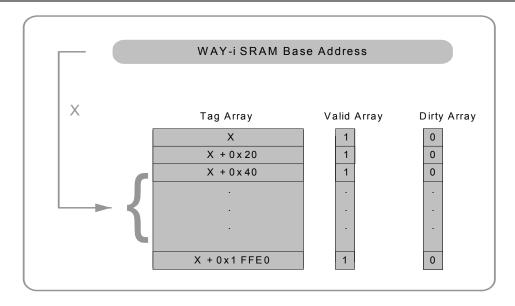

|    | Figure 17: | SRAM Initialization per Way                               | 133 |

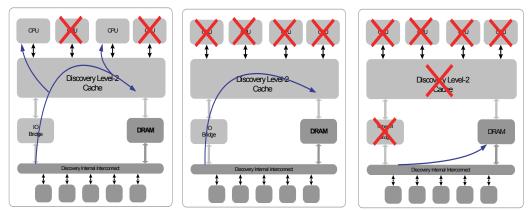

|    | Figure 18: | L2 Power Down                                             | 138 |

| 9  | -          | cessor Interrupt Controller (MPIC)                        |     |

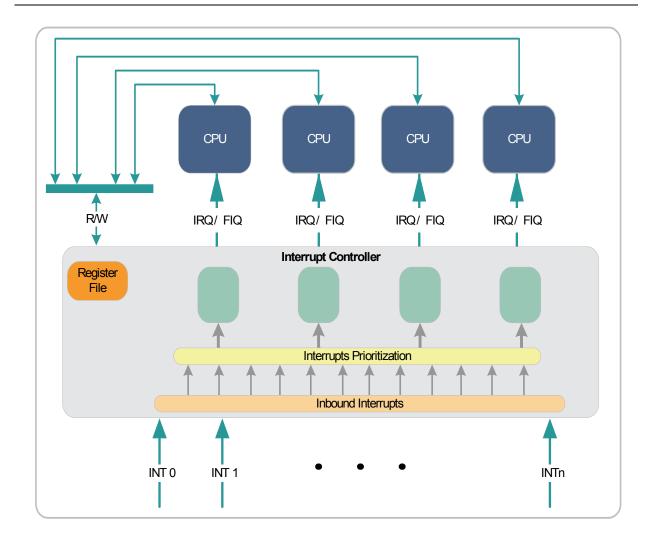

|    | Figure 19: |                                                           |     |

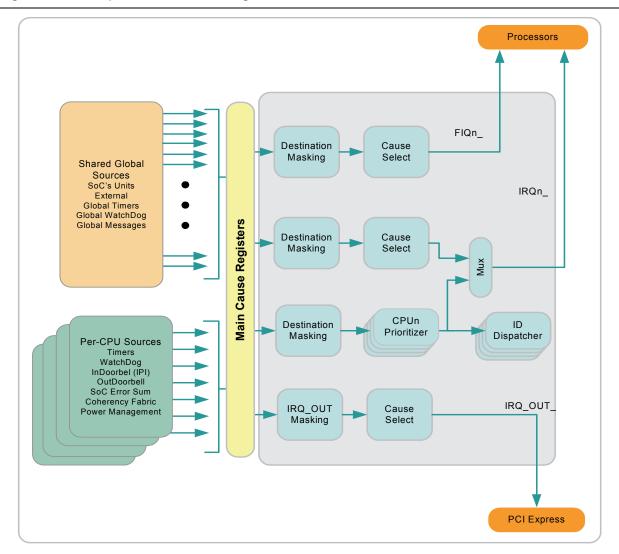

|    | Figure 20: | Interrupt Sources Block Diagram                           |     |

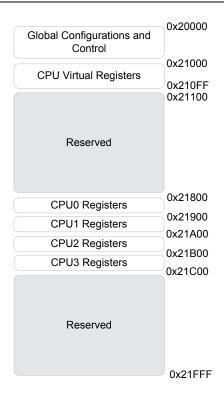

|    | Figure 21: | MP Subsystem Register File Mapping                        |     |

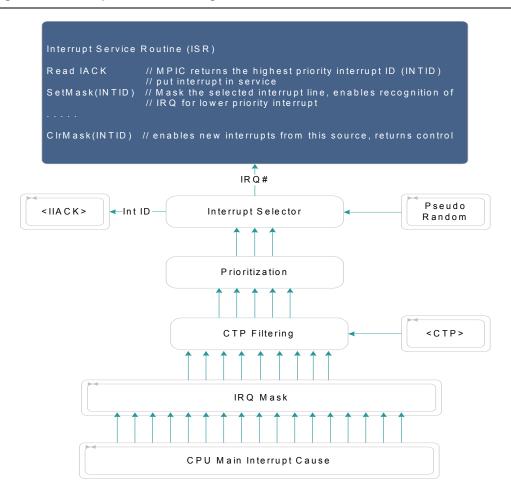

|    | Figure 22: | Interrupt IRQ Processing Flow                             | 146 |

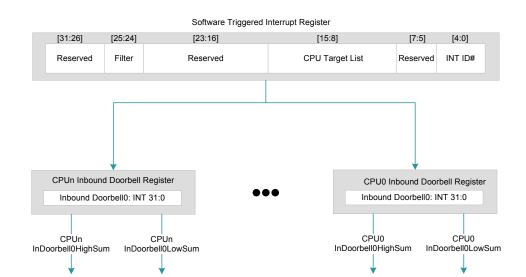

| Figure 24: MSI-X Capturing Scheme Using the Software Trigger Interrupt, Quad-CPU Configuration   148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | Figure 23: | IPI Dispatching Scheme Using the Software Trigger Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 147 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 25: Multiprocessor Timers Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | Figure 24: | MSI-X Capturing Scheme Using the Software Trigger Interrupt, Quad-CPU Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 148 |

| Figure 25: Multiprocessor Timers Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 | Timers C   | ounters, and Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 157 |