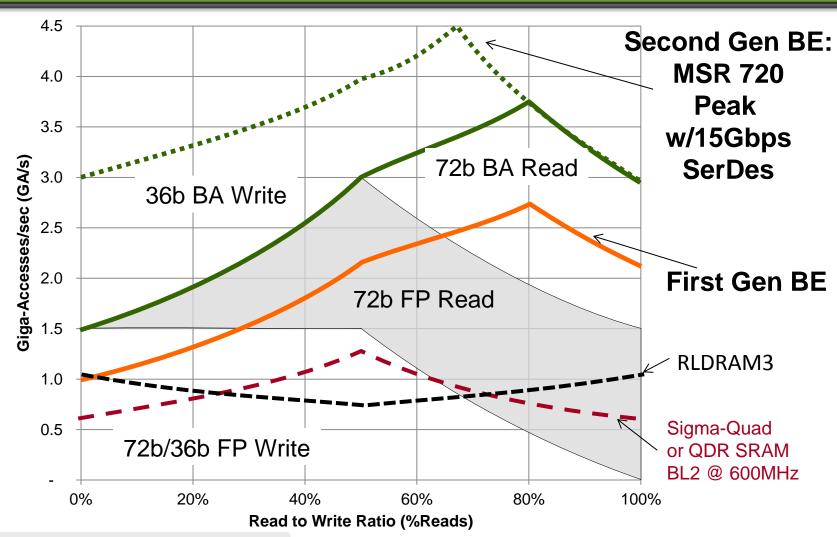

## Second Generation Bandwidth Engine® IC Breaks 4.5 Billion Accesses/sec

Michael J. Miller VP, Technology Innovation & System Applications

## The Vision: Fast, Intelligent Access Architecture

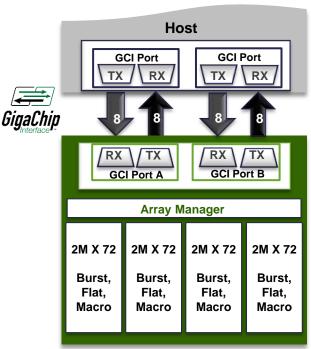

# Bandwidth Engine 2 Architecture & Family Sampling Now

- Parallel Array Architecture ... Performance up to:

- 16 outstanding transactions

- 4.5G Accesses per second

- 192 Gbps full duplex throughput

- ~12ns deterministic read latency

- 2.7ns Random cycle time (tRC)

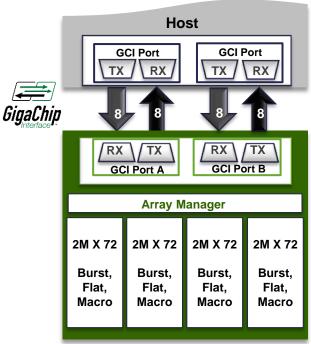

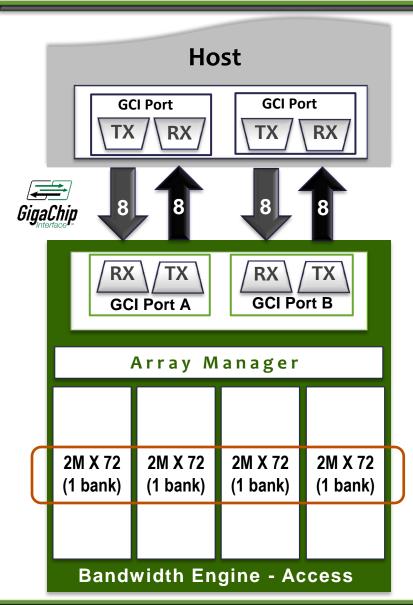

- GigaChip Interface ... 90% Efficient Transport Protocol

- Up to sixteen low latency SerDes lanes (8G to 15G)

- High Reliability ...70X better SER than 6T-SRAM

- Full ECC support; 72bit array and macro datapath operations

and Compression

- CRC protected and self recovering GigaChip Interface

- SEU resistant 1T-SRAM Memory core: < 10 FIT/Mb</li>

Pandwidth Engina

Bit Safe™ Self Test and Self Repair Option

|                              |              | Ва               | inawiath Engine – | Z <sup>iiii</sup> Generation                       |

|------------------------------|--------------|------------------|-------------------|----------------------------------------------------|

| Applications                 | BE1 - MSR576 | MSR620           | MSR820            | MSR720                                             |

| Lookup, LPM, Hash            |              | Highest sing     | s Rate            |                                                    |

| Statistics                   | Onboard ALU  |                  | Onboard ALU+      |                                                    |

| Buffer – up to 80% efficient |              | Per cycle Burst, | Write Broadcast   |                                                    |

| Metering, Dual Ops           |              | Fixed Macro      |                   |                                                    |

| Semaphore, Link List         |              |                  | Atomic Ops        |                                                    |

| State, Queuing, Link List    |              |                  |                   | Dual Port w/ Data Coherency,<br>36 bit word access |

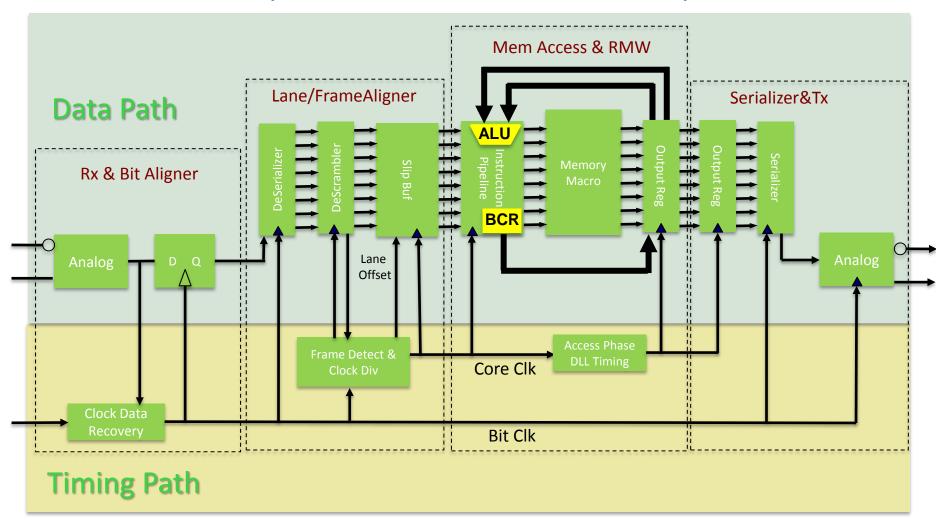

### **Functional Design**

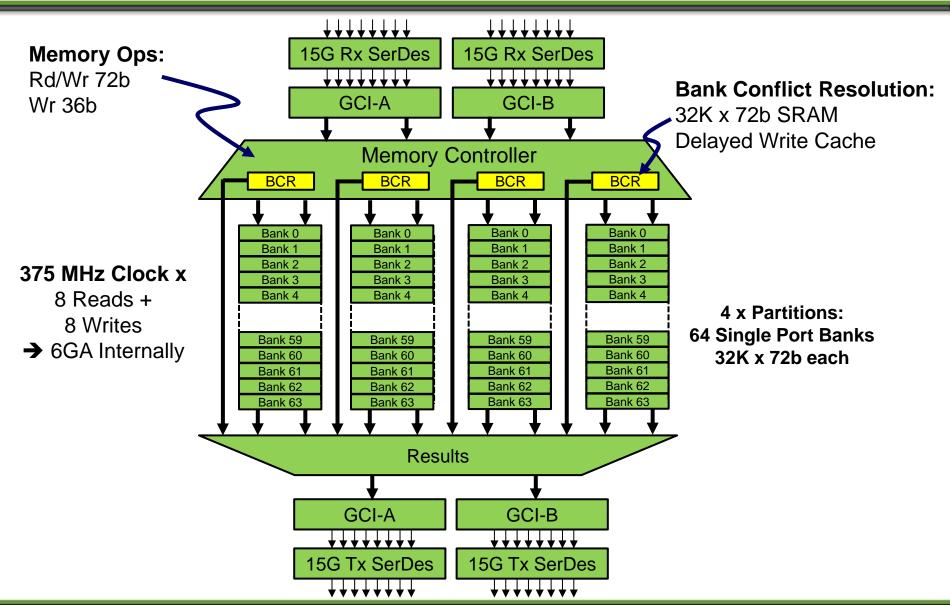

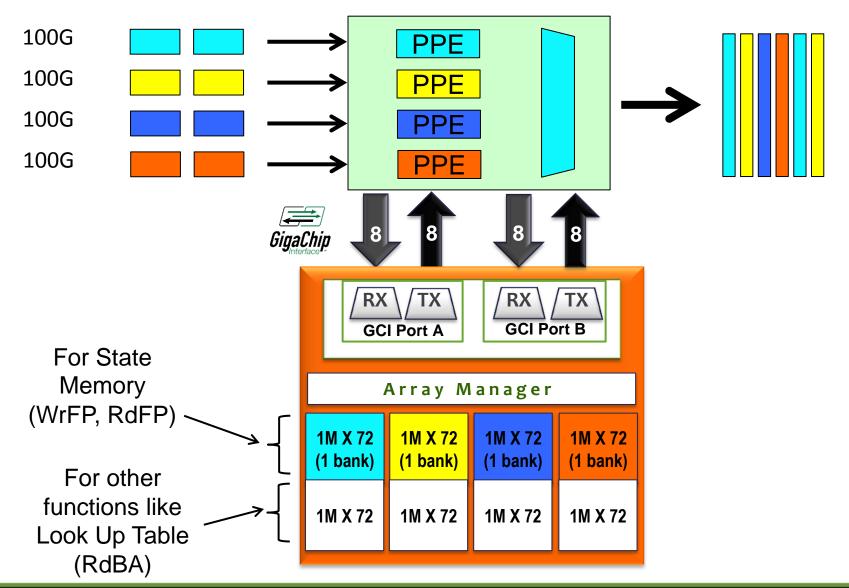

#### **Bandwidth Engine MSR720 Architecture**

### **MSR720:** Bandwidth Engine 2 – Access

- Simultaneous Read & Write @ same address

- ... treat each partition as a single bank

- ... >>2x the access performance of QDR SRAM

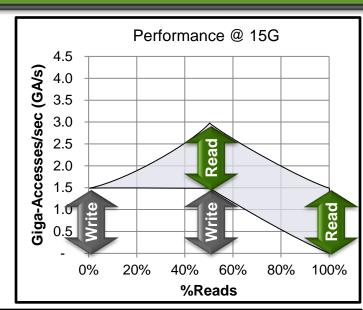

- 4.5GA: 3 billion reads/sec, 1.5B 36b write/sec

- 72b & 36b words each access

- 12 ns read latency pin to pin

- 2.7ns tRC cycle time

- 8.5W @ 12.5G system power

- ... 90% efficient transport protocol

- Up to Sixteen 15G serial lanes (2 links of 8 lanes)

- High Density

- ... 576Mbit 1T-SRAM ® memory core

- 19mm x 19mm package 1mm pitch

- High Reliability

- ... 70X better SER than 6T-based SRAM

- Memory core: < 10 FIT/Mb native</p>

- Interface: < 1 FIT</p>

- Bit Safe™ Self Test and Self Repair Option

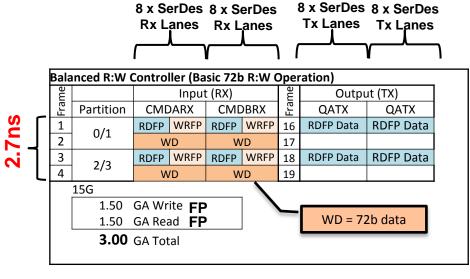

#### MSR720: Basic 'Dual Port' Operation

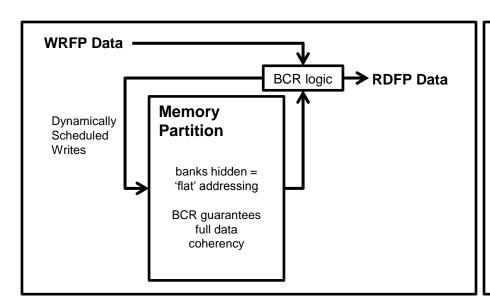

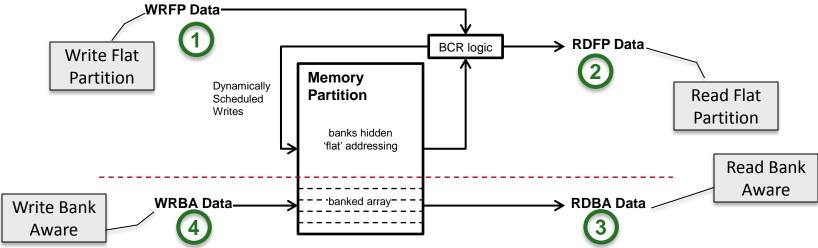

#### Flat Partition Mode:

- Double the effective bandwidth in worst case:

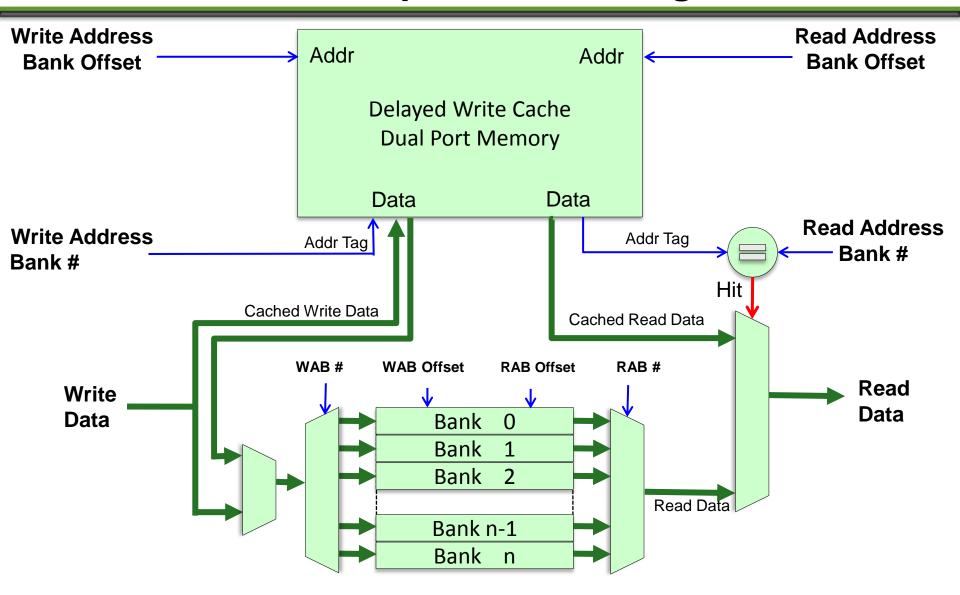

- Bank Conflict Resolution (BCR) function allows for simultaneous Read and Write of the same bank

- Implements dual port behavior with single port banks

- Guarantees data coherency

- 3 billion accesses / sec @ 15G

|               | Scheduling Balanced R:W |           |      |      |       |             |      |  |  |  |

|---------------|-------------------------|-----------|------|------|-------|-------------|------|--|--|--|

| Bala          | Balanced R:W Controller |           |      |      |       |             |      |  |  |  |

| Frame         |                         | Input     | (RX) |      | Frame | Output (TX) |      |  |  |  |

| Fra           | Partition               | CMDARX    | CMD  | BRX  | Fra   | QATX        | QATX |  |  |  |

| 1             | 0/1                     | RDFP WRFP | RDFP | WRFP | 16    | RDFP        | RDFP |  |  |  |

| 2             | 0/1                     | WD W      |      | 'D   | 17    |             |      |  |  |  |

| 3             | 2/3                     | RDFP WRFP | RDFP | WRFP | 18    | RDFP        | RDFP |  |  |  |

| 4             | 2/3                     | WD        | WD   |      | 19    |             |      |  |  |  |

| 15G           |                         |           |      |      |       |             |      |  |  |  |

| 1.50 GA Write |                         |           |      |      |       |             |      |  |  |  |

| 1.50 GA Read  |                         |           |      |      |       |             |      |  |  |  |

| 3.00 GA Total |                         |           |      |      |       |             |      |  |  |  |

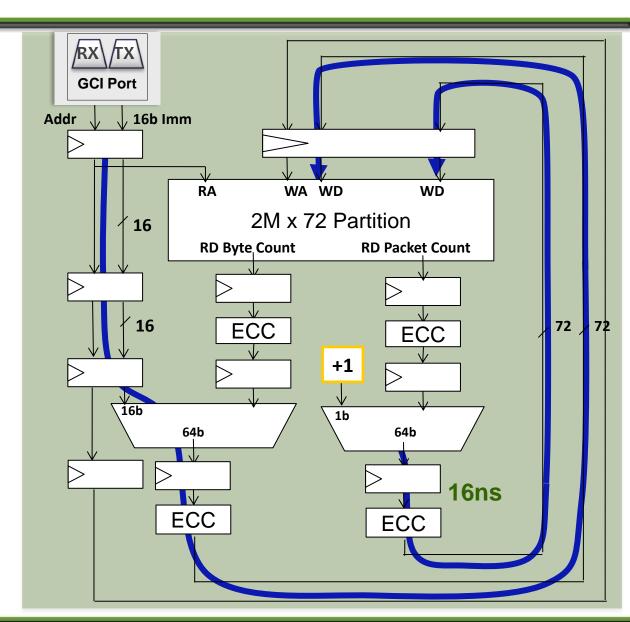

# "BCR" Implemented w/Delayed Write Cache Conceptual Block Diagram

# Up to 4 Accesses Per Partition In One Cycle 3 Accesses Sustained Throughput

#### The MSR720 supports Bank Aware commands.

This can be used to improve the data read performance on the interface, however bypasses the BCR logic

- Useful for unified memory applications combining dual port SRAM performance of "buffers" or "state" tables and read-only "lookup" tables

- The two address ranges cannot overlap.

#### MSR720 supports 36b write operations: WRFP and WRBA

- Useful for small word size tables (pointers)

- Increases write performance

#### **Mapping Ports and Banks**

### **MSR720 Access Scheduling**

Flat Partition guarantees no bank conflict between read and write to any address, even in the same cycle

| Nati                 | Native BE Controller (36b WRITES) |                   |             |              |      |       |             |      |   |

|----------------------|-----------------------------------|-------------------|-------------|--------------|------|-------|-------------|------|---|

| Frame                |                                   | Input (RX)        |             |              |      | Frame | Output (TX) |      | ] |

| Fra                  | Partition                         | CME               | DARX CMDBRX |              | Fra  | QATX  | QATX        |      |   |

| 1                    | <b>⊣</b> 0/1                      | RDFP              | RDBA        | RDFP         | RDBA | 16    | RDFP        | RDFP |   |

| 2                    |                                   | WRFP              | WD          | WRFP         | WD   | 17    | RDBA        | RDBA | - |

| 3                    | <b>→</b> 2/3                      | RDFP              | RDBA        | RDFP         | RDBA | 18    | RDFP        | RDFP |   |

| 4                    |                                   | WRFP              | WD          | WRFP         | WD   | 19    | RDBA        | RDBA |   |

| 15G                  |                                   |                   |             |              |      |       |             |      |   |

|                      | 1.50 GA Read <b>BA</b>            |                   |             |              |      |       |             |      |   |

|                      | 1.50                              | GA Wr             | ite (36     | b) <b>FP</b> |      |       |             |      |   |

|                      | 1.50                              | GA Read <b>FP</b> |             |              |      |       |             |      |   |

| <b>4.50</b> GA Total |                                   |                   |             |              |      |       |             |      |   |

| Native BE Controller (72b WRITES) |                        |            |      |          |                      |             |                  |      |  |

|-----------------------------------|------------------------|------------|------|----------|----------------------|-------------|------------------|------|--|

| Frame                             |                        | Input (RX) |      |          |                      | Frame       | ပို့ Output (TX) |      |  |

| Fra                               | Partition              | CME        | ARX  | CME      | BRX                  | Fra         | QATX             | QATX |  |

| 1                                 | 0/1                    | RDFP       | RDBA | RDFP     | RDBA                 | 16          | RDFP             | RDFP |  |

| 2                                 | 0/1                    | WRFP       | WDL  | WRFP     | WDL                  | 17          | RDBA             | RDBA |  |

| 3                                 | 2/3                    | RDFP       | RDBA | RDFP     | RDBA                 | 18          | RDFP             | RDFP |  |

| 4                                 | 2/3                    | WRFP       | WDL  | WRFP     | WDL                  | 19          | RDBA             | RDBA |  |

| 1                                 | 0/1                    | RDFP       | RDBA | RDFP     | RDBA                 | 16          | RDFP             | RDFP |  |

| 2                                 | 0/1                    | WRFP       | WDU  | WRFP     | WDU                  | 17          | RDBA             | RDBA |  |

| 3                                 | 2/2                    | RDFP       | RDBA | RDFP     | RDBA                 | 18          | RDFP             | RDFP |  |

| 4                                 | 2/3                    | WRFP       | WDU  | WRFP     | WDU                  | 19          | RDBA             | RDBA |  |

| 15G                               |                        |            |      |          |                      |             |                  |      |  |

|                                   | 1.50 GA Read <b>BA</b> |            |      |          |                      |             |                  |      |  |

|                                   | 0.75                   | GA Wri     | 1    | <u>\</u> | WDL = Lower 36b data |             |                  |      |  |

|                                   | 1.50                   | GA Rea     |      |          | WD                   | U = Upper 3 | 6b data          |      |  |

| 3.75 GA Total                     |                        |            |      |          |                      |             |                  |      |  |

| Partition Access Restrictions |           |       |       |  |  |  |  |  |

|-------------------------------|-----------|-------|-------|--|--|--|--|--|

| Frame                         |           | RX    |       |  |  |  |  |  |

| Fra                           | Partition | GCI-A | GCI-B |  |  |  |  |  |

| 1                             | 0/1       | P0    | P1    |  |  |  |  |  |

| 2                             | 0/1       | PU    | P1    |  |  |  |  |  |

| 3                             | 2/2       | P2    | Р3    |  |  |  |  |  |

| 4                             | 2/3       | PZ    | 5     |  |  |  |  |  |

|                               |           |       |       |  |  |  |  |  |

#### MSR 720 : Breaking 4.5GA

Note: Datasheet comparison - 1 access = 72 bits

- FP Access is arbitrated by BCR.

- BA Access is to/from array only. Must be bank aware.

# **Get More Done With The Same Amount of I/O**

#### **Bandwidth Engine 2 Architecture & Family**

- Parallel Array Architecture ... Performance up to:

- 16 outstanding transactions

- 4.5G Accesses per second

- 192 Gbps full duplex throughput

- ~12ns deterministic read latency

- 2.7ns Random cycle time (tRC)

- ❖ GigaChip Interface ... 90% Efficient Transport Protocol

- Up to sixteen low latency SerDes lanes (8G to 15G)

- High Reliability ...70X better SER than 6T-SRAM

- Full ECC support; 72bit array and macro datapath operations

- CRC protected and self recovering GigaChip Interface

- SEU resistant 1T-SRAM Memory core: < 10 FIT/Mb</li>

Daniela della Caratica

Bit Safe<sup>™</sup> Self Test and Self Repair Option

|                              |              | Ba               | andwidth Engine – 2 | <sup>nd</sup> Generation                           |  |

|------------------------------|--------------|------------------|---------------------|----------------------------------------------------|--|

| Applications                 | BE1 - MSR576 | MSR620           | MSR820              | MSR720                                             |  |

| Lookup, LPM, Hash            |              | Highest sin      | le component Acces  | Rate                                               |  |

| Statistics                   | Onboard ALU  |                  | Onboard ALU+        |                                                    |  |

| Buffer – up to 80% efficient |              | Per cycle Burst, | Write Broadcast     |                                                    |  |

| Metering, Dual Ops           |              |                  | Fixed Macro         |                                                    |  |

| Semaphore, Link List         |              |                  | Atomic Ops          |                                                    |  |

| State, Queuing, Link List    |              |                  |                     | Dual Port w/ Data Coherency,<br>36 bit word access |  |

### **Dual Counter: 5 Stage Pipeline**

## Includes Index Compare Logic (not illustrated) for Data Forwarding:

- In case of an index match, data is forwarded in the pipeline

- Prevents stale data in the pipeline

- Similar pipeline for Split Counter

- End-to-End ECC Protection

- 16 ns to completion

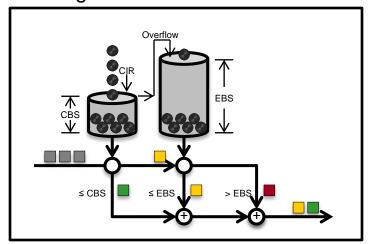

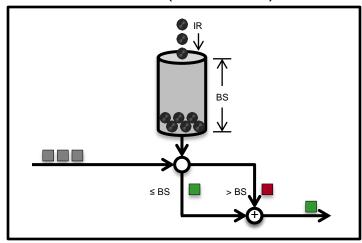

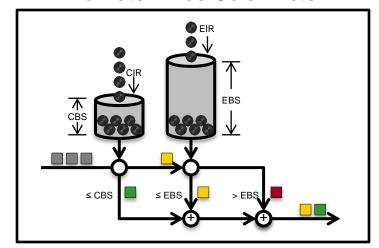

### **MSR820 – Metering Capabilities**

- Individual Flow Programmability

- Meter Type

- Flow Rates

- Thresholds

- 8M Two Color Flows

- 4M Three Color Flows

- Line Rate 4x100G

Single Rate Three Color Meter

Basic Meter (Two Color)

Two Rate Three Color Meter

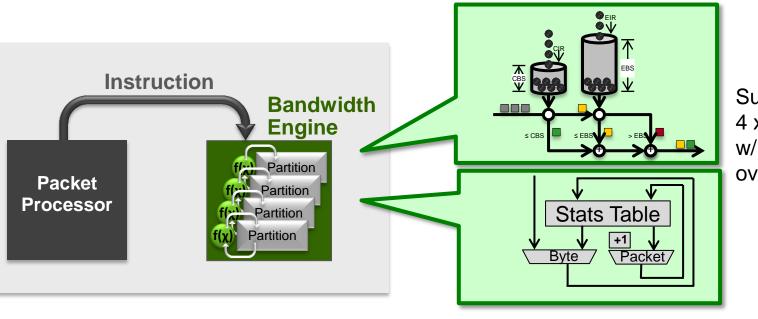

# MSR820 – Bandwidth Engine 2 – Intelligent Memory Macros <u>Leverages I/O</u>

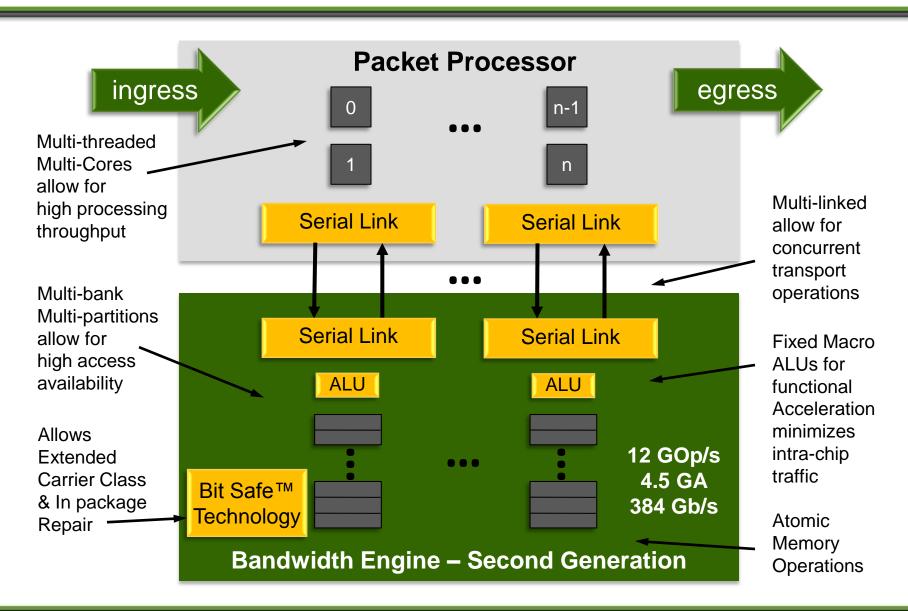

#### Second Generation Bandwidth Engine Architecture

- Up to 4.5 billion external memory accesses per second w/16 SerDes Lanes

- Macros support up to 6 billion internal accesses per second w/8 SerDes Lane

- Macros execute Atomically: Stats, Metering, Read & Set, Test & Set

Supports: 4 x 100GE ports w/ Stats + Metering over 8 lanes

Intelligent Offload, Fire Forward Architecture

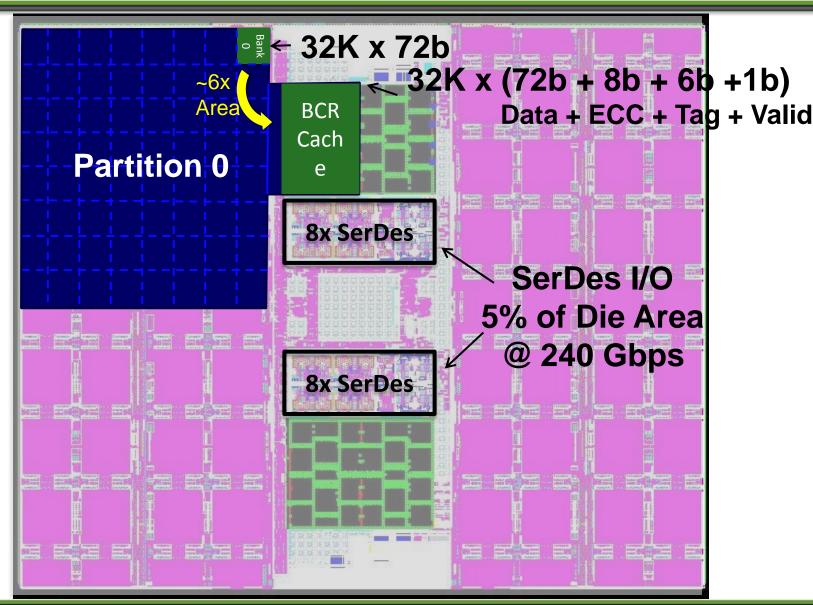

### **Physical Design**

### **Conceptual Timing & Data Access Control**

BE 1: Read Latency of 15.9ns vs. BE2: Read Latency of ~12.5ns

#### **MSR720 Layout**

QDR like

Dual Port

Performance

for 1.10x

vs

3x die area

cost

### Thank you

Michael J. Miller mmiller@mosys.com