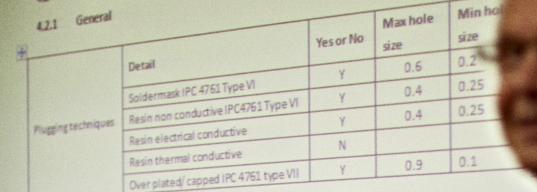

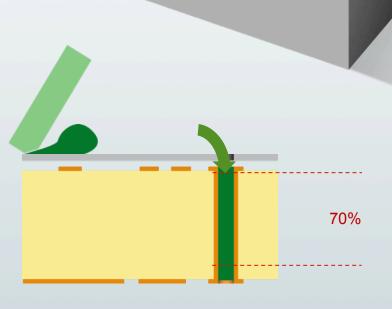

### 4.2.2 Plug depth (solder mask IPC4761 type VI)

| Board Thickness (H) | 0.4mmSH<1.0mm | 1.0mm≤H<1.8mm | 1.8mm≤H<≥ |  |

|---------------------|---------------|---------------|-----------|--|

| 0.2mmsDc0.6mm       | A=100%        | A=100%        | A=70%     |  |

| mm8.0202mm8.0       | A=100%        | A=70%         | A=70%     |  |

English (US)

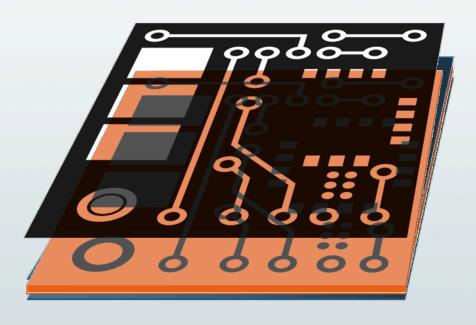

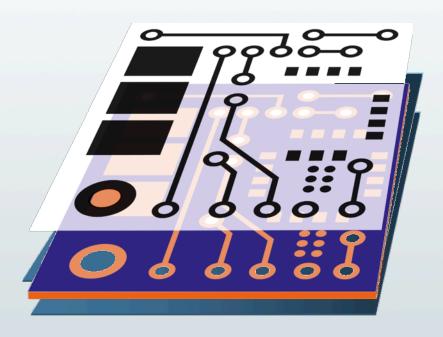

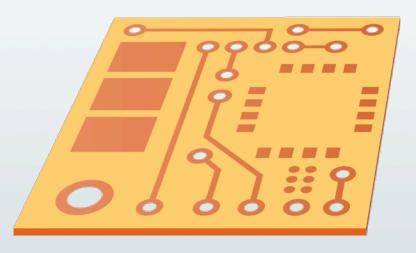

Introduction to Multilayer PCBs

#### Introduction to multilayer PCB's

## What is a multilayer PCB?

- The green thing with holes in it.

- The first item needed when building any electronic product, but often ordered last.

- A platform for components.

- Circuitry with pre-defined electrical function.

- Three or more conductive layers of copper which have been bonded to non-conductive substrates, yet are electrically connected where needed, so that they connect specific components using features (tracks and component pads) that have been imaged and etched to form a bespoke design, in order to fulfill a bespoke function.

#### Introduction to multilayer PCB's

# **History of PCBs**

**1903** First PCB-patent

**1903-1946** Single / double sided boards (NPTH)

1947 Double sided, plated through holes developed

1960 Multilayer process developed.

1993 NCAB was founded

**1995** Micro via production

**2000** Embedded components

### #2 - Material issue

Base material is cut from sheets / larger sizes to working panel sizes.

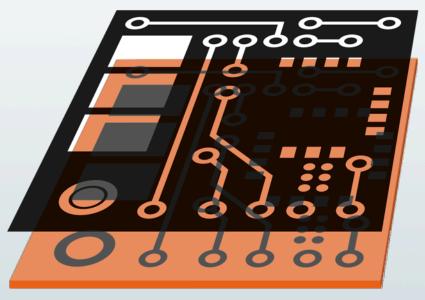

# #3 – Inner layer

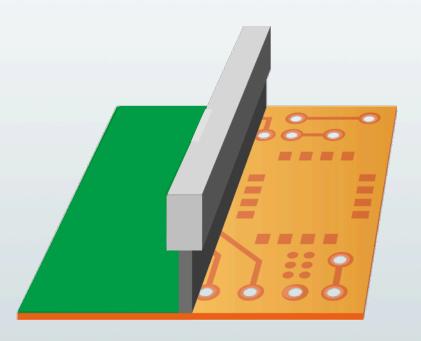

Transfer the image from the artwork to the board surface using photosensitive dry-film and exposure to UV light.

# #4 – Inner layer etch

Removal of the unwanted copper (**not** protected by film) from the panel through etching, to leave copper circuitry that matches the image.

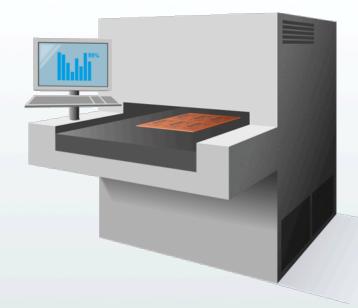

# #5 – Inner layer AOI

Inspection of the circuitry against digital 'images' (based upon data) to verify that it is free from such defects as shorts, opens, etc.

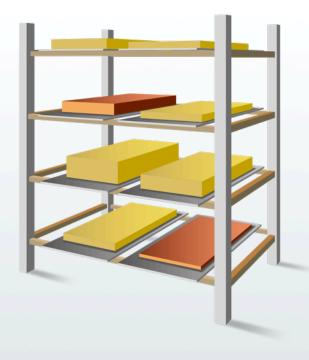

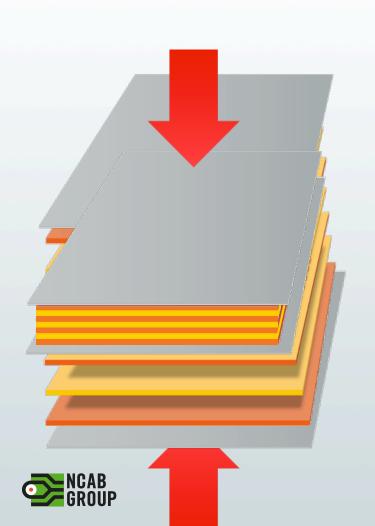

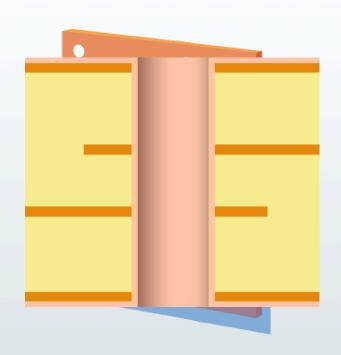

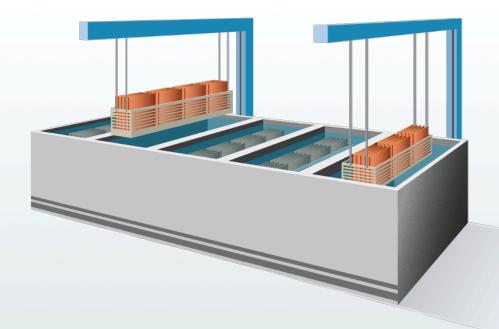

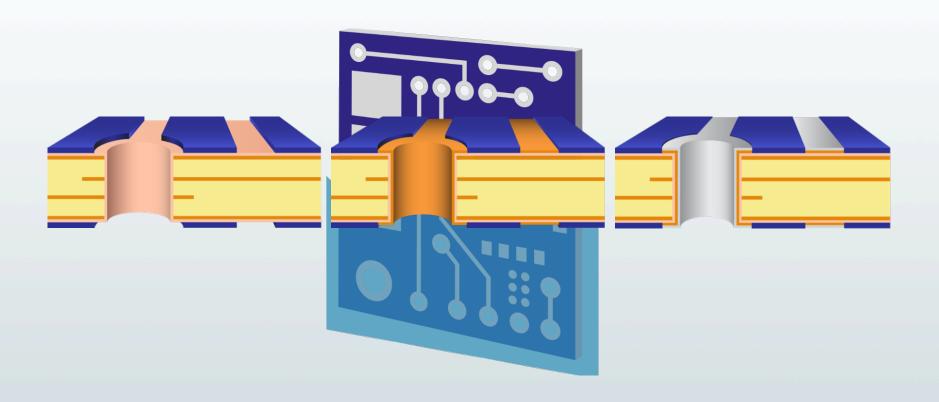

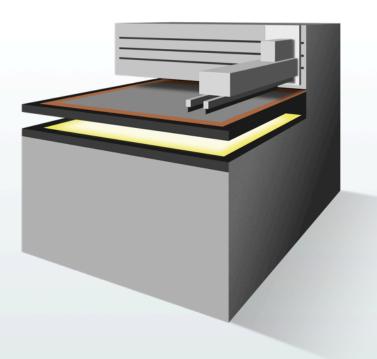

### #6 - Lamination

'Fix' the imaged inner layer cores and pre-preg, through bonding them together at a specific temperature and pressure for a specific time to form a solid, rigid stack up.

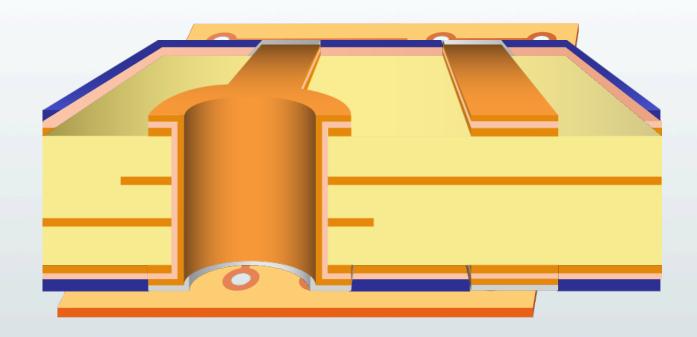

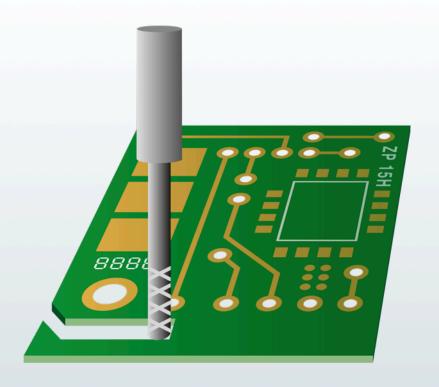

# #7 – Drilling

Mechanical drilling of holes to facilitate the provision of electrical continuity between layers. At this moment, the barrel of the hole has NO metallic deposit.

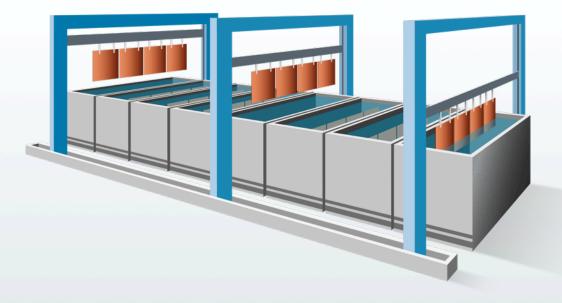

# **Electroless and Panel plating**

Using the two processes the aim is to provide a uniform deposit of copper onto the hole wall through both chemical and electrochemical reactions.

Electroless copper is there only to provide a very thin deposit of ≤ 1um that covers the hole wall and also the complete panel.

A complex chemical process that utilises a log of chemistry and with this being the base deposit, if this is poorly controlled then reliability is compromised.

Panel plating follows on from electroless to provide a thicker deposit of copper on top of the electroless deposit – typically 5 to 8 um.

The combination is used to optimise the amount of copper that is to be plated and etched in order to achieve the track and gap demands.

### #8 - PTH / Electroless

PTH provides a <u>very</u> thin deposit (<1um) over all surface – on the outer surface and within the barrel of the hole. A special process as it supports metallic plating onto non-metallic surfaces (inside the hole)

# #9 – Panel plating

Adds a thicker deposit of copper (5 – 8um) onto the thin amount plated during PTH process. Provides the basis for a more reliable thickness of copper through the hole.

# #10 – Outer layer image

Similar to inner layer, but with one difference - we remove dry film where we want to keep the copper / define circuitry.

# #10 – Outer layer image

Dry film transitions – from application to imaging to developing.

# #11 – Pattern plate

Additional plating deposited in areas exposed by imaging process. Finished plating thickness meets NCAB demands of 20um min, 25um average through the hole.

# #11 – Pattern plate

Basic steps in pattern plate process.

# #12 – Outer layer etch

Removal of the remaining dry film (blue), etching of the unwanted & exposed copper and tin - leaving the copper (under the tin) that defines the circuitry.

# #12 – Outer layer etch

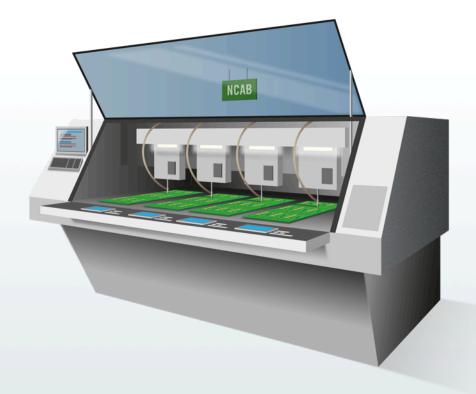

# #13 – Outer layer AOI

Inspection of the circuitry against digital 'images' (based upon data) to verify that it is free from such defects as shorts, opens, etc.

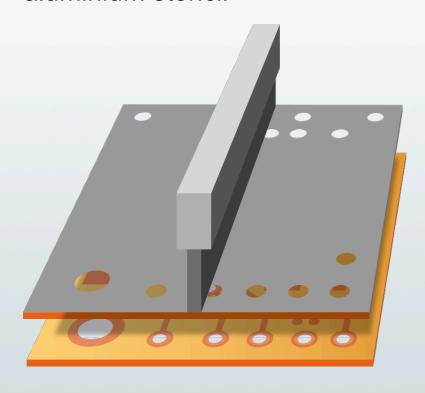

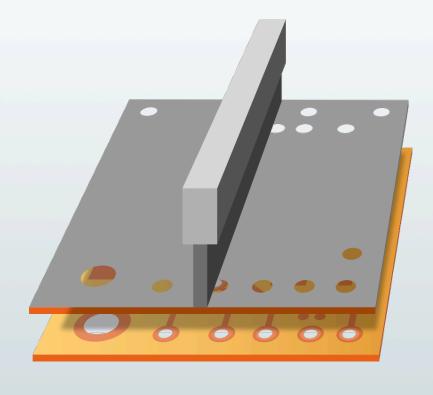

# #14 – Via hole plugging

Screen printing to push soldermask into holes – a separate operation using an aluminium stencil

# #14 – Via hole plugging

Screen printing to push soldermask into holes – a separate operation using an aluminium stencil

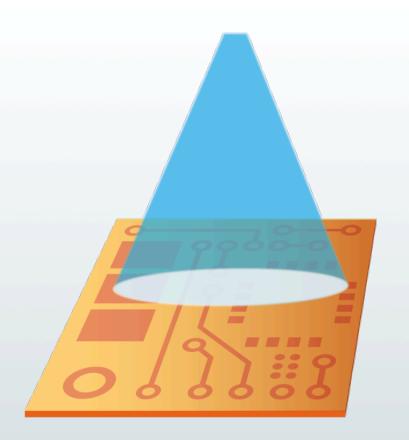

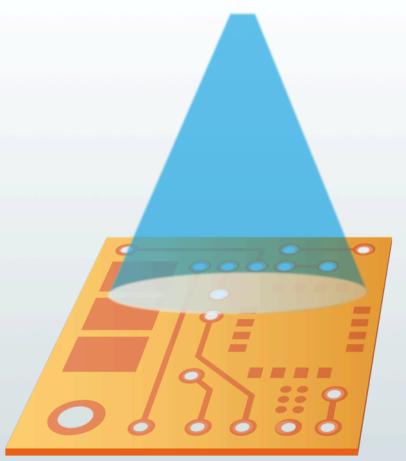

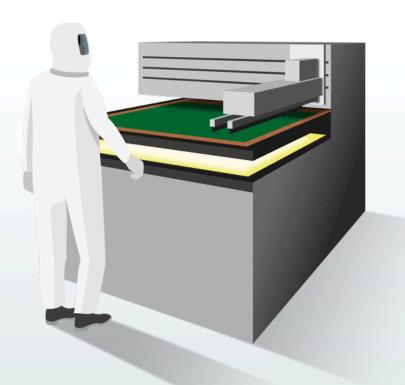

### #15 - Soldermask

Soldermask is applied to the whole board. Exposed to UV (artworks again!) in areas we wish to keep, and then unexposed areas are washed / developed away.

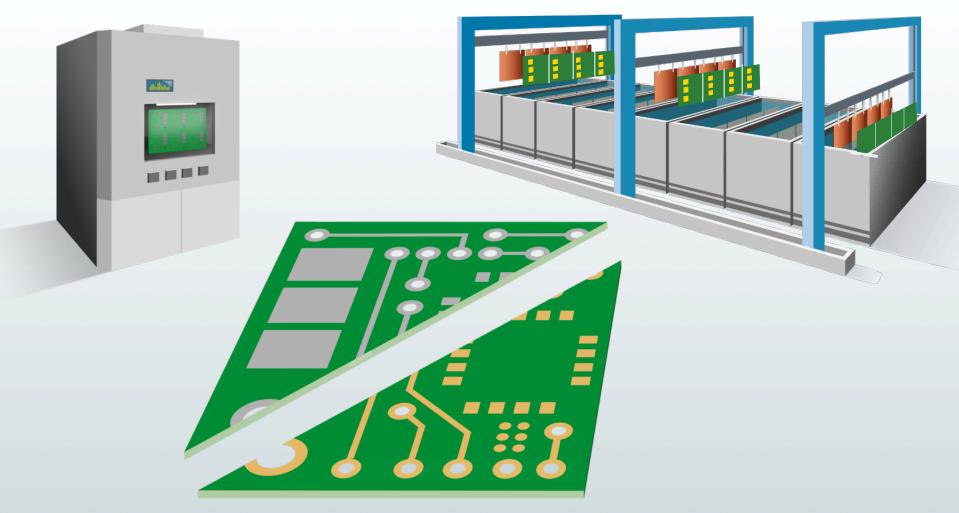

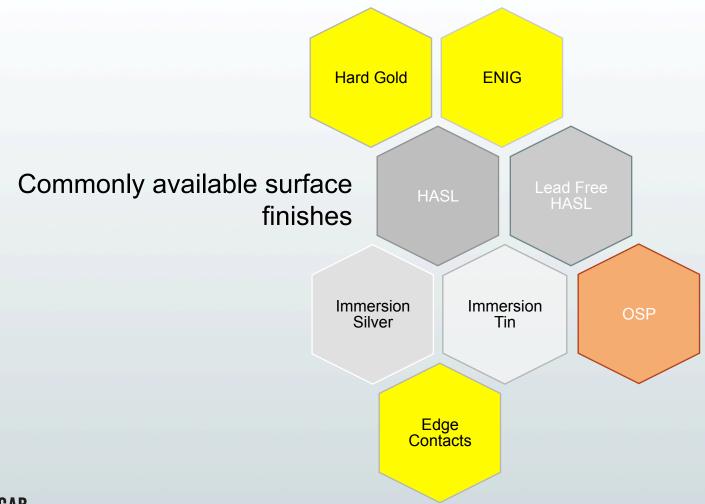

## #16 - Surface finishes

### #16 - Surface finishes

## #17 - Profile

Machining the panels to provide circuits of a specific shape and size.

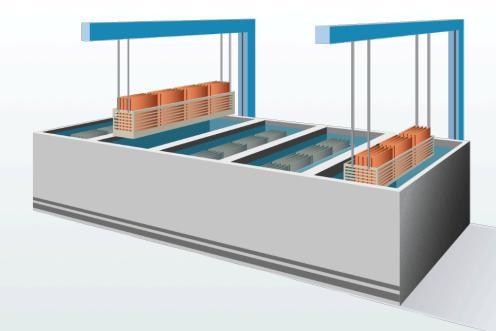

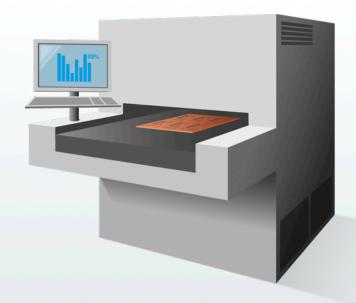

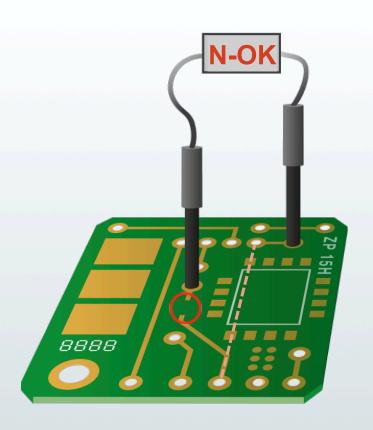

## #18 - Electrical test

Used for checking the integrity of the tracks and the through hole interconnections — ensuring there are no open or short circuits.

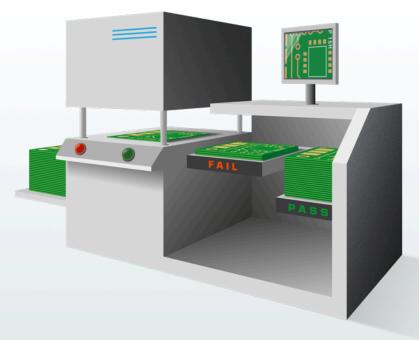

## #19 – Final Inspection

Visual checking of the PCB for cosmetic defects against NCAB demands and customer / IPC demands.

Using manual visual inspection and also AVI – compares digitally to identified anomalies at a speed faster than the human eye.

All orders are also subjected to a full inspection including dimensional, solderability, microsection, etc.