# **USER'S MANUAL**

PROGRAMMABLE SINGLE-CHIP HIGH-SPEED PULSE GENERATORS

# PCL240AS/MS

NIPPON PULSE MOTOR CO., LTD.

# **CONTENTS**

| 1.   | Ger | neral Description                                         | 1  |

|------|-----|-----------------------------------------------------------|----|

| 2.   | Spe | cifications                                               | 2  |

|      |     | Specifications                                            |    |

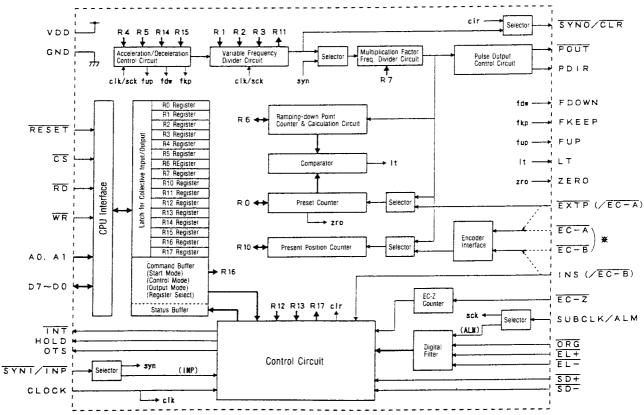

|      | 2.2 | Block Diagram                                             | 3  |

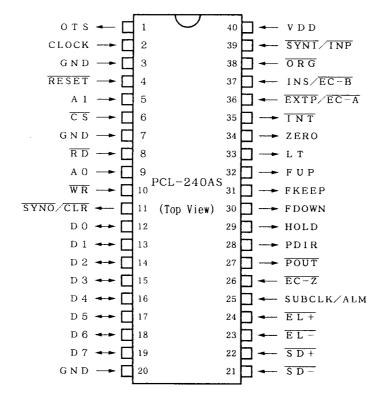

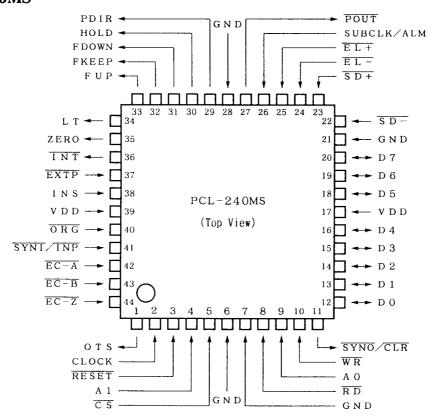

|      | 2.3 | Terminal Pin Layout                                       | 4  |

| 3.   | Out | lline of Functions                                        | 5  |

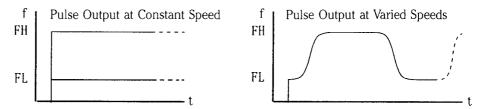

|      | 3.1 | Pulse Output Patterns                                     | 5  |

|      |     | Commands                                                  |    |

|      | 3.3 | Registers                                                 | 7  |

|      | 3.4 | Counters                                                  | 10 |

|      | 3.5 | Operation Modes                                           | 11 |

|      | 3.6 | Control Functions                                         | 11 |

|      | 3.7 | Monitor                                                   | 12 |

|      | 3.8 | Basic Operation                                           | 13 |

| 4.   | Sof | tware                                                     | 14 |

|      | 4.1 | Address Map                                               | 14 |

|      | 4.2 | Writing/Reading Data to/from Registers                    | 14 |

|      | 4.3 | Reading Status                                            | 16 |

|      | 4.4 | Reading Extension Status                                  | 17 |

|      | 4.5 | Default Conditions                                        | 17 |

|      | 4.6 | Precautions in Designing Software                         | 18 |

| 5. ( |     | ration                                                    |    |

|      | 5.1 | Setting Pulse Output Pattern                              | 19 |

|      |     | 5.1.1 Multiplication Parameter [16-bit R7 Register]       | 20 |

|      |     | 5.1.2 FL Pulse Rate [13-bit R1 Register]                  | 20 |

|      |     | 5.1.3 FH1 Pulse Rate [13-bit R2 Register]                 | 21 |

|      |     | 5.1.4 FH2 Pulse Rate [13-bit R3 Register]                 | 21 |

|      |     | 5.1.5 Maximum Acceleration Parameter [16-bit R4 Register] | 21 |

|      |     | 5.1.6 Maximum Deceleration Parameter [16-bit R5 Register] | 21 |

|      |     | 5.1.7 S-curve Acceleration Section [16-bit R14 Register]  | 22 |

|      |     | 5.1.8 S-curve Deceleration Section [12-bit R15 Register]  |    |

|      |     | 5.1.9 Acceleration/Deceleration Time                      |    |

|      |     | 5.1.10 Ramping-down Point [24-bit R6 Register]            | 23 |

|      |     | 5.1.11 Changing Pulse Output Pattern in Motion            |    |

|      | 5.2 | Bits of Command Buffer                                    |    |

|      |     | 5.2.1 Start Mode Command                                  | 27 |

|      |     | 5.2.2 Control Mode Command                                | 30 |

|      |     | 5.2.3 Register Select Command                             | 33 |

|      |     | 5.2.4 Output Mode Command                                 |    |

|      | 5.3 | Operation Modes                                           |    |

|      |     | 5.3.1 Continuous Mode                                     |    |

|      |     | 5.3.2 Preset Mode                                         |    |

|      |     | 5.3.3 Origin Return Mode                                  |    |

|      |     | 5.3.4 Timer Mode                                          |    |

|    | 5.4 | Control Functions                                                | 43 |

|----|-----|------------------------------------------------------------------|----|

|    |     | 5.4.1 Servomotor Interface                                       | 43 |

|    |     | 5.4.2 Pulse Output Mode                                          | 46 |

|    |     | 5.4.3 Present Position Counter (R10 Register)                    | 47 |

|    |     | 5.4.4 External Mechanical Signals                                | 48 |

|    |     | 5.4.5 General-purpose Input/Output Pins                          | 51 |

|    |     | 5.4.6 Interrupt Signal Output                                    | 51 |

|    | 5.5 | Registers                                                        | 53 |

|    |     | 5.5.1 R0—Preset Counter Setting Register, 24-bit                 | 53 |

|    |     | 5.5.2 R1—FL Pulse Rate Setting Register, 13-bit                  | 54 |

|    |     | 5.5.3 R2—FH1 Pulse Rate Setting Register, 13-bit                 | 55 |

|    |     | 5.5.4 R3—FH2 Pulse Rate Setting Register, 13-bit                 | 55 |

|    |     | 5.5.5 R4—Acceleration Rate Setting Register, 16-bit              | 55 |

|    |     | 5.5.6 R5—Deceleration Rate Setting Register, 16-bit              | 55 |

|    |     | 5.5.7 R6—Ramping-down Point Setting Register, 24-bit             | 55 |

|    |     | 5.5.8 R7—Multiplication Factor Setting Register, 16-bit          | 56 |

|    |     | 5.5.9 R10—Present Position Counter, 24-bit                       | 56 |

|    |     | 5.5.10 R11—Present Pulse Rate Monitor, 13-bit                    | 56 |

|    |     | 5.5.11 R12—Extension Mode Register 1, 24-bit                     | 56 |

|    |     | 5.5.12 R13—Extension Mode Register 2, 24-bit                     | 59 |

|    |     | 5.5.13 R14—S-curve Acceleration Section Setting Register, 16-bit | 61 |

|    |     | 5.5.14 R15—S-curve Deceleration Section Setting Register, 12-bit | 62 |

|    |     | 5.5.15 R16—Command Buffer Monitor, 24-bit                        | 62 |

|    |     | 5.5.16 R17—Extension Status Monitor, 21-bit                      |    |

|    | 5.6 | Monitor                                                          | 65 |

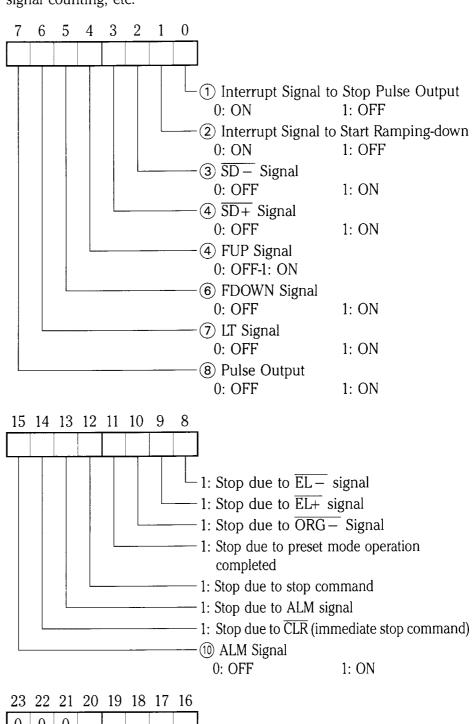

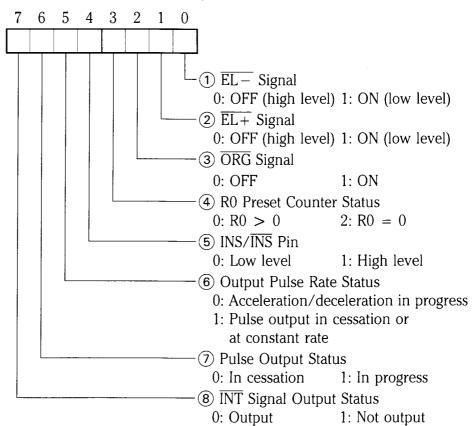

|    |     | 5.6.1 Status Buffer                                              | 65 |

| 6. | Har | rdware                                                           | 67 |

|    | 6.1 | Terminal Pin Assignment                                          | 67 |

|    | 6.2 | Terminal Pin Functions                                           | 69 |

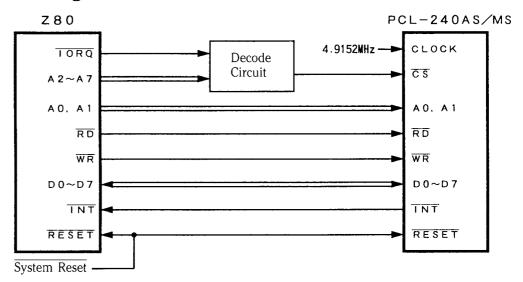

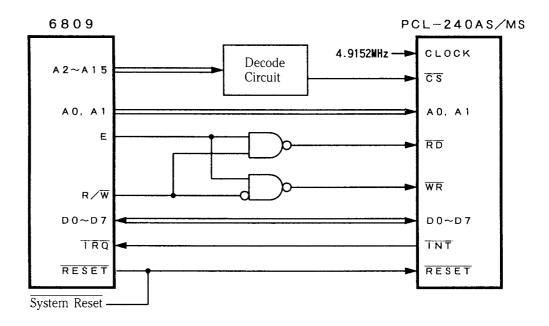

|    | 6.3 | Block Diagrams of CPU Interface Circuit                          | 74 |

|    | 6.4 | Precautions in Designing Hardware                                | 74 |

| 7. | Cha | aracteristics                                                    | 75 |

|    | 7.1 | Absolute Maximum Ratings                                         | 75 |

|    | 7.2 | Recommended Operating Conditions                                 | 75 |

|    | 7.3 | DC Characteristics                                               | 75 |

|    | 7.4 | AC Characteristics                                               | 76 |

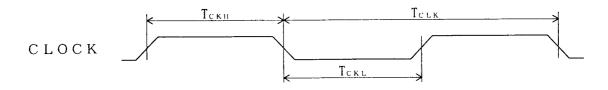

|    |     | 7.4.1 Reference Clock                                            | 76 |

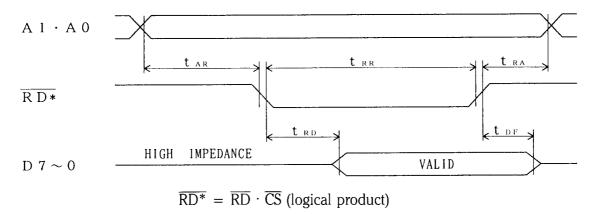

|    |     | 7.4.2 Read Cycle                                                 | 76 |

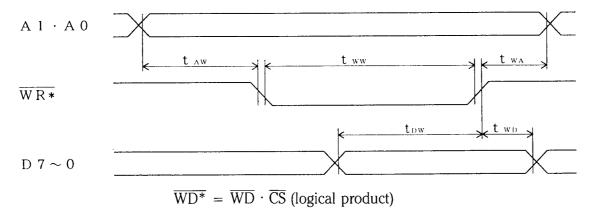

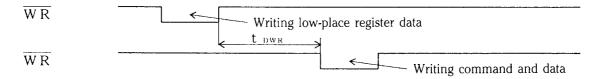

|    |     | 7.4.3 Write Cycle                                                |    |

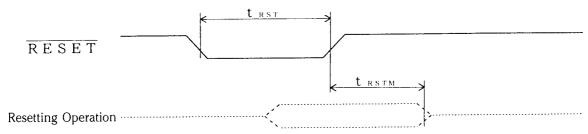

|    |     | 7.4.4 Reset Cycle                                                | 76 |

|    |     | 7.4.5 Operation Timing                                           | 77 |

|    | 7.5 | Timing Charts                                                    |    |

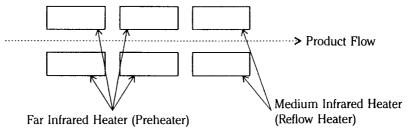

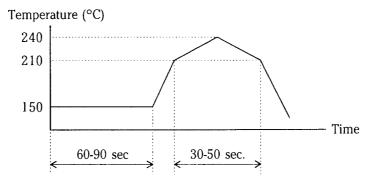

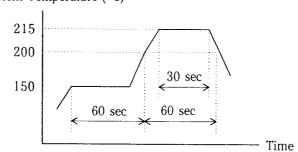

| 8. Handling Precautions                    | 83 |

|--------------------------------------------|----|

| 8.1 Designing Precautions                  | 83 |

| 8.2 Transportation and Storage Precautions |    |

| 8.3 Assembling Precautions                 | 85 |

| 8.4 Other Precautions                      | 85 |

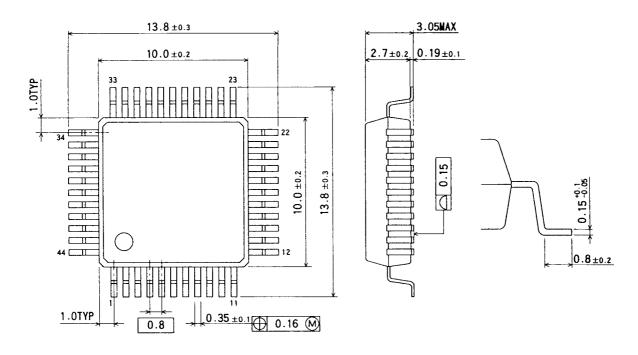

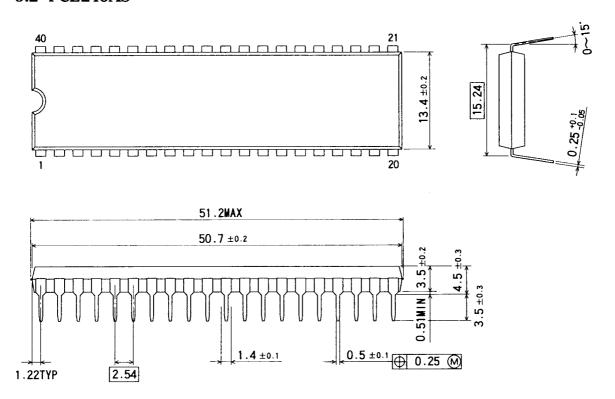

| 9.External Dimensions                      | 86 |

# Considerations in Reading this User's Manual

- (1) Varied-speed operation means pulse output with S-curve acceleration/deceleration at the start/stop.

- (2) Constant-speed operation means pulse output at a constant rate with no acceleration/deceleration.

- (3) The input/output logic of each pin indicates the logic under the reset condition.

# 1. General Description

The PCL240AS and PCL240MS are CMOS LSIs. Each LSI oscillates high-frequency pulses to drive the stepping motor and pulse train input servo-motor according to the command written through the CPU bus interface. Thus, using the CMOS LSI, you can perform S-curve acceleration/deceleration, continuous constant-speed control, preset positioning, and origin return.

If you use the PCL-80K, 240K or 240AK, you can replace it with the PCL240AS to enjoy the S-curve acceleration/deceleration function. The PCL240MS can replace the PCL-240MK for the same purpose.

#### **Features**

- Motion control made available through S-curve acceleration/deceleration (acceleration and deceleration rates can be independently set)

- Automatic adjustment of maximum speed

- Maximum output frequency of up to 2.4 Mpps

- S-curve acceleration/deceleration made available with the same hardware and software as used for PCL-240AK/240MK

- Interface for servomotor control

- Motion control available with mechanical limit signal input

- Present position counter

# 2. Specifications

# 2.1 Specifications

Power Requirement:  $+5V \pm 5\%$

Reference Clock: 4.9152MHz standard (10MHz maximum)

Positioning Pulse Setting Range: 0 to 16,777,215 pulses

Pulse Rate Setting Steps: 1 to 8,191

Pulse Rate Multiplication Setting Range: 0.01 to 300 times (with a reference clock of

4.9152MHz)

0.01 to 81.91 pps with 0.01x 1 to 8,191 pps with 1x

300 to 2,457,300 pps with 300x

Pulse Rate Setting Registers: Three types of FL, FH1 and FH2

Ramping-down Point Setting Range: 0 to 16,777,215

Acceleration/Deceleration Rate Setting Range: 1 to 65,535 (can be independently set)

Up/Down Counter Counting Range: 0 to 16,777,215

Major Operations Available: • Constant-speed or varied-speed operation in

continuous mode or preset mode

• Constant-speed or varied-speed origin return

• Speed change on the way of operation

• Immediate stop/deceleration-stop

• Timer mode operation

Operating Temperature Range: 0 to +70°C

Storage Temperature Range: -40 to +125°C

Package: PCL240AS: 40-pin DIP

PCL240MS: 44-pin QFP

# 2.2 Block Diagram

Note: EC-A and EC-B pins are provided for PCL240MS only. With the PCL240AS, EXTP and INS pins are used in common with EC-A and EC-B pins.

# 2.3 Terminal Pin Layout

#### PCL240AS

#### PCL240MS

# 3. Outline of Functions

The LSI generates pulses to control the stepping motor or servomotor according to commands sent from the CPU. You can let the LSI control the motor in a desired mode by setting a variety of parameters.

This chapter roughly describes the functions provided by the LSI. For details, refer to the Chapter 5 "Operation."

# 3.1 Pulse Output Patterns

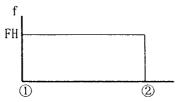

The LSI allows you to select a pulse output pattern of either constant speed or varied speeds.

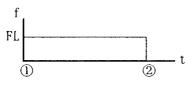

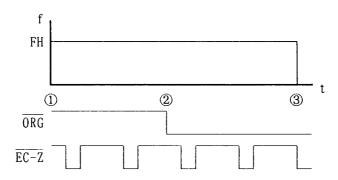

# 3.1.1 Pulse Output at Constant Speed

The LSI generates pulses at a fixed rate to run the motor at a constant speed from the start to end. You can select the pulse rate from those entered in FL (low speed), FH1 (high speed 1) and FH2 (high speed 2) registers.

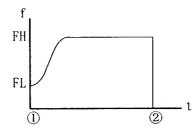

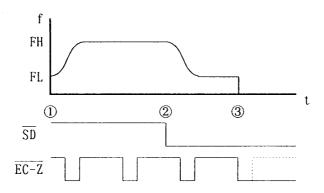

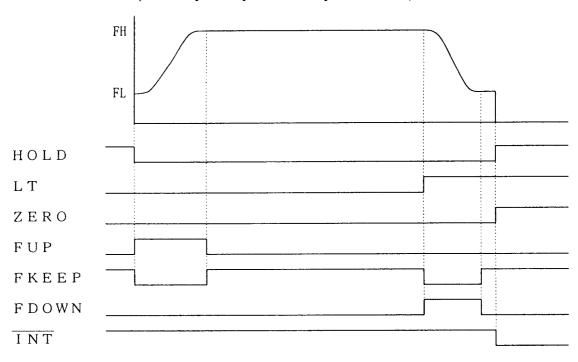

# 3.1.2 Pulse Output at Varied Speeds

The LSI start generating pulses at the FL rate and then accelerates the pulse output to the FH rate. It decelerates the pulse output to the FL rate before stop. Acceleration or deceleration is made in S-curve profile where pulses are output at a gentle rate at the start and end of acceleration and deceleration.

#### 3.2 Commands

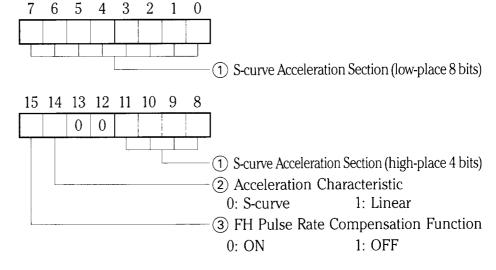

You can operate the LSI by writing commands from the CPU to the designated addresses (command buffer). There are four basic types of commands and each type is selected with high-place two bits.

#### 3.2.1 Start Mode Command

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | n | n | n | n | n | n |

The start mode command is to start or to stop the motion of the LSI. The command also allows you to select a pulse rate (FL, FH1 or FH2), an output pattern (constant-speed or varied-speed) and whether or not to output the  $\overline{\text{INT}}$  (interrupt) signal.

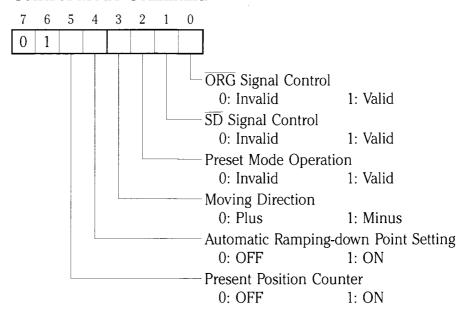

#### 3.2.2 Control Mode Command

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 1 | n | n | n | n | n | n |

The control mode command allows you to select:

- (1) Whether or not to let the ORG signal stop the motion of the LSI

- (2) Whether or not to use the  $\overline{SD}$  signal

- (3) Whether or not to place the LSI in the preset (positioning) mode

- (4) Moving direction, plus or minus

- (5) Whether or not to use the automatic ramping-down point setting function. If the function is made valid, the LSI will automatically decelerate pulse output at the ramping-down point in positioning operation.

- (6) Whether or not to use the present position counter.

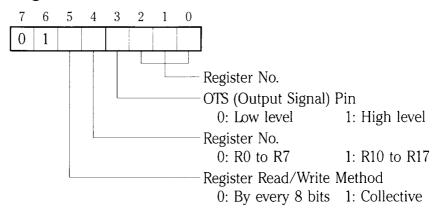

# 3.2.3 Register Select Command

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | n | n | n | n | n | n |

The register select command allows you to select a register for writing data to or reading data from the register. The register is kept as selected until the next register select command is written. With this command, you can select:

- (1) A desired register

- (2) Whether the data are read or written from/to the register by every 8 bits or in a lump (by 24 bits)

- (3) Whether or not to use the general-purpose output signal (OTS) pin

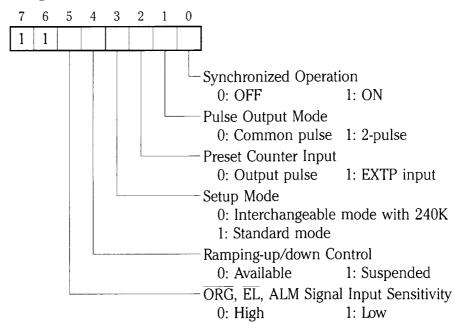

#### 3.2.4 Output Mode Command

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | n | n | n | n | n | n |

The output mode command allows you to set and select the following:

- (1) Input sensitivity of  $\overline{ORG}$  and  $\overline{EL}$  signals

- (2) Suspension of acceleration/deceleration on the way

- (3) Interchangeable mode with the PCL-240K or standard mode\*

- (4) Input signal to the preset counter (internal or external pulses)

- (5) Pulse output mode (common pulse or 2-pulse mode)

- (6) Synchronized operation

\*The PCL240AS and PCL240MS are function-enhanced renewal versions of old model PCL-240K. To make the PCL240AS and PCL240MS compatible with the system built for PCL-240K, they provide the interchangeable mode. Note, however, that if you select the interchangeable mode, enhanced functions such as present position counter, servo control signals (INP, CLR, ALM), origin return with Z-phase signal, S-curve acceleration/deceleration,

monitoring of command, extension status and registers and collective processing of register data are not available.

# 3.3 Registers

Registers store numerical parameters (pulse rates, number of output pulses, etc.) and data for extended functions. To read/write data from/to a register, you need to select the register in advance with the register select command. If the interchangeable mode with 240K is selected, you cannot read data from any of registers R1 to R17 and cannot write data in the register in a lump (by 24 bits).

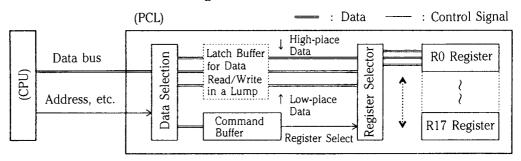

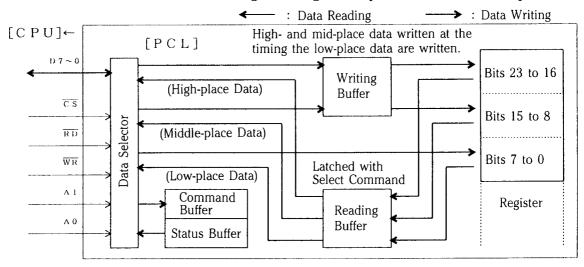

#### Data Flow from/to Registers

# 3.3.1 R0 Register, Preset Number of Output Pulses

Enter the total number of output positioning pulses in the R0 register.

# 3.3.2 R1 Register, FL Pulse Rate

Enter the FL pulse rate in the R1 register. In varied-speed operation, the rate will be used at the start of acceleration and as the target rate for deceleration. Note, however, that the rate is multiplied by the value set in R7 register.

# 3.3.3 R2 Register, FH1 Pulse Rate

Enter the FH1 pulse rate in the R2 register. In varied-speed operation, the rate will be a target rate for acceleration and be used constantly thereafter until the start of deceleration. Note, however, that the rate is multiplied by the value set in R7 register.

# 3.3.4 R3 Register, FH2 Pulse Rate

Enter the FH2 pulse rate in the R3 register. The function is the same as the R2 register. Use the start mode command to select either FH1 or FH2 pulse rate.

# 3.3.5 R4 Register, Acceleration Rate

Enter the acceleration rate in the R4 register. The rate will be used for acceleration in varied-speed operation.

# 3.3.6 R5 Register, Deceleration Rate

Enter the deceleration rate in the R5 register. The rate will be used for deceleration in varied-speed operation. Note, however, that if the automatic ramping-down point setting function is made valid, deceleration will be made at the rate entered in the R4 register.

# 3.3.7 R6 Register, Ramping-down Point

Enter the starting point of deceleration in varied-speed or positioning operation in the R6 register. If the automatic ramping-down point setting function is made invalid, enter the number of pulses required for deceleration. If the automatic ramping-down point setting function is made valid, enter 0 or an offset value.

# 3.3.8 R7 Register, Multiplifcation Factor

Enter in the R7 register the factor to multiply the pulse rates entered in R1, R2 and R3 registers.

The following registers R10 to R17 are effective only with the LSI placed in the standard mode.

# 3.3.9 R10 Register, Present Position Counter

The LSI has a present position counter (up/down counter for position control). The R10 register allows you to read/write data from/to the counter.

# 3.3.10 R11 Register, Present Pulse Rate Monitor

This read-only register allows you to monitor the pulse rate at which the LSI is outputting pulses. Note, however, that the rate monitored is the parameter entered in the R1, R2 or R3 register and is not multiplied by the parameter entered in the R7 register.

# 3.3.11 R12 Register, Extension Mode 1

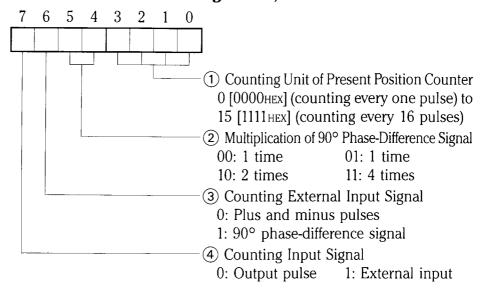

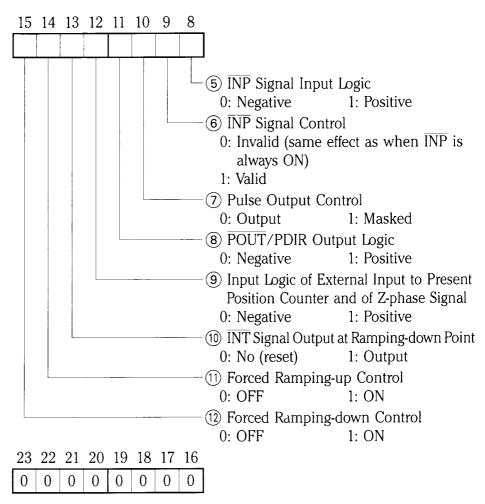

The R12 register allows you to set details with regard to the present position counter,  $\overline{\text{INP}}$  signal, pulse output,  $\overline{\text{INT}}$  signal at the ramping-down point, etc.

# 3.3.12 R13 Register, Extension Mode 2

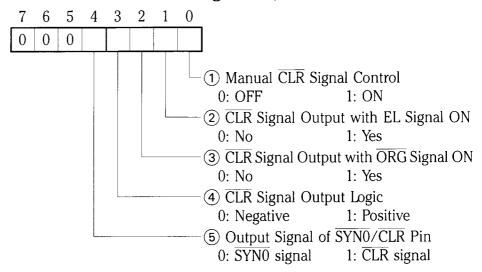

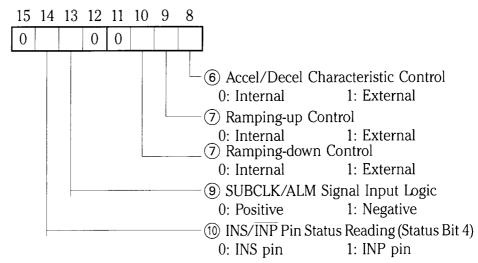

The R13 register allows you to set details with regard to  $\overline{\text{CLR}}$  signal output, ALM signal input, INP signal monitor, origin return with Z-phase signal,  $\overline{\text{ORG}}$  signal input, etc.

# 3.3.13 R14 Register, S-curve Acceleration Section

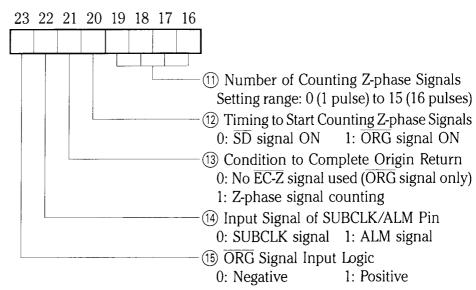

The R14 register allows you to set the S-curve section at the start and the end of linear acceleration.

# 3.3.14 R15 Register, S-curve Deceleration Section

The R15 register allows you to set the S-curve section at the start and the end of linear deceleration.

# 3.3.15 R16 Register, Command Buffer Monitor

The read-only register allows you to monitor the contents written in the command buffer.

# 3.3.16 R17 Register, Extension Status

This read-only register allows you to monitor the signals, the factor which stopped the LSI from generating pulses and the Z-phase counting.

#### Register Data Applied Points on Pulse Output Pattern

#### 3.4 Counters

The LSI is equipped with 1) Preset counter for positioning operation, 2) Present position counter which counts output pulses or external pulses, and 3) Ramping-down point counter for automatic deceleration in varied-speed operation.

#### 3.4.1 Preset Counter

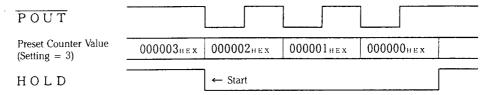

Each pulse output lets the preset counter count down the number of pulses entered in the R0 register. In the positioning operation, the LSI stops generating pulses when the preset counter counts down to 0. If you use the same number of pulses, you need to enter the value in the R0 register anew. The present counter counts down even in other than positioning operation. You can check the counter value by reading the R0 register.

#### 3.4.2 Present Position Counter

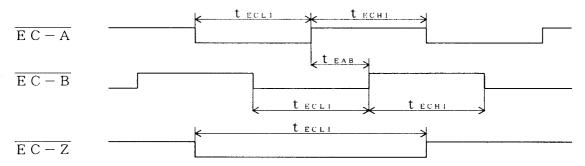

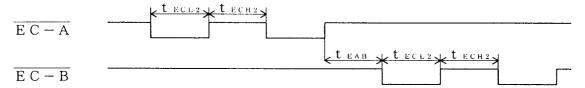

The present position counter counts output pulses or external signals input through  $\overline{EC-A}$  and  $\overline{EC-B}$  pins.\*

If you let it count signals through  $\overline{\text{EC-A}}$  and  $\overline{\text{EC-B}}$  pins, you can select either 2-pulse signals (plus and minus pulses) or 90° phase-difference signals. In the case of 90° phase-difference signal, you can let it count multiplied signals. You can also select a counting unit in a range of 1/1 to 1/16.

You can check the counter value by reading the R10 register.

\*In the case of the PCL240AS which is not equipped with EC-A and EC-B pins, EXTP and INS pins serve in place of them.

#### 3.4.3 Ramping-down Point Counter

Use the ramping-down point counter for automatic deceleration in varied-speed positioning operation. Set the control mode command for use of the automatic ramping-down point setting function, the number of pulses required for deceleration will be calculated and entered in this register during acceleration. The LSI will compare the value with the number of pulses entered in the R0 register. When the preset counter value becomes equal to the value of ramping-down point counter, deceleration will start and the ramping-down point counter will count down. If desired, you can shift the ramping-down point by setting the R6 register.

If the automatic ramping-down point setting function is made invalid, the ramping-down point entered in the R6 register is used for deceleration. You can check the counter value by reading the R6 register.

# 3.5 Operation Modes

In combination with the control mode commands, you can operate the LSI in various ways such as positioning and origin return.

#### 3.5.1 Continuous Mode

In the continuous mode, the LSI starts generating pulses upon receiving the start command and continues generating pulses until receiving the stop command.

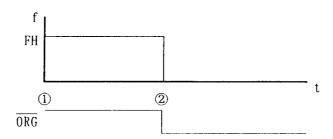

# 3.5.2 Origin Return Mode

In the origin return mode, the LSI stops generating pulses upon receiving the  $\overline{ORG}$  signal. Origin return is also available in combination with the Z-phase signal ( $\overline{EC-Z}$ ).

#### 3.5.3 Preset Mode

In the preset mode, the LSI stops generating pulses upon outputting the total number of pulses entered in the R0 register.

#### 3.5.4 Timer Mode

This mode allows you to use the LSI as a timer. The internal operation is the same as the abovementioned preset mode except for no pulse output in the timer mode.

#### 3.6 Control Functions

The LSI provides sophisticated functions to control the motor in various ways.

#### 3.6.1 Input of External Mechanical Signals

The LSI can input the following signals as position signals from the mechanical system:

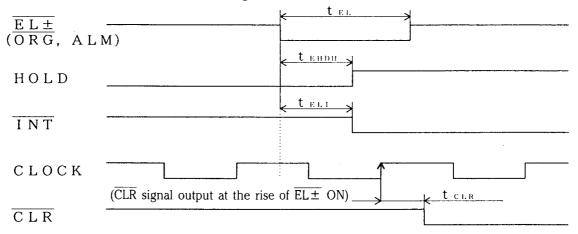

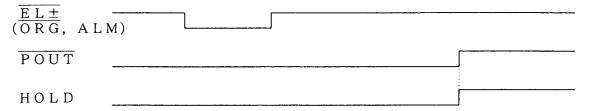

- (1) Mechanical Limit Signals,  $\overline{EL+}$  and  $\overline{EL-}$  The limit signal in the moving direction immediately stops the LSI from generating pulses. If the limit signal is turned off, the LSI keeps stopping pulse output.

- (2) Ramping-down Signals,  $\overline{SD+}$  and  $\overline{SD-}$  In varied-speed operation, the ramping-down signal in the moving direction lets the LSI decelerate the pulse output to the FL pulse rate. When the ramping-down signal is turned off, the pulse output is accelerated to the FH rate.

- (3) Origin Signal, ORG

In the origin return mode, the origin signal immediately stops the LSI from generating pulses.

#### 3.6.2 Pulse Output Modes

The LSI provides two pulse output modes. In the common pulse mode, it outputs control pulses and direction signals. In the 2-pulse mode, it outputs plus direction pulses and minus direction pulses. You can change the output logic.

#### 3.6.3 Dummy Operation

You can let the LSI perform all activities except for pulse output to check the operation without running the motor.

#### 3.6.4 Servomotor Interface

The LSI provides the following servomotor control signals:

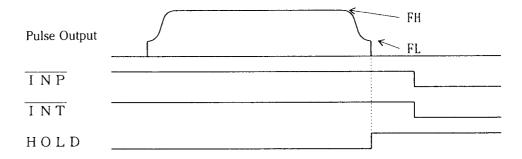

- (1) In-position Signal, INP

- The LSI can input the in-position signal from the servomotor driver. Interrupt signal output is delayed to the input of this signal.

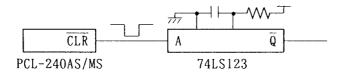

- (2) Deviation Counter Clear Signal,  $\overline{\text{CLR}}$  The LSI can output this one-shot signal to clear the deviation counter of servomotor driver.

- (3) Alarm Signal, ALM

The alarm signal from the servomotor driver stops the LSI from generating pulses.

# 3.6.5 General-purpose Output Pin

The OTS pin is available to output general-purpose signals.

#### 3.6.6 General-purpose Input Pin

The INS pin is available to input general-purpose signals. In the case of PCL240AS, the INS pin is common to the external input pin,  $\overline{\text{EC-B}}$ , for the present position counter.

# 3.6.7 Interrupt Signal Output

Based on two factors, cessation of pulse output and ramping-down point, the LSI can output the  $\overline{\text{INT}}$  signal to the CPU.

#### 3.7 Monitor

Through designated addresses, you can monitor the operation status and setting conditions.

#### 3.7.1 Operation Status

You can monitor the following:

- (1) Operation status such as cessation of pulse output and deceleration in progress

- (2) Input/output signal status

- (3) Interrupt factor, cessation factor, etc.

#### 3.7.2 Register Parameters

You can check parameters entered in the registers and values of the counters.

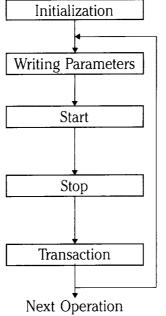

# 3.8 Basic Operation

The basic operation procedure is as follows:

#### 3.8.1 Writing Commands

Write commands from the CPU to command buffer addresses.

# 3.8.2 Reading Status

The CPU reads status data from the status addresses (command buffer).

# 3.8.3 Writing Data to Registers

- (1) Using the register select command, select the register to which you want to write data.

- (2) Write register data to the addresses for high-place, middle-place and low-place data.

# 3.8.4 Reading Data from Registers

- (1) Using the register select command, select the register from which you want to read data.

- (2) The CPU will read register data from the addresses for high-place, middle-place and low-place data.

# 3.8.5 Typical Operation Flow

Set the pulse output mode, external input signal logic, etc.

Set the number of output pulses, pulse rates, control mode, etc. and write the clear command.

Write the start mode command.

(Read data of position, pulse rate, etc.)

The LSI stops generating pulses with the stop command, upon completion of preset mode operation or with an external signal.

Take appropriate transactions such as reading interrupt factors.

# 4. Software

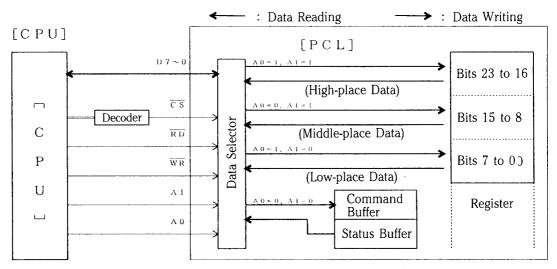

# 4.1 Address Map

Relations of addresses A1, A0, RD, WR and CS with data bus are as follows:

| CS | RD | WR | A1 | A0 | Description                                      |       |

|----|----|----|----|----|--------------------------------------------------|-------|

| L  | Н  | L  | L  | L  | Data bus ⇒ Command buffer                        |       |

| L  | Н  | L  | L  | Н  | Data bus ⇒ Low-place register data (bits 7-0)    | White |

| L  | Н  | L  | Н  | L  | Data bus ⇒ Mid-place register data (bits 15-8)   | Write |

| L  | Н  | L  | Н  | Н  | Data bus ⇒ High-place register data(bits 23-16)  |       |

| L  | L  | Н  | L  | L  | Data bus ← Status                                |       |

| L  | L  | Н  | L  | Н  | Data bus <- Low-place register data (bits 7-0)   | Dead  |

| L  | L  | Н  | Н  | L  | Data bus <- Mid-place register data (bits 15-8)  | Read  |

| L  | L  | Н  | Н  | Н  | Data bus ← High-place register data (bits 23-16) |       |

| L  | L  | L  |    | _  | Prohibited                                       |       |

| Н  | _  |    |    | _  | Data bus = High impedance                        |       |

As shown on the table above, A1 and A0 addresses are used as follows:

A1=L and A0=L to write command/to read status

A1=L and A0=H to write/read low-lace register data

A1=H and A0=L to write/read mid-place register data

Al=H and A0=H to write/read high-place register data

# 4.2 Writing/Reading Data to/from Registers

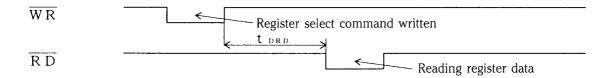

You need to select the register with the register select command before writing or reading data to/from a register.

# 4.2.1 Collective Data Writing and Reading

You can write/read data to/from a register by every 8 bits or by all 24 bits in a lump. You can select either with the register select command. While the LSI is in motion, it is recommended to select the 24-bit collective writing/reading method. Also, note that if the LSI is placed in the interchangeable mode with the 240K, writing or reading data to/from a register is available only by every 8 bits.

#### Writing/Reading by Every 8 Bits

Data will be written or read from the data bus by every 8 bits to the highplace bits, the middle-place bits and the lower-place bits. Since the write or read timing shifts, if used during pulse output in progress, this method may cause an erroneous writing or reading at the time the counter takes a figure up or down.

#### Data Flow in Writing/Reading Data by Every 8 Bits

#### Writing/Reading Data by all 24 Bits in a Lump

When writing, the high- and middle-place register data are once latched in the writing buffer and then are written collectively in the register at the time the low-place register data are written. Be sure to write data in the order of high-place to low-place bits..

When reading, the register data are once copied in the reading buffer at the time the register select command is written and then transferred from the buffer to the CPU.

If the data are collectively written or read during pulse output in progress, counters operate correctly even at the time of taking a figure up or down.

#### Data Flow in Writing/Reading Data by All 24 Bits in a Lump

# 4.2.2 Writing Procedure

#### By Every 8 Bits

- (1) Write the register select command (80-95HEX) to the command buffer.

- (2) Write data to the high-place address, the middle-place address and the low-place address, individually in a desired order.

#### By All 24 Bits in a Lump

- (1) Write the register select command (A0-B5HEX), which designates the collective write/read method, to the command buffer.

- (2) Write all 24-bit data to the high, middle- and low-place register addresses in that order.

- (3) Allow a time length of two cycles of the reference clock (approximately  $0.4\mu s$  with a reference clock of 4.9152 MHz) for internal processing. Do not write any register select command or data during the time.

# 4.2.3 Reading Procedure

#### By Every 8 Bits

- (1) Write the register select command (80-98HEX) to the command buffer.

- (2) Read data from the high, middle- and low-place addresses, individually in a desired order.

#### By All 24 Bits in a Lump

- (1) Write the register select command (A0-B7HEX), which designates the collective write/read method, to the command buffer.

- (2) Allow a time length of two cycles of the reference clock (approximately  $0.4\mu s$  with a reference clock of 4.9152 MHz) for internal processing. Do not read data during the time.

- (Data are copied from the register to the reading buffer.)

- (3) Read high, middle- and low-place data in a desired order.

# 4.3 Reading Status

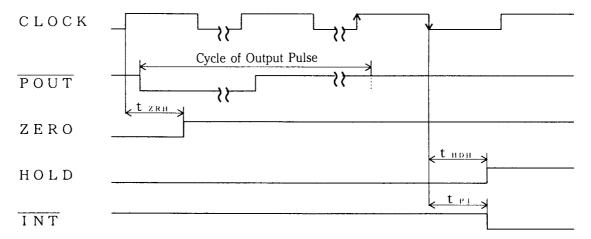

You can monitor the present operation status as well as ON/OFF status of  $\overline{EL\pm}$ ,  $\overline{ORG}$ , ZERO, INS (or  $\overline{INP}$ ), FKEEP and  $\overline{INT}$  signals.

If the "By Every 8 Bits" is designated by the register select command, conditions are not latched during processing for reading. If the "Collective Write/Read" is designated by the register select command, conditions at the start of processing for reading are latched. If you need to place the data bus in a stable condition during the read cycle, designate the "Collective Write/Read."

# 4.4 Reading Extension Status

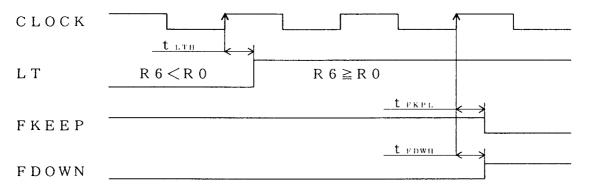

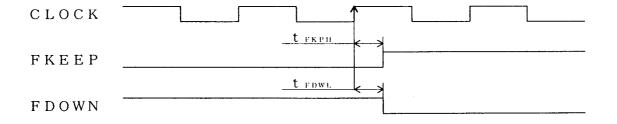

You can read the extension status from the R17 register. Extension status data you can monitor include the interrupt factor (cessation of pulse output/ramping-down point), pulse output, ON/OFF status of  $\overline{\text{SD}\pm}$ , FUP, FDOWN, LT, ALM and EC-Z. the pulse output suspension factor and the EC-Z counter value.

# 4.5 Default Conditions

| Items                   | Default (Reset) Conditions |

|-------------------------|----------------------------|

| All internal registers  | 0                          |

| Start mode command      | 00нех                      |

| Control mode command    | 40нех                      |

| Register select command | 80нех                      |

| Output mode command     | С0нех                      |

| Pins D0 to D7           | High impedance             |

| INT pin                 | High level                 |

| POUT pin                | High level                 |

| PDIR pin                | High level                 |

| HOLD pin                | High level                 |

| OTS pin                 | Low level                  |

| SYNO/CLR pin            | High level                 |

| FDOWN pin               | Low level                  |

| FKEEP pin               | High level                 |

| FUP pin                 | Low level                  |

| LT pin                  | High level                 |

| ZERO pin                | High level                 |

# 4.6 Precautions in Designing Software

- To use all functions of the LSI, place it in the standard mode by setting bit 3 of the output mode command at 1. If you place the LSI in the interchangeable mode with the 240K by setting the bit at 0, some functions are not available.

- If you select the "Collective Write/Read" of register data, allow a time length of two cycles of the reference clock between:

- (1) Writing the register select command and reading the data

- (2) Writing the low-place data and writing the next register select command or data.

- Write data to the register in order from the high- to middle- and low-place data if the "Collective Write/Read" is selected.

- Enter 1 or higher value in registers R1 to R3. Enter 2 or higher value in registers R4, R5 and R7. For preset mode operation, enter 1 or higher value in the R0 register.

- Before sending the start mode command, write the clear command (08HEX). The LSI has a latch to keep the stop condition if stopped at the previous stage and you need to reset the latch before starting. The latch can be reset by setting bit 4 of the start mode command at 0.

- Write the start mode command after setting all necessary conditions, since the start mode command starts the LSI generating pulses.

- The register select command does not allow you to read the present conditions. Take care when changing the register select command for interrupt processing.

# 5. Operation

# 5.1 Setting Pulse Output Pattern

The LSI provides the following two acceleration/deceleration modes:

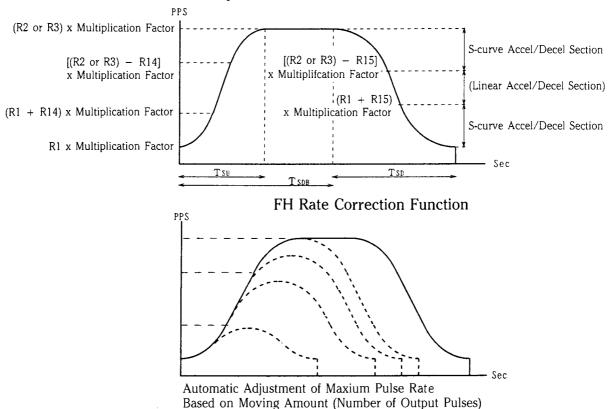

- (1) S-curve acceleration/deceleration with no intermediate linear section. This mode is initiated if registers R14 and R15 are set at "0" or a value higher than "(R2 or R3 value R1 value) ÷ 2." In this mode the acceleration or deceleration rate is constantly changed from the start to end.

- (2) S-curve acceleration/deceleration with intermediate linear section. This mode is initiated if registers R14 and R15 are set at other than "0" and the values are lower than "(R2 or R3 value R1 value)  $\div$  2." In this mode an S-curve acceleration/deceleration is made at the start and the end and a linear acceleration/deceleration, in between.

A pulse output pattern depends on parameters entered in registers R1 to R7 and R14 and R15. Also, if a moving amount is too small in preset mode operation, a maximum pulse rate is automatically lowered to permit smooth S-curve acceleration/deceleration. In this case, the smaller the moving amount, the shorter the linear acceleration/deceleration section and if the linear section is zero, the S-curve section is made shorter. The FH rate correction function can be turned off as required.

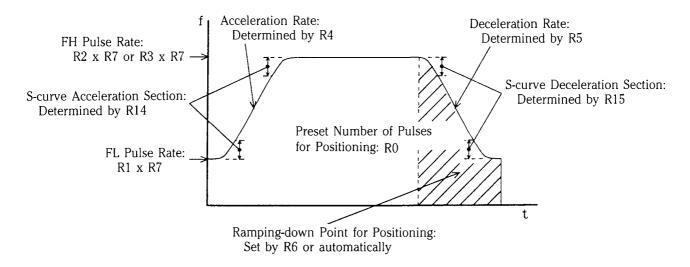

#### Pulse Output Pattern with S-curve Acceleration/Deceleration

# 5.1.1 Multiplication Parameter [16-bit R7 Register]

Write the multiplication parameter to the R7 register in a range of 2 to 65,536 (FFFFHEX). The parameter will determine the factor to multiply the pulse rates entered in registers R1, R2 and R3. The higher the multiplication factor, the coarser the selectable pulse rate steps. Usually therefore, a smaller multiplication factor is used. Relations between the R7 value and a multiplication factor are expressed with the following equation:

R7 value =  $\frac{\text{Reference clock (Hz)}}{\text{(Multiplication factor) x 8192}}$

Examples with a reference clock of 4.9152MHz

| R7 Value         | Multiplication<br>Factor | Output Pulse Rate (pps) |

|------------------|--------------------------|-------------------------|

| 60000 (0ЕА60нех) | 0.01                     | 0.01 to 81.91           |

| 30000 (7530нех)  | 0.02                     | 0.02 to 163.82          |

| 12000 (2ЕЕОнех)  | 0.05                     | 0.05 to 409.55          |

| 6000 (1770нех)   | 0.1                      | 0.1 to 819.1            |

| 3000 (ОВВВнех)   | 0.2                      | 0.2 to 1638.2           |

| 1200 (4В0нех)    | 0.5                      | 0.5 to 4095.5           |

| 600 (258нех)     | 1                        | 1 to 8191               |

| 300 (12Снех)     | 2                        | 2 to 16382              |

| 120 (78нех)      | 5                        | 5 to 40955              |

| 60 (3Снех)       | 10                       | 10 to 81910             |

| 30 (1Енех)       | 20                       | 20 to 163820            |

| 12 (ОСнех)       | 50                       | 50 to 409550            |

| 6 (6нех)         | 100                      | 100 to 819100           |

| 2 (2нех)         | 300                      | 300 to 2457300          |

To obtain a maximum output pulse rate of 50 kpps with 5,000 entered in the R1, R2 or R3 register, for example, enter 60 in the R7 register to multiply the pulse rate by 10 times.

# 5.1.2 FL Pulse Rate [13-bit R1 Register]

Write the FL pulse rate to the R1 register in a range of 1 to 8,191 (1FFFHEX). The rate will be multiplied by the multiplication factor determined by the R7 value to be used for constant-speed operation or at the start and end of varied-speed operation.

R1 value = Output pulse rate (pps)

Mutiplication factor

e.g. To obtain an output pulse rate of 100 pps through 10 times multiplication, write 10 to the R1 register.

# 5.1.3 FH1 Pulse Rate [13-bit R2 Register]

Write the FH1 pulse rate to the R2 register in a range of 1 to 8,191 (1FFFHEX). The rate will be multiplied by the multiplication factor determined by the R7 register to be used for constant-speed or varied-speed operation. For varied-speed operation, the FH1 pulse rate should be higher than the FL pulse rate.

R2 value =

$$\frac{\text{Output pulse rate (pps)}}{\text{Mutiplication factor}}$$

e.g. To obtain an output pulse rate of 50 kpps through 10 times multiplication, write 5000 to the R2 register.

# 5.1.4 FH2 Pulse Rate [13-bit R3 Register]

Write the FH2 pulse rate to the R3 register in a range of 1 to 8,191 (1FFFHEX). The rate will be multiplied by the multiplication factor determined by the R7 register to be used for constant-speed or varied-speed operation. For varied-speed operation, the FH2 pulse rate should be higher than the FL pulse rate. You may freely use either FH1 or FH2 pulse rate.

R3 value =

$$\frac{\text{Output pulse rate (pps)}}{\text{Mutiplication factor}}$$

e.g. To obtain an output pulse rate of 40 kpps through 10 times multiplication, write 4000 to the R3 register.

# 5.1.5 Maximum Acceleration Parameter [16-bit R4 Register]

Write a maximum acceleration parameter to the R4 register in a range of 1 to 65,535 (FFFFHEX). If the automatic ramping-down point setting function is made valid, the parameter entered here is also used for deeceleration. Relations between the R4 value and a maximum acceleration rate Asu (pps/sec) are expressed with the following equation:

R4 value =

$$\frac{\text{(Multiplication factor) x (Reference clock, Hz) x 2}}{\text{Maximum acceleration rate Asu}}$$

e.g. To obtain a maximum acceleration rate of 100 kpps/sec through 10 times multiplication, write 983 to the R4 register.

$$(10 \times 4915200 \times 2) \div 100000 = 983.$$

# 5.1.6 Maximum Deceleration Parameter [16-bit R5 Register]

Write a maximum deceleration parameter to the R5 register in a range of 1 to 65,535 (FFFFHEX). If the automatic ramping-down point setting function is made valid, the parameter entered here has no function and that entered in the R4 register is used for deceleration. Relations between the R5 value and a maximum deceleration rate AsD (pps/sec) are expressed with the following equation, where AsD is an absolute value of practical deceleration (negative).

R5 value =

$$\frac{\text{(Multiplication factor) x (Reference clock, Hz) x 2}}{\text{Maximum deceleration rate Asp}}$$

e.g. To obtain a maximum deceleration rate of 80 kpps/sec through 10 times multiplication, write 1229 to the R5 register.

$(10 \times 4915200 \times 2) \div 80000 = 1229$

# 5.1.7 S-curve Acceleration Section [16-bit R14 Register]

Write the S-curve acceleration section to the R14 register in a range of 1 to 4,095 (FFFHEX). An S-curve acceleration will be made from the starting pulse rate (R1 value x multiplication factor) to the point [starting pulse rate + (R14 value x multiplication factor)] and from the point [target operating pulse rate - (R14 value x multiplication factor)] to the target operating pulse rate [(R2 or R3) x multiplication factor]. And a linear acceleration will be made in between. If the R14 register is set at 0 (default), S-curve acceleration will be made based on [(operating pulse rate - starting pulse rate)  $\div$  2] and no linear acceleration will be made. To put an intermediate linear acceleration, set the R14 register in a range of 1 to a value lower than [(operating pulse rate - starting pulse rate)  $\div$  2]. Relations between the R14 value and an S-curve acceleration section S (pps) are expressed with the following equation:

R14 value =

$$\frac{\text{S-curve acceleration section S (pps)}}{\text{(Multiplication factor)}}$$

e.g. Write 1000 to the R14 register with multiplication factor = 10, starting pulse rate = 100 pps (R1 = 10) and operating pulse rate = 50,000 pps (R2 = 5000). S will be 10,000 and an S-curve acceleration will be made in a section of 100 to 10,100 pps and in a section of 40,000 to 50,000 pps.

# **5.1.8** S-curve Deceleration Section [12-bit R15 Register]

Write the S-curve deceleration section to the R15 register in a range of 1 to 4,095 (FFFHEX). An S-curve deceleration will be made from the operating pulse rate to the point [operating pulse rate — (R15 value x multiplication factor)] and from the point (R15 value x multiplication factor) to the starting pulse rate. And a linear deceleration will be made in the intermediate section.

If the R15 register is set at 0 (default), S-curve deceleration will be made based on [(operating pulse rate - starting pulse rate)  $\div$  2]. No linear deceleration will be made. To put an intermediate linear deceleration, set the R15 register in a range of 1 to a value lower than [(operating pulse rate - starting pulse rate)  $\div$  2]. Relations between the R15 value and an S-curve deceleration section S (pps) are expressed with the following equation:

R15 value =

$$\frac{\text{S-curve deceleration section S (pps)}}{\text{(Multiplication factor)}}$$

e.g. Write 1000 to the R15 register with multiplication factor = 20, starting pulse rate = 500 pps (R1 = 25) and operating pulse rate = 100,000 pps (R2 = 5000). S will be 20,000 and an S-curve deceleration will be made in a section of 100,000 to 80,000 pps and in a section of 20,500 to 500 pps.

#### 5.1.9 Acceleration/Deceleration Time

You can obtain the acceleration/deceleration time based on values entered in registers R1 to R5 and R14 and R15. The equation differs depending on the acceleration/deceleration mode as follows:

(1) S-curve Acceleration/Deceleration with No Intermediate Linear Section

Acceleration time Tsu (s) =

$$\frac{(R2 - R1) \times R4}{\text{Reference clock (Hz)}}$$

Deceleration time Tsu (s) =

$$\frac{(R2 - R1) \times R5}{\text{Reference clock (Hz)}}$$

(2) S-curve Acceleration/Deceleration with Intermediate Linear Section

Acceleration time Tsu (s) =

$$\frac{(R2 - R1 + R14 \times 2) \times R4}{Reference clock (Hz) \times 2}$$

Deceleration time Tsu (s) =

$$\frac{(R2 - R1 + R15 \times 2) \times R5}{Reference clock (Hz) \times 2}$$

Substitute R3 for R2 if you use the R3 register for the operating pulse rate. Also, if the automatic ramping-down point setting function is made valid, substitute R4 for R5, since the R4 value is used in place of the R5 value for deceleration.

# 5.1.10 Ramping-down Point [24-bit R6 Register]

For varied-speed operation in the preset mode, write the ramping-down starting point (number of total pulses output before stop) to the R6 register in a range of 0 to 16,777,215 (FFFFFHEX).

The LSI provides the automatic ramping-down point setting function which can be made valid or invalid by the control mode command bit 4. If the function is made valid, the R6 value is offset from the automatic setting value. A resultant positive value starts ramping-down earlier and a negative value delays ramping-down. In the case of automatic setting, reset the R6 register once with the clear command, and then write the ramping-down point to the R6 register in a range of -8,388,608 (8000000HEX) to +8,388,607 (8FFFFFHEX).

If the automatic setting function is made invalid, the ramping-down point entered in the R6 register is used as it is.

- For normal operation of the automatic ramping-down point setting function, the time Tsdb from the start of acceleration to the start of deceleration should be equal to or longer than the deceleration time Tsd. Generally, the R14 value should be equal to or longer than the R15 value. (See the pulse output pattern with S-curve acceleration/deceleration on page 19.

- For the manual setting of ramping-down point, use the following procedure to obtain the value to be entered in the R6 register. If you use the FH2 pulse rate, substitue R3 for R2 in the equations below.

#### 5.1.10.1 S-curve Acceleration/Deceleration with No Linear Section

(1) Make sure of the trapezoidal motion profile pulse output pattern. If the moving amount is too small, acceleration is not available to the FH pulse rate, thereby resulting in a triangular motion profile pattern.

Minimum number of output pulses required for trapezoidal profile

$$= \frac{(R2^2 - R1^2) \times (R4 + R5)}{R7 \times 16384}$$

(2) Revise FH pulse rate.

If a preset number of output pulses (R0) is equal to or lower than a minimum number of output pulses, a triangular pattern results. Therefore, revise the FH pulse rate required for the trapezoidal profile.

Revised FH pulse rate (R2) =

$$\sqrt{\frac{R0 \times R7 \times 16384}{R4 + R5} + R1^2}$$

(3) Write the ramping-down point to the R6 register.

Ramping-down point (R6) =

$$\frac{(R2^2 - R1^2) \times R5}{R7 \times 16384}$$

#### 5.1.10.2 S-curve Acceleration/Deceleration with Linear Section

(1) Make sure of the trapezoidal motion profile pulse output pattern. If the moving amount is too small, acceleration is not available to the FH pulse rate, thereby resulting in a triangular pattern.

Minimum number of output pulses required for trapezoidal pattern  $= \frac{(R1 + R2) \times [(R2 - R1) \times (R4 + R5) + 2 \times (R4 \times R14 + R5 \times R15)]}{R7 \times 32768}$

(2) Make sure of the linear acceleration/decleration section.

If a preset number of output pulses (R0) is equal to or lower than a minimum number of output pulses required for the trapezoidal pattern, make sure that a linear acceleration/deceleration section is available.

[In the case of

$$R14 = R15$$

]

Minimum number of output pulses required

to put an intermediate linear acceleration/deceleration section

$$= \frac{(R1 + R14) \times R14 \times (R4 + R5)}{R7 \times 4096}$$

[In the case of R14 > R15]

Minimum number of output pulses required

to put an intermediate linear acceleration/deceleration section

$$= \frac{(R1 + R14) \times [R5 \times (R14 + R15) + 2 \times R4 \times R15]}{R7 \times 8192}$$

In the case of R14 < R15:

Minimum number of output pulses required

to put an intermediate linear acceleration/deceleration section

$$= \frac{(R1 + R15) \times [R4 \times (R14 + R15) + 2 \times R5 \times R15]}{R7 \times 8192}$$

(3) Revise the FH pulse rate.

If a minimum number of output pulses required to put an intermediate acceleration/deceleration section is lower than the preset number of output pulses (R0), and the R0 value is equal to or lower than a minimum number of output pulses required for a trapezoidal pattern, revise the FH pulse rate to avoid a triangular pattern.

In the case of R14 = R15:

Revised FH pulse rate (R2) =

$$R14 + \sqrt{(R14 - R1)^2 - \frac{R0 \times R7 \times 32768}{R4 + R5}}$$

In the case of R14 o R15:

Revised FH pulse rate (R2) =

$$-A + \sqrt{(A - B \times R1)^2 + (B \times R0 \times R7 \times 32768)}$$

B

Where,

$$A = R4 \times R14 + R5 \times R15$$

$B = R4 + R5$

If the preset number of output pulses (R0) is equal to or lower than a minimum number of output pulses required to put an intermediate linear acceleration/deceleration section, enter 0 in R14 and R15 registers to effect the S-curve acceleration/deceleration mode with no intermediate linear section, and follow instructions of 5.1.10.1.

(4) Write the ramping-down point to the R6 register.

Ramping-down point (R6) =

$$\frac{(R1 + R2) \times (R2 - R1 + R15 \times 2) \times R5}{R7 \times 32768}$$

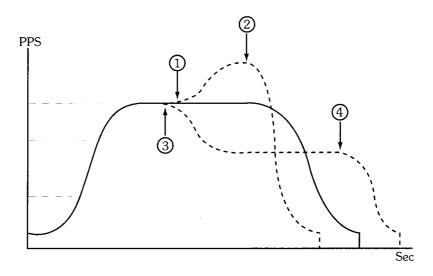

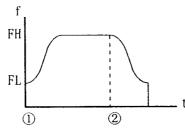

# 5.1.11 Changing Pulse Output Pattern in Motion

You can change the pulse output speed during pulse output in progress by revising the FH pulse rate. However, if the automatic ramping-down point setting function is made valid, do not revise parameters entered in R1, R4, R5, R14 and R15 registers during operation. The automatic ramping-down point setting function cannot follow the revision.

# Examples of Changing Pulse Output Pattern in Motion in Preset Mode

- 1) ① The operation speed is increased due to revision of the R2 or R3 value to a higher pulse rate.

- (FH1 or FH2 varied-speed start command)

- 2 Ramping-down starts automatically at the ramping-down point.

- 2) ③ The operation speed is decreased due to revision of the R2 or R3 value to a lower pulse rate.

- (FH1 or FH2 varied-speed start command)

- 4 Ramping-down starts automatically at the ramping-down point.

#### 5.2 Bits of Command Buffer

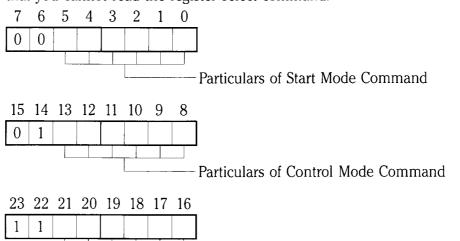

To operate the LSI, you need to write data to the command buffer and registers through the 8-bit data bus. Commands are classified into four types by high-place two bits as in the chart below. The LSI provides the command buffer to hold the content of each type of command and to retain the content until the next command of same type is written.

Each command is not a code but provides functions by bits. Therefore, you can set a command other than exampled in this manual.

Writing the start mode command starts the LSI generating pulses. Therefore, write this command at the end.

Besides the command buffer, the LSI provides extension mode registers R12 and R13. Note, however, that the extension mode registers cannot be used if the LSI is placed in the interchangeable mode with the 240K.

| _D7 | D6 | D5              | D4              | D3  | D2 | D1 | D0 |  |  |  |  |  |

|-----|----|-----------------|-----------------|-----|----|----|----|--|--|--|--|--|

| C1  | C0 |                 |                 |     |    |    |    |  |  |  |  |  |

| C1  | C0 |                 | Type of Command |     |    |    |    |  |  |  |  |  |

| 0   | 0  | Sta             | rd m            | ode |    |    |    |  |  |  |  |  |

| 0   | 1  | Co              | Control mode    |     |    |    |    |  |  |  |  |  |

| 1   | 0  | Register select |                 |     |    |    |    |  |  |  |  |  |

| 1   | 1  | Output mode     |                 |     |    |    |    |  |  |  |  |  |

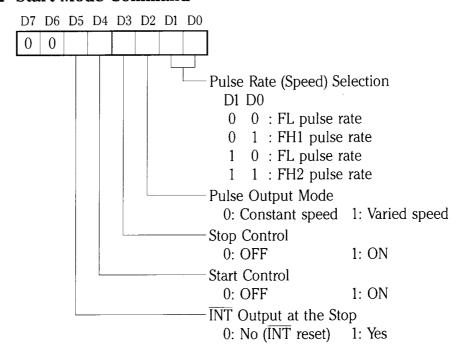

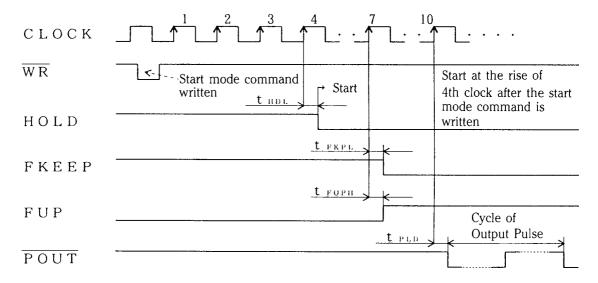

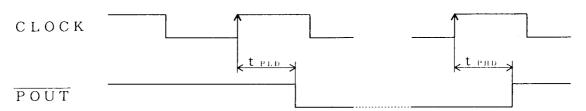

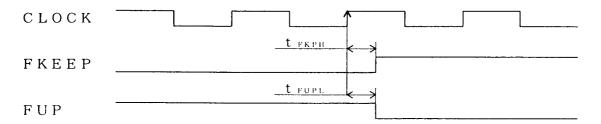

#### 5.2.1 Start Mode Command

#### Pulse Rate Selection (Bits 1 and 0)

Select the R1, R2 or R3 register, the pulse rate of which you want to use, by entering 00, 01 or 11 in these bits. The output pulse rate is a product of the parameter written in the register and the multiplication factor determined by the R7 register.

#### Pulse Output Mode (Bit 2)

Enter 0 in bit 2. The LSI will output pulses at a fixed rate selected by bits 1 and 0. In constant-speed operation,  $\overline{SD} \pm$  signals and ramping-down point setting in the R6 register have no function.

Enter 1 in bit 2. The LSI will output pulses while accelerating the rate from the FL to FH rate at the start and decelerating it from the FH to FL rate before stop. In varied-speed operation  $\overline{SD} \pm$  signals and the ramping-down point setting for the preset mode have respective functions.

#### Start/Stop Control (Bit 4 or 3)

Enter 1 in bit 4 to start the LSI generating pulses and enter 1 in bit 3 to stop it. By using bits 4 and 3 in combination, you can perform deceleration-stop.

#### **INT** Output at the Stop (Bit 5)

Enter 1 in bit 5. The  $\overline{INT}$  signal will be output when the LSI will stop generating pulses due to completion of the preset mode operation, the  $\overline{EL\pm}$ ,  $\overline{ORG}$  or  $\overline{ALM}$  signal or the stop command.

To reset the INT signal, set bit 5 at 0. Also, if you want to mask the INT signal at the time of stop, set bit 5 at 0.

In the standard mode the LSI can output the  $\overline{\text{INT}}$  signal at the ramping-down point with bit 13 of R12 register set at 1.

The INT pin outputs a logical sum—the interrupt signal due to stop or ramping-down point. To find which factor causes the INT signal, check the extension status register.

#### Clear Command

The LSI provides a latch to hold the stop condition. Therefore, to start the LSI generating pulses anew, you need to reset the latch. Enter 0 in bit 4 of the start mode command. The latch will be reset. Before starting, write the clear command (typically, 08HEX for immediate stop). The clear command will also be used to reset the ramping-down point counter if the automatic ramping-down point setting function is made valid.

Typical Settings of Start Mode Command

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | HEX | Description                                                                                                                                                        |

|----|----|----|----|----|----|----|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 10  | Constant-speed operation at FL rate with no $\overline{\text{INT}}$ signal at the stop                                                                             |

| 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 30  | Constant-speed operation at FL rate with the $\overline{\text{INT}}$ signal at the stop                                                                            |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 11  | Constant-speed operation at FH1 rate with no $\overline{\text{INT}}$ signal at the stop                                                                            |

| 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 15  | Constant-speed operation at FH2 rate with no $\overline{\text{INT}}$ signal at the stop                                                                            |

| 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 15  | Varied-speed operation with no $\overline{\text{INT}}$ signal at the stop; acceleration from FL to FH1 rate                                                        |

| 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 17  | Varied-speed operation with no $\overline{\text{INT}}$ signal at the stop; acceleration from FL to FH2 rate                                                        |

| 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 14  | Deceleration on the way with no $\overline{\text{INT}}$ signal at the stop: deceleration from FH1 or FH2 to FL rate                                                |

| 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1F  | Deceleration-stop with no INT signal at the stop;<br>Stop when the FL rate is reached through deceleration<br>from the FH rate (clear command required after stop) |

| 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 3F  | Deceleration-stop with the INST signal at the stop                                                                                                                 |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 08  | Immediate stop (= clear command) with no $\overline{\text{INT}}$ signal at the stop                                                                                |

| 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 28  | Immediate stop with the $\overline{\text{INT}}$ signal at the stop                                                                                                 |

Note: FL, FH1 and FH2 rates here are output pulse rates (pulse rates written to R1, R2 and R3 registers x the multiplication factor determined by the R7 value).

#### **5.2.2 Control Mode Command**

#### ORG Signal Control (Bit 0)

You can select whether the  $\overline{ORG}$  signal stops the LSI from generating pulses or not.

Enter 1 in bit 0. Putting the  $\overline{ORG}$  pin at low level will immediately stop the LSI from generating pulses. This function is useful for origin return. Origin return is also available with a combination of the  $\overline{ORG}$  signal and Z-phase signal.

Enter 0 in bit 0. The  $\overline{ORG}$  pin will have no function. However, you can monitor the  $\overline{ORG}$  signal using the status buffer.

#### SD Signal Control (Bit 1)

You can select whether SD  $\pm$  signal decelerates the output pulse rate or not. Enter 1 in bit 1. Putting the  $\overline{SD}$  pin in the moving direction at low level will decelerate the output pulse rate from FH to FL, and the LSI will keep generating pulses at the FL rate until the  $\overline{SD}$  signal will recover high level. Enter 0 in bit D1.  $\overline{SD}\pm$  pins will have no function. However, you can check the  $\overline{SD}$  signal ON/OFF status with the extension status register.

#### Preset Mode Operation (Bit 2)

Enter 1 in bit 2 with a desired number of pulses written to the preset counter (R0 register). The start mode command will start the LSI generating pulses while letting the preset counter count down by every pulse output. When the counter value becomes equal to or higher than the ramping-down point value set in the R6 register, the LSI will decelerate the output pulse rate and stop generating pulses when the counter counts down to 0.

If you enter 0 in bit 2, the preset counter counts down but the LSI does not stop generating pulses when the counter counts down to 0.

#### Moving Direction (Bit 3)

You can select the direction of output pulses. Enter 0 in bit 3 to select plus direction pulses and enter 1 to select minus direction pulses. For relations between the direction signal pin and the pulse output pin, refer to "5.4.2 Pulse Output Mode."

Setting of this bit is related with the direction of  $\overline{EL\pm}$  and  $\overline{SD\pm}$  signals.

#### Automatic Ramping-down Point Setting (Bit 4)

Enter 0 in bit 4. The ramping-down point will be as written to the R6 register.

Enter 1 in bit 4. The ramping-down point will be automatically calculated during acceleration and pulse output at the FH rate. If a parameter is written to the R6 register, the value is added to the automatically calculated value to make a ramping-down point.

#### Present Position Counter (Bit 5)

You can turn the present position counter on or off.

Enter 1 in bit 5. The present position counter will count up by every output of plus direction pulse or will count down by every output of minus direction pulse.

Enter 0 in bit 5. The present position counter will not operate.

For the continuous mode, preset mode and origin return, refer to "5.3 Operation Modes."

# **Typical Settings of Start Mode Command**

(Mark "-" in the table may be 0 or 1.)

| D6 | D5                                                                                          | D4                                                                 | D3                                                                                                                                                                                                                                                                                                                                                                                                        | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 0                                                                                           | _                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Makes ORG signal control invalid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |