# User's Manual For PCL6045BL Pulse Control LSI

Thank you for considering our pulse control LSI, the "PCL6045B."

To learn how to use the PCL6045B, read this manual to become familiar with the product.

The handling precautions for installing this LSI are described at the end of this manual. Make sure to read them before installing the LSI.

In addition to this manual, the PLC6045B User's Manual, Application Version, will be available. It includes programming examples. Please contact us if you need a copy.

# [Cautions]

- (1) Copying all or any part of this manual without written approval is prohibited.

- (2) The specifications of this LSI may be changed to improve performance or quality without prior notice.

- (3) Although this manual was produced with the utmost care, if you find any points that are unclear, wrong, or have inadequate descriptions, please let us know.

- (4) We are not responsible for any results that occur from using this LSI, regardless of item (3) above.

- Explanation of the descriptions in this manual

- 1. The "x" "y" "z" and "u" of terminal names and bit names refer to the X axis, Y axis, Z axis and U axis, respectively.

- 2. Terminals with a # (ex.#RST) are negative logic. Their logic cannot be changed. Terminals without a # are positive logic. Their output logic can be changed.

- 3. When describing the bits in registers, "n" refers to the bit position. A "0" means that the bit is in position 0 and that it is prohibited to write to any bit other than "0". Finally, this bit will always return a "0" when read out.

# INDEX

| 1. | Outline and Features                                                                |    |

|----|-------------------------------------------------------------------------------------|----|

|    | 1-1. Outline                                                                        |    |

|    | 1-2. Features                                                                       | 1  |

|    |                                                                                     | _  |

| 2. | Specifications                                                                      | 5  |

| ^  | Townsia at Applicance and Dispusses                                                 | ,  |

| ა. | Terminal Assignment Diagram                                                         | ర  |

| 1  | Functions of Terminals                                                              | -  |

| 4. | runctions of terminals                                                              |    |

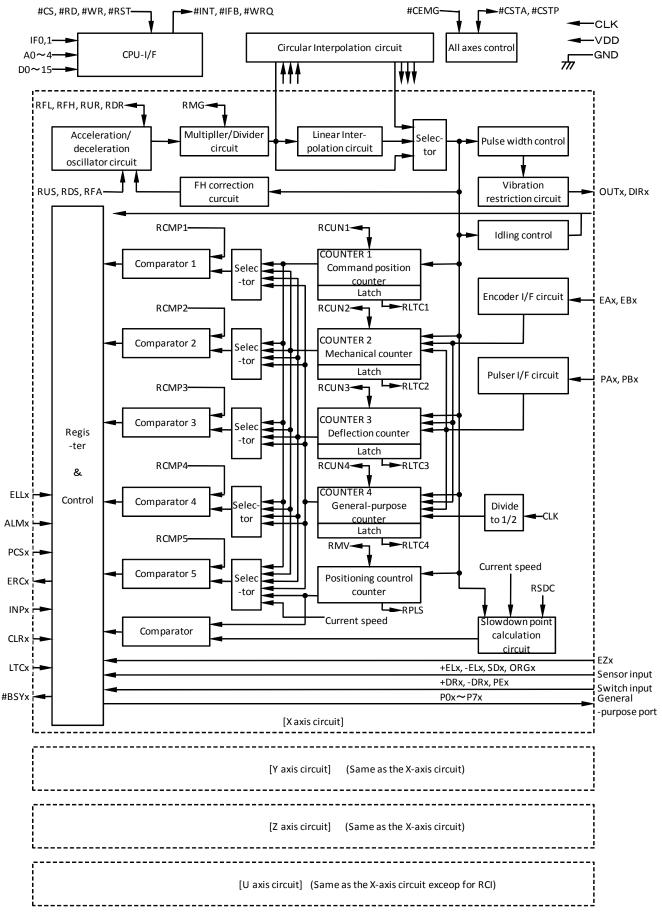

| 5  | Block Diagram                                                                       | 12 |

| ٥. | Blook Blagram                                                                       |    |

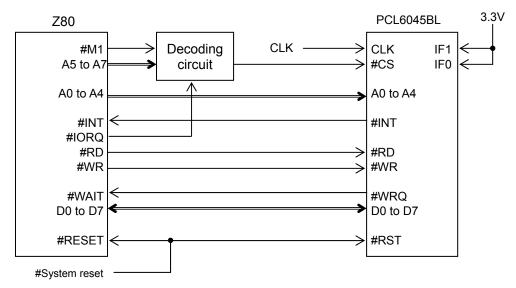

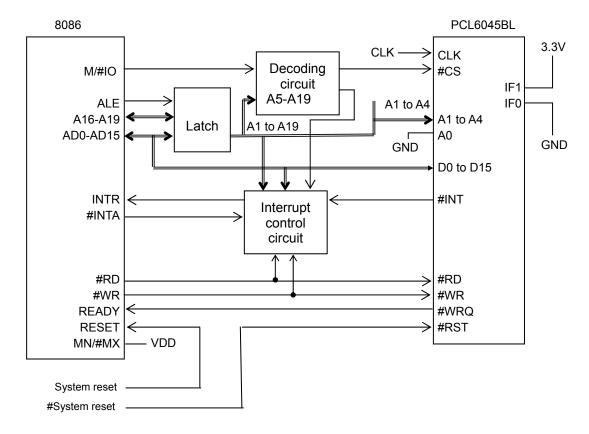

| 6. | CPU Interface                                                                       | 13 |

|    | 6-1. Setting up connections to a CPU                                                | 13 |

|    | 6-2. Precautions for designing hardware                                             |    |

|    | 6-3. CPU interface circuit block diagram                                            |    |

|    | 6-4. Address map                                                                    |    |

|    | 6-4-1. Axis arrangement map                                                         | 16 |

|    | 6-4-2. Internal map of each axis                                                    |    |

|    | 6-5. Description of the map details                                                 |    |

|    | 6-5-1. Write a command code and axis selection (COMW, COMB)                         |    |

|    | 6-5-2. Write to an output port (OTPW, OTPB)                                         | 18 |

|    | 6-5-3. Write/read the input/output buffer (BUFW, BUFB)                              |    |

|    | 6-5-4. Reading the main status (MSTSW, MSTSB)                                       |    |

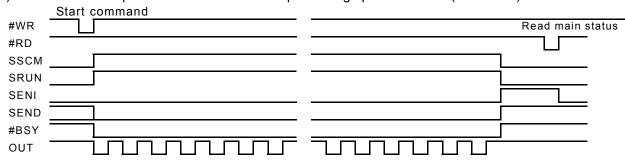

|    | 6-5-5. Reading the sub status and input/output port. (SSTSW, SSTSB, IOPB)           | 20 |

| 7  | Commands (Operation and Control Commands)                                           | 24 |

| ١. | 7-1. Operation commands                                                             |    |

|    | 7-1-1. Procedure for writing an operation command (the axis assignment is omitted)  |    |

|    | 7-1-1.1 Hocedure for writing an operation command (the axis assignment is offitted) |    |

|    | 7-1-3. Speed change command                                                         |    |

|    | 7-1-4. Stop command                                                                 |    |

|    | 7-1-5. NOP (do nothing) command                                                     |    |

|    | 7-2. General-purpose output bit control commands                                    | 24 |

|    | 7-3. Control command                                                                |    |

|    | 7-3-1. Software reset command                                                       | 25 |

|    | 7-3-2. Counter reset command                                                        |    |

|    | 7-3-3. ERC output control command                                                   |    |

|    | 7-3-4. Pre-register control command                                                 |    |

|    | 7-3-5. PCS input command                                                            |    |

|    | 7-3-6. LTCH input (counter latch) command                                           |    |

|    | 7-3-7. SENI, SEOR reset command                                                     |    |

|    | 7-4. Register control command                                                       |    |

|    | 7-4-1. Procedure for writing data to a register (the axis assignment is omitted)    |    |

|    | 7-4-2. Procedure for reading data from a register (the axis assignment is omitted)  |    |

|    | 7-4-3. Table of register control commands                                           |    |

|    | 7-5. General-purpose output port control command                                    |    |

|    | 7-5-1. Command writing procedures                                                   |    |

|    | 7-5-2 Command bit allocation                                                        | ∠8 |

| 8  | Registers                                                                           | 30 |

| J. | 8-1. Table of registers                                                             |    |

|    | 8-2. Pre-registers                                                                  |    |

|    | 8-2-1. Writing to the operation pre-registers                                       |    |

|    | 8-2-2. Cancel the operation pre-register                                            |    |

|    | 8-2-3. Writing to the comparator pre-registers                                      | 32 |

|    | 8-2-4. Cancel the comparator pre-register data                                      |    |

|    | 8-3.Description of the registers                                                    |    |

|    | 8-3-1. PRMV (RMV) register                                                          | 33 |

|             | PRFL (RFL) register                                                                           |     |

|-------------|-----------------------------------------------------------------------------------------------|-----|

|             | PRFH (RFH) register                                                                           |     |

|             | PRUR (RUR) register                                                                           |     |

|             | PRDR (RDR) register                                                                           |     |

|             | PRMG (RMG) register                                                                           |     |

|             | PRDP (RDP) register                                                                           |     |

|             | PRMD (RMD) register                                                                           |     |

|             | PRIP (RIP) registerPRUS (RUS) register                                                        |     |

|             | PRDS (RDS) register                                                                           |     |

|             | RFA register                                                                                  |     |

|             | RENV1 register                                                                                |     |

|             | RENV2 register                                                                                |     |

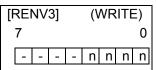

|             | RENV3 register                                                                                |     |

|             | RENV4 register                                                                                |     |

|             | RENV5 register                                                                                |     |

|             | RENV6 register                                                                                |     |

|             | RENV7 register                                                                                |     |

|             | RCUN1 register                                                                                |     |

|             | RCUN2 register                                                                                |     |

|             | RCUN3 register                                                                                |     |

| 8-3-23.     | RCUN4 register                                                                                | .51 |

|             | RCMP1 register                                                                                |     |

| 8-3-25.     | RCMP2 register                                                                                | .51 |

| 8-3-26.     | RCMP3 register                                                                                | .52 |

|             | RCMP4 register                                                                                |     |

|             | RCMP5 (PRCP5) register                                                                        |     |

|             | RIRQ register                                                                                 |     |

|             | RLTC1 register                                                                                |     |

|             | RLTC2 register                                                                                |     |

|             | RLTC3 register                                                                                |     |

|             | RLTC4 register                                                                                |     |

|             | RSTS register                                                                                 |     |

|             | REST register                                                                                 |     |

|             | RIST register                                                                                 |     |

|             | RPLS register                                                                                 |     |

|             | RSPD register                                                                                 |     |

|             | PRCI (RCI) register                                                                           |     |

|             | RCIC register                                                                                 |     |

|             | RIPS register                                                                                 |     |

| 0-3-42.     | Till O Toglotol                                                                               | .00 |

| 9 Operation | Mode                                                                                          | 60  |

| 9-1. Contin | nuous operation mode using command control                                                    | 60  |

|             | oning operation mode                                                                          |     |

| 9-2-1. F    | Positioning operation (specify a target position using an incremental value) (MOD: 41h)       | 60  |

|             | Positioning operation (specify the absolute position in COUNTER1) (MOD: 42h)                  |     |

|             | Positioning operation (specify the absolute position in COUNTER2) (MOD: 43h)                  |     |

|             | Command position 0 return operation (MOD: 44h)                                                |     |

| 9-2-5. N    | Mechanical position 0 return operation (MOD: 45h)                                             | 61  |

| 9-2-6. 0    | One pulse operation (MOD: 46h, 4Eh)                                                           | .61 |

|             | Timer operation (MOD: 47h)                                                                    |     |

|             | r (PA/PB) input mode                                                                          |     |

|             | Continuous operation using a pulsar input (MOD: 01h)                                          |     |

|             | Positioning operations using a pulsar input (specify incremental position) (MOD: 51h)         |     |

|             | Positioning operation using pulsar input (specify absolute position to COUNTER1) (MOD: 52h)   |     |

|             | Positioning operation using pulsar input (specify the absolute position in COUNTER2) (MOD: 53 |     |

|             | 2                                                                                             |     |

|             | Command position zero return operation using a pulsar input (MOD: 54h)                        |     |

|             | Mechanical position zero return operation using pulsar input (MOD: 55h)                       |     |

|             | Continuous linear interpolation 1 using pulsar input (MOD: 68h)                               |     |

|             | Linear interpolation 1 using pulsar input (MOD: 69h)                                          |     |

| 9-3-9. C    | Continuous linear interpolation 2 using pulsar input (MOD: 6Ah)                               | .00 |

|             | - iii -                                                                                       |     |

| 9-3-10. Linear interpolation 2 using pulsar input (MOD: 6Bh)                                      | 66                                                                                                      |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 9-3-11. CW circular interpolation using pulsar input (MOD: 6Ch)                                   |                                                                                                         |

| 9-3-12. CCW circular interpolation using pulsar input (MOD: 6Dh)                                  | 66                                                                                                      |

| 9-4. External switch (±DR) operation mode                                                         | 67                                                                                                      |

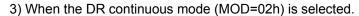

| 9-4-1. Continuous operation using an external switch (MOD: 02h)                                   | 67                                                                                                      |

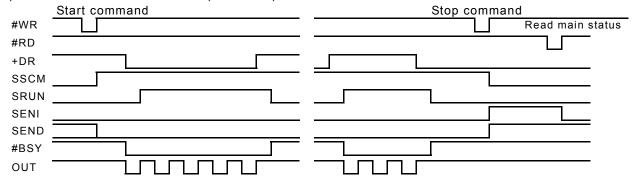

| 9-4-2. Positioning operation using an external switch (MOD: 56h)                                  | 68                                                                                                      |

| 9-5. Origin position operation mode                                                               |                                                                                                         |

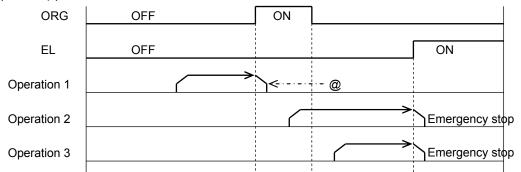

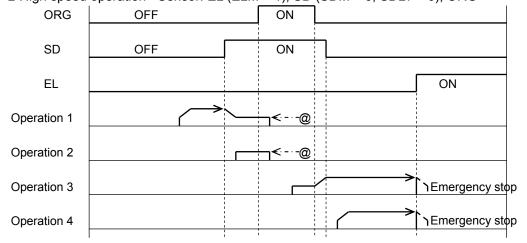

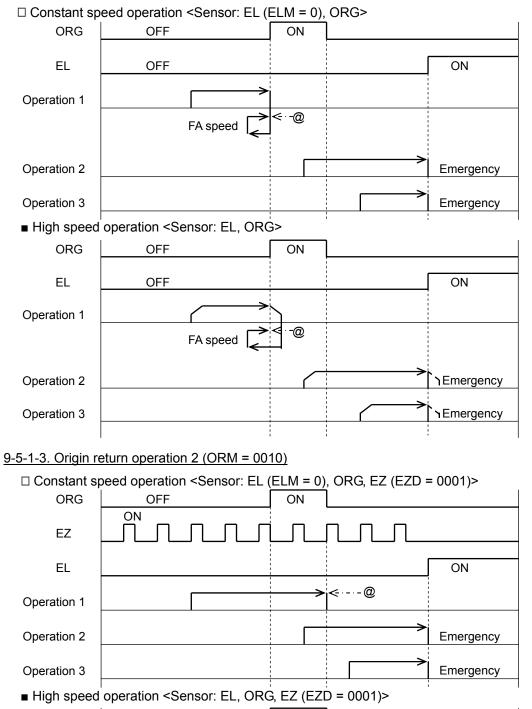

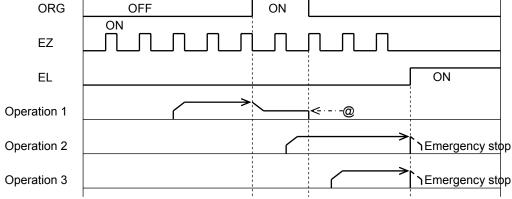

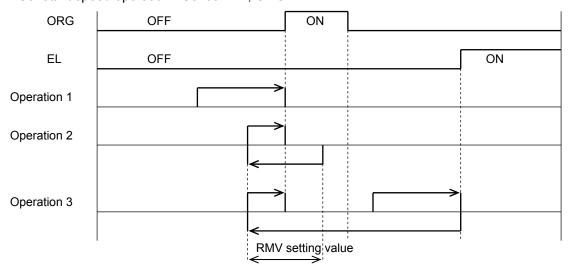

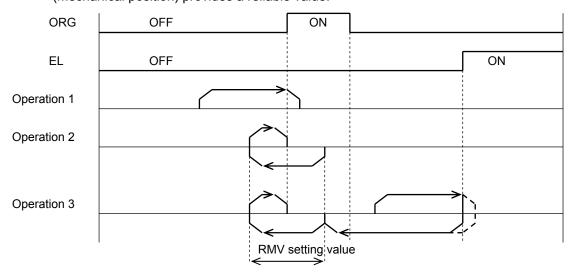

| 9-5-1. Origin return operation                                                                    |                                                                                                         |

| 9-5-2. Leaving the origin position operations                                                     |                                                                                                         |

| 9-5-3. Origin search operation                                                                    |                                                                                                         |

| 9-6. EL or SL operation mode                                                                      |                                                                                                         |

| 9-6-1. Feed until reaching an EL or SL position                                                   |                                                                                                         |

| 9-6-2. Leaving an EL or SL position                                                               |                                                                                                         |

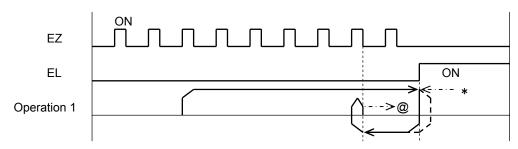

| 9-7. EZ count operation mode                                                                      |                                                                                                         |

| 9-8. Interpolation operations                                                                     |                                                                                                         |

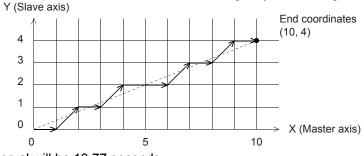

| 9-8-1.Interpolation operations                                                                    |                                                                                                         |

| 9-8-2. Interpolation control axis                                                                 |                                                                                                         |

| 9-8-3. Synthesized speed constant control                                                         |                                                                                                         |

| 9-8-4. Continuous linear interpolation 1 (MOD: 60h)                                               |                                                                                                         |

| 9-8-5. Linear interpolation 1 (MOD: 61h)                                                          |                                                                                                         |

| 9-8-6. Continuous linear interpolation 2 (MOD: 62h)                                               |                                                                                                         |

| 9-8-7. Linear interpolation 2 (MOD: 63h)                                                          |                                                                                                         |

| 9-8-8. Circular interpolation                                                                     |                                                                                                         |

| 9-8-9. Circular interpolation synchronized with the U axis                                        |                                                                                                         |

| 9-8-10. Interpolation operation synchronized with PA/PB                                           |                                                                                                         |

| 9-8-11. Operation during interpolation                                                            |                                                                                                         |

| 5-5-11. Operation during interpolation                                                            |                                                                                                         |

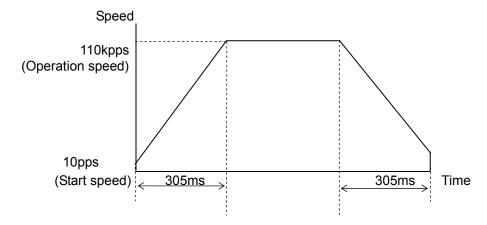

| 10. Speed patterns                                                                                | 90                                                                                                      |

| 10-1. Speed patterns                                                                              |                                                                                                         |

| 10-2. Speed pattern settings                                                                      |                                                                                                         |

| 10-3. Manual FH correction                                                                        |                                                                                                         |

|                                                                                                   |                                                                                                         |

| 10-4 Example of Semino no an acceleration/deceleration speed pattern                              |                                                                                                         |

| 10-4. Example of setting up an acceleration/deceleration speed pattern                            |                                                                                                         |

| 10-4. Example of setting up an acceleration/deceleration speed pattern                            |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  | 100                                                                                                     |

| 10-5. Changing speed patterns while in operation                                                  | 100                                                                                                     |

| 10-5. Changing speed patterns while in operation                                                  | 100<br>101<br>101                                                                                       |

| 10-5. Changing speed patterns while in operation                                                  | 100<br>101<br>101<br>102                                                                                |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions               |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions 11-1. Reset   |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions.  11-1. Reset |                                                                                                         |

| 10-5. Changing speed patterns while in operation.  11. Description of the Functions.  11-1. Reset |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  |                                                                                                         |

| 10-5. Changing speed patterns while in operation                                                  | 100 101 101 101 102 102 103 104 106 106 107 107 108 111 112 112 113 114 115 116 116 117 118 119 119     |

| 10-5. Changing speed patterns while in operation                                                  | 100 101 101 101 102 102 103 104 104 106 107 107 108 111 112 112 115 116 116 117 118 119 119 119 119 119 |

| 11-11-2. Software limit function                                  | 129 |

|-------------------------------------------------------------------|-----|

| 11-11-3. Out of step stepper motor detection function             | 130 |

| 11-11-4. IDX (synchronous) signal output function                 | 131 |

| 11-11-5. Ring count function                                      |     |

| 11-12. Backlash correction and slip correction                    | 133 |

| 11-13. Vibration restriction function                             | 134 |

| 11-14. Synchronous starting                                       | 135 |

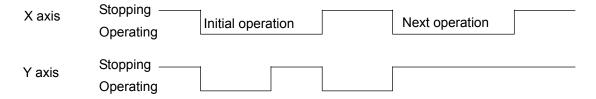

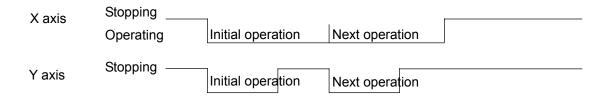

| 11-14-1. Start triggered by another axis stopping                 | 136 |

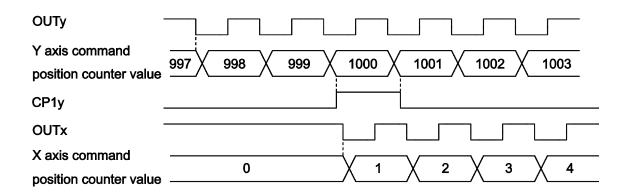

| 11-14-2. Starting from an internal synchronous signal             |     |

| 11-14-3. Continuous interpolation by dummy circular interpolation | 142 |

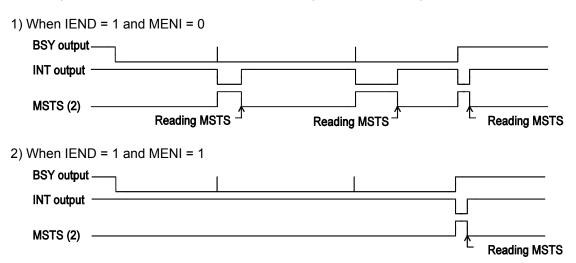

| 11-15. Output an interrupt signal                                 | 143 |

| 12. Electrical Characteristics                                    | 146 |

| 12-1. Absolute maximum ratings                                    | 146 |

| 12-2. Recommended operating conditions                            |     |

| 12-3. DC characteristics                                          |     |

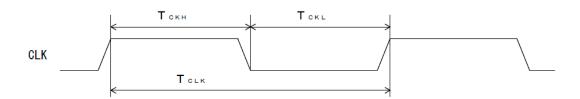

| 12-4. AC characteristics 1) (reference clock)                     |     |

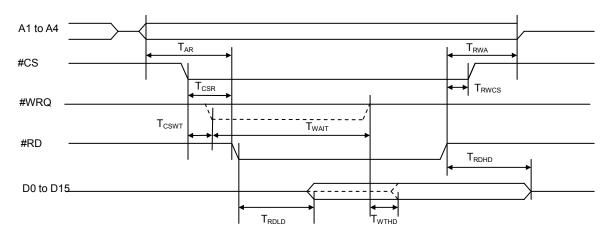

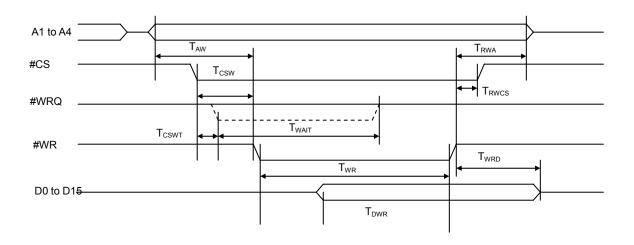

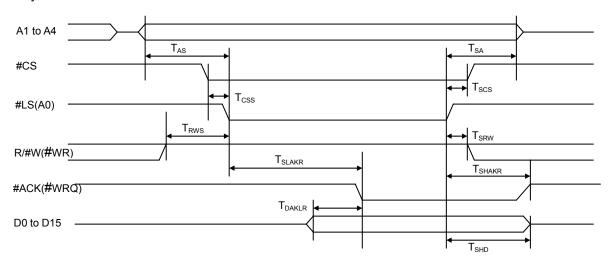

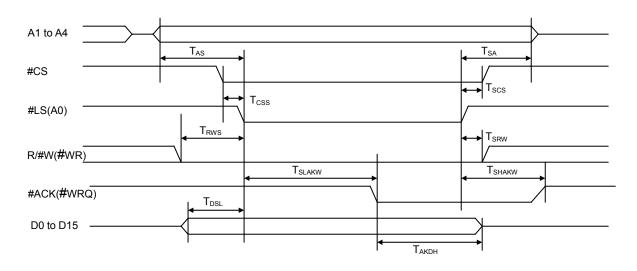

| 12-5. AC characteristics 2) (CPU- I/F)                            |     |

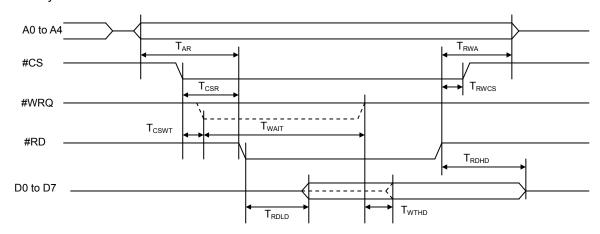

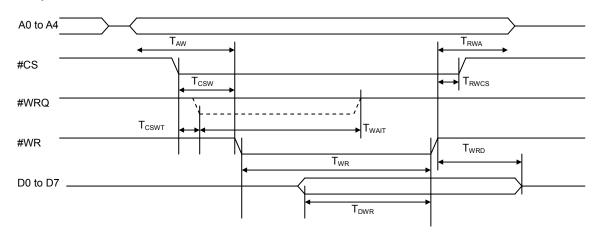

| 12-5-1. CPU-I/F 1) (IF1 = H, IF0 = H) Z80                         |     |

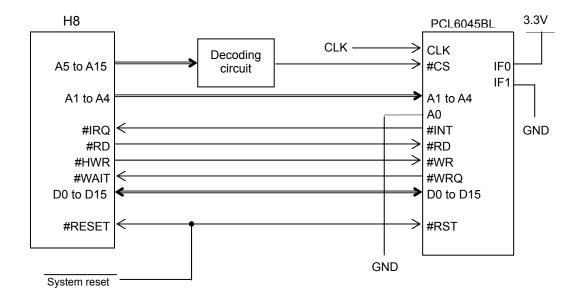

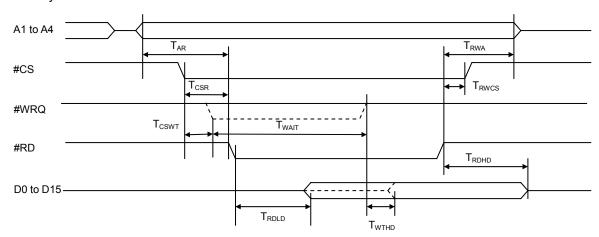

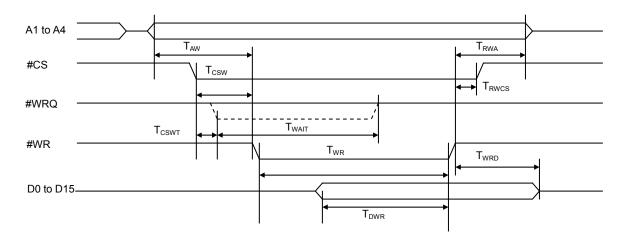

| 12-5-3. CPU-I/F 3) (IF1 = L, IF0 = L) H8                          | 150 |

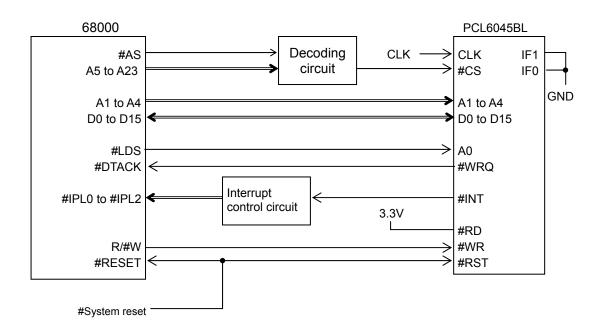

| 12-5-4. CPU-I/F 4) (IF1 = L, IF0 = L) 68000                       |     |

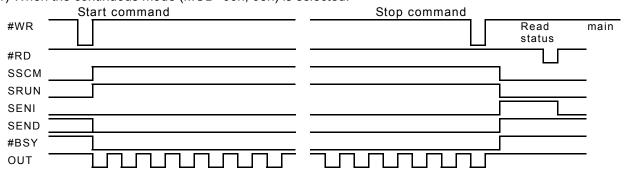

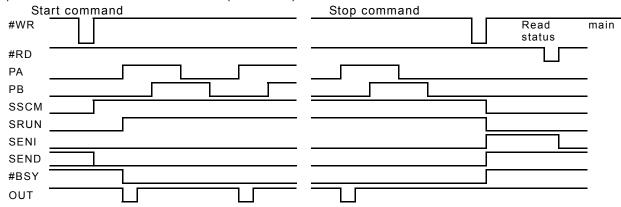

| 12-6. Operation timing                                            | 152 |

| 13. External Dimensions                                           | 154 |

| Appendix 1: List of commands                                      | 155 |

| Appendix 2: Setting speed pattern                                 | 158 |

| Appendix 3: Label list                                            |     |

| Appendix 4: Differences between the PCL6045 and PCL6045BL         |     |

| 4-1. How to identify the PCL6045 and PCL6045BL                    | 175 |

| 4-2. Difference in hardware                                       |     |

| 4-2-1. Package                                                    |     |

| 4-2-2. Power supply voltage                                       |     |

| 4-3. Difference in software                                       |     |

| 4-3-1. PRMD(RMD) register                                         |     |

| 4-3-2. RENV5 register                                             |     |

| 4-3-3. Control command                                            |     |

| 4-3-4. Register control command                                   | 176 |

| [Handling Precautions]                                            |     |

| 1. Design precautions                                             |     |

| Precautions for transporting and storing LSIs                     |     |

| 3. Precautions for installation                                   |     |

| 4. Other precautions                                              | 178 |

# 1. Outline and Features

### 1-1. Outline

The PCL6045BL is a CMOS LSI designed to provide the oscillating, high-speed pulses needed to drive stepper motors and servomotors (pulse string input types) using various commands.

It can offer various types of control over the pulse strings and therefore the motor performance. These include continuous feeding, positioning, and origin return, etc. at a constant speed, linear acceleration/deceleration, and S-curve acceleration/deceleration.

PCL6045BL is more user-friendly than PCL6045B because of adapting of 3.3V single power supply and JEDEC standard package, etc. Additionally, it is upward compatible in software.

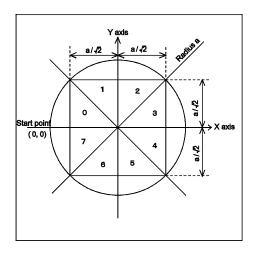

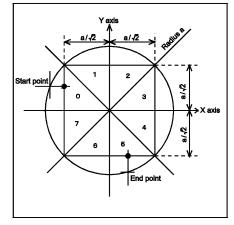

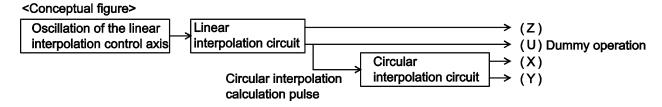

The PCL6045BL controls four axes. It can control the linear interpolation of two to four axes, circular interpolations between any two axes, confirm PCL operation status, and output an interrupt with various conditions. It also integrates an interface for servo motor drivers.

These functions can be used with simple commands. The intelligent design philosophy reduces the burden on the CPU units to control motors.

#### 1-2. Features

#### - CPU-I/F

The PCL6045BL contains the following CPU interface circuits.

- 1) 8-bit interface for Z80 CPU.

- 2) 16-bit interface for 8086 CPU.

- 3) 16-bit interface for H8 CPU.

- 4) 16-bit interface for 68000 CPU.

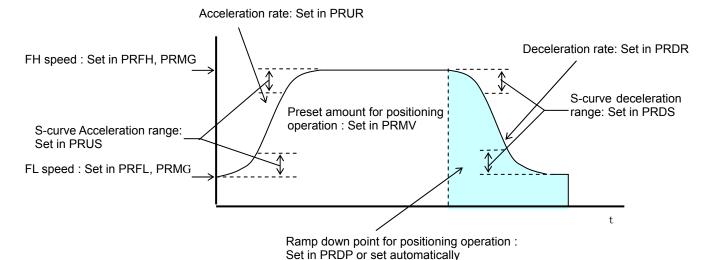

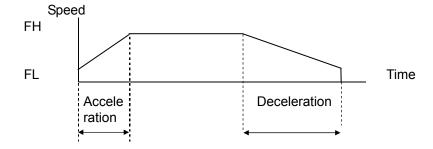

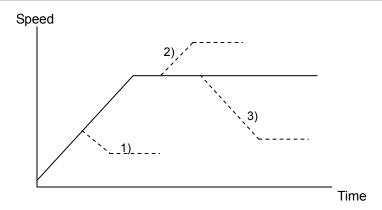

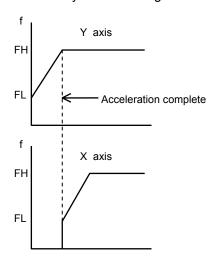

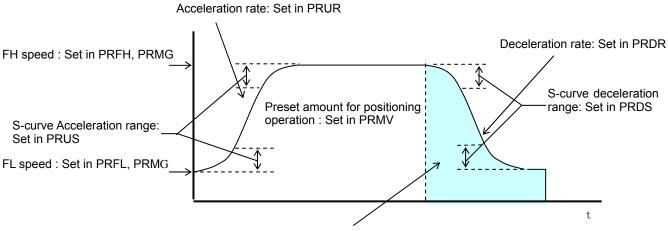

#### - Acceleration/Deceleration speed control

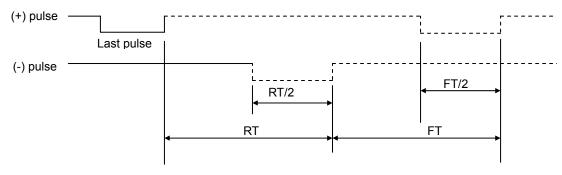

Linear acceleration/deceleration and S-curve acceleration/deceleration are available.

Linear acceleration/deceleration can be inserted in the middle of an S-curve acceleration/deceleration curve. (Specify the S-curve range.)

The S-curve range can specify each acceleration and deceleration independently. Therefore, you can create an acceleration/deceleration profile that consists of linear acceleration and S-curve deceleration, or vice versa.

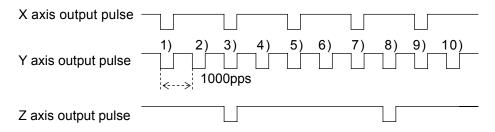

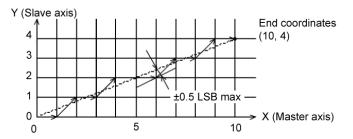

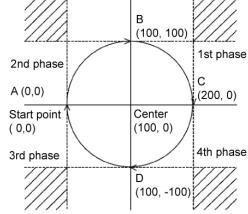

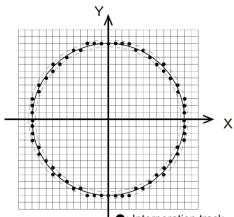

#### - Interpolation operation

Feeding with linear interpolation of any two to four axes and circular interpolation of any two axes are both possible.

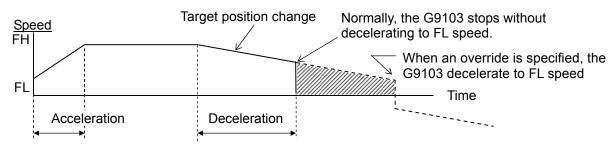

#### - Speed override

The feed speed can be changed in the middle of any feed operation.

However, the feed speed cannot be changed during operation when the synthesized speed constant control for linear interpolation is ON while using S-curve deceleration.

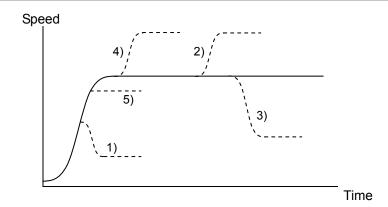

# - Overriding target position 1) and 2)

- 1) The target position (feed amount) can be changed while feeding in the positioning mode.

If the current position exceeds the newly entered position, the motor will decelerate, stop (immediate stop)

- when already feeding at a constant speed), and then feed in the reverse direction.

- 2) Starts operation like in the continuous mode and, when it receives an external signal, it will stop after outputting the specified number of pulses.

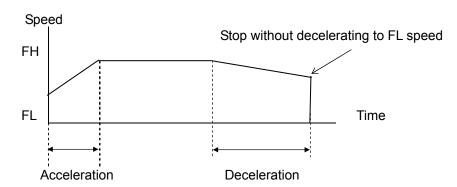

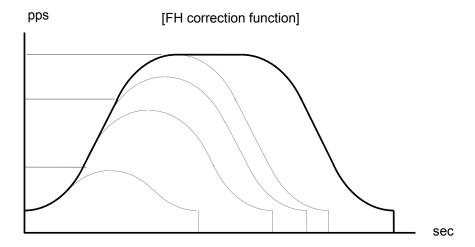

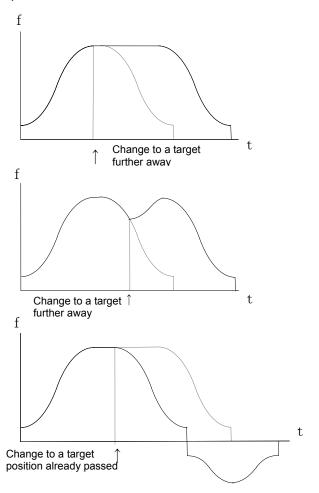

#### - Triangle drive elimination (FH correction function)

In the positioning mode, when there are a small number of output pulses, this function automatically lowers the maximum speed and eliminates triangle driving.

#### - Pre-register function

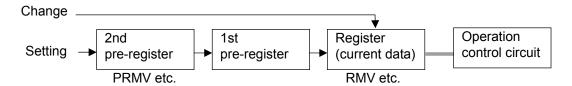

The next two sets of data (feed amount, initial speed, feed speed, acceleration rate, deceleration rate, speed magnification rate, ramping-down point, operation mode, center of circular interpolation, S-curve range on an acceleration, S-curve range on a deceleration, number of steps for circular interpolation) can be written while executing the current data. The next set of data, and other sets of data, can be written in advance of their execution for checking by the comparator.

When the current operation is complete, the system will immediately execute the next operation.

#### - A variety of counter circuits

The following four counters are available separately for each axis.

| Counter   | Use or purpose                                        | Counter Input                 |  |

|-----------|-------------------------------------------------------|-------------------------------|--|

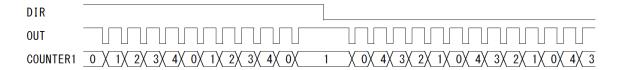

| COUNTER 1 | 28-bit counter for control of the command position    | Output pulses                 |  |

| COUNTER 2 | 28-bit counter for mechanical position control        | EA/EB input                   |  |

|           | (Can be used as a general-purpose counter)            | Output pulses                 |  |

|           |                                                       | PA/PB input                   |  |

| COUNTER 3 | 16-bit counter for controlling the deflection between | Output pulses and EA/EB input |  |

|           | the command position and the machine's current        | Output pulses and PA/PB input |  |

|           | position                                              | EA/EB input and PA/PB input   |  |

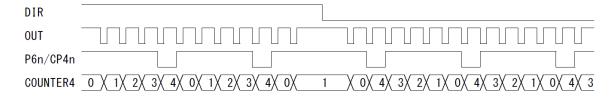

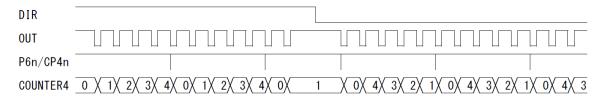

| COUNTER 4 | 28-bit counter used to output synchronous signals     | Output pulses                 |  |

|           | (Can be used as a general-purpose counter)            | EA/EB input                   |  |

|           |                                                       | PA/PB input                   |  |

|           |                                                       | 1/2 of reference clock        |  |

All counters can be reset by writing a command or by providing a CLR signal.

They can also be latched by writing a command, or by providing an LTC or ORG signal.

The PCL6045BL can also be set to reset automatically soon after latching these signals.

The COUNTER 1, COUNTER 2, and COUNTER 4 counters have a ring count function that repeats counting through a specified counting range.

#### - Comparator

There are five comparator circuits for each axis. They can be used to compare target values and internal counter values.

The counter to compare can be selected from COUNTER 1 (command position counter), COUNTER 2 (mechanical position counter), COUNTER 3 (deflection counter), and COUNTER 4 (a general-purpose counter).

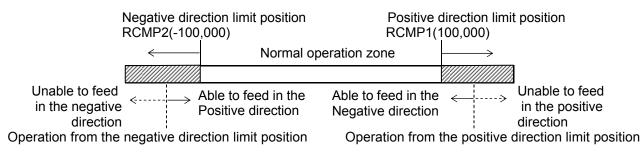

Comparators 1 and 2 can also be used as software limits (+SL, -SL).

#### - Software limit function

You can set software limits using two of the comparator's circuits.

When the mechanical position approaches the software limit range, the LSI will instruct the motors to stop immediately or to stop by deceleration. After that these axes can only be moved in the direction opposite to their previous travel.

#### - Backlash correction function / Slip correction function

Both the backlash and slip corrections are available. Backlash correction corrects the feed amount each time the feed direction is changed. Slip correction corrects the feed amount regardless of the feed direction. However, the backlash correction cannot be applied while performing a circular interpolation.

### - Synchronous signal output function

The LSI can output pulse signals for each specified rate interval.

#### - Simultaneous start function

Multiple axes controlled by the same LSI or multiple sets of this LSI, can be started at the same time by a command or an external signal.

#### - Simultaneous stop function

Multiple axes controlled by the same LSI or multiple sets of this LSI, can be stopped at the same time by a command, by an external signal, or by an error stop on any axis.

#### - Vibration restriction function

Specify a control constant in advance and add one pulse each for reverse and forward feed just before stopping.

Using this function, vibration can be decreased while stopping.

#### - Manual pulsar input function

By applying manual pulse signals (PA/PB), you can rotate a motor directly.

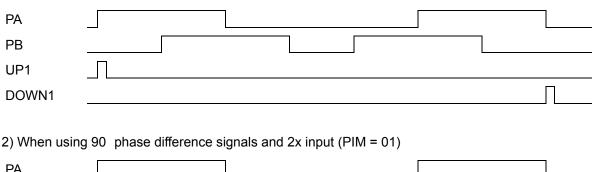

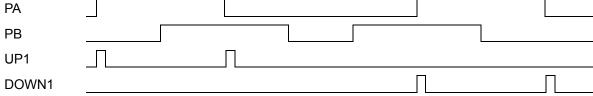

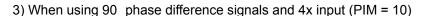

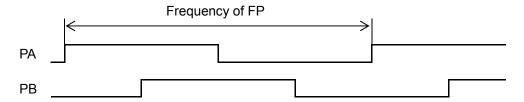

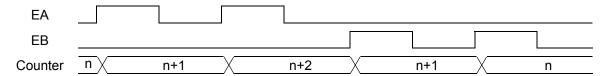

The input signals can be 90 phase difference signals (1x, 2x, or 4x) or up and down signals.

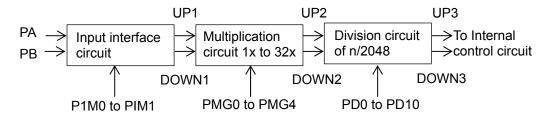

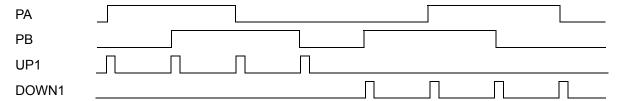

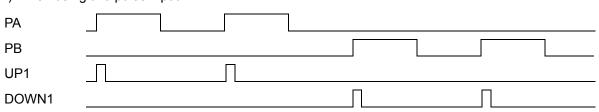

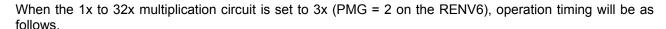

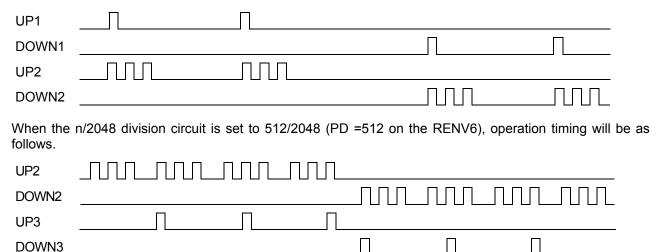

In addition to the magnification rates above, the PCL6045BL contains an integral pulse number magnification circuit which multiplies by 1x to 32x and a pulse quantity division circuit of (1 to 2048)/2048. Software limit settings can be used, and the PCL stops outputting pulses. It can also feed in the opposite direction.

#### - Direct input of operation switch

Positive and negative direction terminals (±DR) are provided to drive a motor with an external operation switch

These switches turn the motor forward (+) and backward (-).

#### - Out-of-step detection function

This LSI has a deflection counter which can be used to compare command pulses and encoder signals (EA/EB).

It can be used to detect out-of-step operation and to confirm a position by using a comparator.

#### - Idling pulse output function

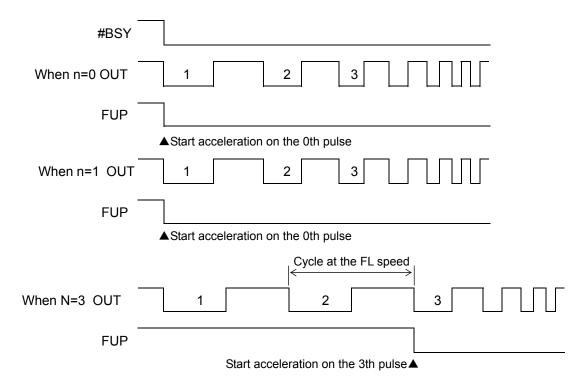

This function outputs a preset number of pulses at the initial speed (FL) before a high-speed start acceleration operation.

Even if a value near to the maximum starting pulse rate is set during acceleration, this function is effective in preventing out-of-step operation for stepper motors.

#### - Operation mode

The basic operations of this LSI are: continuous operation, positioning, origin return, linear interpolation, and circular interpolation. By setting the optional operation mode bits, you can use a variety of operations. <Examples of the operation modes>

- 1) Start/stop by command.

- 2) Continuous operation and positioning operation using PA/PB inputs (manual pulsar).

- 3) Operate for specified distances or in continuous operation using +DR/-DR signals (drive switch).

- 4) Origin return operation.

- 5) Positioning operation using commands.

- 6) Hardware start of the positioning operation using #CSTA input.

- 7) Change the target position after turning ON the PCS. (Delay control)

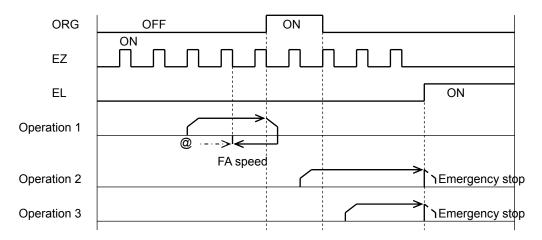

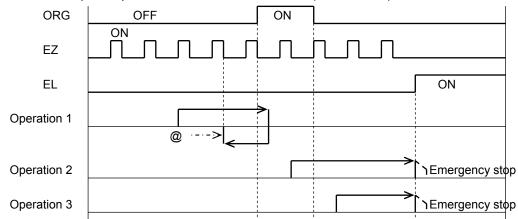

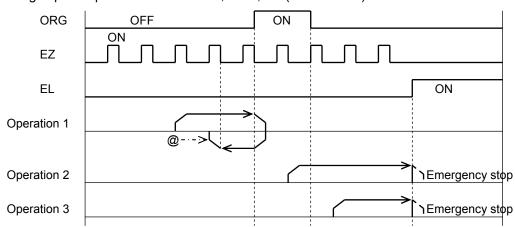

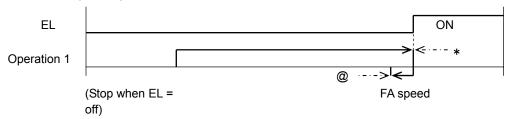

#### - Variety of origin return sequences (Homing)

The following patterns can be used.

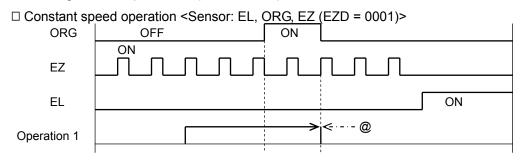

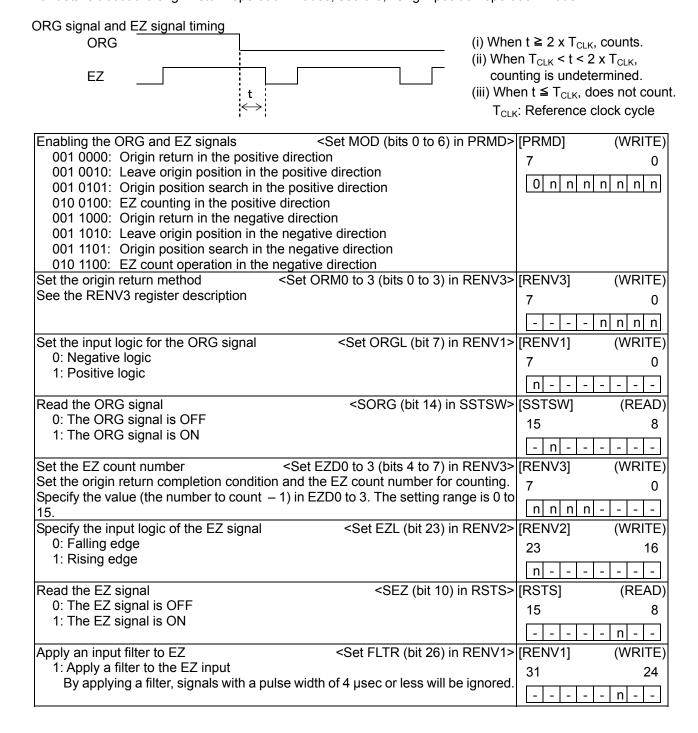

- 1) Feeds at constant speed and stops when the ORG signal is turned ON

- 2) Feeds at constant speed and stops when an EZ signal is received (after the ORG signal is turned ON).

- 3) Feeds at constant speed, reverses when the ORG signal is turned ON, and stops when an EZ signal is

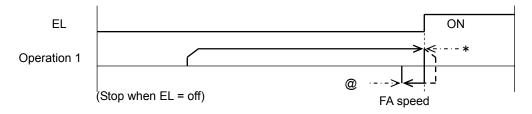

- 4) Feeds at constant speed and stops when the EL signal is turned ON. (Normal stop)

- 5) Feeds at constant speed, reverses when the EL signal is turned ON, and stops when an EZ signal is received.

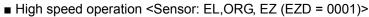

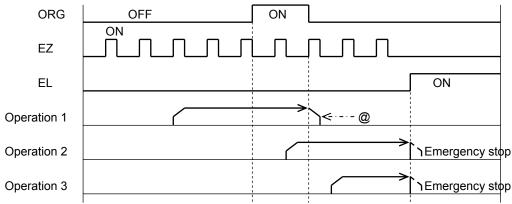

- 6) Feeds at high speed, decelerates when the SD signal is turned ON, and stops when the ORG signal is turned ON.

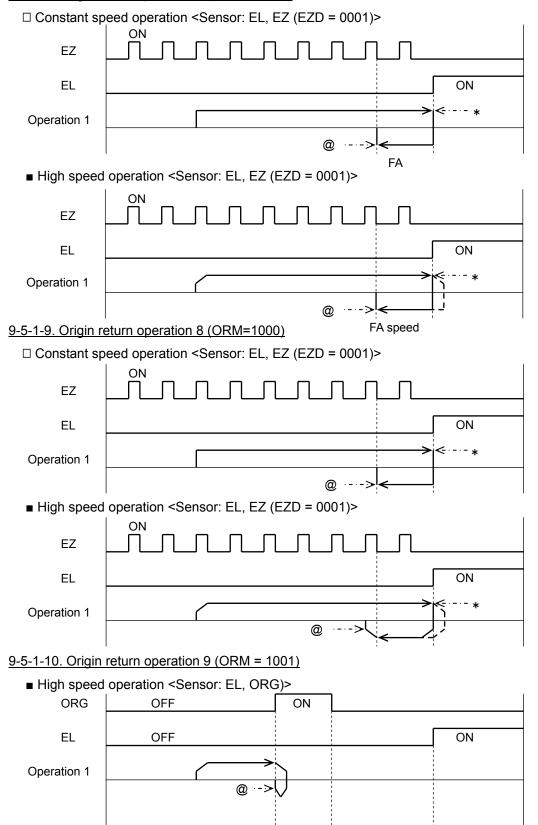

- 7) Feeds at high speed, decelerates when the ORG signal is turned ON, and stops when an EZ signal is received.

- 8) Feeds at high speed, decelerates and stops after the ORG signal is turned ON. Then, reverses to feed and stops when an EZ signal is received.

- 9) Feeds at high speed, decelerates and stops by memorizing the position when the ORG signal is turned ON, and stops at the memorized position.

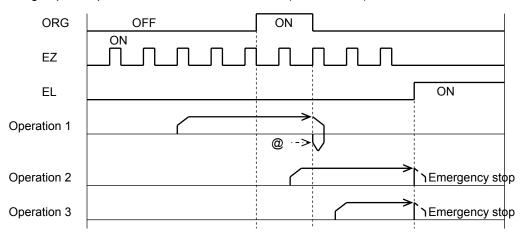

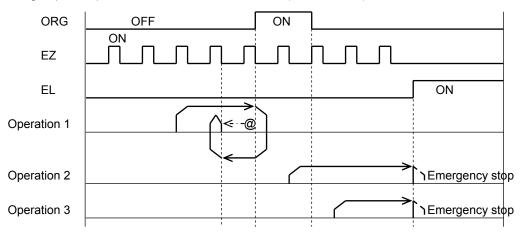

- 10)Feeds at high speed, decelerates to the position stored in memory when an EZ signal is received after the ORG signal is turned ON. Then, returns to the memorized position if an overrun occurs.

- 11)Feeds at high speed, reverses after a deceleration stop triggered by the EL signal, and stops when an EZ signal is received.

#### - Mechanical input signals

The following four signals can be input for each axis.

- 1)+EL: When this signal is turned ON, while feeding in the positive (+) direction, movement on this axis stops immediately (with deceleration). When this signal is ON, no further movement occurs on the axis in the positive (+) direction. (The motor can be rotated in the negative (-) direction.)

- 2)-EL: Functions the same as the +EL signal except that it works in the negative (-) direction.

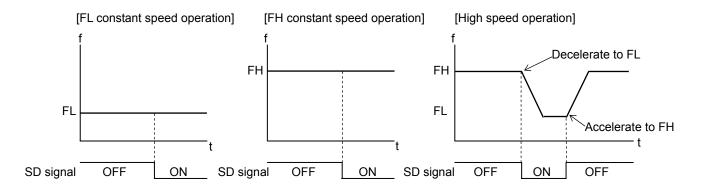

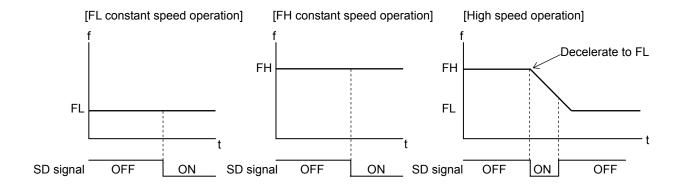

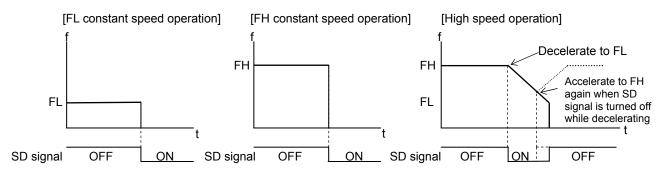

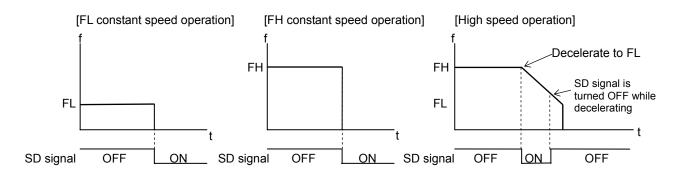

- 3)SD: This signal can be used as a deceleration signal or a deceleration stop signal, according to the software setting. When this is used as a deceleration signal, and when this signal is turned ON during a high speed feed operation, the motor on this axis will decelerate to the FL speed. If this signal is ON and movement on the axis is started, the motor on this axis will run at the FL constant speed. When this signal is used as a deceleration stop signal, and when this signal is turned ON during a high speed feed operation, the motor on this axis will decelerate to the FL speed and then stop.

- 4) ORG: Input signal for an origin return operation.

For safety, make sure the +EL and -EL signals stay on from the EL position until the end of each stroke. The input logic for these signals can be changed using the ELL terminal.

The input logic of the SD and ORG signals can be changed using software.

#### - Servomotor I/F

The following three signals can be used as an interface for each axis

1) INP: Input positioning complete signal that is output by a servomotor driver.

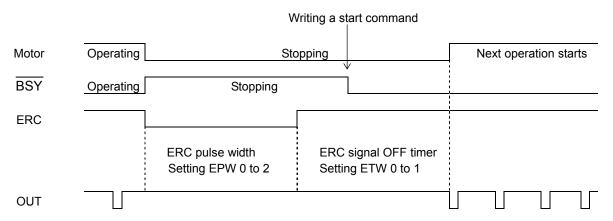

2)ERC: Output deflection counter clear signal to a servomotor driver.

3) ALM: Regardless of the direction of operation, when this signal is ON, movement on this axis stops immediately (deceleration stop). When this signal is ON, no movement can occur on this axis.

The input/output logic of the INP, ERC, and ALM signals can be changed using software.

The ERC signal is a pulsed output. The pulse length can be set. (12 µsec to 104 msec. A level output is also available.)

#### - Output pulse specifications

Output pulses can be set to a common pulse, Two-pulse mode or 90° phase difference mode. The output logic can also be selected.

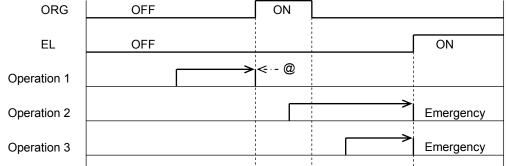

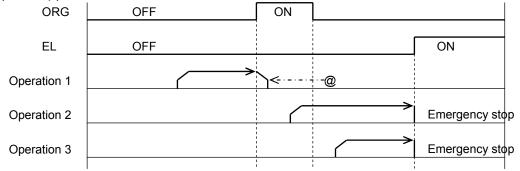

#### - Emergency stop signal (#CEMG) input

When this signal is turned ON, movement on both axes stops immediately. While this signal is ON, no movement is allowed on any axes.

#### - Interrupt signal output

An #INT signal (interrupt request) can be output for many reasons.

The #INT terminal output signal can use ORed logic for lots of conditions on each axis.

(When more than one 6045BL LSI is used, wired OR connections are not possible.)

# 2. Specifications

| Item                                        | Description                                                                                                                                                                      |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of axes                              | 4 axes (X, Y, Z, and U axis)                                                                                                                                                     |

| Reference clock                             | Standard: 19.6608 MHz (Max. 20 MHz)                                                                                                                                              |

| Positioning control range                   | -134,217,728 to +134,217,727 (28-bit)                                                                                                                                            |

| Ramping-down point setting range            | 0 to 16,777,215 (24-bit)                                                                                                                                                         |

| Number of registers used for setting speeds | Three for each axis (FL, FH, and FA (speed correction))                                                                                                                          |

| Speed setting step range                    | 1 to 65,535 (16-bits)                                                                                                                                                            |

| Speed magnification range                   | Multiply by 0.1 to 100  Multiply by 0.1 = 0.1 to 6,553.5 pps  Multiply by 1 = 1 to 65,535 pps  Multiply by 100 = 100 to 6,553,500 pps  (When the reference clock is 19.6608 MHz) |

| Acceleration/deceleration                   | Selectable acceleration/deceleration pattern for both increasing and decreasing                                                                                                  |

| characteristics                             | speed separately, using Linear and S-curve acceleration/deceleration.                                                                                                            |

| Acceleration rate setting range             | 1 to 65,535 (16-bit)                                                                                                                                                             |

| Deceleration rate setting range             | 1 to 65,535 (16-bit)                                                                                                                                                             |

| Ramping-down point automatic setting        | Automatic setting within the range of (deceleration time) < (acceleration time x 2)                                                                                              |

| Feed speed automatic correction function    | Automatically lowers the feed speed for short distance positioning moves.                                                                                                        |

| Manual operation input                      | Manual pulsar input, pushbutton switch input                                                                                                                                     |

| Counter                                     | COUNTER 1: Command position counter (28-bit)                                                                                                                                     |

|                                             | COUNTER 2: Mechanical position counter (28-bit)                                                                                                                                  |

|                                             | COUNTER 3: Deflection counter (16-bit)                                                                                                                                           |

|                                             | COUNTER 4: General-purpose counter (28-bit)                                                                                                                                      |

| Comparators                                 | 28-bits x 5 circuits / axis                                                                                                                                                      |

| Interpolation functions                     | Linear interpolation: Any 2 to 4 axes, Circular interpolation: Any 2 axes                                                                                                        |

| Operating temperature range                 | -40 to +85°C                                                                                                                                                                     |

| Power supply                                | Single power supply of 3.3 V±10%                                                                                                                                                 |

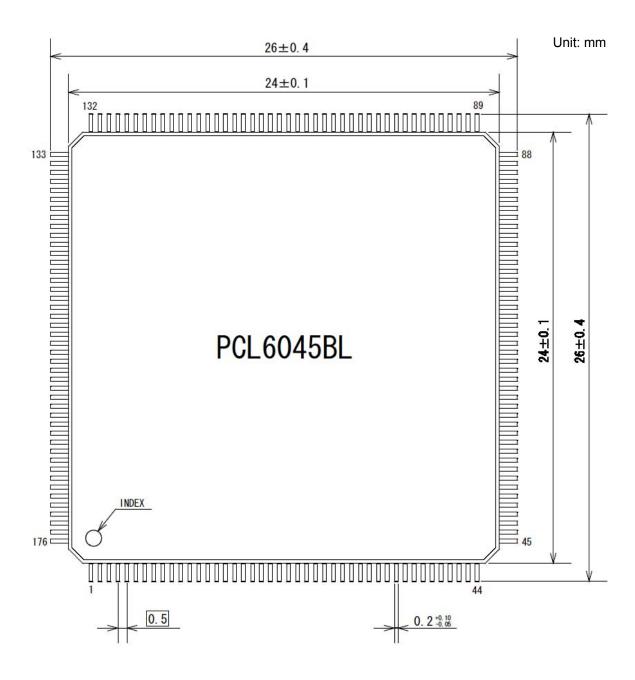

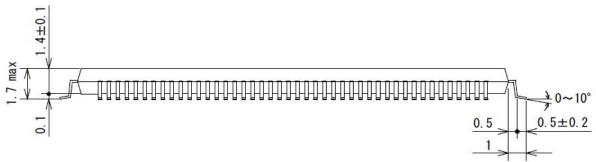

| Package                                     | 176-pin QFP                                                                                                                                                                      |

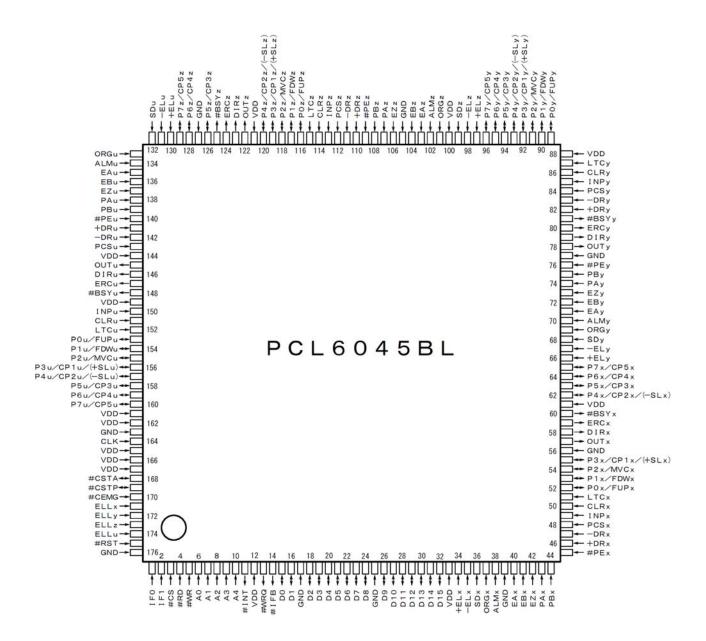

# 3. Terminal Assignment Diagram

Note: Pin number 1 is to the lower left of the LSI when you see the model name "PCL6045BL" marked on the chip at the front

# 4. Functions of Terminals

| Signal      | Terminal                                                                | •               | Logic    |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                        |                                                                                                                                                                  | Descri                                                                | ption                                                    |                                                   |                                                                               |

|-------------|-------------------------------------------------------------------------|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------|

| name<br>GND | No. 17,25,                                                              | output<br>Power |          | Supply                                                                                                                                                                                                                                                                                                                                                                                                                                       | a negat                                                                                                                | ive nower                                                                                                                                                        |                                                                       | •                                                        |                                                   |                                                                               |

| GND         | 39,56,<br>77,105,<br>127,163,<br>176                                    | source          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                              | Supply a negative power.  Make sure to connect all of these terminals.                                                 |                                                                                                                                                                  |                                                                       |                                                          |                                                   |                                                                               |

| VDD         | 12,33,<br>66,88,<br>100,121,<br>144,149,<br>161,162,<br>165,166,<br>167 | Power<br>source |          | The allo                                                                                                                                                                                                                                                                                                                                                                                                                                     | Supply +3.3 VDC power. The allowable power supply range is +3.3 VDC ±10%. Make sure to connect all of these terminals. |                                                                                                                                                                  |                                                                       |                                                          |                                                   |                                                                               |

| #RST        | 175                                                                     | Input           | Negative | Input reset signal.  Make sure to set this signal LOW after turning ON the power and before starting operation. Input at least 8 cycles of the reference clock while holding #RST low.  For details about the chip's status after a reset, see section 11-1, "Reset", in this manual.                                                                                                                                                        |                                                                                                                        |                                                                                                                                                                  |                                                                       |                                                          |                                                   |                                                                               |

| CLK         | 164                                                                     | Input           |          | The refe                                                                                                                                                                                                                                                                                                                                                                                                                                     | erence (                                                                                                               |                                                                                                                                                                  | ency is 1                                                             | k signal.<br>9.6608 MH<br>aput on this                   |                                                   |                                                                               |

| IF0         | 1                                                                       | Input           |          | Enter th                                                                                                                                                                                                                                                                                                                                                                                                                                     | e CPU-                                                                                                                 | I/F mode                                                                                                                                                         |                                                                       | •                                                        |                                                   |                                                                               |

| IF1         | 2                                                                       |                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                              | IFO                                                                                                                    | CPU                                                                                                                                                              | CPU:                                                                  | signal conne                                             | ected to the                                      | e terminal                                                                    |

|             |                                                                         |                 |          | IF1                                                                                                                                                                                                                                                                                                                                                                                                                                          | IF0                                                                                                                    | example                                                                                                                                                          | #RD                                                                   | #WR                                                      | A0                                                | #WRQ                                                                          |

|             |                                                                         |                 |          | L L                                                                                                                                                                                                                                                                                                                                                                                                                                          | L                                                                                                                      | 68000                                                                                                                                                            | VDD                                                                   | R/#W                                                     | #LDS                                              | #DTACK                                                                        |

|             |                                                                         |                 |          | H H                                                                                                                                                                                                                                                                                                                                                                                                                                          | H<br>L                                                                                                                 | H8<br>8086                                                                                                                                                       | #RD<br>#RD                                                            | #HWR<br>#WR                                              | (GND)<br>(GND)                                    | #WAIT<br>READY                                                                |

|             |                                                                         |                 |          | Н                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                      | Z80                                                                                                                                                              | #RD                                                                   | #WR                                                      | A0                                                | #WAIT                                                                         |

| #CS         | 3                                                                       | Input           | Negative | When the                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |                                                                                                                                                                  | his termi                                                             | nal is LOW                                               | /, the #R[                                        | and #WR                                                                       |

| #RD<br>#WR  | 4<br>5                                                                  | Input           | Negative |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                        | I/F termina<br>#CS termi                                                                                                                                         |                                                                       |                                                          | RD and #                                          | WR terminals                                                                  |

| A0 to A4    | 6 to 10                                                                 | Input           | Positive |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                        | l signals                                                                                                                                                        |                                                                       |                                                          |                                                   |                                                                               |

| #INT        | 11                                                                      | Output          | Negative | Outputs an interrupt request signal (IRQ) to an external CPU. After this terminal is turned ON, the signal will return to OFF when a REST (error interrupt cause) or RIST (event interrupt cause) signal is received. The output status can be checked with an MSTSW (main status) command signal. The #INT output signal can be masked. When more than one 6045BL LSI is used, a wired OR connection between #INT terminals is not allowed. |                                                                                                                        |                                                                                                                                                                  |                                                                       |                                                          |                                                   |                                                                               |

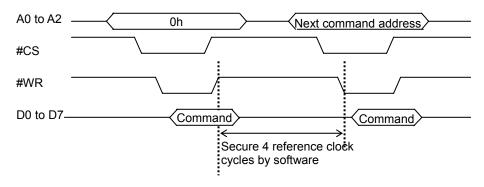

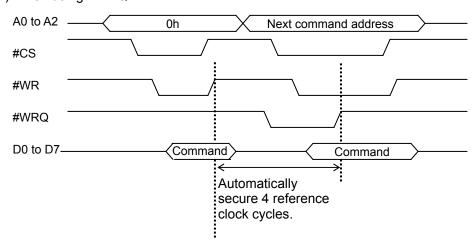

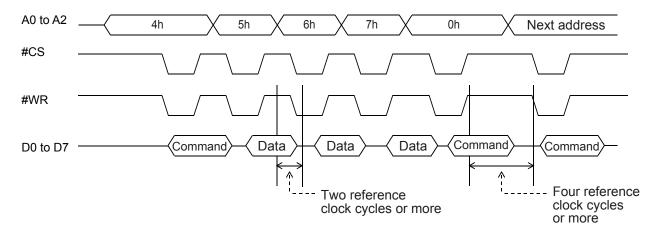

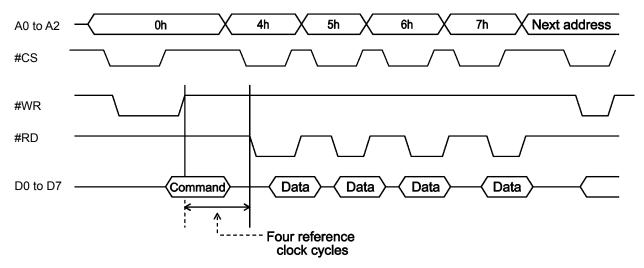

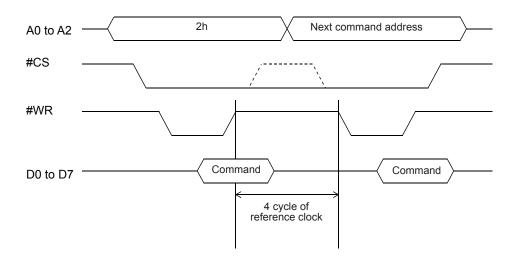

| #WRQ        | 13                                                                      | Output          | Negative | Outputs a wait request signal to cause a CPU to wait. The LSI needs 4 reference clock cycles to process each command. If the #WRQ signal is not used, make sure that an external CPU does not access this LSI during this interval.                                                                                                                                                                                                          |                                                                                                                        |                                                                                                                                                                  |                                                                       |                                                          |                                                   |                                                                               |

| #IFB        | 14                                                                      | Output          | Negative | Signal u<br>Use this<br>a wait c<br>When the<br>go LOW<br>The LSI                                                                                                                                                                                                                                                                                                                                                                            | used to<br>s signal<br>ontrol ir<br>ne LSI ro<br>/. When<br>makes                                                      | ndicate that to make con termine termine ceives a value the LSI fin sure that the termine ceives and the LSI fin the that the the the the the the the the the th | at the LS<br>onnection<br>al.<br>vrite com<br>ishes pro<br>his termin | I is process<br>as with a C<br>mand from<br>acessing, th | PU that d<br>a CPU, t<br>nis signal<br>I and ther | mands.<br>loes not have<br>this signal will<br>will go HIGH.<br>n proceeds to |

| Signal name                      | Terminal<br>No.          | Input/<br>output  | Logic      | Description                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|--------------------------|-------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 to D7                         | 15 to 16,<br>18 to 23    | Input/            | Positive   | Bi-directional data bus. When connecting a 16-bit data bus, connect the lower 8 signal lines here.                                                                                                                                                                                                                                          |

| D8 to D15                        | 24,<br>26 to 32          | Input/<br>Output  | Positive   | Bi-directional data bus. When connecting a 16-bit data bus, connect the upper 8 signal lines here. When a Z80-I/F (IF1 = H, IF0 = H) is used, provide a pull up resistor (5k to 10 K-ohms) on VDD. (One resistor can be used for all 8 lines.)                                                                                              |

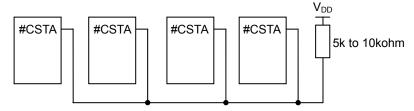

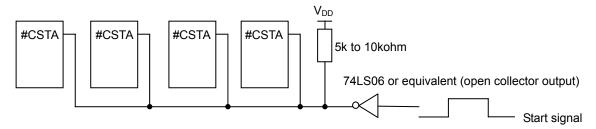

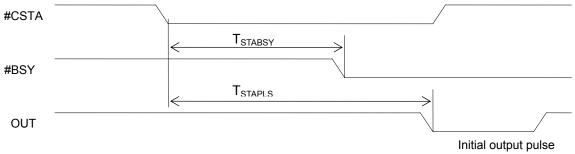

| #CSTA                            | 168                      | Input/<br>Output* | Negative   | Input/Output terminal for simultaneous start. When more than one LSI is used and you want to start them simultaneously, connect this terminal on each LSI. The terminal status can be checked using an RSTS command signal (extension status).                                                                                              |

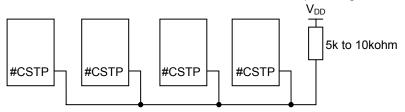

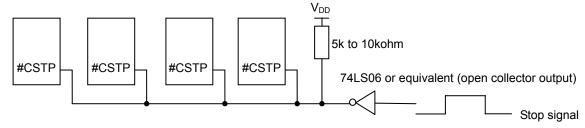

| #CSTP                            | 169                      | Input/<br>Output* | Negative   | Input/Output terminal for a simultaneous stop. (See Note 6.) When more than one LSI is used and you want to stop them simultaneously, connect this terminal on each LSI. The terminal status can be checked using an RSTS command signal (extension status).                                                                                |

| #CEMG                            | 170                      | Input U           | Negative   | Input for an emergency stop. While this signal is LOW, motion cannot start. If this signal changes to LOW while in operation, all the motors will stop operation immediately.                                                                                                                                                               |

| ELLx<br>ELLy<br>ELLz<br>ELLu     | 171<br>172<br>173<br>174 | Input U           |            | Specify the input logic for the ±EL signal. LOW: The input logic on ±EL is positive. HIGH: The input logic on ±EL is negative.                                                                                                                                                                                                              |

| + ELx<br>+ ELy<br>+ ELz<br>+ ELu | 34<br>66<br>97<br>130    | Input U           | Negative%  | Input end limit signal in the positive (+) direction. (See Note 6.) When this signal is ON while feeding in the positive (+) direction, motion of an axis will stop immediately or will decelerate and stop. Specify the input logic using the ELL terminal. The terminal status can be checked using an SSTSW command signal (sub status). |

| - ELx<br>- ELy<br>- ELz<br>- ELu | 35<br>67<br>98<br>131    | Input U           | Negative%  | Input end limit signal in the negative (-) direction. (See Note 6.) When this signal is ON while feeding in negative (-) direction, motion of an axis will stop immediately, or will decelerate and stop. Specify the input logic using the ELL terminal. The terminal status can be checked using an SSTSW command signal (sub status).    |

| SDx<br>SDy<br>SDz<br>SDu         | 36<br>68<br>99<br>132    | Input U           | Negative#  | Input deceleration (deceleration stop) signal. Selects the input method: LEVEL or LATCHED inputs. The input logic can be selected using software. The terminal status can be checked using an SSTSW command signal (sub status).                                                                                                            |

| ORGx<br>ORGy<br>ORGz<br>ORGu     | 37<br>69<br>101<br>133   | Input U           | Negative # | Used for origin position operations. (Edge detection.) The input logic can be selected using software. The terminal status can be checked using an SSTSW command signal (sub status).                                                                                                                                                       |

| ALMX<br>ALMy<br>ALMz<br>ALMu     | 38<br>70<br>102<br>134   | Input U           | Negative # | Input alarm signal. (See Note 6.) When this signal is ON, motion of an axis stops immediately, or will decelerate and stop. The input logic can be selected using software. The terminal status can be checked using an SSTSW command signal (sub status).                                                                                  |

| Signal            | Terminal       | Input/  |              | 5                                                                                                                                        |

|-------------------|----------------|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

| name              | No.            | output  | Logic        | Description                                                                                                                              |