# ERES35104HR

PCI Express Dual Synchro/Resolver/LVDT Interface

# User's Manual

BDM-610020108 Rev. D

**RTD Embedded Technologies, Inc.**

103 Innovation Boulevard State College, PA 16803 USA Telephone: 814-234-8087 Fax: 814-234-5218

www.rtd.com

sales@rtd.com techsupport@rtd.com

# **Revision History** Initial Dalaga

| Rev A | Initial Release                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev B | Corrected Section 7.2.3 on page 26.                                                                                                                                                         |

| Rev C | Changed "Channel 1 and 2" to "Channel 0 and 1". Corrected description in Section 7.3.2 on page 28. Added Resolution for each Bandwidth Filter in Table 6 on page 18.                        |

| Rev D | Corrected Subsystem ID Offsets in Table 23 on page 26. Updated External Reference Jumper Settings in Table 20 and Table 22 on page 25. Define Excitation Amplitudes in Table 30 on page 33. |

|       |                                                                                                                                                                                             |

|       |                                                                                                                                                                                             |

Advanced Analog I/O, Advanced Digital I/O, aAIO, aDIO, a2DIO, Autonomous SmartCal, "Catch the Express", cpuModule, dspFramework, dspModule, expressMate, ExpressPlatform, HiDANplus, "MIL Value for COTS prices", multiPort, PlatformBus, and PC/104EZ are trademarks, and "Accessing the Analog World", dataModule, IDAN, HIDAN, RTD, and the RTD logo are registered trademarks of RTD Embedded Technologies, Inc (formerly Real Time Devices, Inc.). PS/2 is a trademark of International Business Machines Inc. PCI, PCI Express, and PCIe are trademarks of PCI-SIG. PC/104.PLus, PCI-104, PCIe/104, PCIe/104, PCI/104-Express and 104 are trademarks of the PC/104 Embedded Consortium. All other trademarks appearing in this document are the property of their respective owners.

Failure to follow the instructions found in this manual may result in damage to the product described in this manual, or other components of the system. The procedure set forth in this manual shall only be performed by persons qualified to service electronic equipment. Contents and specifications within this manual are given without warranty, and are subject to change without notice. RTD Embedded Technologies, Inc. shall not be liable for errors or omissions in this manual, or for any loss, damage, or injury in connection with the use of this manual.

Copyright © 2014 by RTD Embedded Technologies, Inc. All rights reserved.

# Table of Contents

| 1 | Introduction | ion                                                                                                                                                                                                                     | 7                          |

|---|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1          | Product Overview                                                                                                                                                                                                        | 7                          |

|   | 1.2          | Board Features                                                                                                                                                                                                          | 7                          |

|   | 1.3          | Ordering Information                                                                                                                                                                                                    | 7                          |

|   | 1.4          | Contact Information<br>1.4.1 Sales Support<br>1.4.2 Technical Support                                                                                                                                                   |                            |

| 2 | Specificat   | tions                                                                                                                                                                                                                   | 9                          |

|   | 2.1          | Operating Conditions                                                                                                                                                                                                    | 9                          |

|   | 2.2          | Electrical Characteristics                                                                                                                                                                                              | 9                          |

| 3 | Board Cor    | nnection                                                                                                                                                                                                                | 10                         |

|   | 3.1          | Board Handling Precautions                                                                                                                                                                                              | 10                         |

|   | 3.2          | Physical Characteristics                                                                                                                                                                                                | 10                         |

|   | 3.3          | Connectors and Jumpers                                                                                                                                                                                                  | 11                         |

|   |              | <ul> <li>3.3.1 External I/O Connectors <ul> <li>J1: Sensor Input / Output</li> </ul> </li> <li>3.3.2 Bus Connectors <ul> <li>CN1 (Top) &amp; CN2 (Bottom): PCIe Connector</li> <li>3.3.3 Jumpers</li> </ul> </li> </ul> | 11<br>11<br>12<br>12<br>12 |

|   | 3.4          | Steps for Installing                                                                                                                                                                                                    | 13                         |

| 4 | IDAN Con     | nections                                                                                                                                                                                                                | 14                         |

|   | 4.1          | Module Handling Precautions                                                                                                                                                                                             |                            |

|   | 4.2          | Physical Characteristics                                                                                                                                                                                                | 14                         |

|   | 4.3          | Connectors<br>4.3.1 External I/O Connectors<br>Sensor Input / Output<br>4.3.2 Bus Connectors<br>CN1 (Top) & CN2 (Bottom): PCIe Connector                                                                                |                            |

|   | 4.4          | Steps for Installing                                                                                                                                                                                                    | 16                         |

| 5 | Functiona    | al Description                                                                                                                                                                                                          | 17                         |

|   | 5.1          | Block Diagram                                                                                                                                                                                                           | 17                         |

|   | 5.2          | PCIe Switch                                                                                                                                                                                                             | 17                         |

|   | 5.3          | Resolver to Digital Converter<br>5.3.1 Bandwidth Filters                                                                                                                                                                | 17<br>18                   |

|   | 5.4          | Front End                                                                                                                                                                                                               | 18                         |

|   | 5.5          | On-Board Excitation                                                                                                                                                                                                     | 18                         |

|   | 5.6          | EPLD                                                                                                                                                                                                                    |                            |

| 6 | Board Cor    | nfiguration                                                                                                                                                                                                             | 19                         |

|   | 6.1          | Sensor Input Connections<br>6.1.1 Resolver Input<br>Input Connections<br>Jumper Configuration<br>6.1.2 Synchro Input<br>Input Connections<br>Jumper Configuration<br>6.1.3 2-Wire LVDT Input                            |                            |

|    |               | Input Connections<br>Jumper Configuration<br>6.1.4 3-Wire LVDT Input<br>Input Connections<br>Jumper Configuration<br>6.1.5 Direct Input<br>Input Connections<br>Jumper Configuration                                                                                                                                                                                                                                                                                   | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>23<br>23                               |

|----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|    | 6.2           | Reference Input         6.2.1       Internally Generated Reference         Connections         Jumper Configuration         6.2.2       Differential Externally Generated Reference         Connections         Jumper Configuration         6.2.3       Single-Ended Externally Generated Reference         Connections         Jumper Configuration         6.2.3       Single-Ended Externally Generated Reference         Connections         Jumper Configuration | 24<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25                                     |

| 7  | Register Ad   | ddress Space                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                           |

|    | 7.1           | Identifying the Board                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|    | 7.2           | Index and Data Registers         7.2.1       GPIOAB_CTRL (Read/Write)         7.2.2       GPIOCD_CTRL (Read/Write)         7.2.3       SELECT (Read/Write)         7.2.4       INDEX_DATA (Read/Write)                                                                                                                                                                                                                                                                 |                                                                                              |

|    | 7.3           | Accessing the Board Registers         7.3.1       Reading from a Board Register         7.3.2       Writing to a Board Register         7.3.3       Reading Shift Register Status                                                                                                                                                                                                                                                                                      |                                                                                              |

|    | 7.4           | Board Registers         7.4.1       BUILD_NUM_LS, BUILD_NUM_MS (Read-Only)         7.4.2       SR_SELECT (Read/Write)         7.4.3       SR_DATA_OUT (Read/Write)         7.4.4       SR_DATA_IN (Read-Only)         7.4.5       CHx_SETUP_STATUS (Read/Write, Read-Only)         7.4.6       CHx_POSITION (Read-Only)                                                                                                                                                |                                                                                              |

|    | 7.5           | <ul> <li>Shift Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31<br>31<br>31<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33 |

| 8  | Troubleshoe   | poting                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                           |

| 9  | Additional lu | Information                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                           |

|    | 9.1           | PC/104 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|    | 9.2           | PCI and PCI Express Specification                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 10 | Limited War   | arranty                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                                                                                           |

# Table of Figures

| Figure 1: Board Dimensions        |    |

|-----------------------------------|----|

| Figure 2: Board Connections       |    |

| Figure 3: Jumper Locations        | 12 |

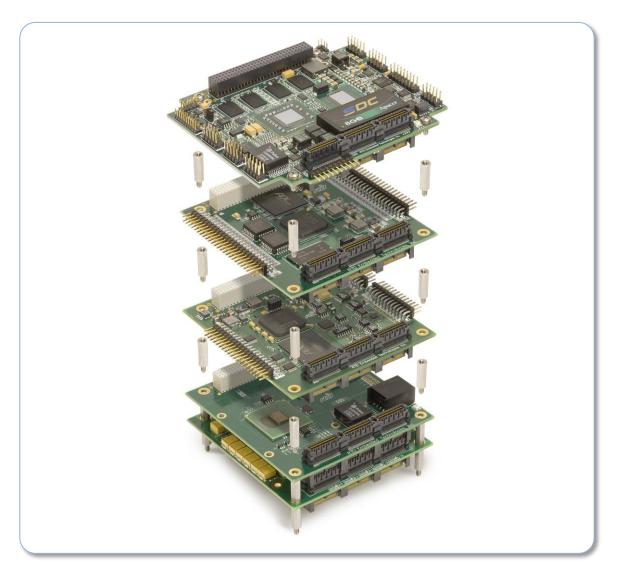

| Figure 4: Example 104™Stack       | 13 |

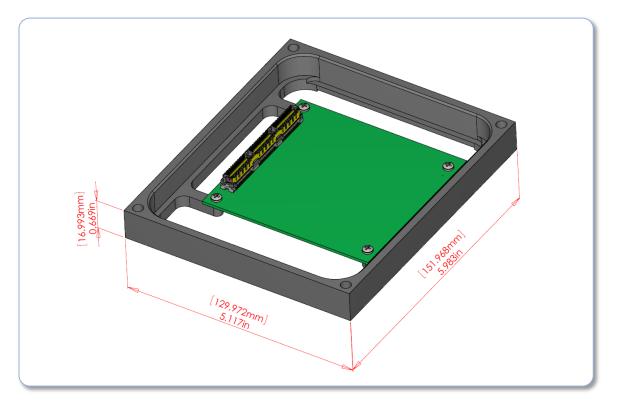

| Figure 5: IDAN Dimensions         |    |

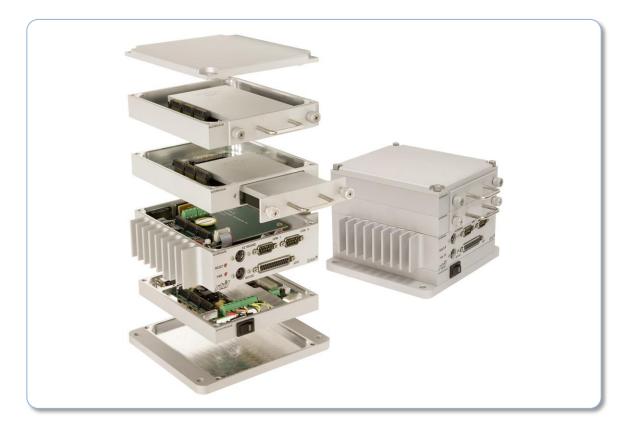

| Figure 6: Example IDAN System     | 16 |

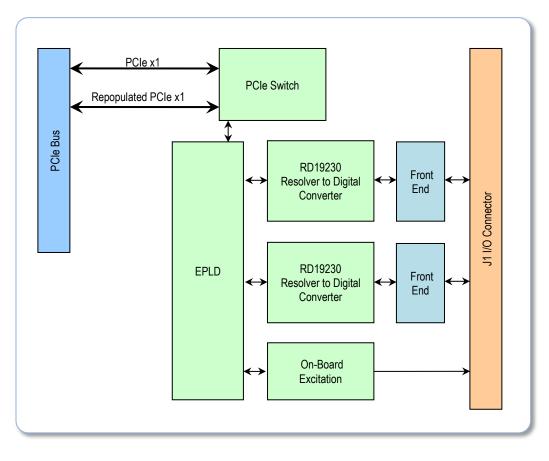

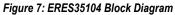

| Figure 7: ERES35104 Block Diagram | 17 |

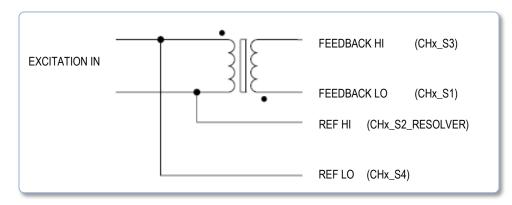

| Figure 8: 2-Wire LVDT Schematic   | 21 |

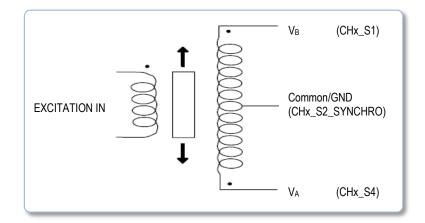

| Figure 9: 3-Wire LVDT Schematic   | 22 |

# Table of Tables

| Table 1: Ordering Options                                 | 7  |

|-----------------------------------------------------------|----|

| Table 2: Operating Conditions                             | 9  |

| Table 3: Electrical Characteristics                       |    |

| Table 4: J1 Input / Output Pin Assignments 1              | 1  |

| Table 5: IDAN Input / Output Pin Assignments 1            |    |

| Table 6: Bandwidth Filters                                | 8  |

| Table 7: Resolver Input Connections 1                     | 9  |

| Table 8: Resolver Jumper Settings 1                       | 9  |

| Table 9: Synchro Input Connections                        | 0  |

| Table 10: Synchro Jumper Settings                         | .0 |

| Table 11: 2-Wire LVDT Input Connections                   |    |

| Table 12: 2-Wire LVDT Jumper Settings 2                   | 1  |

| Table 13: 3-Wire LVDT Input Connections                   | 2  |

| Table 14: 3-Wire LVDT Jumper Settings                     | 2  |

| Table 15: Direct Input Connections                        | 3  |

| Table 16: Direct Input Jumper Settings                    | 3  |

| Table 17: Internal Reference Connections                  |    |

| Table 18: Internal Reference Jumper Settings              | 4  |

| Table 19: Differential External Reference Connections     |    |

| Table 20: Differential External Reference Jumper Settings | 5  |

| Table 21: Single-Ended External Reference Connections     |    |

| Table 22: Single-Ended External Reference Jumper Settings | 5  |

| Table 23: Identifying the ERES35104 2                     |    |

| Table 24: Index and Data Registers                        | .6 |

| Table 25: Board Registers                                 |    |

| Table 26: Channel Mode Shift Register                     | 1  |

| Table 27: Channel Modes                                   |    |

| Table 28: Velocity Trim Shift Register                    | 2  |

| Table 29: Excitation Amplitude Shift Register             | 3  |

| Table 30: Excitation Amplitude Values                     | .3 |

# 1 Introduction

# 1.1 **Product Overview**

The ERES35104 provides a direct interface to two Synchro/Resolver/LVDT channels on the compact PC/104 form factor with a stackable PCI Express bus. Both sensor input channels are independently configurable with jumpers. An onboard solid state Scott-T circuitry provides a precision conversion from Synchro to Resolver signals. Onboard precision thin-film resistor divider networks for 2.0, 11.8 or 90.0 V<sub>RMS</sub> configurations.

The onboard programmable sine wave oscillator reference outputs a 0 - 7V<sub>RMS</sub> excitation signal with a programmable frequency range of 0 Hz to 10 kHz.

# 1.2 Board Features

- PC/104 form factor

- PCIe/104 stackable bus structure

- PCIe/104 Universal Connector

- o Uses a PCIe x1 link

- Repopulates the PCIe bus

- 2 Independent Channels

- Directly interfaces to Synchros, Resolvers and LVDTs

- Connection to 2.0V/11.8V/90.0V sensors

- Programmable resolution 10/12/14/16 bits

- +5V only operation

- Programmable sine wave excitation

- o 0 Hz to 10 kHz frequency range

- $\circ$  0V to 7V<sub>RMS</sub> voltage range

- Up to 100mA drive current at 85C

- Dual software selectable filters can be changed on-the-fly

- High Resolution mode for 16-bit resolution

- High Velocity mode for tracking rate up to 320 rps

- Other filter options available

- Synthesized reference corrects for phase shift up to 45 degrees

- Loss of signal detection

- Single-ended or Differential Inputs

- PCI Express (PCIe) x1 Upstream Interface to CPU

# 1.3 Ordering Information

The ERES35104 is available with the following options:

#### **Table 1: Ordering Options**

| Part Number          | Description                                                                                                 |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| ERES35104HR-1        | PCIe/104 Two-Channel, 11.8 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module                   |

| ERES35104HR-2        | PCIe/104 Two-Channel, 90.0 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module                   |

| ERES35104HR-3        | PCIe/104 Two-Channel, 2.0 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module                    |

| IDAN- ERES35104HR-1S | PCIe/104 Two-Channel, 11.8 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module in IDAN enclosure |

| IDAN- ERES35104HR-2S | PCIe/104 Two-Channel, 90.0 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module in IDAN enclosure |

| IDAN- ERES35104HR-3S | PCIe/104 Two-Channel, 2.0 V <sub>RMS</sub> Synchro/Resolver to Digital Peripheral Module in IDAN enclosure  |

The Intelligent Data Acquisition Node (IDAN<sup>™</sup>) building block can be used in just about any combination with other IDAN building blocks to create a simple but rugged 104<sup>™</sup> stack. This module can also be incorporated in a custom-built RTD HiDAN<sup>™</sup> or HiDANplus High Reliability Intelligent Data Acquisition Node. Contact RTD sales for more information on our high reliability systems.

# 1.4 **Contact Information**

## 1.4.1 SALES SUPPORT

For sales inquiries, you can contact RTD Embedded Technologies sales via the following methods:

Phone: 1-814-234-8087 Monday through Friday, 8:00am to 5:00pm (EST). E-Mail: sales@rtd.com

## 1.4.2 TECHNICAL SUPPORT

If you are having problems with you system, please try the steps in the Troubleshooting section of this manual on page 26.

For help with this product, or any other product made by RTD, you can contact RTD Embedded Technologies technical support via the following methods:

Phone: 1-814-234-8087 Monday through Friday, 8:00am to 5:00pm (EST). E-Mail: techsupport@rtd.com

# 2 Specifications

# 2.1 **Operating Conditions**

### **Table 2: Operating Conditions**

| Symbol            | Parameter                | Test Condition                                       | Min  | Max  | Unit  |

|-------------------|--------------------------|------------------------------------------------------|------|------|-------|

| V <sub>cc5</sub>  | 5V Supply Voltage        |                                                      | 4.75 | 5.25 | V     |

| V <sub>cc3</sub>  | 3.3V Supply Voltage      |                                                      | n/a  | n/a  | V     |

| V <sub>cc12</sub> | 12V Supply Voltage       |                                                      | n/a  | n/a  | V     |

| Vcc-12            | -12V Supply Voltage      |                                                      | n/a  | n/a  | V     |

| Ta                | Operating Temperature    |                                                      | -40  | +85  | С     |

| Ts                | Storage Temperature      |                                                      | -55  | +125 | С     |

| RH                | Relative Humidity        | Non-Condensing                                       | 0    | 90%  | %     |

| MTBF              | Mean Time Before Failure | Telcordia Issue 2<br>30°C, Ground benign, controlled |      | TBD  | Hours |

# 2.2 Electrical Characteristics

| Symbol                                | Parameter                        | Test Condition              | Min   | Max   | Unit              |  |  |  |  |

|---------------------------------------|----------------------------------|-----------------------------|-------|-------|-------------------|--|--|--|--|

| P                                     | Power Consumption                | V <sub>cc5</sub> = 5.0V     |       | 3.5   | W                 |  |  |  |  |

| Icc5                                  | 5V Input Supply Current          | Active                      |       | 700   | mA                |  |  |  |  |

|                                       | PCIe Bus                         |                             |       |       |                   |  |  |  |  |

| Differential Output Voltage 0.8 1.2 V |                                  |                             |       |       |                   |  |  |  |  |

|                                       | DC Differential TX Impedance     |                             | 95.2  | 116.9 | Ω                 |  |  |  |  |

|                                       | Differential Input Voltage       |                             | 0.175 | 3.3   | V                 |  |  |  |  |

|                                       | DC Differential RX Impedance     |                             | 92.7  | 115.8 | Ω                 |  |  |  |  |

|                                       | Electrical Idle Detect Threshold |                             | 61    | 173   | mV                |  |  |  |  |

|                                       | Exci                             | tation Output (Per Channel) |       |       |                   |  |  |  |  |

|                                       | Output Frequency                 |                             | 0     | 10k   | Hz                |  |  |  |  |

|                                       | Output Voltage                   |                             |       | 7     | V <sub>RMS</sub>  |  |  |  |  |

|                                       | Output Current                   |                             |       | 100   | mA <sub>RMS</sub> |  |  |  |  |

|                                       |                                  | Reference Input             |       |       |                   |  |  |  |  |

|                                       | Frequency Range                  |                             | 0     | 10k   | Hz                |  |  |  |  |

|                                       | Voltage                          | JPx20, JPx21 (1-2)          | 4.5   | 14.0  | VRMS              |  |  |  |  |

|                                       | Voltage                          | JPx20, JPx21 (2-3)          | 30.0  | 99.0  | VRMS              |  |  |  |  |

|                                       |                                  | Channel Inputs              |       |       |                   |  |  |  |  |

|                                       | Frequency Range                  |                             | 0     | 10k   | Hz                |  |  |  |  |

|                                       | Voltage (Operating)              | 2V Configuration            | 1.7   | 2.3   | VRMS              |  |  |  |  |

|                                       | Voltage (Operating)              | 11.8V Configuration         | 10.0  | 13.4  | VRMS              |  |  |  |  |

|                                       | Voltage (Operating)              | 90V Configuration           | 76.5  | 103.5 | V <sub>RMS</sub>  |  |  |  |  |

|                                       | Voltage (Absolute Max)           | 2V Configuration            | -5    | +5    | V                 |  |  |  |  |

|                                       | Voltage (Absolute Max)           | 11.8V Configuration         | -30   | +30   | V                 |  |  |  |  |

|                                       | Voltage (Absolute Max)           | 90V Configuration           | -225  | +225  | V                 |  |  |  |  |

### Table 3: Electrical Characteristics

# 3 Board Connection

# 3.1 Board Handling Precautions

To prevent damage due to Electrostatic Discharge (ESD), keep your board in its antistatic bag until you are ready to install it into your system. When removing it from the bag, hold the board at the edges, and do not touch the components or connectors. Handle the board in an antistatic environment, and use a grounded workbench for testing and handling of your hardware.

# 3.2 **Physical Characteristics**

- Weight: Approximately 0.16 lbs. (72 g)

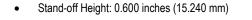

- Dimensions: 90.17 mm L x 95.89 mm W (3.550 in L x 3.775 in W)

Figure 1: Board Dimensions

# 3.3 Connectors and Jumpers

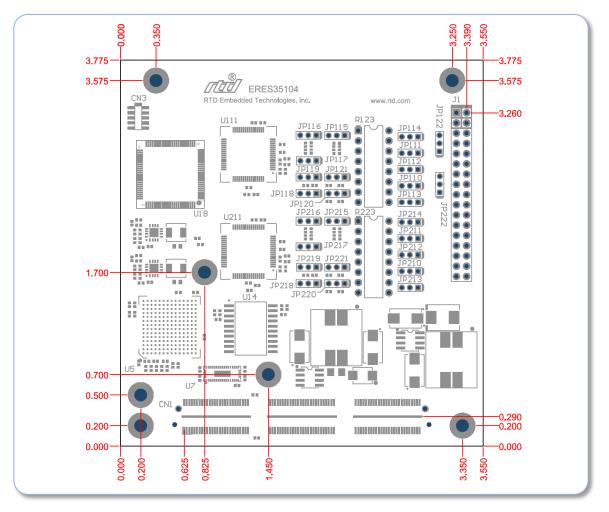

### Figure 2: Board Connections

## 3.3.1 EXTERNAL I/O CONNECTORS

### J1: Sensor Input / Output

The main connector for all of the I/O is J1. It includes the connections for the Synchro/Resolver/LVDT inputs, reference inputs, excitation outputs, and some test signals. The pin assignments are shown in the Table below.

| Pin Name       | #  | #  | Pin Name        |

|----------------|----|----|-----------------|

| GND            | 2  | 1  | CH0_EXCITATION  |

| GND            | 4  | 3  | CH0_SINE+       |

| GND            | 6  | 5  | CH0_COSINE+     |

| CH0_REF_IN-    | 8  | 7  | CH0_REF_IN+     |

| GND            | 10 | 9  | CH1_EXCITATION  |

| GND            | 12 | 11 | CH1_SINE+       |

| GND            | 14 | 13 | CH1_COSINE+     |

| CH1_REF_IN-    | 16 | 15 | CH1_REF_IN+     |

| CH1_VELOCITY   | 18 | 17 | CH0_VELOCITY    |

| CH0_S3         | 20 | 19 | CH0_S1          |

| CH0_S4         | 22 | 21 | GND             |

| CH0_S2_SYNCHRO | 24 | 23 | CH0_S2_RESOLVER |

| CH1_REF_IN+    | 24 | 25 | CH0_REF_IN+     |

| CH1_S3         | 28 | 27 | CH1_S1          |

| CH1_S4         | 30 | 29 | GND             |

| CH1_S2_SYNCHRO | 32 | 31 | CH1_S2_RESOLVER |

| GND            | 34 | 33 | GND             |

#### Table 4: J1 Input / Output Pin Assignments

## 3.3.2 BUS CONNECTORS

#### CN1 (Top) & CN2 (Bottom): PCIe Connector

The PCIe connector is the connection to the system CPU. The position and pin assignments are compliant with the *PCI/104-Express Specification*. (See PC/104 Specifications on page 35)

The ERES35104 is a "Universal" board, and can connect to either a Type 1 or Type 2 PCIe/104 connector.

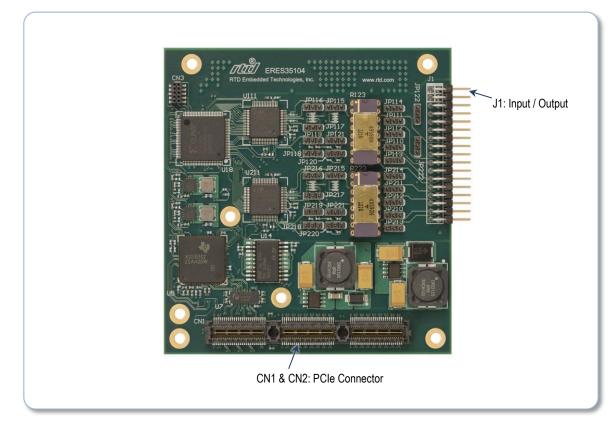

## 3.3.3 JUMPERS

On all jumpers, pin 1 is designated by a thick white silkscreen line, and a square pad on the PCB. The jumpers are discussed in the following sections of this manual.

The jumper settings are described in Section 6 starting on page 19.

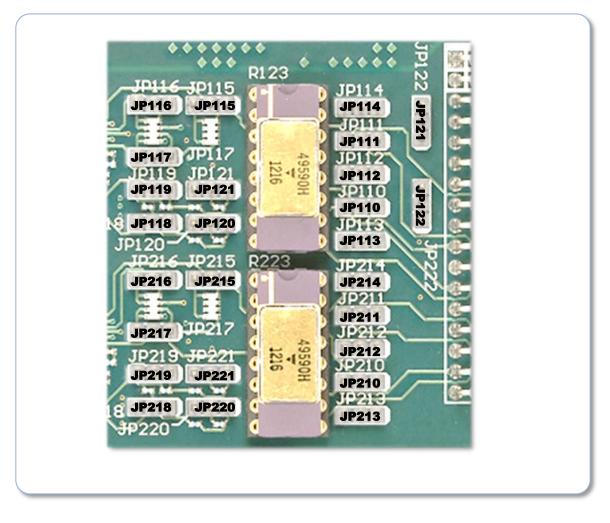

Figure 3: Jumper Locations

# 3.4 Steps for Installing

- 1. Always work at an ESD protected workstation, and wear a grounded wrist-strap.

- 2. Turn off power to the PC/104 system or stack.

- 3. Select and install stand-offs to properly position the module on the stack.

- 4. Remove the module from its anti-static bag.

- 5. Check that pins of the bus connector are properly positioned.

- 6. Check the stacking order; make sure all of the busses used by the peripheral cards are connected to the cpuModule.

- 7. Hold the module by its edges and orient it so the bus connector pins line up with the matching connector on the stack.

- 8. Gently and evenly press the module onto the PC/104 stack.

- 9. If any boards are to be stacked above this module, install them.

- 10. Attach any necessary cables to the PC/104 stack.

- 11. Re-connect the power cord and apply power to the stack.

- 12. Boot the system and verify that all of the hardware is working properly.

Figure 4: Example 104™Stack

# 4 IDAN Connections

# 4.1 Module Handling Precautions

To prevent damage due to Electrostatic Discharge (ESD), keep your module in its antistatic bag until you are ready to install it into your system. When removing it from the bag, hold the module by the aluminum enclosure, and do not touch the components or connectors. Handle the module in an antistatic environment, and use a grounded workbench for testing and handling of your hardware.

# 4.2 **Physical Characteristics**

- Weight: Approximately 0.21 Kg (0.46 lbs.)

- Dimensions: 151.972 mm L x 129.978 mm W x 16.993 mm H (5.983 in L x 5.117 in W x 0.669 in H)

Figure 5: IDAN Dimensions

# 4.3 Connectors

## 4.3.1 EXTERNAL I/O CONNECTORS

#### Sensor Input / Output

The IDAN connector includes the connections for the Synchro/Resolver/LVDT inputs, reference inputs, excitation outputs, and some test signals. The pin assignments are shown in the Table below.

| IDAN Pin #  | Pin Name        | J1 Pin # |  |  |  |  |

|-------------|-----------------|----------|--|--|--|--|

| 1           | CH0_EXCITATION  | 1        |  |  |  |  |

| 2           | CH0_SINE+       | 3        |  |  |  |  |

| 3           | CH0_COSINE+     | 5        |  |  |  |  |

| 4           | CH0_REF_IN+     | 7        |  |  |  |  |

| 5           | CH1_EXCITATION  | 9        |  |  |  |  |

| 6           | CH1_SINE+       | 11       |  |  |  |  |

| 7           | CH1_COSINE+     | 13       |  |  |  |  |

| 8           | CH1_REF_IN+     | 15       |  |  |  |  |

| 9           | CH0_VELOCITY    | 17       |  |  |  |  |

| 10          | CH0_S1          | 19       |  |  |  |  |

| 11          | GND             | 21       |  |  |  |  |

| 12          | CH0_S2_RESOLVER | 23       |  |  |  |  |

| 13          | CH0_REF_IN+     | 25       |  |  |  |  |

| 14          | CH1_S1          | 27       |  |  |  |  |

| 15          | GND             | 29       |  |  |  |  |

| 16          | CH1 S2 RESOLVER | 31       |  |  |  |  |

| 17          | GND             | 33       |  |  |  |  |

| 18          | RESERVED        | -        |  |  |  |  |

| 19 RESERVED |                 | -        |  |  |  |  |

| 20          | GND             | 2        |  |  |  |  |

| 21          | GND             | 4        |  |  |  |  |

| 22          | GND             | 6        |  |  |  |  |

| 23          | CH0 REF IN-     | 8        |  |  |  |  |

| 24          | GND             | 10       |  |  |  |  |

| 25          | GND             | 12       |  |  |  |  |

| 26          | GND             | 14       |  |  |  |  |

| 27          | CH1_REF_IN-     | 16       |  |  |  |  |

| 28          | CH1 VELOCITY    | 18       |  |  |  |  |

| 29          | CH0_S3          | 20       |  |  |  |  |

| 30          | CH0_S4          | 22       |  |  |  |  |

| 31          | CH0_S2_SYNCHRO  | 24       |  |  |  |  |

| 32          | CH1_REF_IN+     | 26       |  |  |  |  |

| 33          | CH1_S3          | 28       |  |  |  |  |

| 34          | CH1_S4          | 30       |  |  |  |  |

| 35          | CH1_S2_SYNCHRO  | 32       |  |  |  |  |

| 36          | GND             | 34       |  |  |  |  |

| 37          | RESERVED        |          |  |  |  |  |

| 51          | NLOLIVED        | -        |  |  |  |  |

Table 5: IDAN Input / Output Pin Assignments

# 4.3.2 BUS CONNECTORS

### CN1 (Top) & CN2 (Bottom): PCIe Connector

The PCIe connector is the connection to the system CPU. The position and pin assignments are compliant with the *PCI/104-Express Specification*. (See PC/104 Specifications on page 35)

The ERES35104 is a "Universal" board, and can connect to either a Type 1 or Type 2 PCIe/104 connector.

# 4.4 Steps for Installing

- 1. Always work at an ESD protected workstation, and wear a grounded wrist-strap.

- 2. Turn off power to the IDAN system.

- 3. Remove the module from its anti-static bag.

- 4. Check that pins of the bus connector are properly positioned.

- 5. Check the stacking order; make sure all of the busses used by the peripheral cards are connected to the cpuModule.

- 6. Hold the module by its edges and orient it so the bus connector pins line up with the matching connector on the stack.

- 7. Gently and evenly press the module onto the IDAN system.

- 8. If any boards are to be stacked above this module, install them.

- 9. Finish assembling the IDAN stack by installing screws of an appropriate length.

- 10. Attach any necessary cables to the IDAN system.

- 11. Re-connect the power cord and apply power to the stack.

- 12. Boot the system and verify that all of the hardware is working properly.

Figure 6: Example IDAN System

# 5.1 Block Diagram

The Figure below shows the functional block diagram of the ERES35104. The various parts of the block diagram are discussed in the following sections.

## 5.2 PCle Switch

The PCI Express Switch provides the bus interface to the ERES35104. The switch includes GPIO that are accessible from its Configuration Space, which is configured as a generic bus. This is a low speed interface that does not provide support for interrupts or DMA.

The PCIe Switch also provides lane repopulation. One lane is used as the uplink to the CPU. On the opposite side of the board it is replaced by a lane from the switch. This allows a virtually limitless number of boards to be added to the system.

# 5.3 Resolver to Digital Converter

The RD-19230 is a mixed signal CMOS IC containing analog input and digital output sections. Precision analog circuitry is merged with digital logic to form a complete high-performance tracking resolver-to-digital converter. For user flexibility and convenience, the converter bandwidth, dynamics, and velocity scaling are externally set with passive components.

The converter front-end consists of differential sine and cosine input amplifiers. The Control Transformer (CT) compares the analog input signals with the digital output, resulting in an error signal proportional to the sine of the angular difference. The CT uses a combination of amplifiers, switches, logic and capacitors in precision ratios to perform the calculation.

The converter accuracy is limited by the precision of the computing elements in the CT. Instead of a traditional precision resistor network, this converter uses capacitors with precisely controlled ratios. Sampling techniques are used to eliminate errors due to voltage drift and op-amp offsets.

The error processing is performed using the industry standard technique for Type II tracking converters. The DC error is integrated yielding a velocity voltage which in turn drives a voltage controlled oscillator (VCO). This VCO is an incremental integrator (constant voltage input to position rate output) which, together with the velocity integrator, forms a Type II servo feedback loop. A lead in the frequency response is introduced to stabilize the loop and another lag at higher frequency is introduced to reduce the gain and ripple at the carrier frequency and above. The settings of the various error processor gains and break frequencies are done with external resistors and capacitors so that the converter loop dynamics can be easily controlled.

### 5.3.1 BANDWIDTH FILTERS

The Resolver to Digital Converter circuit includes two selectable bandwidth filters. The filter characteristics are shown in the Table below. For other bandwidth filter configurations, contact RTD Tech Support.

| Description     | Filter<br>Channel | SHIFT | Maximum Excitation<br>Frequency | Resolution                | Bandwidth | Maximum<br>Tracking Rate |

|-----------------|-------------------|-------|---------------------------------|---------------------------|-----------|--------------------------|

| High Resolution | 1                 | 1     | 10 kHz                          | 16-bit (Synchro/Resolver) | 180 Hz    | 1200 rpm                 |

|                 |                   |       |                                 | 14-bit (LVDT)             |           |                          |

| High Velocity   | 2                 | 0     | 10 kHz                          | 12-bit (Synchro/Resolver) | 750 Hz    | 19200 rpm                |

|                 |                   |       |                                 | 10-bit (LVDT)             |           |                          |

#### Table 6: Bandwidth Filters

# 5.4 Front End

The front end consists of a precision resistor pack that sets the input voltage range (2V, 11.8V, or 90V). It also includes the jumpers to configure the board for different sensors.

Sensor signals must be converted to SIN and COS resolver signals that can be directly be interfaced by the Resolver-to-Digital converters. The classical transformer coupled connection is often too cumbersome to use. The ERES35104 module uses an operational amplifier and precision resistors to implement the Solid State Scott-T circuit. The most important design criteria in this connection are the perfect matching of the resistors. Precision is maintained by using a special trimmed resistor network together with the op-amps. These resistor networks are available for the three standard voltage levels of 2V, 11.8V and 90V. The resistor network value ratios are pre-trimmed to produce the 2V<sub>RMS</sub> input signal required by the converters.

You may separately purchase resistor networks for the standard voltages from RTD. They may be easily configured channel-by-channel by inserting the correct resistor network into the onboard sockets. The resistor networks are used as follows:

DDC-49530 are used with 11.8V inputs DDC-49590 are used with 90V inputs DDC-76037 are used with 2V inputs

# 5.5 **On-Board Excitation**

The on-board excitation can be used in certain applications to provide a reference to the sensors. It consists of a Programmable Waveform Generator and two output amplifiers. Both channels must use the same excitation frequency, but the output levels can be individually adjusted.

## 5.6 **EPLD**

The EPLD provides glue logic between the PCIe interface and the on-board functions.

# 6 Board Configuration

# 6.1 Sensor Input Connections

The following sections describe how to connect and configure the ERES35104 for use with a resolver, synchro, LVDT, and direct input. All sensors except for LVDTs also require a reference input. Please see Section 6.2 on page 24 for information on connecting the reference.

## 6.1.1 RESOLVER INPUT

A resolver is a type of absolute rotary encoder. It consists of an excitation coil in the rotor, and two pickup coils in the stator at a 90° angle. One pickup coil has leads that are generally labeled S3 for positive and S1 for negative; and the other coil has S2 for positive and S4 for negative. This section described how to connect and configure this board for use with a resolver.

A resolver also requires a reference input. Please see Section 6.2 on page 24 for information on connecting the reference.

#### Input Connections

| Sensor |               |                 | ERES35104     | IDAN-ERES35104 |               |               |

|--------|---------------|-----------------|---------------|----------------|---------------|---------------|

| Lead   | Description   | Pin Name        | Channel 0 Pin | Channel 1 Pin  | Channel 0 Pin | Channel 1 Pin |

| S1     | SINE -        | CHx_S1          | 19            | 27             | 10            | 14            |

| S2     | COSINE +      | CHx_S2_RESOLVER | 23            | 31             | 12            | 16            |

|        | No Connection | CHx_S2_SYNCHRO  | 24            | 32             | 31            | 35            |

| S3     | SINE +        | CHx_S3          | 20            | 28             | 29            | 33            |

| S4     | COSINE -      | CHx_S4          | 22            | 30             | 30            | 34            |

#### **Table 7: Resolver Input Connections**

#### **Jumper Configuration**

See Figure 3 on page 12 for jumper locations.

#### Table 8: Resolver Jumper Settings

| Channel 0 | Channel 1 |          |

|-----------|-----------|----------|

| Jumper    | Jumper    | Position |

| JP110     | JP210     | 1-2      |

| JP111     | JP211     | 1-2      |

| JP112     | JP212     | 1-2      |

| JP113     | JP213     | 1-2      |

| JP114     | JP214     | 1-2      |

| JP115     | JP215     | 1-2      |

| JP116     | JP216     | 1-2      |

| JP117     | JP217     | 1-2      |

| JP118     | JP218     | 1-2      |

## 6.1.2 SYNCHRO INPUT

A synchro is a type of absolute rotary encoder. It consists of an excitation coil in the rotor, and three pickup coils in the stator at a 120° angles. The pickup coils have leads that are generally labeled S1, S2, and S3. The other ends of the coils are tied together. This section described how to connect and configure this board for use with a synchro.

A synchro also requires a reference input. Please see Section 6.2 on page 24 for information on connecting the reference.

#### Input Connections

| Sensor |               | ERES35104       |               | IDAN-ERES35104 |               |               |

|--------|---------------|-----------------|---------------|----------------|---------------|---------------|

| Lead   | Description   | Pin Name        | Channel 0 Pin | Channel 1 Pin  | Channel 0 Pin | Channel 1 Pin |

| S1     | 240°          | CHx_S1          | 19            | 27             | 10            | 14            |

|        | No Connection | CHx_S2_RESOLVER | 23            | 31             | 12            | 16            |

| S2     | 0°            | CHx_S2_SYNCHRO  | 24            | 32             | 31            | 35            |

| S3     | 120°          | CHx_S3          | 20            | 28             | 29            | 33            |

|        | No Connection | CHx_S4          | 22            | 30             | 30            | 34            |

#### **Table 9: Synchro Input Connections**

#### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

### Table 10: Synchro Jumper Settings

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position |

|---------------------|---------------------|----------|

| JP110               | JP210               | 2-3      |

| JP111               | JP211               | 2-3      |

| JP112               | JP212               | 2-3      |

| JP113               | JP213               | 2-3      |

| JP114               | JP214               | 2-3      |

| JP115               | JP215               | 1-2      |

| JP116               | JP216               | 1-2      |

| JP117               | JP217               | 1-2      |

| JP118               | JP218               | 1-2      |

## 6.1.3 2-WIRE LVDT INPUT

A 2-wire LVDT is a type of absolute linear encoder. It consists of an excitation coil and a pickup coil. There is also a moving ferromagnetic core between the two coils. The output amplitude is directly proportional to the position of the ferromagnetic core. The pickup coil has leads that are generally labeled FEEDBACK HI and FEEDBACK LO. The excitation has leads that are generally labeled REF HI and REF LO.

An LVDT does not use the reference input. It does require an excitation source that may be supplied on-board or from an external source.

An LVDT generally requires some scaling to make full use of the dynamic range of the ERES35104. In order to facilitate this, the signal path allows the addition of gain. Contact RTD Tech Support for more details.

#### Figure 8: 2-Wire LVDT Schematic

#### Input Connections

#### Table 11: 2-Wire LVDT Input Connections

| Sensor      |               | ERES35104       |                  |                  | IDAN-ERES35104   |                  |

|-------------|---------------|-----------------|------------------|------------------|------------------|------------------|

| Lead        | Description   | Pin Name        | Channel 0<br>Pin | Channel 1<br>Pin | Channel 0<br>Pin | Channel 1<br>Pin |

| FEEDBACK LO | Pickup -      | CHx_S1          | 19               | 27               | 10               | 14               |

| REF HI      | Excitation +  | CHx_S2_RESOLVER | 23               | 31               | 12               | 16               |

|             | No Connection | CHx_S2_SYNCHRO  | 24               | 32               | 31               | 35               |

| FEEDBACK HI | Pickup +      | CHx_S3          | 20               | 28               | 29               | 33               |

| REF LO      | Excitation -  | CHx_S4          | 22               | 30               | 30               | 34               |

#### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

#### Table 12: 2-Wire LVDT Jumper Settings

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position |

|---------------------|---------------------|----------|

| JP110               | JP210               | 1-2      |

| JP111               | JP211               | 1-2      |

| JP112               | JP212               | 1-2      |

| JP113               | JP213               | 1-2      |

| JP114               | JP214               | 1-2      |

| JP115               | JP215               | 2-3      |

| JP116               | JP216               | 2-3      |

| JP117               | JP217               | 2-3      |

| JP118               | JP218               | 2-3      |

| JP119               | JP219               | 2-3      |

| JP120               | JP220               | Any      |

| JP121               | JP221               | Any      |

| JP122               | JP222               | 1-2      |

## 6.1.4 3-WIRE LVDT INPUT

A 3-wire LVDT is a type of absolute linear encoder. It consists of an excitation coil and a pickup coil with a center tap. There is also a moving ferromagnetic core between the two coils. The pickup coil has leads that are generally labeled V<sub>A</sub>, V<sub>B</sub>, and Common.

An LVDT does not use the reference input. It does require an excitation source that may be supplied on-board or from an external source.

An LVDT generally requires some scaling to make full use of the dynamic range of the ERES35104. In order to facilitate this, the signal path allows the addition of gain. Contact RTD Tech Support for more details.

Input Connections

| Sensor |                            | ERES35104       |                  | IDAN-ERES35104   |                  |                  |

|--------|----------------------------|-----------------|------------------|------------------|------------------|------------------|

| Lead   | Description                | Pin Name        | Channel 0<br>Pin | Channel 1<br>Pin | Channel 0<br>Pin | Channel 1<br>Pin |

| VB     | Pickup +                   | CHx_S1          | 19               | 27               | 10               | 14               |

|        | No Connection              | CHx_S2_RESOLVER | 23               | 31               | 12               | 16               |

| Common | May also<br>connect to GND | CHx_S2_SYNCHRO  | 24               | 32               | 31               | 35               |

|        | No Connection              | CHx_S3          | 20               | 28               | 29               | 33               |

| VA     | Pickup +                   | CHx_S4          | 22               | 30               | 30               | 34               |

#### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

| Table 14: 3-Wire LVDT | Jumper Settings |

|-----------------------|-----------------|

|-----------------------|-----------------|

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position |

|---------------------|---------------------|----------|

| JP110               | JP210               | 2-3      |

| JP111               | JP211               | 2-3      |

| JP112               | JP212               | 1-2      |

| JP113               | JP213               | 2-3      |

| JP114               | JP214               | 1-2      |

| JP115               | JP215               | 2-3      |

| JP116               | JP216               | 2-3      |

| JP117               | JP217               | 2-3      |

| JP118               | JP218               | 2-3      |

| JP119               | JP219               | 2-3      |

| JP120               | JP220               | Any      |

| JP121               | JP221               | Any      |

| JP122               | JP222               | 1-2      |

## 6.1.5 DIRECT INPUT

The ERES35104 also allows direct input to the resolver converter. This allows connection to other types of devices. These devices typically require a specialized external signal conditioning board.

Direct Input also requires a reference input. Please see Section 6.2 on page 24 for information on connecting the reference.

### Input Connections

| Sensor |               | ERE\$35104      |                  |                  | IDAN-ERES35104   |                  |

|--------|---------------|-----------------|------------------|------------------|------------------|------------------|

| Lead   | Description   | Pin Name        | Channel 0<br>Pin | Channel 1<br>Pin | Channel 0<br>Pin | Channel 1<br>Pin |

|        | No Connection | CHx_S1          | 19               | 27               | 10               | 14               |

|        | No Connection | CHx_S2_RESOLVER | 23               | 31               | 12               | 16               |

|        | No Connection | CHx_S2_SYNCHRO  | 24               | 32               | 31               | 35               |

|        | No Connection | CHx_S3          | 20               | 28               | 29               | 33               |

|        | No Connection | CHx_S4          | 22               | 30               | 30               | 34               |

| Sine   | Sine Input    | CHx_SINE+       | 3                | 11               | 2                | 6                |

| Cosine | Cosine Input  | CHx_COSINE+     | 5                | 13               | 3                | 7                |

#### Table 15: Direct Input Connections

### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

#### Table 16: Direct Input Jumper Settings

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position              |

|---------------------|---------------------|-----------------------|

| JP110               | JP210               |                       |

|                     |                     | any                   |

| JP111               | JP211               | any                   |

| JP112               | JP212               | any                   |

| JP113               | JP213               | any                   |

| JP114               | JP214               | any                   |

| JP115               | JP215               | Open (jumper removed) |

| JP116               | JP216               | 1-2                   |

| JP117               | JP217               | Open (jumper removed) |

| JP118               | JP218               | 1-2                   |

# 6.2 **Reference Input**

The resolver converter requires a reference input. The reference can come from the on-board excitation signal, or from an external source. The connection to the reference is found in the following sections.

The converter uses a synthesized reference, allowing up to 45 degrees of phase shift between the reference input and the sensor inputs.

NOTE: When using in LVDT mode, the reference is derived on-board from the input signals. The CHx\_REF\_IN signals must be left unconnected.

## 6.2.1 INTERNALLY GENERATED REFERENCE

#### Connections

#### Table 17: Internal Reference Connections

| Sensor        | ERI                 | IDAN-ERES35104 |     |           |           |

|---------------|---------------------|----------------|-----|-----------|-----------|

|               | Channel 0 Channel 1 |                |     | Channel 0 | Channel 1 |

| Lead          | Pin Name            | Pin            | Pin | Pin       | Pin       |

| REF HI        | CHx_EXCITATION      | 1              | 9   | 1         | 5         |

| REF LO        | GND                 | 2              | 20  | 22        | 6         |

| No Connection | CHx_REF_IN+         | 7              | 4   | 15        | 8         |

| No Connection | CHx_REF_IN-         | 8              | 23  | 16        | 27        |

#### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

#### Table 18: Internal Reference Jumper Settings

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position |

|---------------------|---------------------|----------|

| JP119               | JP219               | 2-3      |

| JP120               | JP220               | 1-2      |

| JP121               | JP221               | 1-2      |

| JP122               | JP222               | 2-3      |

## 6.2.2 DIFFERENTIAL EXTERNALLY GENERATED REFERENCE

### **Connections**

| Sensor        | ERES35104      |                  |                  | IDAN-ERES35104   |                  |

|---------------|----------------|------------------|------------------|------------------|------------------|

| Lead          | Pin Name       | Channel 0<br>Pin | Channel 1<br>Pin | Channel 0<br>Pin | Channel 1<br>Pin |

| No Connection | CHx_EXCITATION | 1                | 9                | 1                | 5                |

| No Connection | GND            | 2                | 20               | 22               | 6                |

| REF HI        | CHx_REF_IN+    | 7                | 15               | 4                | 8                |

| REF LO        | CHx_REF_IN-    | 8                | 16               | 23               | 27               |

#### Table 19: Differential External Reference Connections

## Jumper Configuration

See Figure 3 on page 12 for jumper locations.

| Channel 1<br>Jumper | Channel 2<br>Jumper | Position                                                                              |

|---------------------|---------------------|---------------------------------------------------------------------------------------|

| JP119               | JP219               | 1-2                                                                                   |

| JP120               | JP220               | 2-3 (2V <sub>RMS</sub> )<br>1-2 (11.8V <sub>RMS</sub> )<br>Open (90V <sub>RMS</sub> ) |

| JP121               | JP221               | 2-3 (2V <sub>RMS</sub> )<br>1-2 (11.8V <sub>RMS</sub> )<br>Open (90V <sub>RMS</sub> ) |

| JP122               | JP222               | 1-2                                                                                   |

## 6.2.3 SINGLE-ENDED EXTERNALLY GENERATED REFERENCE

#### **Connections**

#### Table 21: Single-Ended External Reference Connections

| Sensor        | ERES35104      |                  | IDAN-ERES35104   |                  |                  |

|---------------|----------------|------------------|------------------|------------------|------------------|

| Lead          | Pin Name       | Channel 0<br>Pin | Channel 1<br>Pin | Channel 0<br>Pin | Channel 1<br>Pin |

| No Connection | CHx_EXCITATION | 1                | 9                | 1                | 5                |

| No Connection | GND            | 2                | 20               | 22               | 6                |

| REF           | CHx_REF_IN+    | 7 or 25          | 15 or 26         | 4 or13           | 8 or 32          |

| GND           | GND            | 6                | 14               | 22               | 26               |

### Jumper Configuration

See Figure 3 on page 12 for jumper locations.

#### Table 22: Single-Ended External Reference Jumper Settings

| Channel 0<br>Jumper | Channel 1<br>Jumper | Position                                                                              |  |  |

|---------------------|---------------------|---------------------------------------------------------------------------------------|--|--|

| JP119               | JP219               | 2-3                                                                                   |  |  |

| JP120               | JP220               | 2-3 (2V <sub>RMS</sub> )<br>1-2 (11.8V <sub>RMS</sub> )<br>Open (90V <sub>RMS</sub> ) |  |  |

| JP121               | JP221               | 2-3 (2V <sub>RMS</sub> )<br>1-2 (11.8V <sub>RMS</sub> )<br>Open (90V <sub>RMS</sub> ) |  |  |

| JP122               | JP222               | 1-2                                                                                   |  |  |

# 7 Register Address Space

The bus interface is provided through the GPIO of the PCIe Switch. The GPIO are configured as a generic bus, and the board registers are accessed through an index and data register. The following sections describe the steps needed to access the board registers.

# 7.1 Identifying the Board

The ERES35104 shows up in standard PCI Configuration space as a set of PCI to PCI Bridges. It can be positively identified as shown in the Table below.

#### Table 23: Identifying the ERES35104

| Configuration<br>Space Offset |                     |        |

|-------------------------------|---------------------|--------|

| 0x00                          | Vendor ID           | 0x104C |

| 0x02                          | Device ID           | 0x8232 |

| 0x84                          | Subsystem Vendor ID | 0x1435 |

| 0x86                          | Subsystem ID        | 0x3616 |

## 7.2 Index and Data Registers

| Table 24: Index and Data Registers |             |      |            |      |

|------------------------------------|-------------|------|------------|------|

| Configurat<br>ion Space            |             |      |            |      |

| Offset                             | 0x03        | 0x02 | 0x01       | 0x00 |

| 0xBC                               | GPIOAB_CTRL |      |            |      |

| 0xC0                               | GPIOCD_CTRL |      |            |      |

| 0xC4                               | SELECT      |      | INDEX_DATA |      |

## 7.2.1 GPIOAB\_CTRL (READ/WRITE)

This register is used to set the direction for the GPIO port. The values to write to it are:

0x12491249 for a Write operation 0x00000000 for a Read operation

## 7.2.2 GPIOCD\_CTRL (READ/WRITE)

This register is used to set the direction for the GPIO port. The values to write to it are:

0x01491249 for a Write operation 0x01480000 for a Read operation

## 7.2.3 SELECT (READ/WRITE)

This register is used to select between the Index and Data register. All undefined bits may be written with a 0.

B2: DATA

| 0 = Accessing | Index register |

|---------------|----------------|

| 1 = Accessing | Data register  |

#### B1:WR\_STRB

Writes take effect on 0 to 1 transition

B0: OE#

- 0 = Output of EPLD is enabled (for reads)

- 1 = Output of EPLD is disabled (for writes)

## 7.2.4 INDEX\_DATA (READ/WRITE)

This register is used to access the Index or Data register.

NOTE: The SELECT and INDEX\_DATA register may be accessed using a single 32-bit operation.

# 7.3 Accessing the Board Registers

### 7.3.1 READING FROM A BOARD REGISTER

To read one of the Board Registers, use the following steps:

- 1. Read the GPIOAB\_CTRL, GPIOCD\_CTRL, SELECT and INDEX\_DATA registers and store them so they can be restored.

- 2. Save the Index Register

- a. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Read values.

- b. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=0

- c. Read INDEX\_DATA and store it as the Old Index.

- 3. Set the Index Register

- a. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=1 and set INDEX\_DATA to the desired Index.

- b. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Write values.

- c. Set SELECT such that DATA=0, WR\_STRB=1, and OE#=1. (May also set INDEX\_DATA to the desired Index again).

- 4. Read the Data Register

- a. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Read values.

- b. Set SELECT such that DATA=1, WR\_STRB=0, and OE#=0

- c. Read INDEX\_DATA as the desired Data.

- 5. Restore the Index Register

- a. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=1 and set INDEX\_DATA to the Old Index.

- b. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Write values.

- c. Set SELECT such that DATA=0, WR\_STRB=1, and OE#=1. (May also set INDEX\_DATA to the Old Index again).

- 6. Restore Other Registers

- a. Restore GPIOAB\_CTRL

- b. Restore GPIOCD\_CTRL bit-wise or'ed with the Read Value (to make sure the SELECT pins are always output)

- c. Restore SELECT and INDEX\_DATA with the WR\_STRB bit cleared (to make sure a write isn't duplicated)

## 7.3.2 WRITING TO A BOARD REGISTER

To write to one of the Board Registers, use the following steps:

- 1. Read the GPIOAB\_CTRL, GPIOCD\_CTRL, SELECT and INDEX\_DATA registers and store them so they can be restored.

- 2. Save the Index Register

- a. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Read values.

- b. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=0

- c. Read INDEX\_DATA and store it as the Old Index.

- 3. Set the Index Register

- a. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=1 and set INDEX\_DATA to the desired Index.

- b. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Write values.

- c. Set SELECT such that DATA=0, WR\_STRB=1, and OE#=1. (May also set INDEX\_DATA to the desired Index again).

- 4. Set the Data Register

- a. Set SELECT such that DATA=1, WR\_STRB=0, and OE#=1 and set INDEX\_DATA to the desired Data.

- b. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Write values. (Already set by Step 3 above)

- c. Set SELECT such that DATA=1, WR\_STRB=1, and OE#=1. (May also set INDEX\_DATA to the desired Data again).

- 5. Restore the Index Register

- a. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=1 and set INDEX\_DATA to the Old Index.

- b. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Write values. (Already set by Step 3 above)

- c. Set SELECT such that DATA=0, WR\_STRB=1, and OE#=1. (May also set INDEX\_DATA to the Old Index again).

- 6. Restore Other Registers

- a. Restore GPIOAB\_CTRL

- b. Restore GPIOCD\_CTRL bit-wise or'ed with the Read Value (to make sure the SELECT pins are always output)

- c. Restore SELECT and INDEX\_DATA with the WR\_STRB bit cleared (to make sure a write isn't duplicated)

NOTE: If multi-thread safe operation is not required, steps 1, 2, 5, and 6 can be eliminated.

## 7.3.3 READING SHIFT REGISTER STATUS

The Index Register includes a Read-Only bit indicating whether the shift register is busy. This can be accessed as follows:

- 1. Read the GPIOAB\_CTRL, GPIOCD\_CTRL, SELECT and INDEX\_DATA registers and store them so they can be restored.

- 2. Read the Index/Status Register

- a. Set GPIOAB\_CTRL and GPIOCD\_CTRL to their Read values.

- b. Set SELECT such that DATA=0, WR\_STRB=0, and OE#=0

- c. Read INDEX\_DATA. Bit 8 is set if the Shift Register is busy, and cleared if the Shift Register is idle.

- 3. Restore Other Registers

- a. Restore GPIOAB\_CTRL

- b. Restore GPIOCD\_CTRL bit-wise or'ed with the Read Value (to make sure the SELECT pins are always output)

- c. Restore SELECT and INDEX\_DATA with the WR\_STRB bit cleared (to make sure a write isn't duplicated)

NOTE: If multi-thread safe operation is not required, steps 1, and 3 can be eliminated.

# 7.4 **Board Registers**

#### Table 25: Board Registers

| Index | Data (16-bit)    |

|-------|------------------|

| 0x00  | BUILD_NUM_LS     |

| 0x01  | BUILD_NUM_MS     |

| 0x02  | Reserved         |

| 0x03  | SR_SELECT        |

| 0x04  | SR_DATA_OUT      |

| 0x05  | SR_DATA_IN       |

| 0x06  | CH0_SETUP_STATUS |

| 0x07  | CH1_SETUP_STATUS |

| 0x08  | CH0_POSITION     |

| 0x09  | CH1_POSITION     |

## 7.4.1 BUILD\_NUM\_LS, BUILD\_NUM\_MS (READ-ONLY)

These two registers contain the build number of the EPLD. It can be used to track revisions of the EPLD. BUILD\_NUM\_LS is the least-significant word, and BUILD\_NUM\_MS is the most significant word.

## 7.4.2 SR\_SELECT (READ/WRITE)

This register selects which of the various on-board devices the shift register is accessing. Possible options are below. All other values are reserved.

- 0x00: Channel 0 Mode

- 0x01: Channel 0 Velocity Trim

- 0x02: Channel 1 Mode

- 0x03: Channel 1 Velocity Trim

- 0x04: Excitation Frequency

- 0x05: Excitation Amplitude

## 7.4.3 SR\_DATA\_OUT (READ/WRITE)

This register contains the output data for the shift register. Writing to this register also causes the shift register to start.

Prior to any writes to SR\_DATA\_OUT, the Shift Register Status must be checked to make sure it is idle as described in Section 7.3.3 on page 29.

## 7.4.4 SR\_DATA\_IN (READ-ONLY)

This register contains the data returned from the selected device during the last transaction.

Prior to any reads from SR\_DATA\_IN, the Shift Register Status must be checked to make sure it is idle as described in Section 7.3.3 on page 29.

## 7.4.5 CHx\_SETUP\_STATUS (Read/WRITE, READ-ONLY)

This register is used to setup each of the channels, and to return the status of the channels.

B0: SHIFT (Read/Write) – Selects the bandwidth filter (See Section 5.3.1 on page 18).

0 = Filter 2 (High Velocity)

1 = Filter 1 (High Resolution)

B1: DN\_UP (Read/Write)

0 = Inactive bandwidth filter is precharged with a gain of 4. Resolution will be increased.

1 = Inactive bandwidth filter is precharged with a gain of 14. Resolution will be decreased.

B2: DSR (Read/Write) – Disable Synthesized Reference

0 = Synthesized Reference is enabled

1 = Synthesized Reference is disabled

B4: DIR (Read-Only)

0 = Position angle is decreasing

1 = Position angle is increasing

B5: BIT# (Read-Only) – Built-In-Test.

0 = Fault condition

1 = No Fault condition

## 7.4.6 CHX\_POSITION (READ-ONLY)

This register contains the current position of the sensor. A full rotation is represented as 2<sup>16</sup>, regardless of number of bits. Therefore, to get the position in degrees, use the following formula:

$$\theta = \frac{(CHx\_POSITION)(360)}{2^{16}}$$

If CHx\_POSITION is interpreted as an unsigned integer, the range for  $\theta$  is 0° to 359.99°. If CHx\_POSITION is interpreted as a signed integer, the range for  $\theta$  is -180° to +179.99°.

# 7.5 Shift Register

The shift register is used to communicate with various devices on the board. This includes digital potentiometers for setting the mode, velocity trim, and excitation amplitude, and the excitation Programmable Waveform Generator. The commands that can be sent to the devices are described in the following sections.

NOTE: Prior to any writes to SR\_DATA\_OUT or reads from SR\_DATA\_IN, the Shift Register Status must be checked to make sure it is idle as described in Section 7.3.3 on page 29.

## 7.5.1 PERFORMING A SHIFT REGISTER COMMAND

To use the Shift Register, use the following steps:

- 1. Read the SR\_SELECT board register, and store the value.

- 2. Wait until the Shift Register is idle (See Section 7.3.3 on page 29).

- 3. Write to the SR\_SELECT board register with the desired device.

- 4. Write to the SR\_DATA\_OUT board register with the desired command

- 5. Wait until the Shift Register is idle (See Section 7.3.3 on page 29).

- 6. Read from the SR\_DATA\_IN register as the Read Data.

## 7.5.2 CHANNEL X MODE (0x00 AND 0x02)

This shift register select line is connected to an Intersil ISL22424 digital potentiometer. The H pin, which corresponds to a wiper value of 0xFF, is connected to +5V. The L pin, which corresponds to a wiper value of 0x00, is connected to -5V. For 0V, use a wiper value of 0x80.

#### Output Data

The Table below shows the value to write to the SR\_DATA\_OUT register to issue various commands.

| Table 26: Channel Mode Shift Register |                     |                                                                                     |  |  |

|---------------------------------------|---------------------|-------------------------------------------------------------------------------------|--|--|

| Data                                  | Name                | Description                                                                         |  |  |

| 0x60C0                                | Set to Non-Volatile | All subsequent writes to the wiper position are only stored in non-volatile memory. |  |  |

|                                       |                     | This should be done prior to adjusting the wiper, i.e. at board open.               |  |  |

| 0xC0XX                                | Write D0 Wiper      | Writes to the wiper that is attached to the Resolver to Digital Converter D0 pin.   |  |  |

| 0xC1YY                                | Write D1 Wiper      | Writes to the wiper that is attached to the Resolver to Digital Converter D1 pin.   |  |  |

| 0x8000                                | Read D0 Wiper       | Reads from the wiper that is attached to the Resolver to Digital Converter D0 pin.  |  |  |

| 0x8100                                | Read D1 Wiper       | Reads from the wiper that is attached to the Resolver to Digital Converter D1 pin.  |  |  |

#### Input Data

The lower 8 bits of the SR\_DATA\_IN register contain the wiper position after a read command is issued

#### Modes

The following table shows the values to write to the SR\_DATA\_OUT register to set the Resolver to Digital Converter to various modes. Each mode has two commands, one for the D0 wiper, and one for the D1 wiper. They may be written in any order.

| Table 27: Channel Modes |     |     |                         |  |  |

|-------------------------|-----|-----|-------------------------|--|--|

| Data                    | D1  | D0  | Mode                    |  |  |

| 0xC080                  | 0V  | 0V  | 10-bit Synchro/Resolver |  |  |

| 0xC180                  |     |     |                         |  |  |

| 0xC0FF                  | 0V  | 5V  | 12-bit Synchro/Resolver |  |  |

| 0xC180                  |     |     |                         |  |  |