# DM35424HR/DM35224HR

PCI Express Analog I/O dataModule

## User's Manual

BDM-610010044 Rev. C

### RTD Embedded Technologies, Inc.

103 Innovation Boulevard State College, PA 16803 USA Telephone: 814-234-8087 Fax: 814-234-5218

www.rtd.com

sales@rtd.com techsupport@rtd.com

# **Revision History**

Rev A Initial Release

Rev B Added Information about DM35224

Rev C Updated DIO IDAN Pinout

Advanced Analog I/O, Advanced Digital I/O, aAIO, aDIO, a2DIO, Autonomous SmartCal, "Catch the Express", cpuModule, dspFramework, dspModule, expressMate, ExpressPlatform, HiDANplus, "MIL Value for COTS prices", multiPort, PlatformBus, and PC/104EZ are trademarks, and "Accessing the Analog World", dataModule, IDAN, HiDAN, RTD, and the RTD logo are registered trademarks of RTD Embedded Technologies, Inc (formerly Real Time Devices, Inc.). PS/2 is a trademark of International Business Machines Inc. PCI, PCI Express, and PCIe are trademarks of PCI-SIG. PC/104, PCI/104-Plus, PCI-104, PCI/104-Express and 104 are trademarks of the PC/104 Embedded Consortium. All other trademarks appearing in this document are the property of their respective owners.

Failure to follow the instructions found in this manual may result in damage to the product described in this manual, or other components of the system. The procedure set forth in this manual shall only be performed by persons qualified to service electronic equipment. Contents and specifications within this manual are given without warranty, and are subject to change without notice. RTD Embedded Technologies, Inc. shall not be liable for errors or omissions in this manual, or for any loss, damage, or injury in connection with the use of this manual.

Copyright © 2014 by RTD Embedded Technologies, Inc. All rights reserved.

# Table of Contents

| 1 | Introducti | ion                                                                                                                                              | 8                          |  |  |  |  |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|

|   | 1.1        | 1.1 Product Overview                                                                                                                             |                            |  |  |  |  |

|   | 1.2        | Board Features                                                                                                                                   | 8                          |  |  |  |  |

|   | 1.3        | Ordering Information                                                                                                                             | 8                          |  |  |  |  |

|   | 1.4        | Contact Information                                                                                                                              | 9<br>9<br>9                |  |  |  |  |

| 2 | Specificat |                                                                                                                                                  | 10                         |  |  |  |  |

|   | 2.1        | Operating Conditions                                                                                                                             | 10                         |  |  |  |  |

|   | 2.2        | Electrical Characteristics                                                                                                                       | 10<br>12                   |  |  |  |  |

| 3 | Board Co   | onnection                                                                                                                                        | 13                         |  |  |  |  |

|   | 3.1        | Board Handling Precautions                                                                                                                       | 13                         |  |  |  |  |

|   | 3.2        | Physical Characteristics                                                                                                                         | 13                         |  |  |  |  |

|   | 3.3        | Connectors and Jumpers                                                                                                                           | 14<br>14<br>14<br>14       |  |  |  |  |

|   |            | Analog I/O Connectors: CN14 and CN24 3.3.3 DM35224 External I/O Connectors Digital I/O Connectors: CN6 Analog I/O Connectors: CN14 3.3.4 Jumpers | 15<br>15<br>15<br>16<br>16 |  |  |  |  |

|   | 3.4        | Steps for Installing                                                                                                                             | 17                         |  |  |  |  |

| 4 | IDAN Con   | nnections                                                                                                                                        | 18                         |  |  |  |  |

|   | 4.1        | Module Handling Precautions                                                                                                                      | 18                         |  |  |  |  |

|   | 4.2        | Physical Characteristics                                                                                                                         | 18                         |  |  |  |  |

|   | 4.3        | Connectors                                                                                                                                       |                            |  |  |  |  |

|   | 4.4        | Steps for Installing                                                                                                                             | 27                         |  |  |  |  |

| 5 | Functiona  | al Description                                                                                                                                   | 28                         |  |  |  |  |

|   | 5.2        | DMA Engine                                                                                                                                       | 28                         |  |  |  |  |

|   | 5.3        | Analog Front-End                                                                                                                                 |                            |  |  |  |  |

|   | 5.4        | Analog to Digital Converter                                                                                                                      | 30<br>30                   |  |  |  |  |

|   |            | 5.4.2<br>5.4.3             | Analog to Digital Converter Delay<br>Data Formatting               | 30<br>31 |

|---|------------|----------------------------|--------------------------------------------------------------------|----------|

|   | 5.5        | Digital to Ar<br>5.5.1     | nalog ConverterInitializing the DAC Converter                      | 31<br>31 |

|   | 5.6        | Digital I/O                |                                                                    | 31       |

|   | 5.7        | Voltage Re                 | eference                                                           | 31       |

| 6 | Register / | Address Space              | 2                                                                  | 32       |

| · | register 7 | Reg                        | gister Types<br>ock and Trigger Source                             | 32<br>32 |

|   | 6.1        | BAR0 – Ge                  | eneral Board Control                                               |          |

|   |            | 6.1.1                      | GBC_BRD_RST (Read/Write)                                           | 33       |

|   |            | 6.1.2                      | GBC_EOI (Read/Clear)                                               | 33       |

|   |            | 6.1.3<br>6.1.4             | GBC_REV (Read-Only)                                                | 33<br>33 |

|   |            | 6.1. <del>4</del><br>6.1.5 | GBC_FMT (Read-Only) GBC_PDP (Read-Only)                            | 33       |

|   |            | 6.1.6                      | GBC_BUILD (Read-Only)                                              | 33       |

|   |            | 6.1.7                      | GBC_SYS_CLK_FREQ (Read Only)                                       | 34       |

|   |            | 6.1.8                      | GBC_IRQ_STATUS (Read/Clear)                                        | 34       |

|   |            | 6.1.9                      | GBC_DIRQ_STATUS (Read/Clear)                                       | 34       |

|   |            | 6.1.10                     | FBn_ID (Read-Only)                                                 | 34       |

|   |            | 6.1.11                     | FBn_Offset (Read-Only)                                             | 34       |

|   |            | 6.1.12                     | FBn_Offset_DMA (Read-Only)                                         | 34       |

|   | 6.2        |                            | ctional Block Standard DMA                                         | ••••     |

|   |            | 6.2.1                      | FB_DMAm_Action (Read/Write)                                        | 35       |

|   |            | 6.2.2<br>6.2.3             | FB_DMAM_LAST_ACTION (READ/WRITE)                                   | 35       |

|   |            | 6.2.3<br>6.2.4             | FB_DMAm_Setup (Read/Write) FB_DMAm_Stat_Used (Read/Write)          | 36<br>36 |

|   |            | 6.2.5                      | FB_DMAm_Stat_Invalid (Read/Write)                                  | 36       |

|   |            | 6.2.6                      | FB_DMAm_Stat_Overflow (Read/Write)                                 | 36       |

|   |            | 6.2.7                      | FB_DMAm_Stat_Underflow (Read/Write)                                | 36       |

|   |            | 6.2.8                      | FB_DMAm_Stat_Complete (Read/Write)                                 | 36       |

|   |            | 6.2.9                      | FB_DMAm_Current_Buffer (Read-Only)                                 | 36       |

|   |            | 6.2.10                     | FB_DMAm_COUNT (Read-Only)                                          | 36       |

|   |            | 6.2.11                     | FB_DMAm_RD_FIFO_CNT (Read-Only)                                    | 36       |

|   |            | 6.2.12<br>6.2.13           | FB_DMAm_WR_FIFO_CNT (Read-Only) FB_DMAm_ADDRESSn (Read/Write)      | 37<br>37 |

|   |            | 6.2.14                     | FB_DMAm_SIZEn (Read/Write)                                         | 37       |

|   |            | 6.2.15                     | FB_DMAm_CTRLn (Read/Write)                                         | 37       |

|   |            | 6.2.16                     | FB_DMAm_STATn (Read/Clear)                                         | 37       |

|   | 6.3        | BAR2 – AD                  | DC Functional Block                                                | 38       |

|   | 0.0        | 6.3.1                      | FB_ID (Read-Only)                                                  | 39       |

|   |            | 6.3.2                      | FB_DMA_CHANNELS (Read -Only)                                       | 39       |

|   |            | 6.3.3                      | FB_DMA_BUFFERS (Read-Only)                                         | 39       |

|   |            | 6.3.4                      | Mode_Status (Read/Write, Read-Only)                                | 39       |

|   |            | 6.3.5                      | CLK_SRC (Read/Write)                                               | 40       |

|   |            | 6.3.6<br>6.3.7             | START_TRIG (Read/Write) STOP_TRIG (Read/Write)                     | 40<br>40 |

|   |            | 6.3.8                      | CLK_DIV (Read/Write)                                               | 40       |

|   |            | 6.3.9                      | CLK_DIV_CNTR (Read Only)                                           | 40       |

|   |            | 6.3.10                     | PRE_TRIGGER_CAPTURE (Read/Write)                                   | 40       |

|   |            | 6.3.11                     | POST_STOP_CAPTURE (Read/Write)                                     | 40       |

|   |            | 6.3.12                     | SAMPLE_CNT (Read Only)                                             | 40       |

|   |            | 6.3.13                     | INT_ENA (Maskable Read/Write)                                      | 40       |

|   |            | 6.3.14                     | INT_STAT (Read/Clear)                                              | 40       |

|   |            | 6.3.15<br>6.3.16           | CLK_SRC_GBLn AD_CONFIG (Maskable Read/Write)                       | 41<br>41 |

|   |            | 6.3.10                     | CHn_FRONT_END_CONFIG (Maskable Read/Write)                         | 41       |

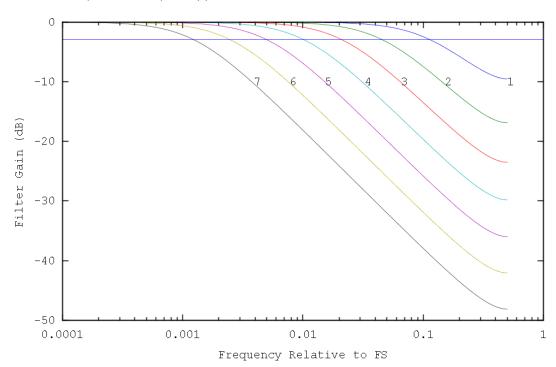

|   |            | 6.3.18                     | CHI_FRONT_END_CONFIG (Maskable Read/Write) CHn_FILTER (Read/Write) | 42       |

|   |            | 6.3.19                     | CHn_THRESH_STAT (Read/Clear)                                       | 43       |

|   |            | 6.3.20                     | CHn_THRESH_ENA (Read/Write)                                        | 43       |

|   |            | 6.3.21                     | CHn_THRESH_LOW (Read/Write)                                        | 43       |

|   |            | 6.3.22                     | CHn_THRESH_HIGH (Read/Write)                                       | 43       |

| 9 | Limited W              | arranty                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                                           |

|---|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   | 8.2                    | PCI and PC                                                                                                                                                                        | I Express Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52                                                                                           |

|   | 8.1                    | PC/104 Spe                                                                                                                                                                        | cifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52                                                                                           |

| 8 | Additional Information |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|   | Troublesh              | •                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51<br>52                                                                                     |

| _ | 6.7                    | 6.7.1<br>6.7.2<br>6.7.3<br>6.7.4                                                                                                                                                  | nperature Sensor Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50<br>50<br>50<br>50                                                                         |

|   | 6.6                    | 6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>6.6.5                                                                                                                                         | erence Adjustment Digital Potentiometer Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49<br>49<br>49<br>49                                                                         |

|   | 6.5                    | 6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5<br>6.5.6                                                                                                                                | ital I/O Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48<br>48<br>48<br>48<br>48                                                                   |

|   |                        | 6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9<br>6.4.10<br>6.4.11<br>6.4.12<br>6.4.13<br>6.4.14<br>6.4.15<br>6.4.16<br>6.4.17<br>6.4.18<br>6.4.19 | FB_ID (Read-Only) FB_DMA_CHANNELS (Read -Only) FB_DMA_BUFFERS (Read-Only) Mode_Status (Read/Write, Read-Only) CLK_SRC (Read/Write) START_TRIG (Read/Write) STOP_TRIG (Read/Write) CLK_DIV (Read/Write) CLK_DIV_CNTR (Read Only) POST_STOP_CONVERSIONS (Read/Write) CONVERSION_CNT (Read Only) INT_ENA (Maskable Read/Write) INT_STAT (Read/Clear) CLK_SRC_GBLn DA_CONFIG (Maskable Read/Write) CH_FRONT_END_CONFIG (Maskable Read/Write) CH_MARKER_STAT (Read/Clear) CH_MARKER_ENA (Read/Clear) CH_LAST_CONVERSIONS (Read/Write) | 44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>46<br>46<br>46<br>46<br>46<br>46<br>47<br>47 |

|   | 6.4                    | DVD3 DV(                                                                                                                                                                          | C Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                                                                                           |

# Table of Figures

| Figure 1: High Speed Mode FFT                              | 12 |

|------------------------------------------------------------|----|

| Figure 2: High Resolution Mode FFT                         | 12 |

| Figure 1: High Speed Mode FFT                              | 13 |

| Figure 4: Board Connections                                | 14 |

| Figure 4: Board Connections<br>Figure 5: Example 104™Stack | 17 |

| Figure 6: IDAN Dimensions                                  | 18 |

| Figure 7: Example IDAN System                              | 27 |

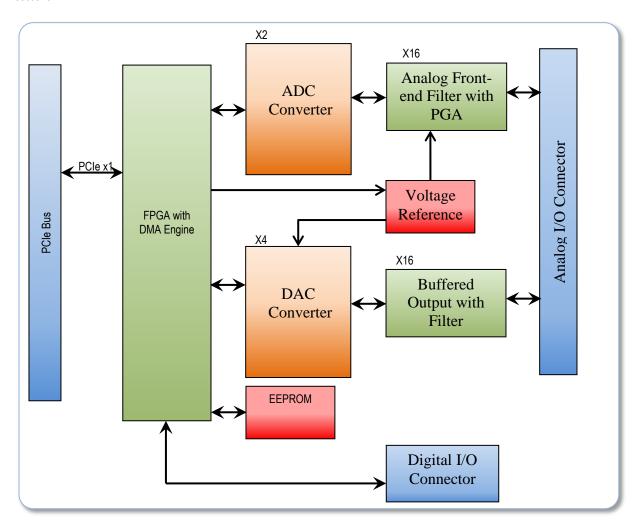

| Figure 8: DM35424 Block Diagram                            | 28 |

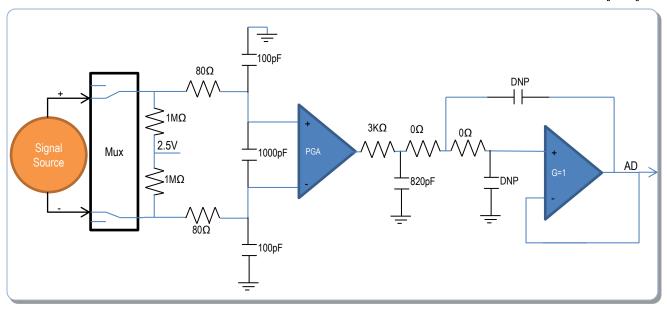

| Figure 9: DM35424 Front-End                                | 29 |

| igure 10: Filter Response with each ORDER Value            | 42 |

# Table of Tables

| Table 1: Ordering Options                                 | 8  |

|-----------------------------------------------------------|----|

| Table 2: Operating Conditions                             | 10 |

| Table 3: Electrical Characteristics                       | 10 |

| Table 4: CN6 Digital I/O Pin Assignments                  | 14 |

| Table 5: CN14 Analog I/O Pin Assignments                  | 15 |

| Table 6: CN24 Analog I/O Pin Assignments                  |    |

| Table 7: CN6 Digital I/O Pin Assignments                  | 15 |

| Table 8: CN14 Analog I/O Pin Assignments                  | 16 |

| Table 9: IDAN- DM35424 68-Pin Subminiature "D" Connector  | 19 |

| Table 10: IDAN- DM35424 68-Pin Subminiature "D" Connector | 20 |

| Table 11: IDAN- DM35424 62-Pin High Density "D" Connector | 21 |

| Table 12: IDAN- DM35424 62-Pin High Density "D" Connector | 22 |

| Table 13: IDAN- DM35424 15-Pin "D" Connector              | 23 |

| Table 14: IDAN- DM35224 68-Pin Subminiature "D" Connector | 24 |

| Table 15: IDAN- DM35224 62-Pin High Density "D" Connector | 25 |

| Table 16: IDAN- DM35224 15-Pin "D" Connector              | 26 |

| Table 17: Corresponding DAC to ADC channel                | 29 |

| Table 18: BAR0                                            | 33 |

| Table 19: DMA Registers                                   | 35 |

| Table 20: Multi-Channel ADC Functional Block              | 38 |

| Table 21: Differential Mode Range/Gain Table              |    |

| Table 22: Single-Ended Mode Range/Gain Table              | 42 |

| Table 23: Multi-Channel DAC Functional Block              | 44 |

| Table 24: Digital I/O Functional Block                    | 48 |

| Table 25: Digital Potentiometer Functional Block          |    |

| Table 26: Temperature Sensor Functional Block             | 50 |

## 1 Introduction

### 1.1 Product Overview

The DM35424 is a software configurable simultaneous sampling data acquisition module. This module provides 16 differential analog input channels, with programmable gains. It also provides 16 individually controlled analog outputs and digital I/O.

The DM35224 is a software configurable simultaneous sampling data acquisition module. This module provides 8 differential analog input channels, with programmable gains. It also provides 8 individually controlled analog outputs and digital I/O.

This board is targeted to sensors that require high precision with a low signal level, such as accelerometers, pressure transducers, and Resistance Temperature Detectors (RTD). The DAC output can provide sufficient current and voltage for the excitation voltage of most sensors.

### 1.2 Board Features

- PCle x 1 Interface

- Universal Board can be used with a PCIe/104 Type 1 or Type 2 host

- Dedicated DMA channel per I/O for maximum efficiency

- Analog Inputs

- o 16 Input Channels (DM35424) / 8 Input Channels (DM35224)

- Programmable Differential or Single Ended

- ±2.5V Differential Analog Input range

- 0-5V Single Ended Input range

- Programmable gains of 1, 2, 4, 8, 16, 32, 64, & 128

- 24-bit delta sigma ADC with simultaneous sampling

- 9.48µs max conversion time (105 KHz throughput)

- Sampling modes and triggers are configurable independently

- Threshold detection can generate an interrupt, or be used as a start or stop trigger

- Configurable IIR filter on each channel

- Analog outputs

- o 16 Single ended channels (DM35424) /8 Single ended channels (DM35224)

- o 16-bit resolution

- 10 μs full-scale settling time (±5V range)

- ±5V output range

- 10mA output current

- Digital I/O

- 14 bits of Digital I/O

- Bit programmable direction

- 5V tolerant

## 1.3 Ordering Information

The DM35424 is available in the following options:

Table 1: Ordering Options

| Part Number        | Description                                                                         |

|--------------------|-------------------------------------------------------------------------------------|

| DM35424HR          | PCIe/104 Analog I/O dataModule                                                      |

| DM35224HR          | PCIe/104 Analog I/O dataModule                                                      |

| IDAN-DM35224HR-62S | PCIe/104 Analog I/O dataModule in IDAN enclosure with 62-pin D-Sub Connector        |

| IDAN-DM35424HR-62S | PCIe/104 Analog I/O dataModule in IDAN enclosure with 62-pin D-Sub Connector        |

| IDAN-DM35224HR-68S | PCIe/104 Analog I/O dataModule in IDAN enclosure with 68-pin High-Density Connector |

| IDAN-DM35424HR-68S | PCIe/104 Analog I/O dataModule in IDAN enclosure with 68-pin High-Density Connector |

#### Note: Throughout this document, DM35424 refers to both DM35424 and DM35224 unless otherwise noted

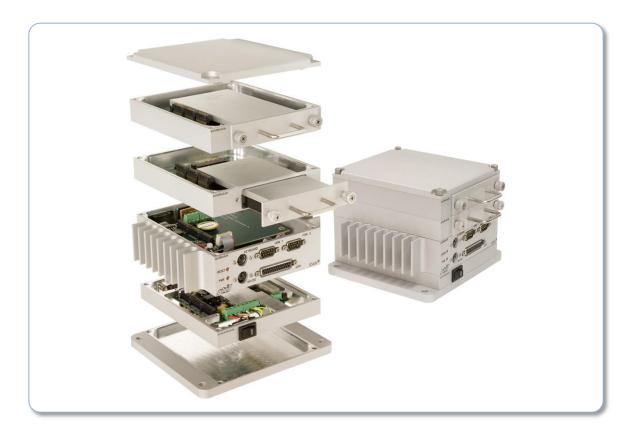

The Intelligent Data Acquisition Node (IDAN™) building block can be used in just about any combination with other IDAN building blocks to create a simple but rugged 104™ stack. This module can also be incorporated in a custom-built RTD HiDAN™ or HiDANplus High Reliability Intelligent Data Acquisition Node. Contact RTD sales for more information on our high reliability systems.

### 1.4 Contact Information

#### 1.4.1 SALES SUPPORT

For sales inquiries, you can contact RTD Embedded Technologies sales via the following methods:

Phone: 1-814-234-8087 Monday through Friday, 8:00am to 5:00pm (EST).

E-Mail: sales@rtd.com

### 1.4.2 TECHNICAL SUPPORT

If you are having problems with you system, please try the steps in the Troubleshooting section of this manual.

For help with this product, or any other product made by RTD, you can contact RTD Embedded Technologies technical support via the following methods:

Phone: 1-814-234-8087 Monday through Friday, 8:00am to 5:00pm (EST).

E-Mail: techsupport@rtd.com

# 2 Specifications

## 2.1 **Operating Conditions**

**Table 2: Operating Conditions**

| Symbol            | Parameter                | Test Condition                                    | Min  | Max  | Unit  |

|-------------------|--------------------------|---------------------------------------------------|------|------|-------|

| V <sub>cc5</sub>  | 5V Supply Voltage        |                                                   | 4.75 | 5.25 | V     |

| $V_{cc3}$         | 3.3V Supply Voltage      |                                                   | n/a  | n/a  | V     |

| V <sub>cc12</sub> | 12V Supply Voltage       |                                                   | n/a  | n/a  | V     |

| Ta                | Operating Temperature    |                                                   | -40  | +85  | С     |

| Ts                | Storage Temperature      |                                                   | -55  | +125 | С     |

| RH                | Relative Humidity        | Non-Condensing                                    | 0    | 90%  | %     |

| MTBF              | Mean Time Before Failure | Telcordia Issue 2 30°C, Ground benign, controlled |      | TBD  | Hours |

### 2.2 Electrical Characteristics

**Table 3: Electrical Characteristics**

| Symbol | Parameter                                | Test Condition                                                              | Min                                                | Тур            | Max                                                      | Unit    |

|--------|------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------|----------------|----------------------------------------------------------|---------|

| Р      | Power Consumption (DM35424)              | $V_{cc5} = 5.0V$                                                            |                                                    | 7.52           |                                                          | W       |

| Icc    | 5V Input Supply Current (DM35424)        | Active                                                                      |                                                    | 1504           |                                                          | mA      |

| Р      | Power Consumption (DM35224)              | V <sub>cc5</sub> = 5.0V                                                     |                                                    | TBD            |                                                          | W       |

| Icc    | 5V Input Supply Current (DM35224)        | Active                                                                      |                                                    | TBD            |                                                          | mA      |

|        |                                          | PCIe/104 Bus                                                                | •                                                  |                |                                                          |         |

|        | Differential Output Voltage              |                                                                             | 0.8                                                |                | 1.2                                                      | V       |

|        | DC Differential TX Impedance             |                                                                             | 80                                                 |                | 120                                                      | Ω       |

|        | Differential Input Voltage               |                                                                             | 0.175                                              |                | 1.2                                                      | V       |

|        | DC Differential RX Impedance             |                                                                             | 80                                                 |                | 120                                                      | Ω       |

|        | Electrical Idle Detect Threshold         |                                                                             | 65                                                 |                | 175                                                      | mV      |

|        |                                          | Analog to Digital Converte                                                  | er                                                 |                |                                                          |         |

|        | Linear Input Voltage                     | IN+ or IN -                                                                 | .05                                                |                | 4.95                                                     | V       |

| FSR    | Full-scale Differential Input Voltage    | V <sub>IN</sub> =(IN+ - IN-)                                                | -2.5 -<br>1LSB                                     |                | +2.5                                                     | V       |

|        | Linear Differential Input Voltage        | V <sub>IN</sub> =(IN+ - IN-)<br>G = PGA Gain                                | $\frac{-2.3}{G}$                                   |                | $\frac{+2.3}{G}$                                         | V       |

|        | Resolution                               |                                                                             |                                                    |                | 24                                                       | Bits    |

|        | Data Rate                                | High-Speed Mode<br>High-Resolution Mode<br>Low-Power Mode<br>Low-Speed Mode |                                                    |                | 105469<br>52734<br>52734<br>10547                        | SPS     |

|        | Passive Filter -3dB Frequency            |                                                                             |                                                    |                | 64                                                       | KHz     |

|        | Internal Filter -3dB Frequency           |                                                                             |                                                    |                | .49 f <sub>DATA</sub>                                    | Hz      |

|        | Internal Filter Stop Band<br>Attenuation | High-Resolution Mode All other modes                                        | 95<br>100                                          |                |                                                          | dB      |

|        | Internal Filter Stop Band                | High-Resolution Mode<br>All other modes                                     | 0.547 f <sub>DATA</sub><br>0.547 f <sub>DATA</sub> |                | 127.453<br>f <sub>DATA</sub><br>63.453 f <sub>DATA</sub> | Hz      |

|        | Front-End Gain Flatness                  | Frequency:0 - 35Khz                                                         |                                                    |                | 1                                                        | dB      |

| _      | Settling Time                            | Complete Settling                                                           |                                                    |                | 78                                                       | Samples |

|        | Delay                                    | High-Resolution Mode All other modes                                        |                                                    |                | 39<br>38                                                 | Samples |

|        | ENOB <sup>(1)</sup>                      | High-Resolution Mode<br>All other modes                                     |                                                    | 15.2<br>15.4   |                                                          | Bits    |

|        | SNR <sup>(1)</sup>                       | High-Resolution Mode<br>All other modes                                     |                                                    | 93.17<br>94.41 |                                                          | dB      |

Table 3: Electrical Characteristics

| Symbol          | Parameter                        | Test Condition               | Min        | Тур   | Max    | Unit |

|-----------------|----------------------------------|------------------------------|------------|-------|--------|------|

|                 | THD <sup>(1)</sup>               | High-Resolution Mode         |            | -     |        | dB   |

|                 |                                  | All other modes              |            | 84.74 |        |      |

|                 |                                  |                              |            | -     |        |      |

|                 |                                  |                              |            | 85.97 |        |      |

|                 | Noise Free Bits <sup>(2)</sup>   | High-Resolution Mode         |            | 15.5  |        | Bits |

|                 |                                  | All other modes              |            | 14.6  |        | Dito |

| G               | Gains                            |                              | 1          |       | 128    |      |

|                 |                                  | Digital to Analog Converte   |            |       |        |      |

|                 | Full-scale Analog Output Voltage |                              | -5.0000    |       | 4.9998 | V    |

|                 | Resolution                       |                              |            |       | 16     | Bits |

| INL             | Relative Accuracy                |                              | -4         |       | +4     | LSB  |

|                 | Full-Scale Accuracy              |                              |            |       |        | LSB  |

|                 | Non-Linearity                    |                              |            |       |        | LSB  |

|                 | Settling Time                    |                              |            |       | 10     | μs   |

|                 | Output Current                   |                              |            |       | 10     | mA   |

|                 | -3dB Frequency                   |                              |            |       | 106440 | Hz   |

|                 | Slew Rate                        |                              |            |       | 5      | V/µs |

|                 |                                  | Digital I/O                  |            |       |        |      |

| $V_{IL}$        | Input High Voltage               |                              | 2          |       | 5      | V    |

| $V_{IH}$        | Input Low Voltage                |                              | -0.5       |       | 0.8    | V    |

| $V_{OL}$        | Output Low Voltage               | I <sub>O</sub> =-12mA        | 0.0        |       | 0.4    | V    |

| V <sub>OH</sub> | Output High Voltage              | $I_0 = -12mA$                | 2.6        |       | 3.3    | V    |

|                 | Refer                            | ence Adjustment Digital Pote | entiometer |       |        |      |

|                 | Settling Time                    | Change from 0x0 –<br>0xFF    |            |       | 0.5    | μs   |

|                 | Write to Nonvolatile             |                              |            |       | 12     | ms   |

|                 | Read Nonvolatile                 |                              |            |       | 1      | μs   |

|                 | Write to Output                  |                              |            |       | 1      | μs   |

$<sup>^{\</sup>rm 1}$  Calculated with Input = -1.2 dbFS @ 1 KHz, Max Sample Rate  $^{\rm 2}$  Calculated with Inputs grounded, Max Sample Rate

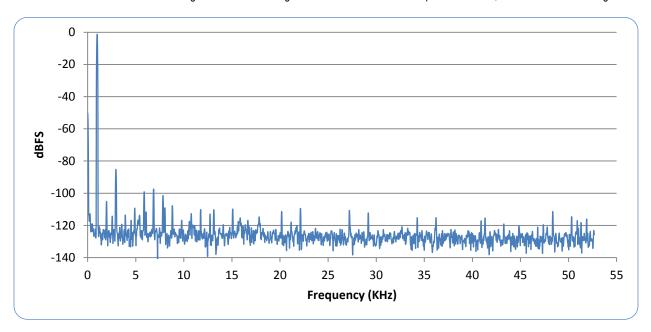

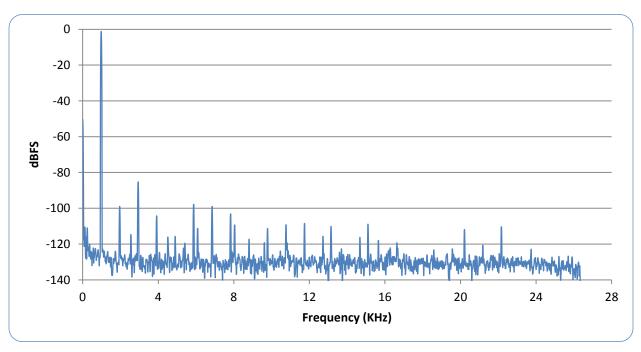

### 2.2.1 ANALOG INPUT FFT PLOTS

In Figure 1, the ADC was set to high speed mode and a coherent 1KHz sine wave signal was attached to input ADC0 Channel 0. The FFT absolute value was calculated using a Blackman-Hanning three term window. Three samples were taken, and the FFT data averaged.

In Figure 2, the ADC was set to high resolution mode and a coherent 1KHz sine wave signal was attached to input ADC0 Channel 0. The FFT absolute value was calculated using a Blackman-Hanning three term window. Three samples were taken, and the FFT data averaged.

Figure 1: High Speed Mode FFT

Figure 2: High Resolution Mode FFT

# 3 Board Connection

### 3.1 **Board Handling Precautions**

To prevent damage due to Electrostatic Discharge (ESD), keep your board in its antistatic bag until you are ready to install it into your system. When removing it from the bag, hold the board at the edges, and do not touch the components or connectors. Handle the board in an antistatic environment, and use a grounded workbench for testing and handling of your hardware.

### 3.2 Physical Characteristics

- Weight: Approximately 80 g (0.18 lbs.)

- Dimensions: 90.17 mm L x 95.89 mm W (3.550 in L x 3.775 in W)

Figure 3: Board Dimensions

### 3.3 Connectors and Jumpers

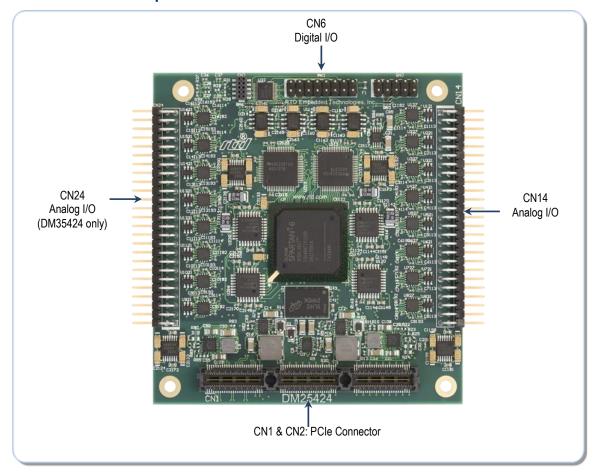

Figure 4: Board Connections

### 3.3.1 Bus Connectors

### CN1(Top) & CN2(Bottom): PCIe Connector

The PCIe connector is the connection to the system CPU. The position and pin assignments are compliant with the *PCI/104-Express Specification*. (See <u>PC/104 Specifications</u> on page 52)

The DM35424 is a "Universal" board, and can connect to either a Type 1 or Type 2 PCIe/104 connector.

### 3.3.2 DM35424 EXTERNAL I/O CONNECTORS

#### Digital I/O Connectors: CN6

$\mbox{CN6}$  contains one 14 bit port of digital I/O. The pin assignment is listed below.

Table 4: CN6 Digital I/O Pin Assignments

| PORT0_1  | 2  | 1  | PORT0_0  |

|----------|----|----|----------|

| PORT0_3  | 4  | 3  | PORT0_2  |

| PORT0_5  | 6  | 5  | PORT0_4  |

| PORT0_7  | 8  | 7  | PORT0_6  |

| PORT0_9  | 10 | 9  | PORT0_8  |

| PORT0_11 | 12 | 11 | PORT0_10 |

| PORT0_13 | 14 | 13 | PORT0_12 |

| +5V      | 16 | 15 | GND      |

#### Analog I/O Connectors: CN14 and CN24

**AGND**

**AGND**

**AGND**

AGND

AGND

AGND

**AGND**

**AGND**

**AGND**

**AGND**

**AGND**

**AGND**

**AGND**

AGND

AGND

AGND

CN14 and CN24 contain the signals for the 16 analog I/O channels. The pin assignment is listed below.

Table 5: CN14 Analog I/O Pin Assignments

**AGND** 3 DAC0 Channel 0 ADC0 Channel 0-6 5 ADC0 Channel 0+ 8 AGND DAC0 Channel 1 10 9 ADC0 Channel1-12 11 ADC0 Channel 1+ 14 13 **AGND** 16 15 DAC0 Channel 2 ADC0 Channel 2-18 17 ADC0 Channel 2+ 20 19 **AGND** 22 21 DAC0 Channel 3 ADC0 Channel 3-24 23 ADC0 Channel 3+ 25 AGND 26 AGND 27 DAC1 Channel 0 28 ADC0 Channel 4-30 29 ADC0 Channel 4+ 32 31 AGND 34 33 DAC1 Channel 1 ADC0 Channel 5-36 35 ADC0 Channel 5+ 38 37 AGND 40 39 DAC1 Channel 2 ADC0 Channel 6-42 41 ADC0 Channel 6+ 44 43 AGND 46 45 DAC1 Channel 3 ADC0 Channel 7-47 48 ADC0 Channel 7+ 50 49 AGND

Table 6: CN24 Analog I/O Pin Assignments

| AGND            | 2  | 1  | AGND            |

|-----------------|----|----|-----------------|

| AGND            | 4  | 3  | DAC2 Channel 0  |

| ADC1 Channel 0- | 6  | 5  | ADC1 Channel 0+ |

| AGND            | 8  | 7  | AGND            |

| AGND            | 10 | 9  | DAC2 Channel 1  |

| ADC1 Channel1-  | 12 | 11 | ADC1 Channel 1+ |

| AGND            | 14 | 13 | AGND            |

| AGND            | 16 | 15 | DAC2 Channel 2  |

| ADC1 Channel 2- | 18 | 17 | ADC1 Channel 2+ |

| AGND            | 20 | 19 | AGND            |

| AGND            | 22 | 21 | DAC2 Channel 3  |

| ADC1 Channel 3- | 24 | 23 | ADC1 Channel 3+ |

| AGND            | 26 | 25 | AGND            |

| AGND            | 28 | 27 | DAC3 Channel 0  |

| ADC1 Channel 4- | 30 | 29 | ADC1 Channel 4+ |

| AGND            | 32 | 31 | AGND            |

| AGND            | 34 | 33 | DAC3 Channel 1  |

| ADC1 Channel 5- | 36 | 35 | ADC1 Channel 5+ |

| AGND            | 38 | 37 | AGND            |

| AGND            | 40 | 39 | DAC3 Channel 2  |

| ADC1 Channel 6- | 42 | 41 | ADC1 Channel 6+ |

| AGND            | 44 | 43 | AGND            |

| AGND            | 46 | 45 | DAC3 Channel 3  |

| ADC1 Channel 7- | 48 | 47 | ADC1 Channel 7+ |

| AGND            | 50 | 49 | AGND            |

Note: CN3 is for Factory Use only

#### 3.3.3 DM35224 EXTERNAL I/O CONNECTORS

#### Digital I/O Connectors: CN6

CN6 contains one 14 bit port of digital I/O. The pin assignment is listed below.

Table 7: CN6 Digital I/O Pin Assignments

| PORT0_1  | 2  | 1  | PORT0_0  |

|----------|----|----|----------|

| PORT0_3  | 4  | 3  | PORT0_2  |

| PORT0_5  | 6  | 5  | PORT0_4  |

| PORT0_7  | 8  | 7  | PORT0_6  |

| PORT0_9  | 10 | 9  | PORT0_8  |

| PORT0_11 | 12 | 11 | PORT0_10 |

| PORT0_13 | 14 | 13 | PORT0_12 |

| +5V      | 16 | 15 | GND      |

### Analog I/O Connectors: CN14

CN14 contain the signals for the 16 analog I/O channels. The pin assignment is listed below.

Table 8: CN14 Analog I/O Pin Assignments

| AGND            | 2  | 1  | AGND            |  |

|-----------------|----|----|-----------------|--|

| AGND            | 4  | 3  | DAC0 Channel 0  |  |

| ADC0 Channel 0- | 6  | 5  | ADC0 Channel 0+ |  |

| AGND            | 8  | 7  | AGND            |  |

| AGND            | 10 | 9  | DAC0 Channel 1  |  |

| ADC0 Channel1-  | 12 | 11 | ADC0 Channel 1+ |  |

| AGND            | 14 | 13 | AGND            |  |

| AGND            | 16 | 15 | DAC0 Channel 2  |  |

| ADC0 Channel 2- | 18 | 17 | ADC0 Channel 2+ |  |

| AGND            | 20 | 19 | AGND            |  |

| AGND            | 22 | 21 | DAC0 Channel 3  |  |

| ADC0 Channel 3- | 24 | 23 | ADC0 Channel 3+ |  |

| AGND            | 26 | 25 | AGND            |  |

| AGND            | 28 | 27 | DAC1 Channel 0  |  |

| ADC0 Channel 4- | 30 | 29 | ADC0 Channel 4+ |  |

| AGND            | 32 | 31 | AGND            |  |

| AGND            | 34 | 33 | DAC1 Channel 1  |  |

| ADC0 Channel 5- | 36 | 35 | ADC0 Channel 5+ |  |

| AGND            | 38 | 37 | AGND            |  |

| AGND            | 40 | 39 | DAC1 Channel 2  |  |

| ADC0 Channel 6- | 42 | 41 | ADC0 Channel 6+ |  |

| AGND            | 44 | 43 | AGND            |  |

| AGND            | 46 | 45 | DAC1 Channel 3  |  |

| ADC0 Channel 7- | 48 | 47 | ADC0 Channel 7+ |  |

| AGND            | 50 | 49 | AGND            |  |

Note: CN3 is for Factory Use only

### 3.3.4 JUMPERS

There are no jumpers on the DM35424.

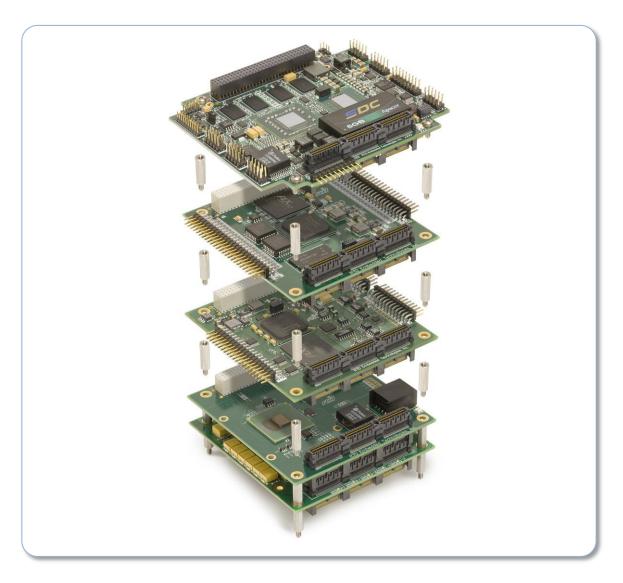

### 3.4 Steps for Installing

- 1. Always work at an ESD protected workstation, and wear a grounded wrist-strap.

- 2. Turn off power to the PC/104 system or stack.

- 3. Select and install stand-offs to properly position the module on the stack.

- 4. Remove the module from its anti-static bag.

- 5. Check that pins of the bus connector are properly positioned.

- 6. Check the stacking order; make sure all of the busses used by the peripheral cards are connected to the cpuModule.

- 7. Hold the module by its edges and orient it so the bus connector pins line up with the matching connector on the stack.

- 8. Gently and evenly press the module onto the PC/104 stack.

- 9. If any boards are to be stacked above this module, install them.

- 10. Attach any necessary cables to the PC/104 stack.

- 11. Re-connect the power cord and apply power to the stack.

- 12. Boot the system and verify that all of the hardware is working properly.

Figure 5: Example 104™ Stack

# 4 IDAN Connections

## 4.1 Module Handling Precautions

To prevent damage due to Electrostatic Discharge (ESD), keep your module in its antistatic bag until you are ready to install it into your system. When removing it from the bag, hold the module by the aluminum enclosure, and do not touch the components or connectors. Handle the module in an antistatic environment, and use a grounded workbench for testing and handling of your hardware.

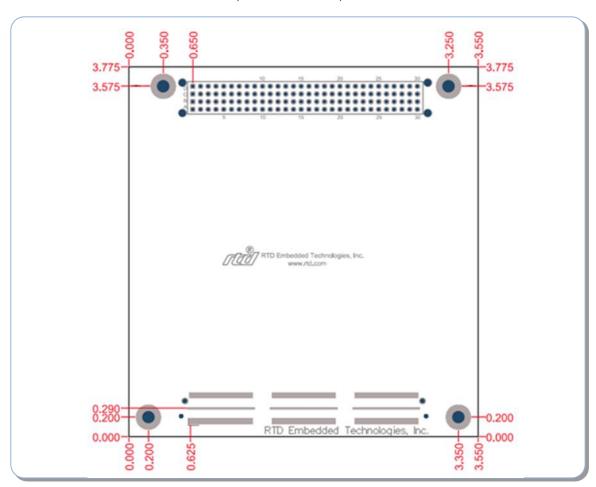

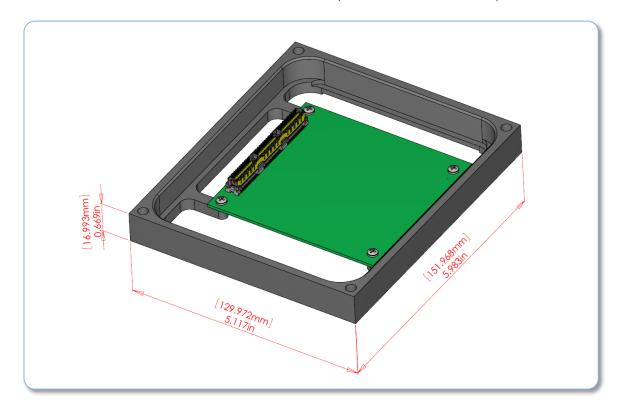

### 4.2 Physical Characteristics

- Weight: Approximately 0.21 Kg (0.46 lbs.)

- Dimensions: 151.972 mm L x 129.978 mm W x 16.993 mm H (5.983 in L x 5.117 in W x 0.669 in H)

Figure 6: IDAN Dimensions

### 4.3 **Connectors**

### 4.3.1 DM35424 EXTERNAL I/O CONNECTORS

### AIO 1-8 Connector - 68-pin Subminiature "D" Female Connector

Connector Part #: Amp 749070-7 Sample Mating Connector: Amp 786090-7(IDC Crimp)

Table 9: IDAN- DM35424 68-Pin Subminiature "D" Connector

Table 9: IDAN- DM35424 68-Pin Subminiature "D" Connector

| IDAN Pin# | Signal          | DM35424 Pin # |    |  |

|-----------|-----------------|---------------|----|--|

| 1         | AGND            | CN14          | 1  |  |

| 2         | AGND            | CN14          | 2  |  |

| 3         | DAC0 Channel 0  | CN14          | 3  |  |

| 4         | AGND            | CN14          | 4  |  |

| 5         | ADC0 Channel 0+ | CN14          | 5  |  |

| 6         | ADC0 Channel 0- | CN14          | 6  |  |

| 7         | AGND            | CN14          | 7  |  |

| 8         | AGND            | CN14          | 8  |  |

| 9         | DAC0 Channel 2  | CN14          | 9  |  |

| 10        | AGND            | CN14          | 10 |  |

| 11        | ADC0 Channel 1+ | CN14          | 11 |  |

| 12        | ADC0 Channel 1- | CN14          | 12 |  |

| 13        | AGND            | CN14          | 13 |  |

| 4         | AGND            | CN14          | 14 |  |

| 15        | DAC0 Channel 2  | CN14          | 15 |  |

| 16        | AGND            | CN14          | 16 |  |

| 17        | ADC0 Channel 2+ | CN14          | 17 |  |

| 18        | ADC0 Channel 2- | CN14          | 18 |  |

| 19        | AGND            | CN14          | 19 |  |

| 20        | AGND            | CN14          | 20 |  |

| 21        | DAC0 Channel 3  | CN14          | 21 |  |

| 22        | AGND            | CN14          | 22 |  |

| 23        | ADC0 Channel 3+ | CN14          | 23 |  |

| 24        | ADC0 Channel 3- | CN14          | 24 |  |

| 25        | AGND            | CN14          | 25 |  |

| 26        | AGND            | CN14          | 26 |  |

| 27        | DAC1 Channel 0  | CN14          | 27 |  |

| 28        | AGND            | CN14          | 28 |  |

| 29        | ADC0 Channel 4+ | CN14          | 29 |  |

| 30        | ADC0 Channel 4- | CN14          | 30 |  |

| 31        | AGND            | CN14          | 31 |  |

| 32        | AGND            | CN14          | 32 |  |

| 33        | DAC1 Channel 1  | CN14          | 33 |  |

| 34        | AGND            | CN14          | 34 |  |

| IDAN Pin# | Signal          | DM35424 Pin # |    |  |

|-----------|-----------------|---------------|----|--|

| 35        | ADC0 Channel 5+ | CN14          | 35 |  |

| 36        | ADC0 Channel 5- | CN14          | 36 |  |

| 37        | AGND            | CN14          | 37 |  |

| 38        | AGND            | CN14          | 38 |  |

| 39        | DAC1 Channel 2  | CN14          | 39 |  |

| 40        | AGND            | CN14          | 40 |  |

| 41        | ADC0 Channel 6+ | CN14          | 41 |  |

| 42        | ADC0 Channel 6- | CN14          | 42 |  |

| 43        | AGND            | CN14          | 43 |  |

| 44        | AGND            | CN14          | 44 |  |

| 45        | DAC1 Channel 3  | CN14          | 45 |  |

| 46        | AGND            | CN14          | 46 |  |

| 47        | ADC0 Channel 7+ | CN14          | 47 |  |

| 48        | ADC0 Channel 7- | CN14          | 48 |  |

| 49        | AGND            | CN14          | 49 |  |

| 50        | AGND            | CN14          | 50 |  |

| 51        | N/C             |               |    |  |

| 52        | N/C             |               |    |  |

| 53        | N/C             |               |    |  |

| 54        | N/C             |               |    |  |

| 55        | N/C             |               |    |  |

| 56        | N/C             |               |    |  |

| 57        | N/C             |               |    |  |

| 58        | N/C             |               |    |  |

| 59        | N/C             |               |    |  |

| 60        | N/C             |               |    |  |

| 61        | N/C             |               |    |  |

| 62        | N/C             |               |    |  |

| 63        | N/C             |               |    |  |

| 64        | N/C             |               |    |  |

| 65        | N/C             |               |    |  |

| 66        | N/C             |               |    |  |

| 67        | N/C             |               |    |  |

| 68        | N/C             |               |    |  |

### AIO 5-16 Connector - 68-pin Subminiature "D" Female Connector

Connector Part #: Amp 749070-7 Sample Mating Connector: Amp 786090-7(IDC Crimp)

Table 10: IDAN- DM35424 68-Pin Subminiature "D" Connector

Table 10: IDAN- DM35424 68-Pin Subminiature "D" Connector

| IDAN Pin# | Signal          | DM35424 Pin # |    |  |

|-----------|-----------------|---------------|----|--|

| 1         | AGND            | CN24          | 1  |  |

| 2         | AGND            | CN24          | 2  |  |

| 3         | DAC2 Channel 0  | CN24          | 3  |  |

| 4         | AGND            | CN24          | 4  |  |

| 5         | ADC1 Channel 0+ | CN24          | 5  |  |

| 6         | ADC1 Channel 0- | CN24          | 6  |  |

| 7         | AGND            | CN24          | 7  |  |

| 8         | AGND            | CN24          | 8  |  |

| 9         | DAC2 Channel 2  | CN24          | 9  |  |

| 10        | AGND            | CN24          | 10 |  |

| 11        | ADC1 Channel 1+ | CN24          | 11 |  |

| 12        | ADC1 Channel 1- | CN24          | 12 |  |

| 13        | AGND            | CN24          | 13 |  |

| 4         | AGND            | CN24          | 14 |  |

| 15        | DAC2 Channel 2  | CN24          | 15 |  |

| 16        | AGND            | CN24          | 16 |  |

| 17        | ADC1 Channel 2+ | CN24          | 17 |  |

| 18        | ADC1 Channel 2- | CN24          | 18 |  |

| 19        | AGND            | CN24          | 19 |  |

| 20        | AGND            | CN24          | 20 |  |

| 21        | DAC2 Channel 3  | CN24          | 21 |  |

| 22        | AGND            | CN24          | 22 |  |

| 23        | ADC1 Channel 3+ | CN24          | 23 |  |

| 24        | ADC1 Channel 3- | CN24          | 24 |  |

| 25        | AGND            | CN24          | 25 |  |

| 26        | AGND            | CN24          | 26 |  |

| 27        | DAC3 Channel 0  | CN24          | 27 |  |

| 28        | AGND            | CN24          | 28 |  |

| 29        | ADC1 Channel 4+ | CN24          | 29 |  |

| 30        | ADC1 Channel 4- | CN24          | 30 |  |

| 31        | AGND            | CN24          | 31 |  |

| 32        | AGND            | CN24          | 32 |  |

| 33        | DAC3 Channel 1  | CN24          | 33 |  |

| 34        | AGND            | CN24          | 34 |  |

| IDAN Pin# | Signal          | DM35424 Pin # |    |  |

|-----------|-----------------|---------------|----|--|

| 35        | ADC1 Channel 5+ | CN24          | 35 |  |

| 36        | ADC1 Channel 5- | CN24          | 36 |  |

| 37        | AGND            | CN24          | 37 |  |

| 38        | AGND            | CN24          | 38 |  |

| 39        | DAC3 Channel 2  | CN24          | 39 |  |

| 40        | AGND            | CN24          | 40 |  |

| 41        | ADC1 Channel 6+ | CN24          | 41 |  |

| 42        | ADC1 Channel 6- | CN24          | 42 |  |

| 43        | AGND            | CN24          | 43 |  |

| 44        | AGND            | CN24          | 44 |  |

| 45        | DAC3 Channel 3  | CN24          | 45 |  |

| 46        | AGND            | CN24          | 46 |  |

| 47        | ADC1 Channel 7+ | CN24          | 47 |  |

| 48        | ADC1 Channel 7- | CN24          | 48 |  |

| 49        | AGND            | CN24          | 49 |  |

| 50        | AGND            | CN24          | 50 |  |

| 51        | N/C             |               |    |  |

| 52        | N/C             |               |    |  |

| 53        | N/C             |               |    |  |

| 54        | N/C             |               |    |  |

| 55        | N/C             |               |    |  |

| 56        | N/C             |               |    |  |

| 57        | N/C             |               |    |  |

| 58        | N/C             |               |    |  |

| 59        | N/C             |               |    |  |

| 60        | N/C             |               |    |  |

| 61        | N/C             |               |    |  |

| 62        | N/C             |               |    |  |

| 63        | N/C             |               |    |  |

| 64        | N/C             |               |    |  |

| 65        | N/C             |               |    |  |

| 66        | N/C             |               |    |  |

| 67        | N/C             |               |    |  |

| 68        | N/C             |               |    |  |

### AIO 1-8 Connector - 62-pin High Density "D" Female Connector

Connector Part #: VALCONN HDB-62S Sample Mating Connector: VALCONN HDB-62P

Table 11: IDAN- DM35424 62-Pin High Density "D" Connector

Table 11: IDAN- DM35424 62-Pin High Density "D" Connector

| Table 11. IDAN- Dinos-124 02-1 III Thigh Density D Connector |                 |               |    |  |  |

|--------------------------------------------------------------|-----------------|---------------|----|--|--|

| IDAN Pin#                                                    | Signal          | DM35424 Pin # |    |  |  |

| 1                                                            | AGND            | CN14          | 1  |  |  |

| 2                                                            | AGND            | CN14          | 4  |  |  |

| 3                                                            | AGND            | CN14          | 7  |  |  |

| 4                                                            | AGND            | CN14          | 10 |  |  |

| 5                                                            | AGND            | CN14          | 13 |  |  |

| 6                                                            | AGND            | CN14          | 16 |  |  |

| 7                                                            | AGND            | CN14          | 19 |  |  |

| 8                                                            | AGND            | CN14          | 22 |  |  |

| 9                                                            | AGND            | CN14          | 25 |  |  |

| 10                                                           | AGND            | CN14          | 28 |  |  |

| 11                                                           | AGND            | CN14          | 31 |  |  |

| 12                                                           | AGND            | CN14          | 34 |  |  |

| 13                                                           | AGND            | CN14          | 37 |  |  |

| 14                                                           | AGND            | CN14          | 40 |  |  |

| 15                                                           | AGND            | CN14          | 43 |  |  |

| 16                                                           | AGND            | CN14          | 46 |  |  |

| 17                                                           | AGND            | CN14          | 49 |  |  |

| 18                                                           | Reserved        |               |    |  |  |

| 19                                                           | Reserved        |               |    |  |  |

| 20                                                           |                 | Reserved      |    |  |  |

| 21                                                           |                 | Reserved      |    |  |  |

| 22                                                           | AGND            | CN14          | 2  |  |  |

| 23                                                           | ADC0 Channel 0+ | CN14          | 5  |  |  |

| 24                                                           | AGND            | CN14          | 8  |  |  |

| 25                                                           | ADC0 Channel 1+ | CN14          | 11 |  |  |

| 26                                                           | AGND            | CN14          | 14 |  |  |

| 27                                                           | ADC0 Channel 2+ | CN14          | 17 |  |  |

| 28                                                           | AGND            | CN14          | 20 |  |  |

| 29                                                           | ADC0 Channel 3+ | CN14          | 23 |  |  |

| 30                                                           | AGND CN14       |               | 26 |  |  |

| 31                                                           | ADC0 Channel 4+ | CN14          | 29 |  |  |

| IDAN Pin# | Signal          | DM35424 Pin # |    |  |

|-----------|-----------------|---------------|----|--|

| 32        | AGND            | CN14          | 32 |  |

| 33        | ADC0 Channel 5+ | CN14          | 35 |  |

| 34        | AGND            | CN14          | 38 |  |

| 35        | ADC0 Channel 6+ | CN14          | 41 |  |

| 36        | AGND            | CN14          | 44 |  |

| 37        | ADC0 Channel 7+ | CN14          | 47 |  |

| 38        | AGND            | CN14          | 50 |  |

| 39        |                 | Reserved      |    |  |

| 40        |                 | Reserved      |    |  |

| 41        |                 | Reserved      |    |  |

| 42        |                 | Reserved      |    |  |

| 43        | DAC0 Channel 0  | CN14          | 3  |  |

| 44        | ADC0 Channel 0- | CN14          | 6  |  |

| 45        | DAC0 Channel 1  | CN14          | 9  |  |

| 46        | ADC0 Channel 1- | CN14          | 12 |  |

| 47        | DAC0 Channel 2  | CN14          | 15 |  |

| 48        | ADC0 Channel 2- | CN14          | 18 |  |

| 49        | DAC0 Channel 3  | CN14          | 21 |  |

| 50        | ADC0 Channel 3- | CN14          | 24 |  |

| 51        | DAC1 Channel 0  | CN14          | 27 |  |

| 52        | ADC0 Channel 4- | CN14          | 30 |  |

| 53        | DAC1 Channel 1  | CN14          | 33 |  |

| 54        | ADC0 Channel 5- | CN14          | 36 |  |

| 55        | DAC1 Channel 2  | CN14          | 39 |  |

| 56        | ADC0 Channel 6- | CN14          | 42 |  |

| 57        | DAC1 Channel 3  | CN14          | 45 |  |

| 58        | ADC0 Channel 7- | CN14          | 48 |  |

| 59        | Reserved        |               |    |  |

| 60        | Reserved        |               |    |  |

| 61        | Reserved        |               |    |  |

| 62        | Reserved        |               |    |  |

### AIO 5-16 Connector - 62-pin High Density "D" Female Connector

Connector Part #: VALCONN HDB-62S Sample Mating Connector: VALCONN HDB-62P

Table 12: IDAN- DM35424 62-Pin High Density "D" Connector

Table 12: IDAN- DM35424 62-Pin High Density "D" Connector

| IDAN Pin# | Signal DM35424 Pin # |          |    |  |  |

|-----------|----------------------|----------|----|--|--|

| 1         | AGND                 | CN24     | 1  |  |  |

| 2         | AGND                 | CN24     | 4  |  |  |

| 3         | AGND                 | CN24     | 7  |  |  |

| 4         | AGND                 | CN24     | 10 |  |  |

| 5         | AGND                 | CN24     | 13 |  |  |

| 6         | AGND                 | CN24     | 16 |  |  |

| 7         | AGND                 | CN24     | 19 |  |  |

| 8         | AGND                 | CN24     | 22 |  |  |

| 9         | AGND                 | CN24     | 25 |  |  |

| 10        | AGND                 | CN24     | 28 |  |  |

| 11        | AGND                 | CN24     | 31 |  |  |

| 12        | AGND                 | CN24     | 34 |  |  |

| 13        | AGND                 | CN24     | 37 |  |  |

| 14        | AGND                 | CN24     | 40 |  |  |

| 15        | AGND                 | CN24     | 43 |  |  |

| 16        | AGND                 | CN24     | 46 |  |  |

| 17        | AGND                 | CN24     | 49 |  |  |

| 18        | Reserved             |          |    |  |  |

| 19        |                      | Reserved |    |  |  |

| 20        |                      | Reserved |    |  |  |

| 21        |                      | Reserved |    |  |  |

| 22        | AGND                 | CN24     | 2  |  |  |

| 23        | ADC1 Channel 0+      | CN24     | 5  |  |  |

| 24        | AGND                 | CN24     | 8  |  |  |

| 25        | ADC1 Channel 1+      | CN24     | 11 |  |  |

| 26        | AGND                 | CN24     | 14 |  |  |

| 27        | ADC1 Channel 2+      | CN24     | 17 |  |  |

| 28        | AGND                 | CN24     | 20 |  |  |

| 29        | ADC1 Channel 3+      | CN24     | 23 |  |  |

| 30        | AGND                 | CN24     | 26 |  |  |

| 31        | ADC1 Channel 4+      | CN24     | 29 |  |  |

| IDAN Pin# | Signal          | Signal DM35424 Pin # |    |  |

|-----------|-----------------|----------------------|----|--|

| 32        | AGND            | CN24                 | 32 |  |

| 33        | ADC1 Channel 5+ | CN24                 | 35 |  |

| 34        | AGND            | CN24                 | 38 |  |

| 35        | ADC1 Channel 6+ | CN24                 | 41 |  |

| 36        | AGND            | CN24                 | 44 |  |

| 37        | ADC1 Channel 7+ | CN24                 | 47 |  |

| 38        | AGND            | CN24                 | 50 |  |

| 39        |                 | Reserved             |    |  |

| 40        |                 | Reserved             |    |  |

| 41        |                 | Reserved             |    |  |

| 42        |                 | Reserved             |    |  |

| 43        | DAC2 Channel 0  | CN24                 | 3  |  |

| 44        | ADC1 Channel 0- | CN24                 | 6  |  |

| 45        | DAC2 Channel 1  | CN24                 | 9  |  |

| 46        | ADC1 Channel 1- | CN24                 | 12 |  |

| 47        | DAC2 Channel 2  | CN24                 | 15 |  |

| 48        | ADC1 Channel 2- | CN24                 | 18 |  |

| 49        | DAC2 Channel 3  | CN24                 | 21 |  |

| 50        | ADC1 Channel 3- | CN24                 | 24 |  |

| 51        | DAC3 Channel 0  | CN24                 | 27 |  |

| 52        | ADC1 Channel 4- | CN24                 | 30 |  |

| 53        | DAC3 Channel 1  | CN24                 | 33 |  |

| 54        | ADC1 Channel 5- | CN24                 | 36 |  |

| 55        | DAC3 Channel 2  | CN24                 | 39 |  |

| 56        | ADC1 Channel 6- | CN24                 | 42 |  |

| 57        | DAC3 Channel 3  | CN24                 | 45 |  |

| 58        | ADC1 Channel 7- | CN24                 | 48 |  |

| 59        | Reserved        |                      |    |  |

| 60        | Reserved        |                      |    |  |

| 61        | Reserved        |                      |    |  |

| 62        | Reserved        |                      |    |  |

### DIO Connectors - 15-pin "D" Female Connector

Connector Part #: Amp 747052-3 Sample Mating Connector: Amp 1658611-3

Table 13: IDAN- DM35424 15-Pin "D" Connector

| IDAN Pin# | Signal   | DM35424 | Pin# |

|-----------|----------|---------|------|

| 1         | PORTO_0  | CN6     | 1    |

| 2         | PORT0_2  | CN6     | 3    |

| 3         | PORT0_4  | CN6     | 5    |

| 4         | PORTO_6  | CN6     | 7    |

| 5         | PORT0_8  | CN6     | 9    |

| 6         | PORTO_10 | CN6     | 11   |

| 7         | PORT0_12 | CN6     | 13   |

| 8         | GND      | CN6     | 15   |

| 9         | PORT0_1  | CN6     | 2    |

| 10        | PORT0_3  | CN6     | 4    |

| 11        | PORT0_5  | CN6     | 6    |

| 12        | PORT0_7  | CN6     | 8    |

| 13        | PORT0_9  | CN6     | 10   |

| 14        | PORT0_11 | CN6     | 12   |

| 15        | PORT0_13 | CN6     | 14   |

### 4.3.2 DM35224 EXTERNAL I/O CONNECTORS

### AIO 1-8 Connector - 68-pin Subminiature "D" Female Connector

Connector Part #: Amp 749070-7 Sample Mating Connector: Amp 786090-7(IDC Crimp)

Table 14: IDAN- DM35224 68-Pin Subminiature "D" Connector

Table 14: IDAN- DM35224 68-Pin Subminiature "D" Connector

| IDAN Pin# | Signal          |      | DM35224 Pin # | IDAN Pin# | Signal          | D    | M35224 Pin # |

|-----------|-----------------|------|---------------|-----------|-----------------|------|--------------|

| 1         | AGND            | CN14 | 1             | 35        | ADC0 Channel 5+ | CN14 | 35           |

| 2         | AGND            | CN14 | 2             | 36        | ADC0 Channel 5- | CN14 | 36           |

| 3         | DAC0 Channel 0  | CN14 | 3             | 37        | AGND            | CN14 | 37           |

| 4         | AGND            | CN14 | 4             | 38        | AGND            | CN14 | 38           |

| 5         | ADC0 Channel 0+ | CN14 | 5             | 39        | DAC1 Channel 2  | CN14 | 39           |

| 6         | ADC0 Channel 0- | CN14 | 6             | 40        | AGND            | CN14 | 40           |

| 7         | AGND            | CN14 | 7             | 41        | ADC0 Channel 6+ | CN14 | 41           |

| 8         | AGND            | CN14 | 8             | 42        | ADC0 Channel 6- | CN14 | 42           |

| 9         | DAC0 Channel 2  | CN14 | 9             | 43        | AGND            | CN14 | 43           |

| 10        | AGND            | CN14 | 10            | 44        | AGND            | CN14 | 44           |

| 11        | ADC0 Channel 1+ | CN14 | 11            | 45        | DAC1 Channel 3  | CN14 | 45           |

| 12        | ADC0 Channel 1- | CN14 | 12            | 46        | AGND            | CN14 | 46           |

| 13        | AGND            | CN14 | 13            | 47        | ADC0 Channel 7+ | CN14 | 47           |

| 14        | AGND            | CN14 | 14            | 48        | ADC0 Channel 7- | CN14 | 48           |

| 15        | DAC0 Channel 2  | CN14 | 15            | 49        | AGND            | CN14 | 49           |

| 16        | AGND            | CN14 | 16            | 50        | AGND            | CN14 | 50           |

| 17        | ADC0 Channel 2+ | CN14 | 17            | 51        | N/C             |      |              |

| 18        | ADC0 Channel 2- | CN14 | 18            | 52        | N/C             |      |              |

| 19        | AGND            | CN14 | 19            | 53        | N/C             |      |              |

| 20        | AGND            | CN14 | 20            | 54        | N/C             |      |              |

| 21        | DAC0 Channel 3  | CN14 | 21            | 55        | N/C             |      |              |

| 22        | AGND            | CN14 | 22            | 56        | N/C             |      |              |

| 23        | ADC0 Channel 3+ | CN14 | 23            | 57        | N/C             |      |              |

| 24        | ADC0 Channel 3- | CN14 | 24            | 58        | N/C             |      |              |

| 25        | AGND            | CN14 | 25            | 59        | N/C             |      |              |

| 26        | AGND            | CN14 | 26            | 60        | N/C             |      |              |

| 27        | DAC1 Channel 0  | CN14 | 27            | 61        | N/C             |      |              |

| 28        | AGND            | CN14 | 28            | 62        | N/C             |      |              |

| 29        | ADC0 Channel 4+ | CN14 | 29            | 63        | N/C             |      |              |

| 30        | ADC0 Channel 4- | CN14 | 30            | 64        | N/C             |      |              |

| 31        | AGND            | CN14 | 31            | 65        | N/C             |      |              |

| 32        | AGND            | CN14 | 32            | 66        | N/C             |      |              |

| 33        | DAC1 Channel 1  | CN14 | 33            | 67        | N/C             |      |              |

| 34        | AGND            | CN14 | 34            | 68        | N/C             |      |              |

### AIO 1-8 Connector - 62-pin High Density "D" Female Connector

Connector Part #: VALCONN HDB-62S Sample Mating Connector: VALCONN HDB-62P

Table 15: IDAN- DM35224 62-Pin High Density "D" Connector

Table 15: IDAN- DM35224 62-Pin High Density "D" Connector

| IDAN Din# | Signal DM35224 Pin # |          |    |  |  |

|-----------|----------------------|----------|----|--|--|

| IDAN Pin# | - 3 -                |          |    |  |  |

| 1         | AGND                 | CN14     | 1  |  |  |

| 2         | AGND                 | CN14     | 4  |  |  |

| 3         | AGND                 | CN14     | 7  |  |  |

| 4         | AGND                 | CN14     | 10 |  |  |

| 5         | AGND                 | CN14     | 13 |  |  |

| 6         | AGND                 | CN14     | 16 |  |  |

| 7         | AGND                 | CN14     | 19 |  |  |

| 8         | AGND                 | CN14     | 22 |  |  |

| 9         | AGND                 | CN14     | 25 |  |  |

| 10        | AGND                 | CN14     | 28 |  |  |

| 11        | AGND                 | CN14     | 31 |  |  |

| 12        | AGND                 | CN14     | 34 |  |  |

| 13        | AGND                 | CN14     | 37 |  |  |

| 14        | AGND                 | CN14     | 40 |  |  |

| 15        | AGND                 | CN14     | 43 |  |  |

| 16        | AGND                 | CN14     | 46 |  |  |

| 17        | AGND                 | CN14     | 49 |  |  |

| 18        | Reserved             |          |    |  |  |

| 19        | Reserved             |          |    |  |  |

| 20        | Reserved             |          |    |  |  |

| 21        |                      | Reserved |    |  |  |

| 22        | AGND                 | CN14     | 2  |  |  |

| 23        | ADC0 Channel 0+      | CN14     | 5  |  |  |