# DM35520HR/SDM35540HR

12-Bit Analog I/O dataModule

# User's Manual

BDM-610010042 Rev. D

**RTD Embedded Technologies, Inc.** AS9100 and ISO 9001 Certified

**RTD Embedded Technologies, Inc.**

103 Innovation Boulevard State College, PA 16803 USA Telephone: 814-234-8087 Fax: 814-234-5218

www.rtd.com

sales@rtd.com techsupport@rtd.com

# **Revision History**

| Rev A | Initial Release                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev B | Added Information for the SDM35540                                                                                                                      |

| Rev C | Added DM35520 picture to front cover                                                                                                                    |

| Rev D | Pin 1 of McBSP Pin-outs was changed to No Connect<br>SDM35540 IDAN Pin-outs listed incorrect SDM35540 CN numbers.<br>Added diagram of 68 pin connector. |

Advanced Analog I/O, Advanced Digital I/O, aAIO, aDIO, aDIO, Autonomous SmartCal, "Catch the Express", cpuModule, dspFramework, dspModule, expressMate, ExpressPlatform, "MIL Value for COTS prices", multiPort, PlatformBus, and PC/104EZ are trademarks, and "Accessing the Analog World", dataModule, IDAN, HiDANplus, RTD, and the RTD logo are registered trademarks of RTD Embedded Technologies, Inc. All other trademarks or registered trademarks are the property of their respective companies.

Failure to follow the instructions found in this manual may result in damage to the product described in this manual, or other components of the system. The procedure set forth in this manual shall only be performed by persons qualified to service electronic equipment. Contents and specifications within this manual are given without warranty, and are subject to change without notice. RTD Embedded Technologies, Inc. shall not be liable for errors or omissions in this manual, or for any loss, damage, or injury in connection with the use of this manual.

Copyright © 2014 by RTD Embedded Technologies, Inc. All rights reserved.

# Table of Contents

| 1 | Introductio | on                                                                                                                                                                                                                                                                                  | 11 |

|---|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1         | Product Overview                                                                                                                                                                                                                                                                    |    |

|   | 1.2         | Board Features                                                                                                                                                                                                                                                                      |    |

|   | 1.3         | Ordering Information                                                                                                                                                                                                                                                                |    |

|   | 1.4         | Contact Information<br>1.4.1 Sales Support<br>1.4.2 Technical Support                                                                                                                                                                                                               |    |

| 2 | Specificati |                                                                                                                                                                                                                                                                                     | 13 |

|   | . 2.1       | Operating Conditions                                                                                                                                                                                                                                                                |    |

|   | 2.2         | Electrical Characteristics                                                                                                                                                                                                                                                          |    |

| 3 | Board Cor   | nnection                                                                                                                                                                                                                                                                            | 15 |

|   | 3.1         | Board Handling Precautions                                                                                                                                                                                                                                                          |    |

|   | 3.2         | Physical Characteristics                                                                                                                                                                                                                                                            |    |

|   | 3.3         | DM35520 Connectors and Jumpers<br>3.3.1 External I/O Connectors<br>CN3: External I/O Connector<br>P3: SyncBus<br>P4: McBSP<br>3.3.2 Bus Connectors<br>CN1(Top) & CN2(Bottom): PCIe Connector<br>3.3.3 Jumpers                                                                       |    |

|   | 3.4         | SDM35540 Connectors and Jumpers<br>3.4.1 External I/O Connectors<br>CN6: External Digital I/O Connector<br>CN9: External Analog I/O Connector<br>CN5: SyncBus<br>CN18: McBSP<br>3.4.1 Bus Connectors<br>CN1(Top) & CN2(Bottom): PCIe Connector<br>3.4.2 Jumpers<br>JP1: Local Reset |    |

|   | 3.5         | Steps for Installing                                                                                                                                                                                                                                                                |    |

| 4 | IDAN Con    | nections                                                                                                                                                                                                                                                                            | 23 |

|   | 4.1         | Module Handling Precautions                                                                                                                                                                                                                                                         |    |

|   | 4.2         | Physical Characteristics                                                                                                                                                                                                                                                            |    |

|   | 4.3         | DM35520 Connectors<br>4.3.1 External I/O Connectors                                                                                                                                                                                                                                 |    |

|   | 4.4         | SDM35540 Connectors<br>4.4.1 External I/O Connectors                                                                                                                                                                                                                                |    |

|   | 4.5         | Steps for Installing                                                                                                                                                                                                                                                                |    |

| 5 | Functiona   | I Description                                                                                                                                                                                                                                                                       | 30 |

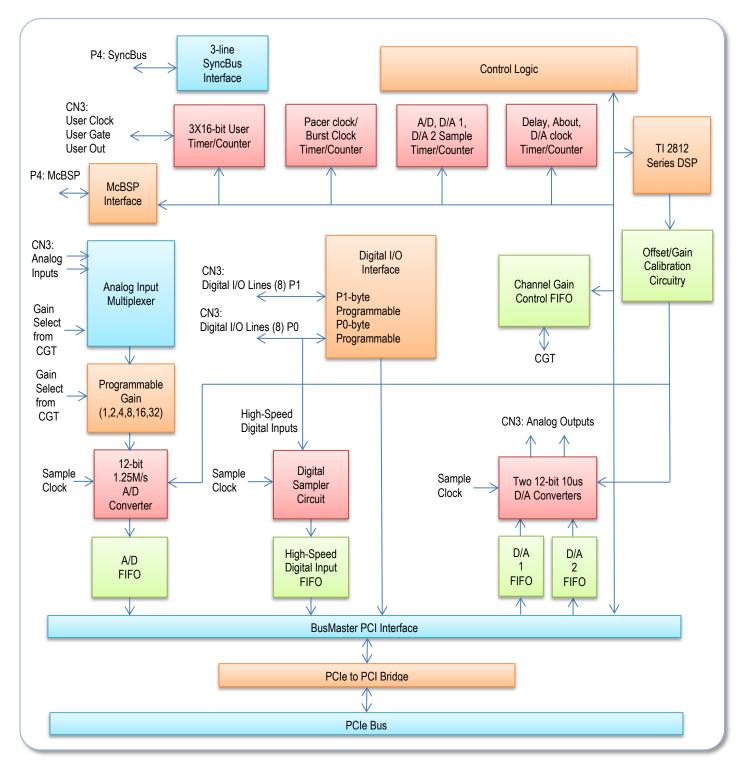

|   | 5.1         | Block Diagram                                                                                                                                                                                                                                                                       |    |

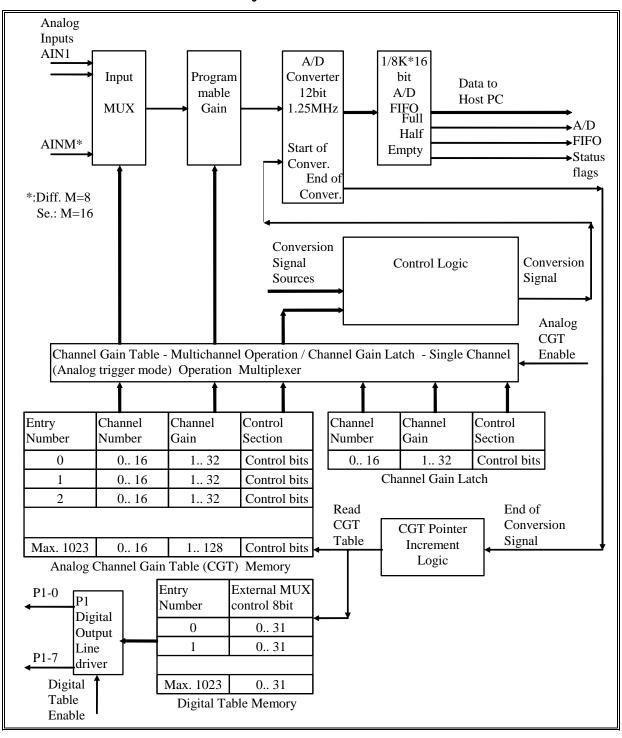

|   | 5.2         | Hardware Description<br>5.2.1 Channel Gain Latch (CGL) and Channel Gain Table (CGT)<br>5.2.2 Analog-to-Digital Conversion<br>A/D Converter<br>A/D FIFO – Sample Buffer<br>Data Transfer                                                                                             |    |

|     | 5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Digital-to-Analog Conversion<br>Timer/Counters<br>Digital I/O<br>High-Speed Digital Inputs<br>SyncBus<br>McBSP Multi-channel Buffered Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33<br>33<br>34<br>34<br>34<br>34<br>34                                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

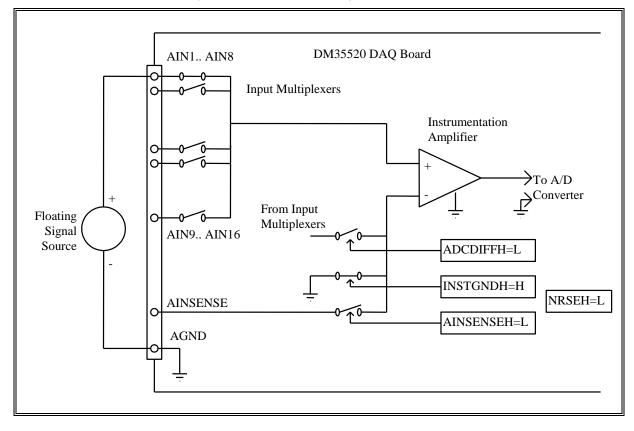

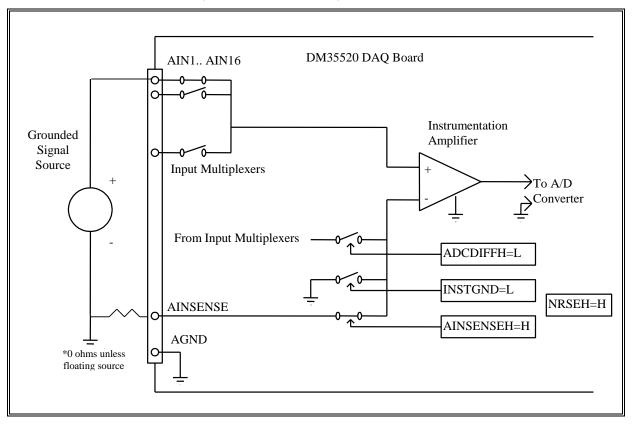

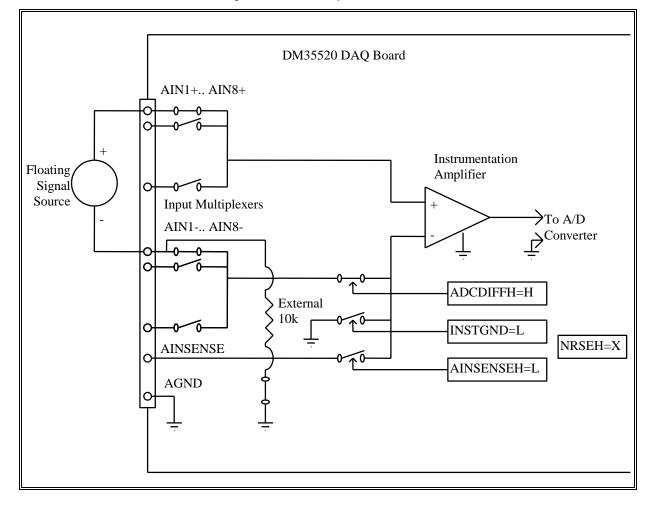

| 5.3 | 5.3.1<br>Groun<br>Non F<br>Differ<br>5.3.2<br>5.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ections<br>Connecting Analog Input Pins<br>nd Referenced Single-Ended (GRSE) Input Mode<br>Referenced Single-Ended (NRSE) Input Mode<br>ential (DIFF) Input Mode<br>Connecting Analog Outputs<br>Connecting the Timer/Counters and Digital I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35<br>35<br>36<br>37<br>38<br>38                                                                                                                                                      |

| 5.4 | 5.4.1<br>000h:<br>000h:<br>000h:<br>010h:<br>014h:<br>018h:<br>024h:<br>022h:<br>02Ch<br>030h:<br>034h:<br>040h:<br>044h:<br>044h:<br>048h:<br>04Ch<br>050h:<br>05Ch<br>060h,<br>06Ch<br>070h:<br>074h:<br>078h:<br>07Ch<br>080h<br>0E4h<br>0E8h<br>0E8h<br>0E8h<br>5.4.1<br>100h:<br>104h:<br>104h:<br>102h:<br>112h:<br>12Ch<br>120h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>12Ch<br>130h:<br>134h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h:<br>138h: | ces of DM35520<br>Local Address Space 0 (LAS0) – Runtime Area<br>Firmware version number (Read Only)<br>User Input read / User Output Write (Read/Write)<br>Software update J/A 2 (Write)<br>Software update D/A 1 (Write)<br>Software update D/A 2 (Write)<br>Software update D/A 1 (Write)<br>Software update D/A 2 (Write)<br>Pacer Clock Software trigger (Read/Write)<br>Pacer/Burst Clock Timer Status Register / Software High Speed Input Sample Command (Read/Write)<br>Interrupt Status/Mask Register (Read/Write)<br>Interrupt Clear Register (Read/Write)<br>Pacer/Burst Clock Timer Status Register / Software High Speed Input Sample Command (Read/Write)<br>Interrupt Clear Register (Read/Write)<br>Pacer/Burst Clock Counter (Read/Write)<br>Pacer Clock Counter (Read/Write)<br>Burst Clock Counter (Read/Write)<br>Di A 1 Update Counter (Read/Write)<br>Delay Counter (Read/Write)<br>Delay Counter (Read/Write)<br>Delay Counter (Read/Write)<br>Delay Counter (Read/Write)<br>Delay Counter (Read/Write)<br>Di A 1 Update Counter (Read/Write)<br>Di A 2 Update Counter (Read/Write)<br>Digital I/O chip Port 0, Bit Programmable Port (Read/Write)<br>Digital I/O chip Port 0, Bit Programmable Port (Read/Write)<br>Digital I/O chip Port 0, Bit Programmable Port (Read/Write)<br>Command Register (Read/Write) SDM35540 ONLY<br>Analog Connector DIO Inerction (Mead/Write) SDM35540 ONLY<br>Analog Connector DIO Dizet (Read/Write) SDM35540 ONLY<br>Analog Connector DIO Dizet (Write Only)<br>DMAI Request Source Select (Write Only)<br>DMAI Request Source Select (Write Only)<br>DMAI Request Source Select (Write Only)<br>AD Eurore Stati trigger select (Write O | $\begin{array}{c} 39\\ 40\\ 41\\ 41\\ 41\\ 42\\ 42\\ 42\\ 44\\ 45\\ 45\\ 45\\ 45\\ 46\\ 46\\ 46\\ 46\\ 46\\ 47\\ 47\\ 48\\ 49\\ 49\\ 50\\ 50\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55$ |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | : Enable Channel Gain Table (Write Only)<br>Enable Digital Table (Write Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59<br>59                                                                                                                                                                              |

|                                                                                                                | "Acc     |

|----------------------------------------------------------------------------------------------------------------|----------|

| 144h: Table Pause enable (Write Only)                                                                          | 59       |

| 148h: Reset Channel Gain Table (Write Only)                                                                    | 59       |

| 14Ch: Clear Channel Gain Table (Write Only)                                                                    | 59       |

| 150h: D/A 1 output type/range (Write Only)                                                                     | 59       |

| 154h: D/A 1 update source (Write Only)                                                                         | 59       |

| 158h: D/A 1 Cycle Mode (Write Only)                                                                            | 59       |

| 15Ch: Reset D/A 1 Cycle FIFO (Write Only)                                                                      | 60       |

| 160h: Clear D/A 1 Cycle FIFO (Write Only)                                                                      | 60       |

| 164h: D/A 2 output type/range (Write Only)                                                                     | 60       |

| 168h: D/A 2 update source (Write Only)                                                                         | 60       |

| 16Ch: D/A 2 Cycle Mode (Write Only)<br>170h: Reset D/A 2 FIFO (Write Only)                                     | 60<br>60 |

| 174h: Clear D/A 2 FIFO (Write Only)                                                                            | 60<br>60 |

| 174h: Clear D/A 2 Fir O (Write Only)<br>178h: A/D Sample Counter Source Select (Write Only)                    | 60<br>60 |

| 180h: Pacer Select (Write Only)                                                                                | 60       |

| 184h: SyncBus 0 Source Select (Write Only)                                                                     | 61       |

| 188h: Enable SyncBus 0 (Write Only)                                                                            | 61       |

| 18Ch: SyncBus 1 Source Select (Write Only)                                                                     | 62       |

| 190h: Enable SyncBus 1 (Write Only)                                                                            | 62       |

| 198h: SyncBus 2 Source Select (Write Only)                                                                     | 62       |

| 19Ch: Enable SyncBus 2 (Write Only)                                                                            | 62       |

| 1A4h: External Trigger Polarity Select (Write Only)                                                            | 62       |

| 1A8h: External Interrupt Polarity Select (Write Only)                                                          | 62       |

| 1ACh: User Timer/Counter 0 Clock Select (Write Only)                                                           | 63       |

| 1B0h: User Timer/Counter 0 Gate Select (Write Only)                                                            | 63       |

| 1B4h: User Timer/Counter 1 Clock Select (Write Only)                                                           | 63       |

| 1B8h: User Timer/Counter 1 Gate Select (Write Only)                                                            | 63<br>64 |

| 1BCh: User Timer/Counter 2 Clock Select (Write Only)<br>1C0h: User Timer/Counter 2 Gate Select (Write Only)    | 64       |

| 1C4h: User Output 0 Signal Select (Write Only)                                                                 | 64       |

| 1C8h: User Output o Signal Select (Write Only)                                                                 | 64       |

| 1ECh: McBSP A/D FIFO Control (Write Only)                                                                      | 64       |

| 1F0h: McBSP D/A 1 and D/A 2 FIFO Control (Write Only)                                                          | 64       |

| 5.4.2 Local Address Space 1 (LAS1) - Setup Area                                                                | 65       |

| 000h: Read A/D FIFO (Read Only)                                                                                | 65       |

| 004h: Read High Speed Digital Input FIFO (Read Only)                                                           | 66       |

| 008h: Write D/A1 FIFO (Read Only)                                                                              | 66       |

| 00Ch: Write D/A21 FIFO (Read Only)                                                                             | 67       |

| A/D Conversion                                                                                                 | 67       |

| 5.5.1 Before Starting Conversions: Initializing the Board                                                      | 67       |

| Before Starting Conversions (single-channel mode): Programming Channel Gain Latch (CGL)                        | 67       |

| Before Starting Conversions (multi-channel mode): Programming the Channel-Gain Table (CGT)                     | 67       |

| 16-Bit A/D Table                                                                                               | 68       |

| Channel Select, Gain Select, Input Range and Input Type                                                        | 68       |

| Pause bit                                                                                                      | 68       |

| D/Ax update bits                                                                                               | 68       |

| Skip bit                                                                                                       | 68       |

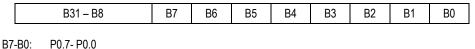

| 8-Bit Digital Table                                                                                            | 68<br>60 |

| Setting Up A/D part and Digital part of Channel Gain Table<br>Using the Channel Gain Table for A/D Conversions | 69<br>69 |

| Channel-gain Table and Throughput Rates                                                                        | 69       |

| 5.5.2 A/D Conversion Modes                                                                                     | 69       |

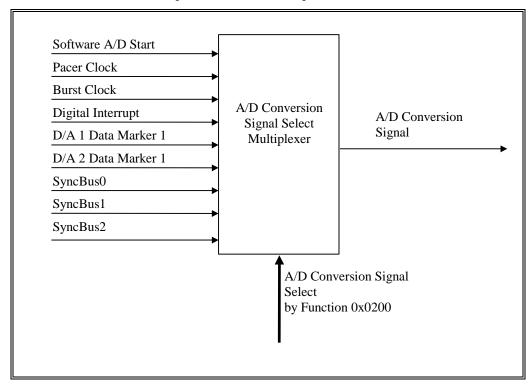

| Start A/D Conversion signal                                                                                    | 69       |

| Pacer Clock Start/Stop Trigger Select                                                                          | 70       |

| Types of Conversions                                                                                           | 72       |

| 5.5.3 Reading the Converted Data                                                                               | 73       |

| 5.5.4 Using the A/D Data Markers                                                                               | 73       |

| 5.5.5 Programming the Pacer Clock                                                                              | 73       |

| 5.5.6 Programming the Burst Clock                                                                              | 74       |

| 5.5.7 Programming the About Counter                                                                            | 75       |

| Using the About Counter to Create Large Data Arrays                                                            | 75       |

| D/A Conversion                                                                                                 | 75       |

| 5.6.1 1K Sample Buffer                                                                                         | 78       |

| 5.6.2 D/A Cycled or Not Cycled Mode                                                                            | 78       |

| 5.6.3 D/A Update Counters                                                                                      | 78       |

|                                                                                                                |          |

5.5

5.6

|               | 5.6.4            | D/A Data Markers                                                                                                          | 79       |

|---------------|------------------|---------------------------------------------------------------------------------------------------------------------------|----------|

| 5.7           |                  | er using DMA                                                                                                              |          |

|               | 5.7.1<br>5.7.2   | Non-Chaining Mode DMA                                                                                                     | 79<br>79 |

|               | 5.7.2            | Non-Chaining Mode DMA<br>DMA Data Transfers                                                                               | 80       |

|               | Dem              | nand Mode DMA                                                                                                             | 80       |

|               |                  | A Priority                                                                                                                | 80       |

|               | 5.7.4<br>(DM)    | DMA Registers<br>AMODE0; PCI: 80h) DMA Channel 0 Mode Register                                                            | 80<br>81 |

|               |                  | APADR0; PCI:84h) DMA Channel 0 PCI Address Register                                                                       | 81       |

|               |                  | ALADR0; PCI:88h) DMA Channel 0 Local Address Register                                                                     | 81       |

|               |                  | ASIZ0; PCI:8Ch) DMA Channel 0 Transfer Size (Bytes) Register<br>ADPR0; PCI:90h) DMA Channel 0 Descriptor Pointer Register | 82<br>82 |

|               |                  | AMODE1; PCI: 94h) DMA Channel 1 Mode Register                                                                             | 82       |

|               |                  | APADR1; PCI:98h) DMA Channel 1 PCI Address Register                                                                       | 83       |

|               |                  | ALADR0; PCI:9Ch) DMA Channel 1 Local Address Register<br>ASIZ0; PCI:A0h) DMA Channel 1 Transfer Size (Bytes) Register     | 83<br>83 |

|               |                  | ADPR0; PCI:A4h) DMA Channel 1 Descriptor Pointer Register                                                                 | 83       |

|               |                  | ACSR0; PCI:A8h) DMA Channel 0 Command/Status Register                                                                     | 83       |

|               |                  | ACSR1; PCI:A9h) DMA Channel 1 Command/Status Register<br>AARB; PCI:ACh) DMA Arbitration Register                          | 84<br>84 |

|               |                  | ATHR; PCI:B0h) DMA Threshold Register                                                                                     | 84       |

| 5.8           | ,                | · , ,                                                                                                                     |          |

| 0.0           | 5.8.1            | The Overall Interrupt Structure of DM35520                                                                                |          |

|               |                  | Interrupt Sources of DM35520                                                                                              | 85       |

|               | I he<br>5.8.2    | Interrupt Registers of DM35520<br>The Operation of On-board Priority Interrupt Controller                                 | 85<br>86 |

|               | 5.8.3            | Advanced Digital Interrupts                                                                                               | 87       |

|               |                  | nt Mode                                                                                                                   | 87       |

|               |                  | ch Mode<br>ıpling Digital Lines for Change of State                                                                       | 87<br>87 |

| 5.0           |                  |                                                                                                                           |          |

| 5.9           | 5.9.1            | ters<br>The internal Timer Timer/Counters                                                                                 |          |

|               | 5.9.2            | User Timer Timer/Counters                                                                                                 | 88       |

| 5.10          | Digital I/O      |                                                                                                                           |          |

|               | 5.10.1           | The Digital I/O Chip                                                                                                      | 90<br>90 |

|               |                  | 0, Bit Programmable Digital I/O<br>anced Digital Interrupts: Mask and Compare Registers                                   | 90       |

|               | Port             | 1, Port Programmable Digital I/O                                                                                          | 90       |

|               |                  | etting the Digital Circuitry                                                                                              | 90       |

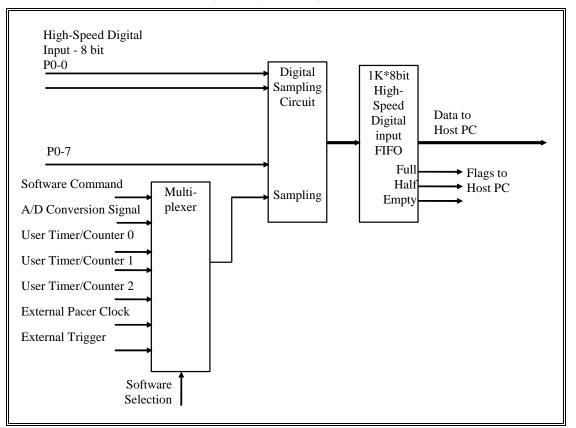

|               | 5.10.2           | bing Data into Port 0<br>High-Speed Digital Input                                                                         | 91<br>91 |

|               | 5.10.3           | Digital Input Data Markers                                                                                                | 91       |

| 5.11          | Calibration      |                                                                                                                           |          |

|               | 5.11.1           | SDM35540 Calibration                                                                                                      | 91       |

|               | 5.11.2<br>5.11.3 | Required Equipment DM35520 A/D Calibration                                                                                | 91<br>91 |

|               |                  | lar Calibration                                                                                                           | 91       |

|               | Com              | nmon Mode Calibration                                                                                                     | 93       |

|               |                  | polar Calibration                                                                                                         | 94<br>94 |

|               |                  | n Adjustment<br>35520 D/A Calibration                                                                                     | 94<br>95 |

| 5.12          | On-board DS      | SP (SDM35540 Only)                                                                                                        |          |

| Troublesho    |                  | · · · · · · · · · · · · · · · · · · ·                                                                                     | 97       |

| Additional lu | -                |                                                                                                                           | 98       |

| 7.1           |                  | cifications                                                                                                               |          |

| 7.2           | •                | Express Specification                                                                                                     |          |

| The PCI Cor   |                  | egisters, Local Configuration Registers, Runtime Registers                                                                | 99       |

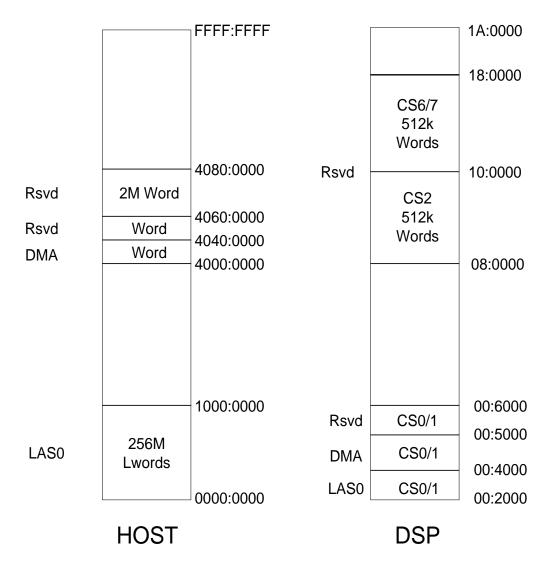

| 8.1           | DSP Memo         | огу тар                                                                                                                   | 104      |

|               |                  |                                                                                                                           |          |

6 7

8

| 8.2        | PCI Configu<br>8.2.1<br>8.2.2 | uration Registers<br>PCIIDR - Device ID, Vendor ID<br>PCICCR - Class Code |     |

|------------|-------------------------------|---------------------------------------------------------------------------|-----|

|            | 8.2.3                         | PCICLSR, PCI LTR, PCI HTR, PCIIPR PCIILR                                  | 106 |

|            | 8.2.4                         | PCISVID - PCI Subsystem Vendor ID                                         | 106 |

|            | 8.2.5                         | PEROMBA - Expansion ROM PCI Base Address Register                         | 106 |

| 8.3        | Local Config                  | guration Registers                                                        |     |

|            | 8.3.1                         | Range for PCI-to-Local Address Space 0 Register                           | 107 |

|            | 8.3.2                         | Local Base Address (Remap) for PCI-to-Local Address Space 0 Register      | 107 |

|            | 8.3.3                         | Mode/Arbitration Register                                                 | 108 |

|            | 8.3.4                         | Big/Little Endian Descriptor Register                                     | 109 |

|            | 8.3.5                         | Expansion ROM Range Register                                              | 109 |

|            | 8.3.6                         | Expansion ROM Local Base Address (Remap) Register and BREQo Control       | 109 |

|            | 8.3.7                         | Local Address Space 0/Expansion ROM Bus Region Descriptor Register        | 110 |

|            | 8.3.8                         | Local Range Register for Direct Master to PCI                             | 110 |

|            | 8.3.9                         | Local Bus Base Address Register for Direct Master to PCI Memory           | 111 |

|            | 8.3.10                        | Local Base Address Register for Direct Master to PCI IO/CFG               | 111 |

|            | 8.3.11                        | PCI Base Address (Remap) Register for Direct Master to PCI Memory         | 111 |

|            | 8.3.12                        | PCI Configuration Address Register for Direct Master to PCI IO/CFG        | 112 |

|            | 8.3.13                        | PCI Local Address Space 1 Range Register for PCI-to-Local Bus             | 112 |

|            | 8.3.14                        | Local Address Space 1 Local Base Address (Remap) Register                 | 113 |

|            | 8.3.15                        | Local Address Space 1 Bus Region Descriptor Register                      | 113 |

| 8.4        | Runtime Re                    | egisters                                                                  |     |

|            | 8.4.1                         | Serial EEPROM Control, PCI Command Codes, User I/O Control, Init Control  | 115 |

| The PLX90  | 80/9056 EEPF                  | ROM Content                                                               | 116 |

| Limited Wa | rranty                        |                                                                           | 117 |

9 10

# Table of Figures

| Figure 1: Board Dimensions                                                                                                  | 15 |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1: Board Dimensions<br>Figure 2: DM35520 Board Connections<br>Figure 3: SDM35540 Board Connections                   | 16 |

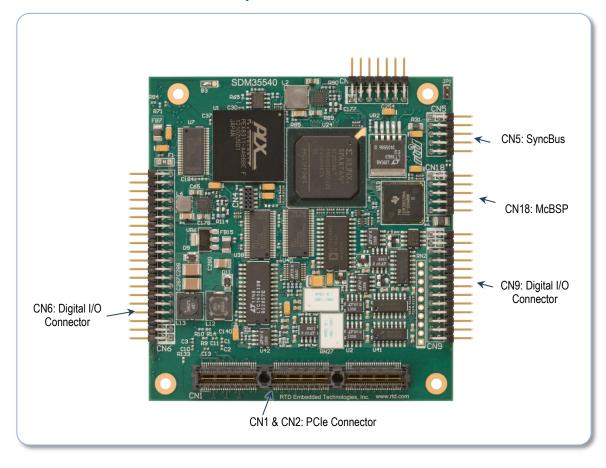

| Figure 3: SDM35540 Board Connections                                                                                        | 19 |

| Figure 4: Example 104™Stack                                                                                                 | 22 |

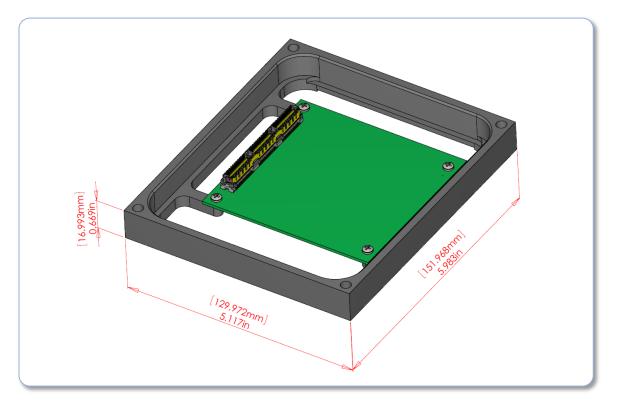

| Figure 5: IDAN Dimensions                                                                                                   | 23 |

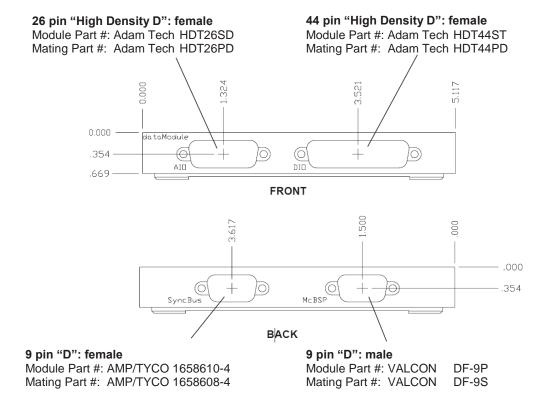

| Figure 6: Example IDAN System                                                                                               | 29 |

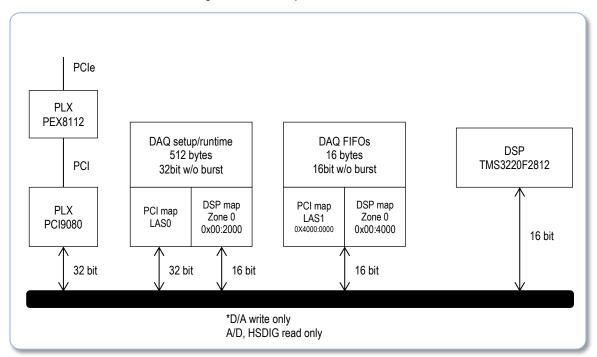

| Figure 7: DM35520 Block Diagram                                                                                             | 30 |

| Figure 8: Channel Gain Table                                                                                                | 32 |

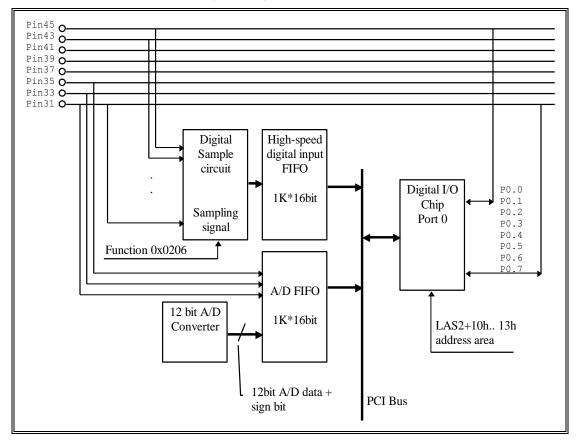

| Figure 8: Channel Gain Table<br>Figure 9: High-Speed Digital Inputs<br>Figure 10: Ground Referenced Single Ended input mode | 34 |

| Figure 10: Ground Referenced Single Ended input mode                                                                        | 35 |

| Figure 11: Non Referenced Single-Ended input mode                                                                           | 36 |

| Figure 12: Differential input mode<br>Figure 13: Digital I/O                                                                | 37 |

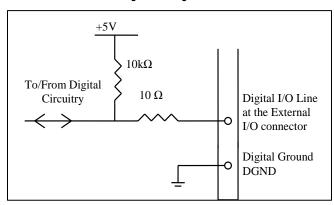

| Figure 13: Digital I/O                                                                                                      | 38 |

| Figure 14: Address Space/ Local Bus Access                                                                                  | 39 |

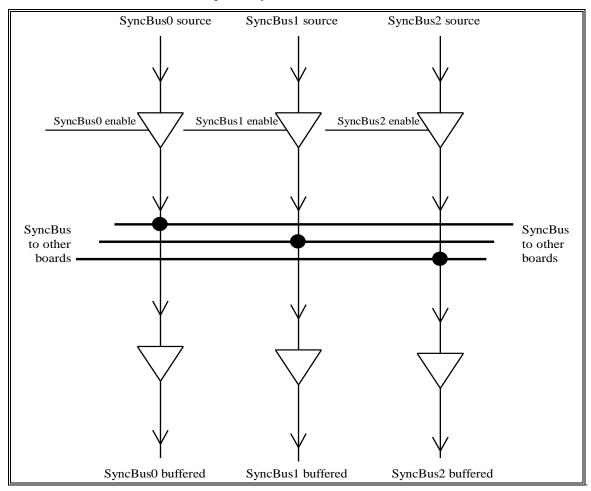

| Figure 15: SyncBus Structure                                                                                                | 61 |

| Figure 16: User TC Section                                                                                                  | 63 |

| Figure 17: A/D Conversion Signal                                                                                            | 70 |

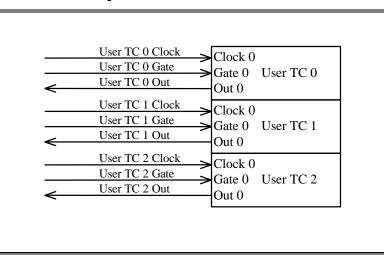

| Figure 18: User Timer/Counter                                                                                               | 88 |

| Figure 18: User Timer/Counter<br>Figure 19: Digital I/O Port 0                                                              | 89 |

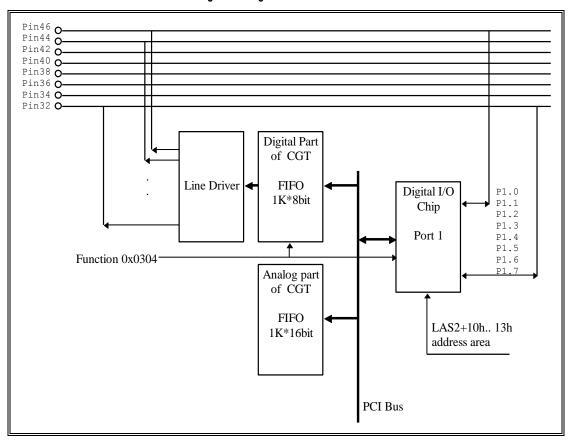

| Figure 20: Digital I/O Port 1                                                                                               | 90 |

|                                                                                                                             |    |

# Table of Tables

| Table 1: Ordering Options                                 | . 12 |

|-----------------------------------------------------------|------|

| Table 2: Operating Conditions                             |      |

| Table 3: Electrical Characteristics                       | . 13 |

| Table 4: Signal Functions                                 | . 16 |

| Table 5: CN3 Connector Pin out                            | . 17 |

| Table 6: P3: SyncBus Pin out                              | . 18 |

| Table 7: P4: McBSP Pin out                                | . 18 |

| Table 8: Signal Functions                                 | . 19 |

| Table 9: Digital I/O Connector                            | . 20 |

| Table 10: Analog I/O Connector                            | . 20 |

| Table 11: SyncBus                                         | . 21 |

| Table 12: McBSP                                           | . 21 |

| Table 13: IDAN- DM35520 68-Pin High Density "D" Connector | . 24 |

| Table 14: IDAN-SDM35540 Analog I/0 26-pin "D" Connector   | . 26 |

| Table 15: IDAN-SDM35540 Digital I/0 44-pin "D" Connector  | . 27 |

| Table 16: IDAN-SDM35540 SyncBus 9-pin "D" Connector       | . 28 |

| Table 17: IDAN-SDM35540 McBSP 9-pin "D" Connector         | . 28 |

| Table 18: LAS0 Register Map Offsets                       |      |

| Table 19: LAS0 Setup Area                                 | . 50 |

| Table 20: LAS1 Address Space                              | . 65 |

| Table 21: Pacer Clock Frequency                           | . 74 |

| Table 22: Burst Clock Frequency                           |      |

| Table 23: DAC Clock Frequency                             | . 76 |

| Table 24: DAC Bipolar Binary Value vs. Output Voltage     | . 77 |

| Table 25: DAC Unipolar Binary Value vs. Output Voltage    |      |

| Table 26: DMA Registers                                   | . 80 |

| Table 27: Interrupt Control/Status Register               | . 85 |

| Table 28: Bipolar Offset and Gain Adjustment              | . 93 |

| Table 29: 20V Range Adjustment                            | . 93 |

| Table 30: Bipolar ADC Bit Weight                          | . 93 |

| Table 31: Unipolar Offset Adjustment                      | . 94 |

| Table 32: | Unipolar ADC Bit Weight |

|-----------|-------------------------|

| Table 33: | Gain Calibration        |

# 1 Introduction

## 1.1 **Product Overview**

The DM35520 is a software configurable high-speed, 12-bit data acquisition module in a PCle/104 format. It provides 8 differential or 16 singleended analog input channels, with programmable gain and input ranges. It also provides two individually controlled analog outputs, multiple board synchronization with the SyncBus and multi-channel buffered Serial Port, McBSP.

The SDM35540 has all the functionality of the DM35520, but also features auto calibration with the use of an onboard DSP and an onboard temperature sensor.

## 1.2 Board Features

- High-Speed Analog Inputs

- 8 Differential or 16 Single-ended channels

- 12-bit A/D with matched internal Sample and Hold

- 0.8µs conversion time (1.25 MHz throughput)

- ±5, ±10, 0 to +10 V Analog Input Ranges

- Programmable binary gains of 1, 2, 4, 8, 16 & 32

- o 1K entry Channel-Gain Scan Memory with Skip Bit

- High-Speed Data Paths

- Multi-channel Buffered Serial Port (McBSP)

- o 1K sample buffer on A/D converter

- 1K sample buffer on each D/A converter channel

- Versatile Triggering

- o Software, Pace Clock, Burst Clock and External Triggers

- o Pre-, Post-, and About- Trigger Modes

- o Random Scan, burst and multi-burst using channel-gain table

- Two fast analog outputs

- 12-bit resolution

- $\circ$  7 µs full-scale settling time (±10V range)

- ±5, +5, ±10, & +10V output ranges

- 5mA output current

- Digital I/O

- o 3 Data-marker Input Bits

- o 1K byte digital input buffer

- o 8 bit-programmable digital I/O lines and an 8-bit programmable port

- Advanced digital interrupts

- o -12/+24mA output drive currents

- Timer and Counters

- Twelve 16-bit, 8 MHz timer/counters to support timing and counting functions (3 available for user applications)

- Programmable Interrupt Source

- Auto calibration (SmartCal) for A/D and D/A with onboard DSP (SDM35540 only)

- On-board Temperature sensor (SDM35540 only)

- PCI Express Bus:

0

- Provides 2.5 Gbps in each direction

- Single lane and single Virtual Channel operation

- Compatible with multi-Virtual Channel chipsets

- Packetized serial traffic with PCI Express Split Completion protocol

- o Data Link Layer Cyclic Redundancy Check (CRC) generator and checker

- Automatic Retry of bad packets

- In-band interrupts and messages

- Message Signaled Interrupt (MSI) support

# 1.3 Ordering Information

The DM35520 is available with the following options:

#### Table 1: Ordering Options

| Part Number     | Description                                                   |

|-----------------|---------------------------------------------------------------|

| DM35520HR       | PCIe/104 12-bit Analog I/O dataModule                         |

| SDM35540HR      | PCIe/104 12-bit Analog I/O Smart dataModule                   |

| IDAN-DM35520HR  | PCIe/104 12-bit Analog I/O dataModule in IDAN enclosure       |

| IDAN-SDM35540HR | PCIe/104 12-bit Analog I/O Smart dataModule in IDAN enclosure |

#### Note: Throughout this document, DM35520 refers to both the DM35520 and SDM35540 unless otherwise noted

The Intelligent Data Acquisition Node (IDAN<sup>™</sup>) building block can be used in just about any combination with other IDAN building blocks to create a simple but rugged 104<sup>™</sup> stack. This module can also be incorporated in a custom-built RTD HiDAN<sup>™</sup> or HiDANplus High Reliability Intelligent Data Acquisition Node. Contact RTD sales for more information on our high reliability systems.

## 1.4 **Contact Information**

## 1.4.1 SALES SUPPORT

For sales inquiries, you can contact RTD Embedded Technologies sales via the following methods:

| Phone:  | 1-814-234-8087 | Monday through Friday, 8:00am to 5:00pm (EST). |

|---------|----------------|------------------------------------------------|

| E-Mail: | sales@rtd.com  |                                                |

### 1.4.2 TECHNICAL SUPPORT

If you are having problems with you system, please try the steps in the Troubleshooting section of this manual.

For help with this product, or any other product made by RTD, you can contact RTD Embedded Technologies technical support via the following methods:

Phone: 1-814-234-8087 Monday through Friday, 8:00am to 5:00pm (EST). E-Mail: techsupport@rtd.com

# 2 Specifications

# 2.1 **Operating Conditions**

## **Table 2: Operating Conditions**

| Symbol            | Parameter                | Test Condition                                       | Min  | Max  | Unit  |

|-------------------|--------------------------|------------------------------------------------------|------|------|-------|

| V <sub>cc5</sub>  | 5V Supply Voltage        |                                                      | 4.75 | 5.25 | V     |

| V <sub>cc3</sub>  | 3.3V Supply Voltage      |                                                      | n/a  | n/a  | V     |

| V <sub>cc12</sub> | 12V Supply Voltage       |                                                      | n/a  | n/a  | V     |

| Vcc-12            | -12V Supply Voltage      |                                                      | n/a  | n/a  | V     |

| Ta                | Operating Temperature    |                                                      | -40  | +85  | С     |

| Ts                | Storage Temperature      |                                                      | -55  | +125 | С     |

| RH                | Relative Humidity        | Non-Condensing                                       | 0    | 90%  | %     |

| MTBF              | Mean Time Before Failure | Telcordia Issue 2<br>30°C, Ground benign, controlled |      | TBD  | Hours |

# 2.2 Electrical Characteristics

## Table 3: Electrical Characteristics

| Symbol | Parameter                        | Test Condition   | Min   | Max    | Unit |

|--------|----------------------------------|------------------|-------|--------|------|

| P      | Power Consumption                | $V_{cc5} = 5.0V$ |       | TBD    | W    |

| lcc5   | 5V Input Supply Current          | Active           |       | TBD    | mA   |

|        |                                  | PCIe Bus         |       | •      | •    |

|        | Differential Output Voltage      |                  | 0.8   | 1.2    | V    |

|        | DC Differential TX Impedance     |                  | 95.2  | 116.9  | Ω    |

|        | Differential Input Voltage       |                  | 0.175 | 3.3    | V    |

|        | DC Differential RX Impedance     |                  | 92.7  | 115.8  | Ω    |

|        | Electrical Idle Detect Threshold |                  | 61    | 173    | mV   |

|        |                                  | A/D Circuitry    |       |        |      |

|        | Input Impedance                  |                  |       | >10    | MΩ   |

|        | Gains                            |                  | 1     | 128    |      |

|        | Gain Error                       |                  |       | 0.1%   |      |

|        | Input Voltage                    | 20V Range Mode   |       | ±10    | V    |

|        |                                  | 10V Range Mode   |       | ±5     | V    |

|        |                                  | Unipolar Mode    | 0     | 10     | V    |

|        | Over Voltage Protection          |                  |       | ±15    | V    |

|        | Common Mode                      |                  |       | ±10    | V    |

|        | Channel Scanning Error           | 10500khz         |       | 0%     |      |

|        | (Gain=1)                         | 600kHz           |       | 0.05%  |      |

|        |                                  | 700kHz           |       | 0.075% |      |

|        |                                  | 800kHz           |       | 0.25%  |      |

|        |                                  | 900kHz           |       | 0.4%   |      |

|        |                                  | 1000kHz          |       | 0.45%  |      |

|        |                                  | 1250kHz          |       | 1%     |      |

|        | Resolution                       |                  |       | 12     | Bits |

|        | Linearity Error                  |                  |       | ±1     | LSB  |

|        | Sampling Rate                    |                  |       | 1.25   | MHz  |

|        | FIFO Size X16                    |                  |       | 1      | Kb   |

|        | Channel Gain table X24           |                  |       | 1      | Kb   |

|        |                                  | Digital I/O      |       |        |      |

|        | Output Current                   |                  |       | ±8     | mA   |

|        | Input Termination                |                  |       | 10     | KΩ   |

|        | Output Termination               |                  |       | 10     | Ω    |

|        |                                  | D/A Circuitry    |       |        |      |

|        | Resolution                       |                  |       | 12     | Bits |

|        | Relative Accuracy                |                  |       | ±1     | LSB  |

|        | Full-Scale Accuracy              |                  |       | ±5     | LSB  |

|        | Non-lineaity                     |                  |       | ±1     | LSB  |

### **Table 3: Electrical Characteristics**

| Symbol | Parameter      | Test Condition | Min | Max | Unit |

|--------|----------------|----------------|-----|-----|------|

|        | Settling Time  |                |     | 5   | μs   |

|        | Output Current |                |     | 5   | mA   |

|        | FIFO Size X16  | Per channel    |     | 8   | Kb   |

# 3 Board Connection

# 3.1 Board Handling Precautions

To prevent damage due to Electrostatic Discharge (ESD), keep your board in its antistatic bag until you are ready to install it into your system. When removing it from the bag, hold the board at the edges, and do not touch the components or connectors. Handle the board in an antistatic environment, and use a grounded workbench for testing and handling of your hardware.

# 3.2 **Physical Characteristics**

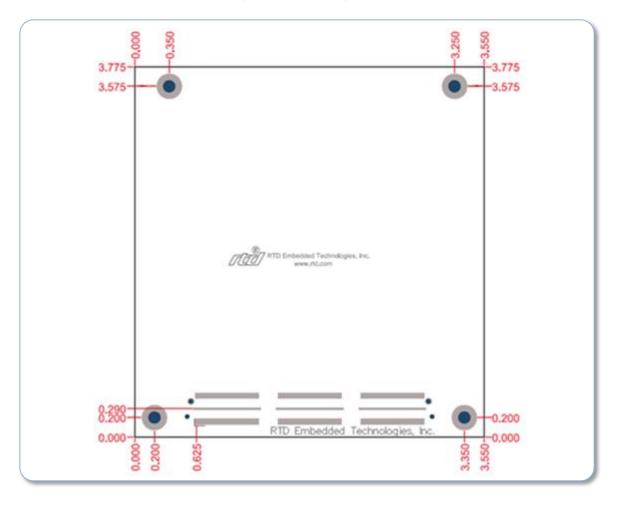

- Weight: Approximately 55 g (0.12 lbs.)

- Dimensions: 90.17 mm L x 95.89 mm W (3.550 in L x 3.775 in W)

Figure 1: Board Dimensions

# 3.3 DM35520 Connectors and Jumpers

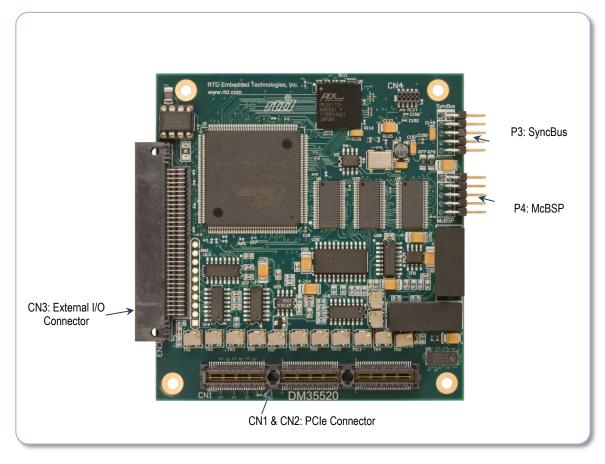

## Figure 2: DM35520 Board Connections

## 3.3.1 EXTERNAL I/O CONNECTORS

### **Table 4: Signal Functions**

| Signal                                 | Function                                                                                                                          |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AINx / AINx +/AINx -                   | SE Analog input high sides / DIFF analog input high<br>sides / DIFF analog inputs low sides.                                      |  |  |  |

| AINSENSE                               | Reference Signal in Non-ground referenced Single<br>Ended (NRSE) input mode.                                                      |  |  |  |

| AOUT x                                 | Analog outputs.                                                                                                                   |  |  |  |

| AGND                                   | Analog Ground                                                                                                                     |  |  |  |

| D/A 1 Data Marker 0                    | D/A 1 0 the output data markers.                                                                                                  |  |  |  |

| D/A 2 Data Marker 0                    | D/A 2 0 the output data markers.                                                                                                  |  |  |  |

| High Speed Input x / P0.x /<br>A/D DMx | High speed inputs to digital input FIFO / Bit<br>programmable P0 lines from digital I/O Chip.                                     |  |  |  |

| P1.x / DIG Table x                     | Port programmable lines from digital I/O Chip.<br>Outputs from digital part of channel gain table.                                |  |  |  |

| Trigger Input                          | External trigger input to trigger A/D pacer clock. (LS<br>TTL)                                                                    |  |  |  |

| External Pace Clock Input              | External pacer clock to clock A/D. (LS TTL)                                                                                       |  |  |  |

| Reset                                  | Active low reset output line asserted when the host<br>PC is in hardware reset, or the Board Clear<br>Command is active. (LS TTL) |  |  |  |

| External Interrupt Input               | Programmable rising or falling edge external Interrupt<br>source. (LS TTL)                                                        |  |  |  |

| User Input x                           | User Input 0 and User Input 1 can be read by the LAS0+04h I/O read instruction (LS TTL)                                           |  |  |  |

| Signal              | Function                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| User Output x       | The source of these buffered lines can be<br>programmed. (LS TTL)                                                                   |

| External TC Gate x  | External gate signals that go to the software<br>programmable clock source select circuit for the user<br>timer/counters. (LS TTL)  |

| TC Out x            | Buffered outputs from the user timer/counters. (LS TTL)                                                                             |

| External TC Clock x | External clock signals that go to the software<br>programmable clock source select circuit for the user<br>timer/counters. (LS TTL) |

| DGND                | Digital Signal Ground                                                                                                               |

| +5V                 | +5 Volts from the computer power supply to power<br>front end boards. (Max. 2A)                                                     |

## CN3: External I/O Connector

CN3 is an external connector for the majority of I/O connections on the board. The connector contains signals for the analog I/O, digital I/O, data triggers, and timer/counter. The pin assignment is listed below.

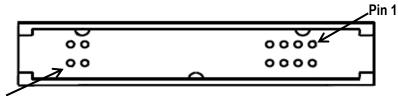

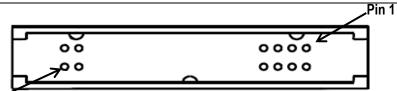

### Pin 68

Table 5: CN3 Connector Pin out

| AIN 9 / AIN1-       | 2  | 1  | AIN 1 / AIN1+                       |

|---------------------|----|----|-------------------------------------|

| AIN 10 / AIN2-      | 4  | 3  | AIN 2 / AIN2+                       |

| AIN 11 / AIN3-      | 6  | 5  | AIN 3 / AIN3+                       |

| AIN 12 / AIN4-      | 8  | 7  | AIN 4 / AIN4+                       |

| AGND                | 10 | 9  | AINSENSE                            |

| AIN 13 / AIN5-      | 12 | 11 | AIN 5 / AIN5+                       |

| AIN 14 / AIN6-      | 14 | 13 | AIN 6 / AIN6+                       |

| AIN 15 / AIN7-      | 16 | 15 | AIN 7 / AIN7+                       |

| AIN 16 / AIN8-      | 18 | 17 | AIN 8 / AIN8+                       |

| AGND                | 20 | 19 | AGND                                |

| Reserved            | 22 | 21 | AOUT 1                              |

| Reserved            | 24 | 23 | AOUT 2                              |

| AGND                | 26 | 25 | Reserved                            |

| AGND                | 28 | 27 | AGND                                |

| D/A 2 DATA MARKER 0 | 30 | 29 | D/A 1 DATA MARKER 0                 |

| P1.7 / DIG TABLE 7  | 32 | 31 | HIGH SPEED INPUT 7 / P0.7 / A/D DM2 |

| P1.6 / DIG TABLE 6  | 34 | 33 | HIGH SPEED INPUT 6 / P0.6 / A/D DM1 |

| P1.5 / DIG TABLE 5  | 36 | 35 | HIGH SPEED INPUT 5 / P0.5 / A/D DM0 |

| P1.4 / DIG TABLE 4  | 38 | 37 | HIGH SPEED INPUT 4 / P0.4           |

| P1.3 / DIG TABLE 3  | 40 | 39 | HIGH SPEED INPUT 3 / P0.3           |

| P1.2 / DIG TABLE 2  | 42 | 41 | HIGH SPEED INPUT 2 / P0.2           |

| P1.1 / DIG TABLE 1  | 44 | 43 | HIGH SPEED INPUT 1 / P0.1           |

| P1.0 / DIG TABLE 0  | 46 | 45 | HIGH SPEED INPUT 0 / P0.0           |

| DGND                | 48 | 47 | TRIGGER INPUT                       |

| RESET               | 50 | 49 | EXTERNAL PACER CLOCK INPUT          |

| DGND                | 52 | 51 | EXTERNAL INTERRUPT INPUT            |

| USER INPUT 1        | 54 | 53 | USER INPUT 0                        |

| USER OUTPUT 1       | 56 | 55 | USER OUTPUT 0                       |

| DGND                | 58 | 57 | TC OUT 0                            |

| EXTERNAL TC GATE 1  | 60 | 59 | EXTERNAL TC CLOCK 1                 |

| TC OUT 2            | 62 | 61 | TC OUT 1                            |

| EXTERNAL TC GATE 2  | 64 | 63 | EXTERNAL TC CLOCK 2                 |

| DGND                | 66 | 65 | +5 VOLTS                            |

| DGND                | 68 | 67 | +5 VOLTS                            |

|                     |    |    |                                     |

### P3: SyncBus

The SyncBus is an RTD defined digital bus for synchronous operation with other RTD's boards. The signaling level is 5V compliant TTL. There are no pull-up resistors on the bus lines. If a line is used, a master/driver for this lane needs to exist somewhere in the system.

#### Table 6: P3: SyncBus Pin out

| SyncBus0 | 1 | 2  | GND |

|----------|---|----|-----|

| GND      | ა | 4  | GND |

| SyncBus1 | 5 | 6  | GND |

| GND      | 7 | 8  | GND |

| SyncBus2 | 9 | 10 | GND |

#### P4: McBSP

The McBSP (Multichannel Buffered Serial) is a Texas Instruments defined serial bus for DSP and front-end communication. This port is 5V compliant.