# XA270

chnolog

# PC/104 PROCESSOR BOARD

# **TECHNICAL REFERENCE MANUAL**

Revision B02 | 23<sup>rd</sup> November 2006 | 286004.B02

(This page is intentionally left blank)

All information in this manual is believed to be accurate and reliable. However, no responsibility is assumed by DSP Design Limited for its use. Since conditions of product use are outside our control, we make no warranties express or implied in relation thereto. We therefore cannot accept any liability in connection with any use of this information. Nothing herein is to be taken as a license to operate under or a recommendation to infringe any patents.

Whilst every effort has been made to ensure that this document is correct, errors can occur. If you find any errors or omissions please let us know, so that we can put this right.

All information contained in this manual is proprietary to DSP Design Limited and cannot be reproduced without the consent of DSP Design Limited. The circuit design and printed circuit board design is copyright of DSP Design Limited 2006.

DSP Design Limited Tapton Park Innovation Centre Brimington Road Chesterfield S41 0TZ United Kingdom

Tel

+44 (0) 1246 545 910

Fax

+44 (0) 1246 545 911

Email

sales@dspdesign.com

Web:

www.dspdesign.com

(This page is intentionally left blank).

# CONTENTS

| 1 IN          | NTRODUCTION                                   | 1   |

|---------------|-----------------------------------------------|-----|

| 1.1           | OVERVIEW                                      | . 1 |

| 1.2           | XA270 FEATURES                                | . 1 |

| 1.3           | PRODUCT HANDLING AND ENVIRONMENTAL COMPLIANCE | . 2 |

| 1.3.1         | Anti-Static Handling                          |     |

| 1.3.2         | Electromagnetic Compatibility (EMC)           |     |

| 1.3.3         | RoHS Compliance                               |     |

| 1.4           | LAUNCHPAD APPLICATION DEVELOPMENT KIT         | 2   |

| 2 H           | IARDWARE                                      |     |

|               | XA270 CONNECTOR SUMMARY                       |     |

| 2.1           |                                               |     |

| 2.2           | XA270 BLOCK DIAGRAM<br>PROCESSOR              |     |

| 2.3           |                                               |     |

| 2.4           | SDRAM<br>FLASH MEMORY                         |     |

| 2.5           | COMPACT FLASH                                 |     |

| 2.6           |                                               |     |

| 2.7<br>2.7.1  | SERIAL PORTS<br>COM1, COM2 and COM3           |     |

| 2.7.1         | COM1, COM2 and COM3                           |     |

| 2.7.2         | COM4                                          |     |

| 2.7.3         | Electrical Ratings                            |     |

| 2.7.4         | DISPLAY                                       |     |

| 2.8.1         | Electrical Ratings                            |     |

| 2.8.2         | LCD Interface Boards                          |     |

| 2.9           | ETHERNET                                      |     |

| 2.10          | USB HOST                                      |     |

| 2.10          | USB CLIENT                                    |     |

| 2.12          | AUDIO                                         |     |

| 2.12.1        | Electrical Ratings                            |     |

| 2.13          | TOUCH-SCREEN                                  |     |

| 2.14          | ANALOG TO DIGITAL CONVERTER                   |     |

| 2.14.1        | Electrical Ratings                            |     |

| 2.15          | I <sup>2</sup> C EXPANSION                    | 16  |

| 2.15.1        | Electrical Ratings                            | 16  |

| 2.16          | PC/104 EXPANSION                              | 17  |

| 2.16.1        | Overview                                      |     |

| 2.16.2        | PC/104 Bus I/O Cycles                         |     |

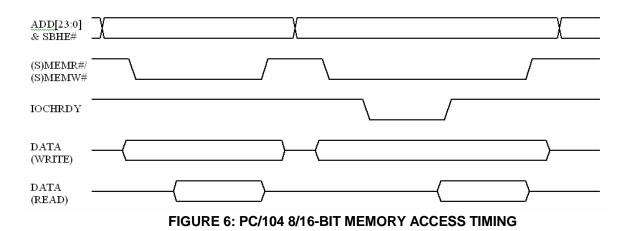

| 2.16.3        | PC/104 Bus Memory Cycles                      |     |

| 2.16.4        | PC/104 Expansion Connector                    |     |

| 2.16.5        | PC/104 Interrupts                             |     |

| 2.16.6        |                                               | 21  |

| 2.16.7        | PC/104 Expansion Bus Power and Reset          |     |

| 2.16.8        | Unsupported PC/104 Features and Signals       |     |

| 2.16.9        | Electrical Ratings                            |     |

| 2.17          | REAL TIME CLOCK                               |     |

| 2.18          | USER IO                                       | -   |

| 2.18.1        | System GPIO                                   |     |

| 2.18.2        | User GPIO                                     |     |

| 2.18.3        | Power Management GPIO                         |     |

| 2.18.4 2.18.5 | DIP Switches                                  |     |

| 2.18.5        | Electrical Ratings                            |     |

| 2.19          | Electrical Ratings                            |     |

| 2.19.1        | RESET                                         |     |

| 2.20          | SOLDER LINKS                                  |     |

| 2.21          | MISCELLANEOUS CONNECTORS                      | 26  |

| APPE                                                                                                                                  | ENDIX A: SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A1                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| A.1                                                                                                                                   | PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A1                                                                                                                               |

| A.2                                                                                                                                   | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| A.3                                                                                                                                   | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| A.4                                                                                                                                   | FLASH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| A.5                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| A.6                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| A.7                                                                                                                                   | USB HOSTUSB CLIENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

| A.8<br>A.9                                                                                                                            | SERIAL PORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

| A.3<br>A.10                                                                                                                           | COMPACT FLASH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| A.11                                                                                                                                  | ETHERNET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| A.12                                                                                                                                  | AUDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| A.13                                                                                                                                  | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A2                                                                                                                               |

| A.14                                                                                                                                  | PC/104 EXPANSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

| A.15                                                                                                                                  | I <sup>2</sup> C EXPANSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| A.16                                                                                                                                  | USER I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| A.17                                                                                                                                  | DIP SWITCHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

| A.18                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| A.19<br>A.20                                                                                                                          | RESET CIRCUIT<br>DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| A.20<br>A.21                                                                                                                          | WEIGHT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| A.22                                                                                                                                  | POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

| A.23                                                                                                                                  | OPERATING TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| A.24                                                                                                                                  | HUMIDITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

|                                                                                                                                       | NDIX B: XA270 DRAWINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

|                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

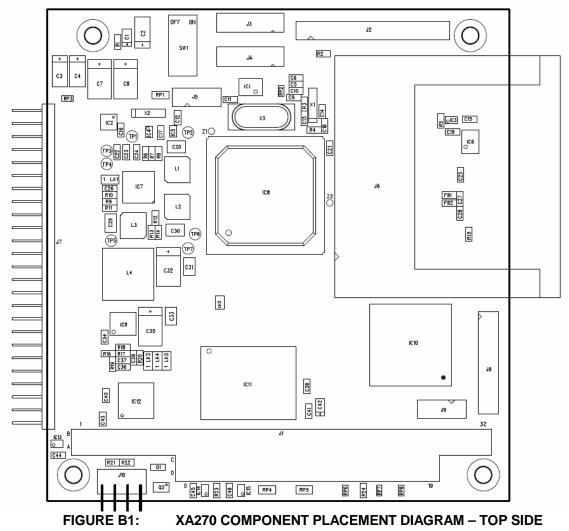

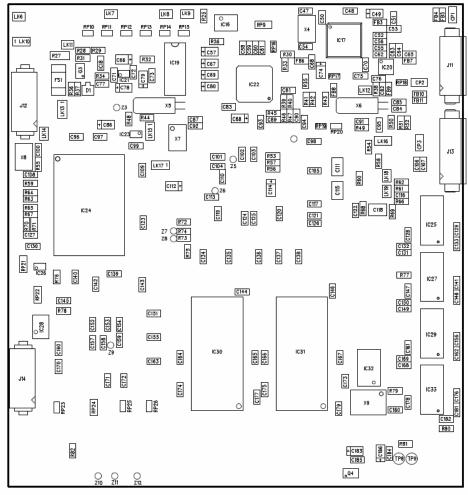

| B.1                                                                                                                                   | COMPONENT PLACEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

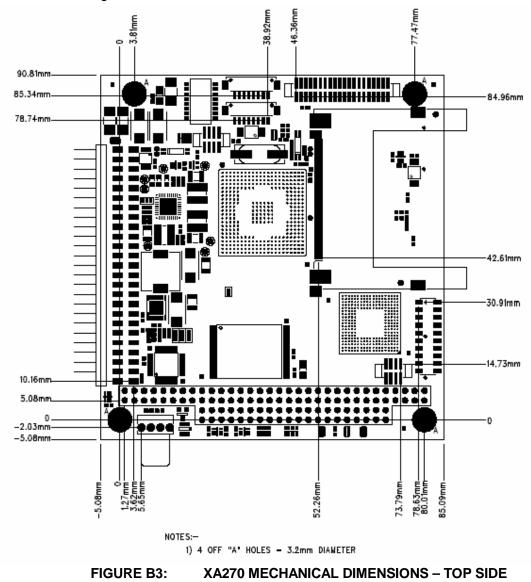

| B.2                                                                                                                                   | MECHANICAL DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | B3                                                                                                                               |

|                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| APPE                                                                                                                                  | ENDIX C: OPTIONS AND ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C1                                                                                                                               |

|                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| <b>APPE</b><br>C.1<br>C.2                                                                                                             | PROCESSOR MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C1                                                                                                                               |

| C.1                                                                                                                                   | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1<br>C1                                                                                                                         |

| C.1<br>C.2                                                                                                                            | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C1<br>C1                                                                                                                         |

| C.1<br>C.2<br>C.3<br>C.4                                                                                                              | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1<br>C1<br>C2<br>C3                                                                                                             |

| C.1<br>C.2<br>C.3<br>C.4<br><b>APPE</b>                                                                                               | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES<br>OTHER ACCESSORIES<br>ENDIX D: TFTIF LCD INTERFACE BOARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C1<br>C2<br>C3<br>C3                                                                                                       |

| C.1<br>C.2<br>C.3<br>C.4<br><b>APPE</b><br>D.1                                                                                        | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES<br>OTHER ACCESSORIES<br>ENDIX D: TFTIF LCD INTERFACE BOARDS<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C1<br>C1<br>C2<br>C3<br>C3                                                                                                       |

| C.1<br>C.2<br>C.3<br>C.4<br><b>APPE</b>                                                                                               | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31.<br>31-pin Connector Pin Assignments.                                                                                                                                                                                                                                                                                                                                                                                                         | C1<br>C2<br>C3<br>C3<br>D1                                                                                                       |

| C.1<br>C.2<br>C.3<br>C.4<br><b>APPE</b><br>D.1<br>D.1.1                                                                               | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES<br>OTHER ACCESSORIES<br>ENDIX D: TFTIF LCD INTERFACE BOARDS<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C1<br>C2<br>C3<br>D1<br>D1<br>D1                                                                                                 |

| C.1<br>C.2<br>C.3<br>C.4<br><b>APPE</b><br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4                                                    | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1                                                                         |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2                                                            | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES<br><b>ENDIX D: TFTIF LCD INTERFACE BOARDS</b><br>TFTIF31<br>31-pin Connector Pin Assignments.<br>Power Supply Selection: LK1<br>Pin 30 and 31 Configuration: LK2 and LK3.<br>Backlight Enable Signal.<br>TFTIF41                                                                                                                                                                                                                                                                                  | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1                                                       |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2<br>D.2.1                                                   | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br><b>ENDIX D: TFTIF LCD INTERFACE BOARDS</b><br>TFTIF31<br>31-pin Connector Pin Assignments.<br>Power Supply Selection: LK1<br>Pin 30 and 31 Configuration: LK2 and LK3.<br>Backlight Enable Signal.<br>TFTIF41<br>41-pin Connector Pin Assignments.                                                                                                                                                                                                                                            | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2                                                       |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2<br>D.2.1<br>D.2.2                                          | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D2                                     |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2<br>D.2.1<br>D.2.2<br>D.2.3                                 | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br><b>ENDIX D: TFTIF LCD INTERFACE BOARDS</b><br>TFTIF31<br>31-pin Connector Pin Assignments.<br>Power Supply Selection: LK1<br>Pin 30 and 31 Configuration: LK2 and LK3.<br>Backlight Enable Signal<br>TFTIF41.<br>41-pin Connector Pin Assignments.<br>Power Supply Selection: LK1<br>Pin 41 and 38 Configuration: LK2 and LK3.                                                                                                                                                                | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D3<br>D3                                           |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4                        | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D3<br>D4                                     |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3                 | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D4<br>D4<br>D4                               |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4        | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D4<br>D4<br>D4             |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4        | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D4<br>D4<br>D4             |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4<br>APPE         | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D3<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4 |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4<br>APPE<br>APPE | PROCESSOR MODULES<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS<br>DISPLAY ACCESSORIES<br>OTHER ACCESSORIES<br>ENDIX D: TFTIF LCD INTERFACE BOARDS<br>TFTIF31<br>31-pin Connector Pin Assignments<br>Power Supply Selection: LK1<br>Pin 30 and 31 Configuration: LK2 and LK3<br>Backlight Enable Signal<br>TFTIF41<br>41-pin Connector Pin Assignments<br>Power Supply Selection: LK1<br>Pin 41 and 38 Configuration: LK2 and LK3<br>Backlight Enable Signal<br>TFTIFK4V<br>AAVGA CRT / VGA INTERFACE BOARD<br>ENDIX E: TP400ET ETHERNET ADAPTER BOARD                                                           | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D3<br>D3<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4 |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4<br>APPE<br>APPE | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31                                                                                                                                                                                                                                                                                                                                                                                                                                               | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D3<br>D3<br>D4<br>D4<br>E1<br>E1<br>E1                   |

| C.1<br>C.2<br>C.3<br>C.4<br>D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.1.4<br>D.2.1<br>D.2.2<br>D.2.3<br>D.2.4<br>D.3<br>D.4<br>APPE<br>APPE | PROCESSOR MODULES.<br>LAUNCHPAD APPLICATION DEVELOPMENT KITS.<br>DISPLAY ACCESSORIES.<br>OTHER ACCESSORIES.<br>ENDIX D: TFTIF LCD INTERFACE BOARDS.<br>TFTIF31.<br>31-pin Connector Pin Assignments.<br>Power Supply Selection: LK1.<br>Pin 30 and 31 Configuration: LK2 and LK3.<br>Backlight Enable Signal.<br>TFTIF41.<br>41-pin Connector Pin Assignments.<br>Power Supply Selection: LK1.<br>Pin 41 and 38 Configuration: LK2 and LK3.<br>Backlight Enable Signal.<br>TFTIFKYV.<br>AAVGA CRT / VGA INTERFACE BOARD.<br>ENDIX E: TP400ET ETHERNET ADAPTER BOARD.<br>ENDIX F: TP300USB USB ADAPTER BOARD. | C1<br>C2<br>C3<br>D1<br>D1<br>D1<br>D1<br>D2<br>D2<br>D2<br>D2<br>D2<br>D3<br>D3<br>D4<br>D4<br>E1<br>E1<br>E1<br>G1             |

# XA270 Technical Reference Manual

| G.3  | MECHANICAL DRAWINGS          | G1 |

|------|------------------------------|----|

| G.4  | ETHERNET                     |    |

| G.5  | USB HOST                     |    |

| G.6  | USB CLIENT                   |    |

| G.7  | AUDIO                        |    |

| G.8  | COM1 AND COM2                |    |

| G.9  | COM3, COM4 AND COM5          | G5 |

| G.10 | ADC                          | G5 |

| G.11 | POWER                        |    |

| G.12 | SWITCHES                     |    |

| G.13 | I2C DIGITAL I/O              | G7 |

| G.14 | BATTERY                      | G8 |

| G.15 | TOUCHSCREEN                  | G8 |

| APPE | ENDIX H: XA270 LINK SETTINGS | H1 |

|      | NDIX I: FAULT REPORTING      |    |

# **FIGURES**

| FIGURE 1:  | THE XA270 LAUNCHPAD                             | 4  |

|------------|-------------------------------------------------|----|

| FIGURE 2:  | XA270 BLOCK DIAGRAM                             | 6  |

| FIGURE 3:  | INTEL® PXA270™ PROCESSOR BLOCK DIAGRAM          | 7  |

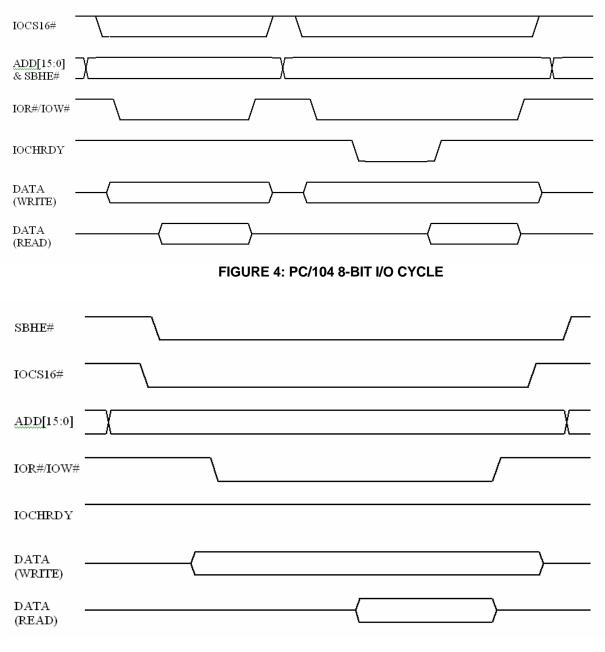

| FIGURE 4:  | PC/104 8-BIT I/O ACCESS TIMING                  | 18 |

| FIGURE 5:  | PC/104 16-BIT I/O ACCESS TIMING                 | 18 |

| FIGURE 6:  | PC/104 8/16-BIT MEMORY ACCESS TIMING            | 19 |

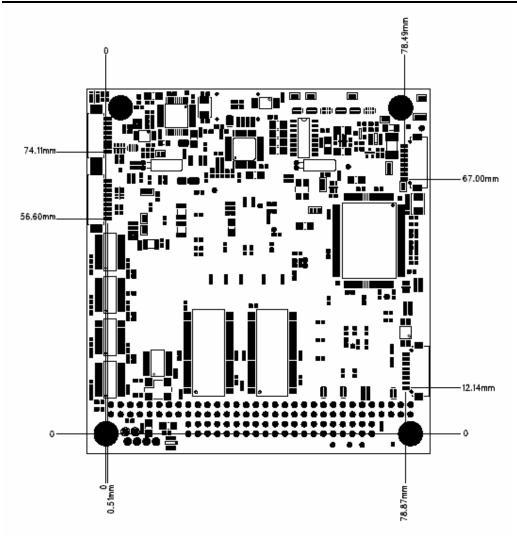

| FIGURE B1: | XA270 COMPONENT PLACEMENT DIAGRAM - TOP SIDE    | B1 |

| FIGURE B2: | XA270 COMPONENT PLACEMENT DIAGRAM - BOTTOM SIDE | B2 |

| FIGURE B3: | XA270 MECHANICAL DIMENSIONS - TOP SIDE          |    |

| FIGURE B4: | XA270 MECHANICAL DIMENSIONS                     | B4 |

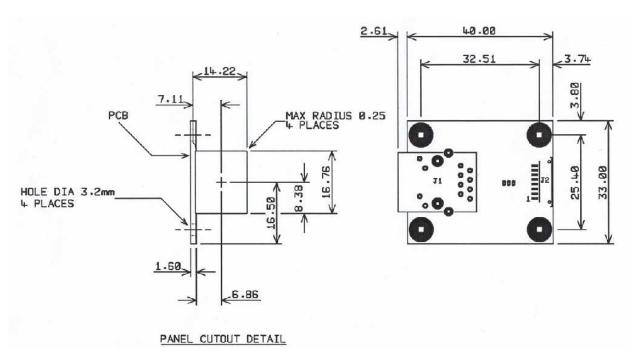

| FIGURE E1: | TP400ET MECHANICAL DRAWING                      | E1 |

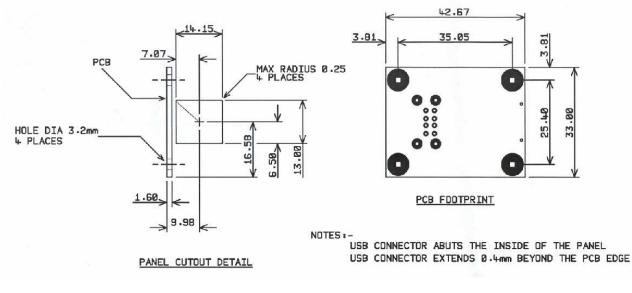

| FIGURE F1: | TP300USB MECHANICAL DRAWING                     | F1 |

# TABLES

| TABLE 1:               | XA270 CONNECTOR SUMMARY                                | F        |

|------------------------|--------------------------------------------------------|----------|

| TABLE 1:<br>TABLE 2:   | XA270 CONNECTOR SUMMARY<br>XA270 J7 PIN ASSIGNMENTS    |          |

| TABLE 2.<br>TABLE 3:   | XA270 J2 PIN ASSIGNMENTS                               |          |

| TABLE 3.<br>TABLE 4:   | XA270 J2 PIN ASSIGNMENTS                               |          |

| TABLE 4.               | XA270 J12 PIN ASSIGNMENTS                              |          |

| TABLE 5.               | XA270 J3 and J4 PIN ASSIGNMENTS                        | -        |

| TABLE 6.               | XA270 J14 PIN ASSIGNMENTS<br>XA270 J11 PIN ASSIGNMENTS |          |

| TABLE 7.               | XA270 J11 PIN ASSIGNMENTS                              |          |

| TABLE 8.               | XA270 J1 PIN ASSIGNMENTS                               |          |

| TABLE 9.               | SUPPORTED PC/104 INTERRUPTS AND GPIO ALLOCATION        |          |

| TABLE 10.              | PC/104 PULL UP RESISTORS                               |          |

| TABLE 11.<br>TABLE 12: | XA270 J8 PIN ASSIGNMENTS                               |          |

| TABLE 12.<br>TABLE 13: | XA270 J10 PIN ASSIGNMENTS                              |          |

| TABLE 13.              | PROCESSOR MODULES                                      |          |

| TABLE CT.              | LAUNCHPAD APPLICATION DEVELOPMENT KITS                 | 01<br>C1 |

| TABLE C2.              | DISPLAY ACCESSORIES                                    |          |

| TABLE C3.              | OTHER ACCESSORIES                                      |          |

| TABLE C4.              | TFTIF31 DISPLPAY PIN ASSIGNMENTS                       |          |

| TABLE D1:              | TETIEST PIN 30 AND PIN 31 CONNECTIONS                  |          |

| TABLE D2:              | TFTIF31 J3 PIN ASSIGNMENTS                             |          |

| TABLE DS:              | TFTIF41 DISPLAY PIN ASSIGNMENTS                        |          |

| TABLE D4:              | TETIE41 PIN 41 AND PIN 38 CONNECTIONS                  |          |

| TABLE DS:              | TFTIF41 J3 PIN ASSIGNMENTS                             |          |

| TABLE G1:              | J7 PIN ASSIGNMENTS                                     |          |

| TABLE G2:              | J5 PIN ASSIGNMENTS                                     |          |

| TABLE G3:              | J8 PIN ASSIGNMENTS                                     |          |

| TABLE G4:              | AUDIO SOCKETS.                                         |          |

| TABLE G5:              | J4 PIN ASSIGNMENTS                                     |          |

| TABLE G6:              | J20 PIN ASSIGNMENTS                                    |          |

| TABLE G7:              | J17. J18 AND J19 PIN ASSIGNMENTS                       |          |

| TABLE G8:              | J21 PIN ASSIGNMENTS                                    |          |

| TABLE G9:              | J3 PIN ASSIGNMENTS                                     |          |

| TABLE G10              | J6 PIN ASSIGNMENTS                                     | G7       |

| TABLE G11              |                                                        |          |

| TABLE G12:             |                                                        |          |

| TABLE H1:              | XA270 SOLDER LINK SETTINGS                             |          |

|                        |                                                        |          |

# **REVISION HISTORY**

| Date     | Rev | Ву  | CR No | Change                                                                                                                                                                               |

|----------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31/10/06 | B00 | IKD | 5601  | This is the first release of this manual.                                                                                                                                            |

| 1/11/06  | B01 | IKD | 5602  | ISA I/O and memory cycles amended.                                                                                                                                                   |

| 23/11/06 | B02 | IKD | 5609  | 8-bit and 16-bit ISA I/O cycles amended. References to<br>keypad/keyboard removed from sections 1.2, 2.1, 2.18.2 and A.16.<br>Connector J8 changed from 2.54mm to 2mm in Table 1 and |

|          |     |     |       | section 2.18.2. New paragraph added to section 2.18.2.                                                                                                                               |

# REFERENCES

Intel® PXA270 Processor Family Developer's Manual. PC/104 specification v2.5. Compact Flash specification v4.0. USB specification v1.1. RoHS Directive 2002/95/EC. I<sup>2</sup>C specification v2.0. IEEE 802.3 standard.

# 1 INTRODUCTION

This manual describes the B00 revision of the Artemis XA270 PC/104 form-factor processor board.

# 1.1 OVERVIEW

The XA270 is a RoHS compliant board using the Intel Xscale<sup>™</sup> PXA270<sup>™</sup> high performance RISC, low-power and high-integration systems-on-a-chip (SOC) processor. Low power consumption in normal operation and during sleep, make the XA270 ideal for battery operated systems.

The XA270 operates as a standalone module requiring only a single 5V input, or customers can either interface to the XACONN (a connector board for the XA270) or their own hardware.

# 1.2 XA270 FEATURES

- The Intel® PXA270<sup>™</sup> processor uses the integer instruction set of the ARM\* Architecture V5TE, providing high performance at very low power consumption when clocked at a maximum of 520MHz.

- PC/104 form factor, offering expansion using the PC/104 bus.

- 128Mbytes of SDRAM soldered to the board.

- 64Mbytes of Spansion Mirror-Bit Flash containing the operating system and Flash File System.

- On-board Compact Flash socket allowing a range of Compact Flash cards to be used for memory or peripheral expansion.

- 10/100 Base-T Ethernet port.

- 16-bit parallel TTL interface supporting a wide range of TFT LCDs at resolutions up to 800x600.

- Four-wire resistive touch screen controller.

- Two channel 12-bit ADC with 0-7.5V input range.

- Four USB 1.1 host ports.

- One USB 1.1 client port.

- Five serial ports. COM1, COM2 and COM3 are full function RS232, and COM4 and COM5 are limited function RS232.

- AC97 codec providing mono microphone input, stereo line outputs and stereo headphone outputs.

- Two RTCs, one with an input for an external battery.

- One I<sup>2</sup>C multi-master serial bus providing simple expansion.

- User I/O signals configurable as general purpose I/O.

- Reset input.

- The XA270 consumes very little power from a single 5V power supply even when operating at full speed. The operating system switches off unused circuitry for extremely low power consumption in power managed states.

### 1.3 PRODUCT HANDLING AND ENVIRONMENTAL COMPLIANCE

#### 1.3.1 Anti-Static Handling

The XA270 and peripherals contain CMOS devices, which can be damaged in the event of static electricity discharging through the device. Please observe anti-static handling precautions when handling the XA270 or when adding or removing connectors.

#### 1.3.2 Electromagnetic Compatibility (EMC)

Although the XA270 and peripherals utilise EMC filtering techniques, it is the user's responsibility to ensure that systems using the XA270 and peripherals are compliant with the appropriate EMC standards.

#### 1.3.3 RoHS Compliance

The XA270 and peripherals are only available as fully RoHS compliant prouducts and do not contain any of the six banned substances above the levels specified in the RoHS Directive 2002/95/EC.

## 1.4 LAUNCHPAD APPLICATION DEVELOPMENT KIT

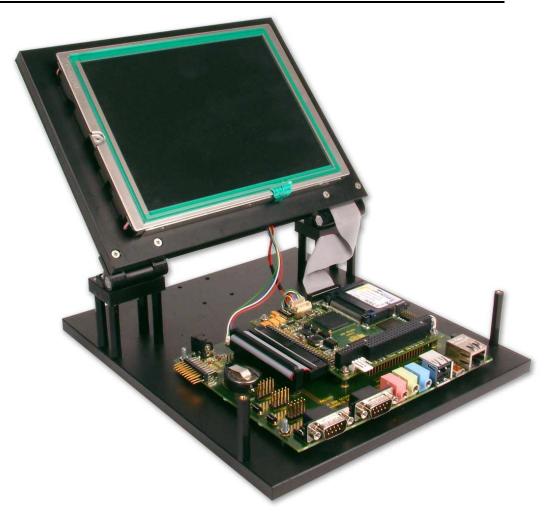

DSP Design strongly recommends that you begin your development project by using the LaunchPad Application Development Kit. This is a complete ready to use embedded computer system that is waiting for your application to be placed into the solid-state disk. Figure 1 shows the LaunchPad hardware. Not shown are the complete set of software, manuals and accessories (mouse, keyboard, PSU and cables) that are included in the LaunchPad package. The LaunchPad hardware comprises the following items mounted on a laptop style stand:

- XA270 processor board.

- XACONN connector board.

- LCD and backlight inverter.

- Touchcreen.

The XACONN is a connector board for the XA270 providing standard PC connectors. Please refer to Appendix G for further details.

Using the LaunchPad will greatly reduce your development time, so your product will get to market sooner at a fraction of the engineering costs normally associated with products.

We have two objectives as you begin to use your new LaunchPad Application Development Kit.

Firstly, we expect that within an hour of receiving your LaunchPad you will have set up the hardware, connected it to your LAN and run the demonstration mouse application.

Secondly, we expect that within a day you will have installed the development tools, compiled a sample application, downloaded it to the target hardware, and experimented with debugging this application remotely from the host computer.

So on the second day you can begin developing your real application.

For full details of the LaunchPad Application Development kits see our web site at <u>www.dspdesign.com/launchpad</u>.

# FIGURE 1: THE XA270 LAUNCHPAD

# 2 HARDWARE

# 2.1 XA270 CONNECTOR SUMMARY

Table 1 provides a summary of the connectors available on the XA270, along with part numbers where appropriate. The function and pin assignment for each connector is covered in other sections of this manual.

| Ref Des | Function         | Connector Type or Part Number                        |

|---------|------------------|------------------------------------------------------|

| J1      | PC/104 expansion | 104-way PC/104.                                      |

| J2      | LCD              | 2x20-way 1.27mm pitch header.                        |

| J3      | USB Host         | 8-way board to wire, Hirose DF13-8P-1.25V.           |

| J4      | USB Host         | 8-way board to wire, Hirose DF13-8P-1.25V.           |

| J5      | Processor JTAG   | 2x10-way 1.27mm pitch header.                        |

| J6      | Compact Flash    | Type I and II.                                       |

| J7      | General Purpose  | 2x25-way 2.54mm pitch header.                        |

| J8      | GPIO             | 2x10-way 2mm pitch header.                           |

| J9      | CPLD JTAG        | 2x10-way 1.27mm pitch header.                        |

| J10     | Input Power      | 4-way 2.54mm pitch board to wire with friction lock. |

| J11     | Audio            | 8-way board to wire, Molex 53261-0871.               |

| J12     | Ethernet         | 8-way board to wire, Hirose DF13-8P-1.25H.           |

| J13     | ADC/Touchscreen  | 9-way board to wire, Molex 53261-0971.               |

| J14     | USB Client       | 8-way board to wire, Hirose DF13-8P-1.25H.           |

TABLE 1: XA270 CONNECTOR SUMMARY

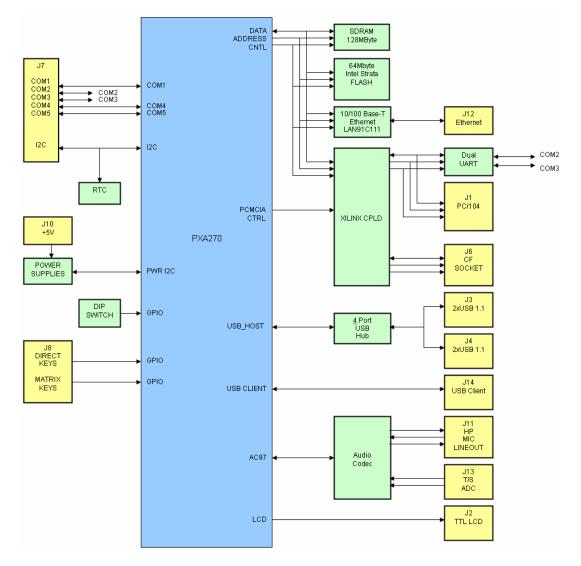

# 2.2 XA270 BLOCK DIAGRAM

Figure 2 shows the block diagram of the XA270.

FIGURE 2: XA270 BLOCK DIAGRAM

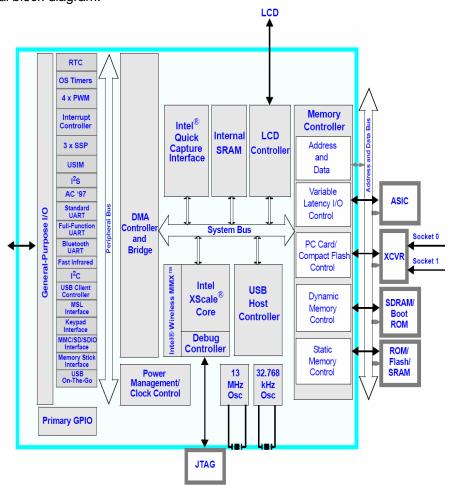

## 2.3 PROCESSOR

The Intel® PXA270<sup>™</sup> processor is an integrated system-on-a-chip microprocessor for high performance, dynamic, low-power portable handheld and hand-set devices as well as embedded platforms. Figure 3 shows the Intel® PXA270<sup>™</sup> processor functional block diagram.

FIGURE 3: INTEL® PXA270™ PROCESSOR BLOCK DIAGRAM

## 2.4 SDRAM

The XA270 provides 128Mbytes of Synchronous Dynamic RAM (SDRAM) as standard, soldered to the PCB.

The SDRAM is connected to the Intel® PXA270<sup>™</sup> processor via a shared 32-bit wide system bus and operates at a maximum frequency of 104MHz.

Some of the SDRAM is allocated to the internal LCD controller, using a technique referred to as unified memory architecture (UMA).

## 2.5 FLASH MEMORY

The XA270 provides 64Mbytes of Spansion Mirror-Bit Flash as standard, soldered to the PCB.

The 16-bit wide Flash is connected to the Intel® PXA270<sup>™</sup> processor via the shared system bus.

The Flash typically contains the operating system and a Flash File System (FFS) for storing user applications and data. Please refer to the Developer's Guide for the specific operating system for further details.

## 2.6 COMPACT FLASH

The XA270 provides a single on-board Compact Flash (CF) socket suitable for 3.3V memory and I/O cards, providing both memory and peripheral expansion. The CF socket is mapped to the Intel® PXA270<sup>™</sup> PC Card Controller socket 0 space.

Power switching circuitry and buffers are provided to isolate the Compact Flash card reducing power consumption and to provide hot swap capability under operating system control.

## 2.7 SERIAL PORTS

The XA270 provides five RS232 serial ports that are labelled as COM1 through COM5.

Each UART is similar to the industry standard 16550 UART and can be independently configured for 5-8 data bits, 1-2 stop bits, even, odd, mark or no parity and baud rates supported by the operating system. Please refer to the Developer's Guide for the specific operating system for further details.

Each port uses ICL3243E transmitters/receivers, which meet EIA/TIA-232 and V.28/V.24 specifications. Additionally they provide  $\pm$ 15KV ESD protection (IEC61000-4-2 Air Gap and Human Body Model).

All five ports are available on a 50-way dual row 0.1" pitch right angle pin header J7. The pin assignments for J7 are provided in Table 2. J7 also provides other functions, which are described in later sections.

The pin assignments for COM1 to COM4 are arranged to interface with IDC D-type connectors simplifying the assembly of cables.

| PIN | NAME   | NOTES                                        | PIN | NAME  | NOTES                                              |

|-----|--------|----------------------------------------------|-----|-------|----------------------------------------------------|

|     |        |                                              | -   |       |                                                    |

| 1   | DCD1   | COM1 RS232 carrier<br>detect input           | 2   | DSR1  | COM1 RS232 data set<br>ready input                 |

| 3   | RXD1   | COM1 RS232 receive<br>data input             | 4   | RTS1  | COM1 RS232 request to<br>send output               |

| 5   | TXD1   | COM1 RS232 transmit data output              | 6   | CTS1  | COM1 RS232 clear to send input                     |

| 7   | DTR1   | COM1 RS232 data<br>terminal ready output     | 8   | RI1   | COM1 RS232 ring indicator input                    |

| 9   | GND    | COM1 ground                                  | 10  | DCD2  | COM2 RS232 carrier detect input                    |

| 11  | DSR2   | COM2 RS232 data set<br>ready input           | 12  | RXD2  | COM2 RS232 receive data input                      |

| 13  | RTS2   | COM2 RS232 request to send output            | 14  | TXD2  | COM2 RS232 transmit data output                    |

| 15  | CTS2   | COM2 RS232 clear to send input               | 16  | DTR2  | COM2 RS232 data terminal ready output              |

| 17  | RI2    | COM2 RS232 ring<br>indicator input           | 18  | GND   | COM2 ground                                        |

| 19  | DCD3   | COM3 RS232 carrier detect input              | 20  | DSR3  | COM3 RS232 data set<br>ready input                 |

| 21  | RXD3   | COM3 RS232 receive data input                | 22  | RTS3  | COM3 RS232 request to send output                  |

| 23  | TXD3   | COM3 RS232 transmit data output              | 24  | CTS3  | COM3 RS232 clear to send input                     |

| 25  | DTR3   | COM3 RS232 data terminal ready output        | 26  | RI3   | COM3 RS232 ring indicator input                    |

| 27  | GND    | COM3 ground                                  | 28  | GPIO9 | General purpose<br>input/output – OS<br>dependant. |

| 29  | RES    | Do not connect, reserved for DSP Design use. | 30  | RXD4  | COM4 RS232 receive data input                      |

| 31  | RTS4   | COM4 RS232 request to<br>send output         | 32  | TXD4  | COM4 RS232 transmit data output                    |

| 33  | CTS4   | COM4 RS232 clear to send input               | 34  | GND   | Ground                                             |

| 35  | RESET# | Reset input                                  | 36  | GND   | Ground                                             |

| 37  | SDA    | I2C Data input/output                        | 38  | SCL   | I2C Clock output                                   |

| 39  | RXD5   | COM5 RS232 receive data input                | 40  | TXD5  | COM5 RS232 transmit data output                    |

| 41  | RES    | Do not connect, reserved for DSP Design use. | 42  | RES   | Do not connect, reserved for DSP Design use.       |

| 43  | RES    | Do not connect, reserved for DSP Design use. | 44  | RES   | Do not connect, reserved for DSP Design use.       |

| 45  | GND    | Ground                                       | 46  | BATT  | Battery Input                                      |

| 47  | VCC    | +5V Supply                                   | 48  | VCC   | +5V Supply                                         |

| 49  | GND    | Ground                                       | 50  | GND   | Ground                                             |

| TABLE 2: | XA270 - | J7 PIN | ASSIGNMENTS |

|----------|---------|--------|-------------|

|----------|---------|--------|-------------|

## 2.7.1 COM1, COM2 and COM3

COM1, COM2 and COM3 are standard full function eight-wire RS232 ports.

COM1 is implemented in the Intel® PXA270<sup>™</sup> processor. COM2 and COM3 are implemented in a XR16C2550 DUART attached to the PC/104 bus on the XA270.

These ports support, three transmit signals (TXD, RTS and DTR) and five receive signals (RXD, CTS, DCD, DSR and RI).

### 2.7.2 COM4

COM4 is a four-wire RS232 port implemented in the Intel® PXA270<sup>™</sup> processor. The port supports two transmit signals (TXD and RTS) and two receive signals (RXD and CTS).

### 2.7.3 COM5

COM5 is a two-wire RS232 port implemented in the Intel® PXA270<sup>™</sup> processor. The port supports one transmit signal (TXD) and one receive signal (RXD).

### 2.7.4 Electrical Ratings

All five ports have an absolute maximum input voltage of  $\pm 25V$  on any receiver input (RXD, CTS, DCD, DSR and RI) and a minimum output voltage swing of  $\pm 5V$  on any transmitter output.

## 2.8 DISPLAY

The XA270 provides a LCD controller implemented in the Intel® PXA270<sup>™</sup> processor, which is capable of driving 16bpp colour LCD panels with resolutions up to 800x600. The parallel TTL interface has been designed to be compatible with a range of interface boards from DSP Design, allowing connection to a variety of common displays. Please refer to Appendix D for a detailed description of each board.

Several TFT panels from different manufacturers have been successfully tested with the XA270. Please refer to the Developer's Guide for the specific operating system for further details.

Due to the unified memory architecture of the Intel® PXA270<sup>™</sup> processor, there are bus bandwidth limitations, which will effect display refresh rates at display resolutions above 640x480. Please refer to the Developer's Guide for the specific operating system for further details.

The LCD interface is available on a 40-way dual row 0.05" pitch pin header J2. Table 3 shows the pin assignment for J2.

J2 supports a generic LCD interface used on all DSP Design processor boards, some of which support 24bpp. Bits not used by the XA270 are connected to GND on J2.

| PIN | NAME NOTES |                       | PIN | NAME     | NOTES               |

|-----|------------|-----------------------|-----|----------|---------------------|

|     |            |                       |     |          |                     |

| 1   | ENBKL      | Active high backlight | 2   | ENAVDD   | Active high LCD     |

|     |            | enable signal         |     |          | power enable signal |

| 3   | GND        | Ground                | 4   | PCLK     | Pixel clock         |

| 5   | GND        | Ground                | 6   | HSYNC    | Horizontal sync     |

| 7   | GND        | Ground                | 8   | VSYNC    | Vertical sync       |

| 9   | GND (R0)   | Ground                | 10  | GND (R1) | Ground              |

| 11  | GND (R2)   | Ground                | 12  | R3       | Data Bit            |

| 13  | GND        | Ground                | 14  | R4       | Data Bit            |

| 15  | R5         | Data Bit              | 16  | R6       | Data Bit            |

| 17  | GND        | Ground                | 18  | R7       | Data Bit            |

| 19  | -          | Reserved. Do not      | 20  | -        | Reserved. Do not    |

|     |            | use.                  |     |          | use.                |

| 21  | GND        | Ground                | 22  | G2       | Data Bit            |

| 23  | G3         | Data Bit              | 24  | G4       | Data Bit            |

| 25  | VCC3V      | 3.3V supply           | 26  | G5       | Data Bit            |

| 27  | G6         | Data Bit              | 28  | G7       | Data Bit            |

| 29  | VCC3V      | 3.3V supply           | 30  | GND (B0) | Ground              |

| 31  | GND (B1)   | Ground                | 32  | GND (B2) | Ground              |

| 33  | VCC/PWM    | 5V supply or PWM      | 34  | B3       | Data Bit            |

| 35  | B4         | Data Bit              | 36  | B5       | Data Bit            |

| 37  | VCC        | 5V supply             | 38  | B6       | Data Bit            |

| 39  | B7         | Data Bit              | 40  | ENAB     | Data enable signal  |

## XA270 Technical Reference Manual

J2 pin 33 can be configured as either VCC (+5V) or PWM via a two position solder link LK10. In position 1-2, VCC is connected to J2 pin 33. In position 2-3, a GPIO signal PWM is connected to J2 pin 33. The PWM signal is configured as a pulse width modulated output by the operating system providing backlight brightness control. Please refer to the Developer's Guide for the specific operating system for further details.

## 2.8.1 Electrical Ratings

The LCD bus has the following characteristics:

- $V_{OH} = 2.7V \text{ min } @ I_{OH} = -3mA.$

- $V_{OL} = 0.3V \text{ max} @ I_{OL} = 3mA.$

#### 2.8.2 LCD Interface Boards

At present DSP Design offers three TFT LCD interface boards, which can be used with the XA270. The TFTIF31, TFTIF41 and TFTIFKYV boards interface to TFT LCDs with conventional parallel interfaces (6 bits of red, green and blue, plus timing signals). Details of the interface boards are provided in Appendix D.

# 2.9 ETHERNET

The XA270 provides a single IEEE 802.3/802.3u compliant 10/100-Base-T Ethernet port implemented in the LAN91C111 controller with integrated MAC and PHY. The 32-bit controller interfaces to the Intel® PXA270 processor via the shared system bus.

Connection to the Ethernet port is made through a Hirose DF13-8P-1.25H(21) connector J12. The pin assignments for J12 are provided in Table 4.

| PIN | NAME      | NOTES                                           |

|-----|-----------|-------------------------------------------------|

| 1   | RX+       | Twisted pair receiving data                     |

| 2   | RX-       | Twisted pair receiving data                     |

| 3   | VCC/VCC3V | Selects the center tap voltage                  |

| 4   | GND       | Ground                                          |

| 5   | LINKLED#  | Controls LINK status LED in the RJ45 connector  |

| 6   | LANLED#   | Controls LAN activity LED in the RJ45 connector |

| 7   | TX-       | Twisted pair transmitting data                  |

| 8   | TX+       | Twisted pair transmitting data                  |

#### TABLE 4: XA270 J12 PIN ASSIGNMENTS

The XA270 connects to a network through one of two interface boards available from DSP Design.

- The TP400ET is a small board, which contains the Ethernet RJ45 connector (with integrated magnetics and LEDs), EMC filters and ESD protection. J12 on the XA270 connects to the TP400ET via a short length of CAT-5 twisted pair cable, the TB486ET-CAB. The TP400ET has been designed to be mounted in an enclosure allowing EMC filtering to be optimised. Details of the TP400ET are provided in Appendix E.

- The XACONN is a connector breakout board, which the XA270 plugs into, providing the Ethernet RJ45 connector (with integrated magnetics and LEDs), EMC filters and ESD proctection. J12 on the XA270 connects to the XACONN via a short length of CAT-5 twisted pair cable. Details of the XACONN are provided in Appendix G.

ESD protection is not provided on the XA270, but is available on the TP400ET and XACONN.

## 2.10 USB HOST

The XA270 provides four USB 1.1 compliant host posts available on two Hirose DF13-8P-1.25V connectors J3 and J4. A TUSB2046 USB 1.1 compliant hub expands the single host port available on the Intel® PXA270 processor into four ports.

Each USB port includes a SN75240 transient suppressor, providing  $\pm$ 15KV ESD protection (IEC61000-4-2 Air Gap and Human Body Model).

### XA270 Technical Reference Manual

Each USB port is powered by a current-limited 5V power supply line. An on-board USB power controller chip limits the current sent to each peripheral at slightly above the 500mA minimum set by the USB specification.

| PIN | NAME | NOTES                                            |  |

|-----|------|--------------------------------------------------|--|

| 1   | DM1  | Port 1 USB negative signal                       |  |

| 2   | DP1  | Port 1 USB positive signal                       |  |