# Driving deployment of wide-bandgap power devices on 200mm

Hans Auer and scientist Dr Dominik Jaeger of Evatec introduce the advantages of wide-bandgap (WBG) power devices and some of the development challenges ahead.

oday's silicon power device technology has evolved to a very mature state. However, with limited options for major future innovation steps, that is where wide-bandgap (WBG) semiconductors now have the opportunity to step in. Their capabilities to operate at higher voltages and temperatures — along with significantly lower switching losses - enable power circuits to run at much higher frequencies, resulting in reduced size. For example, the heat-sink size for variable-speed drives of industrial electric motors could be reduced by more than 50%. Batteryoperated vehicles, mobile computing or wearable electronics could all benefit from longer battery lives. Electric drives like fans, pumps, compressors, conveyer systems etc could all use less power, achieving overall energy savings of more than 20% once wide adoption is achieved.

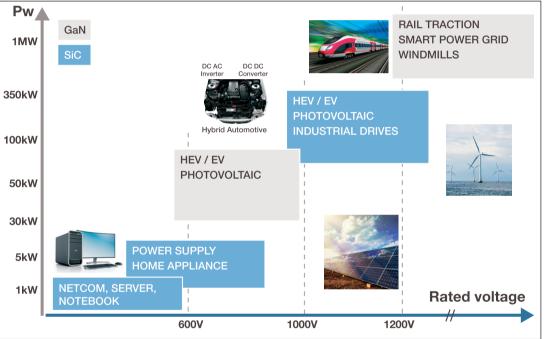

The two most interesting materials for fabricating WBG power devices are silicon carbide (SiC) and gallium nitride (GaN).

Figure 1: Application fields for SiC and GaN power devices.

Hans Auer, Senior Manager Product Marketing.

semiconductorTODAY Compounds & Advanced Silicon • Vol. 11 • Issue 10 • December 2016/January 2017

# Technology focus: Power electronics 71

| GaN cap layer                           | 3nm    |

|-----------------------------------------|--------|

| AIGaN barrier 25%                       | 25nm   |

| GaN:nid                                 | 400nm  |

| GaN:C                                   | 1050nm |

| AIN interlayer                          | 25nm   |

| GaN:C                                   | 710nm  |

| AIN interlayer                          | 25nm   |

| GaN:C                                   | 550nm  |

| Al <sub>0.25</sub> Ga <sub>0.75</sub> N | 550nm  |

| Al <sub>0.65</sub> Ga <sub>0.35</sub> N | 300nm  |

| Al <sub>0.83</sub> Ga <sub>0.17</sub> N | 250nm  |

| AIN                                     | 100nm  |

| Si (111)                                |        |

|                                         |        |

#### Film data of sputtered AIN overgrown with AIGaN

XRD FWHM 00.2 (tilt) of 0.127° Surface roughness comparable to reference (RMS<0.2nm) 2DEG depth 35.0nm  $N_{min} \approx 10^{13}/cm^3$  $V_{th} \approx -3.3V$  $N_s \approx 5 \times 10^{12} / \text{cm}^2$

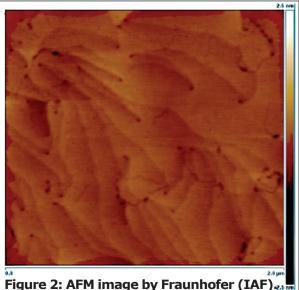

#### Data of sputtered AIN buffer layer: film properties (100nm AIN on Si)

| Deposition rate (nm/s)      | 0.2                            |

|-----------------------------|--------------------------------|

| Thickness uniformity        | ±3.5%                          |

| Film stress (GPa)           | 0.6 (tensile)                  |

| XRD rocking curve AIN (002) | < 2500arcsec                   |

| XRD rocking curve GaN (102) | Comparable to MOCVD AIN buffer |

| Roughness (AFM, RMS)        | <1nm                           |

## An alternative production approach

While the SiC power devices are manufactured from

Figure 3: HEMT structure, as overgrown by Fraunhofer Institute for Applied Solid State Physics (IAF).

Although their use is still small today, the projected sales growth for these devices is between 50% and 80% for the next 5–10 years. SiC is the preferred material for device ratings in excess of 600V with applications in hybrid/electric vehicles (HEV), solar inverters and industrial power supplies while, due to its low switching loss, GaN is expected to dominate low-voltage applications, with a focus on DC/DC converters/commodity power supplies and motor drives.

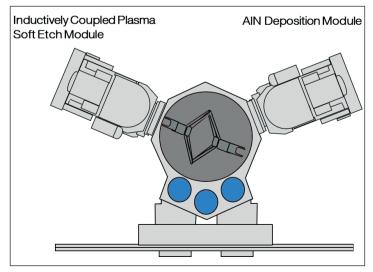

Figure 4: CLUSTERLINE 200 II.

bulk SiC wafers, GaN devices are made on silicon wafers with epitaxially grown GaN, a lower-cost method than building the devices from bulk GaN. The main challenge in manufacturing GaN-on-silicon substrates is the high lattice strain at the GaN/Si interface, which necessitates an aluminium nitride (AIN) buffer layer for subsequent GaN crystal growth. While this layer is traditionally formed by metal-organic chemical vapor deposition (MOCVD), sputtered AIN has recently made inroads due to the significantly lower cost over MOCVD. Compared to MOCVD deposition, sputtering of AIN enables higher deposition rates, and the amount of cleaning cycles in the MOCVD reactor can be reduced dramatically. Furthermore, the pit density in the GaN MOCVD is reduced by the AIN PVD buffer layer and hence results in a higher yield.

### The PVD solution is ready to implement

A manufacturing solution already used in the LED market for GaN-on-Si is also now ready to be deployed for the power device market. Process integration work, with a focus on 8" silicon wafers, is ongoing with multiple partners. The sputtered AIN buffer layers represent savings in MOCVD capacity of >20%. ■

www.evatecnet.com/technology/technology-overview/ layers-magazine

#### **Hardware information**

Standard soft etch-module

Heated chuck in the process module at T>800°C with good uniformity (<40°C)

Standard AIN deposition hardware (cathode) for full face deposition

Temperature-characterization in Transfer-Module