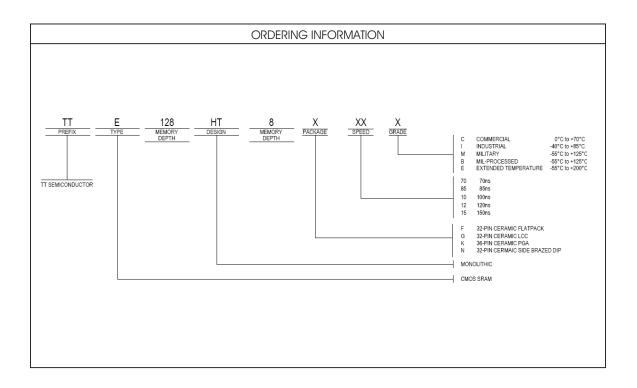

## Extended Temperature, 5 Volt, 1 Megabit EEPROM TTE128HT8F/G/K/N

### DESCRIPTION:

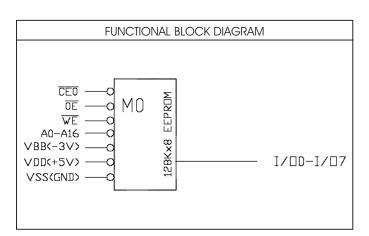

The TTE128HT8F/G/K/N memory contains a 128Kx8 EEPROMs, packaged in a hermetically sealed cermaic package, making the modules suitable for commercial, industrial military and extended temperature applications. The modules are organized in a 128Kx8 configuration supporting 256-Byte Page write operations. This keeps write cycle timing down to as low as 19us/Byte which enables completely writing one memory in less than 2.5 seconds.

### FEATURES:

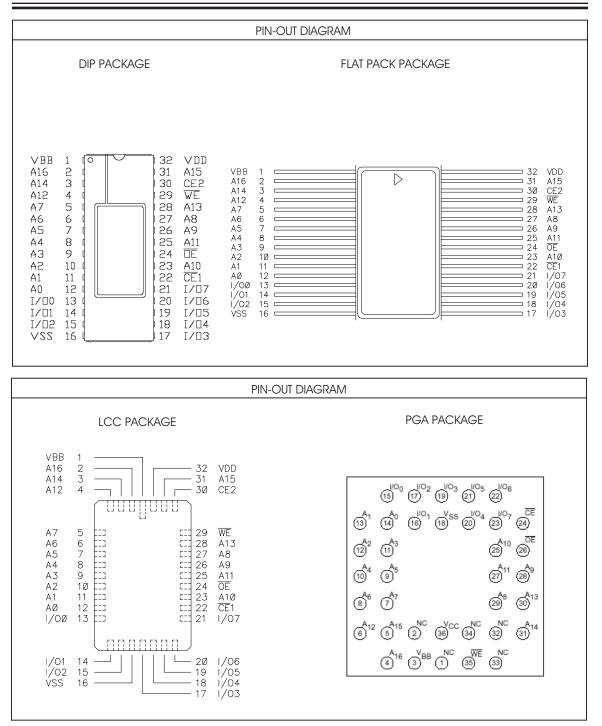

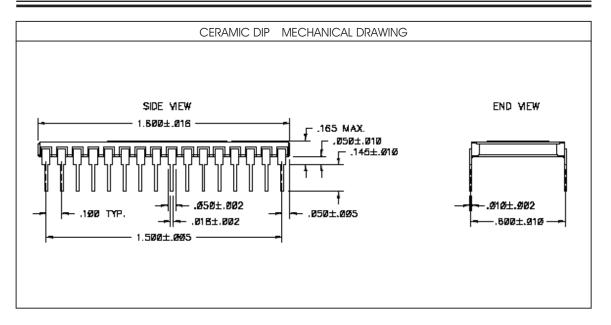

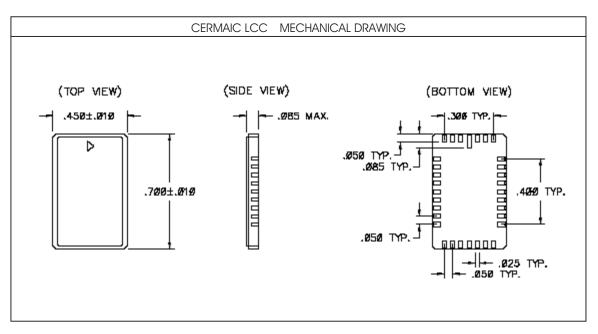

Organizations Available: 128Kx8 Access Times: 200, 250ns 200°C Extended Temperature Range Full Functionality Single +5V Power Supply, 5% Tolerance Single Byte or 2 to 256 Byte Page Writes Self Timed Writes - No Erase before Writes Easy Programming Algorithms, No Overerase Problem Data Retention: 100 Years. Endurance: 10,000 Write Cycles Packages Available: 32 - Pin Ceramic Side Brazed DIP 32 - Pin Ceramic FLATPACK 32 - Pin Ceramic LCC 36 - Pin Ceramic PGA

| PIN NAMES       |                   |  |  |

|-----------------|-------------------|--|--|

|                 |                   |  |  |

| A0 - A16        | Address Inputs    |  |  |

| I/O0 - I/O8     | Data Input/Output |  |  |

| WE              | Write Enable      |  |  |

| <u>CE</u> 0     | Low Chip Enables  |  |  |

| ŌĒ              | Output Enable     |  |  |

| V <sub>BB</sub> | Back Bias (-3V)   |  |  |

| V <sub>DD</sub> | Power (+5V)       |  |  |

| V <sub>SS</sub> | Ground            |  |  |

| N.C.            | No Connect        |  |  |

BACK BIAS VOLTAGE (VBB) It is required to provide -3V on pin 40 (D3). This negative voltage improves higher temperature functionality.

This document contains information on a product that is currently released to production at TI Semiconductor, Inc. TI Semiconductor reserves the right to change products or specifications herein without prior notice.

TT Semiconductor, Inc.

### TT Semiconductor, Inc.

## TTE128HT8F/G/K/N

### DEVICE OPERATION

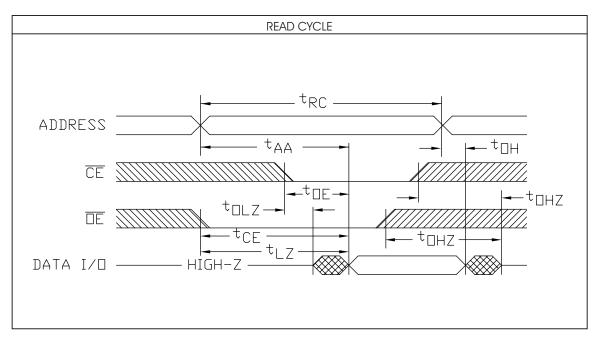

### Read

Read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This two line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedance state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

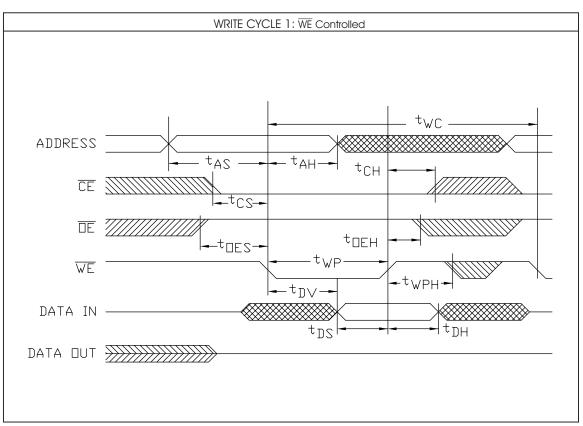

### Write

Write operations are initiated when both  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{OE}$  is HIGH. The TTE128HT8 supports both a  $\overline{CE}$  and  $\overline{WE}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs last. Similarly, the data is latched internally by the rising edge of either  $\overline{CE}$  or  $\overline{WE}$ , which-ever occurs first. A byte write operation, once initiated, will automatically continue to completion, typically within 5ms.

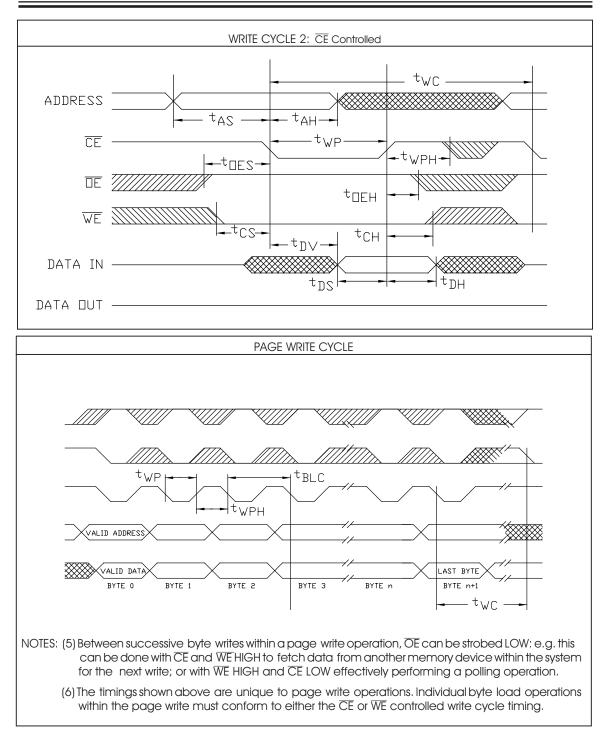

### Page Write Operation

The page write feature of the TTE128HT8 allows one entire memory to be written in 5 seconds. Page write allows two to two hundred fifty-six bytes of data to be consecutively written to the TTE128HT8 prior to the commencement of the internal programming cvcle. The host can fetch data from another device within the system during a page write operation (change the source address), but the page address (A8 through A16) for each subsequent valid write cycle to the part during this operation must be the same as the initial page address. The page write mode can be initiated during any write operation. Following the initial byte write cycle, the host can write an additional one to two hundred fifty-six bytes in the same manner as the first byte was written. Each successive byte load cycle, started by the  $\overline{WE}$ HIGH to LOW transition, must begin within 100ms of the falling edge of the preceding  $\overline{WE}$ . If a subsequent WE HIGH to LOW transition is not detected within 100ms, the internal automatic programming cycle will commence. There is no page write window limitation. Effectively the page write window is infinitely wide, so long as the host continues to access the device within the byte load cvcletime of 100ms.

### HARDWARE DATA PROTECTION

The TTE128HT8 provides three hardware features that protect nonvolatile data from inadvertent writes.

- Default V  $_{\rm CC}\,$  Sense—All functions are inhibited when V  $_{\rm CC}$  is  $\,$  3.4V.

- Write inhibit—Holding either OELOW, WE HIGH, or CE HIGH will prevent an inadvertent write cycle during power-up and power-down, maintaining data integrity.

### SYSTEM CONSIDERATIONS

Because the TTE128HT8 is frequently used in large memory arrays it is provided with a two line control architecture for both read and write operations. Proper usage can provide the lowest possible power dissipation and eliminate the possibility of contention where multiple I/O pins share the same bus.

It has been demonstrated that markedly higher temperature performance can be obtained from this device if  $\overline{CE}$  is left enabled throughout the read and write operation.

To gain the most benefit it is recommended that  $\overline{CE}$  be decoded from the address bus and be used as the primary device selection input. Both  $\overline{OE}$  and  $\overline{WE}$  would then be common among all devices in the array. For a read operation this assures that all deselected devices are in their standby mode and that only the selected device(s) is outputting data on the bus.

Because the TTE128HT8 has two power modes, standby and active, proper decoupling of the memory array is of prime concern. Enabling  $\overline{CE}$  will cause transient current spikes. The magnitude of these spikes is dependent on the output capacitive loading of the I/Os. Therefore, the larger the array sharing a common bus, the larger the transient spikes. The voltage peaks associated with the current transients can be suppressed by the proper selection and placement of decoupling capacitors. As a minimum, it is recommended that a 0.1 F high frequency ceramic capacitor be used between V<sub>DD</sub> and V<sub>SS</sub> at each device. Depending on the size of the array, the value of the capacitor may have to be larger.

In addition, it is recommended that a 4.7 F electrolytic bulk capacitor be placed between  $V_{DD}$  and  $V_{SS}$  for each four modules employed in the array. This bulk capacitor is employed to overcome

## tte128ht8f/G/K/N

TT Semiconductor, Inc.

| ABSOLUTE MAXIMUM RATINGS*              |  |

|----------------------------------------|--|

| The second second second second second |  |

| iemperature under Blas         |

|--------------------------------|

| TTE128HT855°C-200°C            |

| Voltage on any Pin with        |

| Respect to Vss1V to $+7V$ D.C. |

| Output Current5mA              |

| Lead Temperature               |

| (Soldering, 10 seconds)220°C   |

#### \*COMMENT

Stresses above thoselisted under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

| RECOMMENDED OPERATING RANGE |                    |      |      |         |      |

|-----------------------------|--------------------|------|------|---------|------|

| Symbol                      | Characteristic     | Min. | Typ. | Max.    | Unit |

| Vdd                         | Supply Voltage     | 4.75 | 5.0  | 5.25    | V    |

| VBB                         | Back Bias Voltage  | -3.3 | -3.0 | -2.7    | V    |

| Vih                         | Input HIGH Voltage | 2.2  |      | VDD + 1 | V    |

| VIL                         | Input LOW Voltage  | -1   |      | 0.6     | V    |

| Ta                          | Operating Temp     | -40  | +25  | +175    | °C   |

| DC OUTPUT CHARACTERISTICS                  |              |                           |     |     |      |  |

|--------------------------------------------|--------------|---------------------------|-----|-----|------|--|

| Symbol Parameter Conditions Min. Max. Unit |              |                           |     |     | Unit |  |

| VOH                                        | HIGH Voltage | $I_{OH} = -1.0 \text{mA}$ | 2.4 |     | V    |  |

| Vol                                        | LOW Voltage  | I <sub>OL</sub> =2.1mA    |     | 0.4 | V    |  |

| TRUTH TABLE              |    |    |    |         |                   |  |

|--------------------------|----|----|----|---------|-------------------|--|

| Mode                     | CE | WE | OE | I/O Pin | Supply<br>Current |  |

| Not Selected             | Н  | Х  | Х  | HIGH-Z  | Standby           |  |

| D <sub>OUT</sub> Disable | L  | Н  | Н  | HIGH-Z  | Active            |  |

| Read                     | L  | Н  | L  | Dout    | Active            |  |

| Write                    | L  | L  | Х  | DIN     | Active            |  |

| Write Inhibit            | Х  | Н  | Х  | -       | -                 |  |

| Write Inhibit            | Х  | Х  | L  | -       | -                 |  |

| C               | CAPACITANCE <sup>(2)</sup> : $T_A = 25^{\circ}C$ , $F = 1.0MHz$ |      |      |                 |  |  |

|-----------------|-----------------------------------------------------------------|------|------|-----------------|--|--|

| Symbol          | Parameter                                                       | Max. | Unit | Condition       |  |  |

| CADR            | Address Input                                                   | 6    |      |                 |  |  |

| C <sub>CE</sub> | Chip Enable                                                     | 4    |      |                 |  |  |

| CWE             | Write Enable                                                    | 6    | рF   | $V_{IN}^2 = 0V$ |  |  |

| COE             | Output Enable                                                   | 6    |      |                 |  |  |

| CI/O            | Data Input/Output                                               | 4    |      |                 |  |  |

# Note: (2) This Parameter is periodically sampled and not 100% tested

|                                | DC OPERATING CHARACTERISTICS: +25°C |                                                                                                                                                                                                                                                    |      |             |       |  |  |

|--------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-------|--|--|

| Symbol                         | Parameter                           | Test Conditions                                                                                                                                                                                                                                    |      | nits        | Unit  |  |  |

| Syrribol                       | FOIGITIEIEI                         |                                                                                                                                                                                                                                                    | Min. | Max.        | UTIII |  |  |

| I <sub>IN</sub>                | Input Leakage Current               | $V_{IN} = 0V$ to $V_{DD}$                                                                                                                                                                                                                          | -10  | +10         | А     |  |  |

| lout                           | Output Leakage Current              | $V_{I/O} = 0V$ to $V_{DD}$ , $\overline{CE} = V_{IH}$                                                                                                                                                                                              | -10  | +10         | А     |  |  |

| lcc                            | Active Supply Current               | $\label{eq:cell} \begin{array}{l} \overline{\text{CE}} = \overline{\text{OE}} = V_{\text{IL}}, \ \overline{\text{WE}} = V_{\text{IL}}, \ I_{\text{OUT}} = 0 \\ \text{MA Address} \\ \text{Inputs} = .4/2.4 \\ V @ f = 5 \\ \text{MHz} \end{array}$ |      | 35          | mA    |  |  |

| I <sub>SB</sub>                | Standby Current (TTL)               | $\overline{CE} = V_{IH}, \ \overline{OE} = V_{IL}, \ All \ I/O's = Open, \ Other Inputs = V_{IH}$                                                                                                                                                  |      | 2           | mA    |  |  |

| I <sub>BB</sub>                | Back Bais Current                   | $V_{BB} = -3V  10\%$                                                                                                                                                                                                                               |      | 125         | А     |  |  |

| V <sub>IL</sub> <sup>(1)</sup> | Input Low Voltage                   |                                                                                                                                                                                                                                                    | -1   | 0.6         | V     |  |  |

| VIH (1)                        | Input High Voltage                  |                                                                                                                                                                                                                                                    | 2.2  | $V_{DD}$ +1 | V     |  |  |

| V <sub>OL</sub>                | Output Low Voltage                  | $I_{OUT} = 1.0 \text{ mA}$                                                                                                                                                                                                                         |      | 0.5         | V     |  |  |

| VOH                            | Output High Voltage                 | $I_{OUT} = -400$ A                                                                                                                                                                                                                                 | 2.6  |             | V     |  |  |

Notes: (1)  $V_{LL}$  min. and  $V_{H}$  max. are for reference only and are not tested. Unless otherwise stated, measurements are made at +25°C,  $V_{DD}$  = 5.0V.

## TT Semiconductor, Inc.

## TTE128HT8F/G/K/N

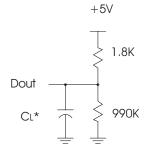

| AC TEST CONDITIONS                          |            |  |  |

|---------------------------------------------|------------|--|--|

| Input Pulse Levels                          | OV to 3.0V |  |  |

| Input Pulse Rise and Fall Times             | 10ns       |  |  |

| Input and Output<br>Timing Reference Levels | 1.5V       |  |  |

|                                                                | OUTPUT LOAD |                                                     |  |  |

|----------------------------------------------------------------|-------------|-----------------------------------------------------|--|--|

| Load                                                           | CL          | Parameters Measured                                 |  |  |

| 1 100pF except tLz1, tLz2, tHz1, tHz2, tOHz, tOLZ,<br>and tWHz |             | except tLz1, tLz2, tHz1, tHz2, tOHz, tOLZ, and tWHz |  |  |

| 2                                                              | 5pF         | tLZ1, tLZ2, tHZ1, tHZ2, tOHZ, tOLZ, and tWHZ        |  |  |

Figure 1. Output Load

\*Including Probe and Jig Capacitance.

| Power-Up Timing                 |                             |     |    |  |  |

|---------------------------------|-----------------------------|-----|----|--|--|

| Symbol Parameter Max. Units     |                             |     |    |  |  |

| t <sub>PUR</sub> <sup>(2)</sup> | Power-Up to Read Operation  | 100 | S  |  |  |

| t <sub>PUW</sub> (2)            | Power-Up to Write Operation | 5   | ms |  |  |

Note: (2) This Parameter is periodically sampled and not 100% tested

| Endurance and Data Retention |        |   |                 |  |  |

|------------------------------|--------|---|-----------------|--|--|

| Parameter Min. Max. Units    |        |   |                 |  |  |

| Endurance                    | 10,000 | - | Cycles per Byte |  |  |

| Data Retention               | 100    | - | Years           |  |  |

## TT Semiconductor, Inc

|     | AC OPERATING CONDITIONS AND CHARACTERISTICS - READ CYCLE: Over operating ranges |                                       |       |      |       |      |        |  |  |  |

|-----|---------------------------------------------------------------------------------|---------------------------------------|-------|------|-------|------|--------|--|--|--|

| No. | Symbol                                                                          | pol Parameter                         | 200ns |      | 250ns |      | - Unit |  |  |  |

|     |                                                                                 |                                       | Min.  | Max. | Min.  | Max. |        |  |  |  |

| 1   | t <sub>RC</sub>                                                                 | Read Cycle Time                       | 200   |      | 250   |      | ns     |  |  |  |

| 2   | t <sub>AA</sub>                                                                 | Address Access Time                   |       | 200  |       | 250  | ns     |  |  |  |

| 3   | t <sub>CE</sub>                                                                 | CE to Output Valid                    |       | 200  |       | 200  | ns     |  |  |  |

| 4   | t <sub>OE</sub>                                                                 | Output Enable to Output Valid         |       | 50   |       | 50   | ns     |  |  |  |

| 5   | † <sub>LZ</sub>                                                                 | CE to Output in LOW-Z                 | 0     |      | 0     |      | ns     |  |  |  |

| 6   | t <sub>OLZ</sub>                                                                | Output Enable to Output in LOW-Z      | 0     |      | 0     |      | ns     |  |  |  |

| 7   | t <sub>HZ</sub>                                                                 | CE to Output in HIGH-Z <sup>4,5</sup> |       | 50   |       | 50   | ns     |  |  |  |

| 8   | t <sub>OHZ</sub>                                                                | Output Enable to Output in HIGH-Z     |       | 50   |       | 50   | ns     |  |  |  |

| 9   | t <sub>OH</sub>                                                                 | Output Hold from Address Change       |       | 0    |       | 0    | ns     |  |  |  |

Note: (3)  $t_{LZ}\,min.,\,t_{HZ},\,T_{OLZ}\,min.$  and  $t_{OHZ}\,$  are periodically sampled and not 100% tested

| WAVEFORM KEY |                                |                                |                                 |  |  |  |  |  |

|--------------|--------------------------------|--------------------------------|---------------------------------|--|--|--|--|--|

|              |                                |                                |                                 |  |  |  |  |  |

| Data Valid   | Travsition from<br>HIGH to LOW | Travsition From<br>HIGH to LOW | Data Undefined or<br>Don't Care |  |  |  |  |  |

|     | AC OPERATING CONDITIONS AND CHARACTERISTICS - WRITE CYCLE <sup>6, 7</sup> : Over operating ranges |                                 |      |      |      |  |  |  |

|-----|---------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|--|--|--|

| No. | Symbol                                                                                            | Parameter                       | Min. | Max. | Unit |  |  |  |

| 13  | t <sub>WC</sub>                                                                                   | Write Cycle Time                |      | 10   | ms   |  |  |  |

| 14  | t <sub>AS</sub>                                                                                   | Address Setup Time              | 20   |      | ns   |  |  |  |

| 15  | t <sub>AH</sub>                                                                                   | Address Hold Time               | 100  |      | ns   |  |  |  |

| 16  | t <sub>CS</sub>                                                                                   | Write Set-Up Time               | 0    |      | ns   |  |  |  |

| 17  | tсн                                                                                               | Write Hold Time                 | 0    |      | ns   |  |  |  |

| 18  | t <sub>CW</sub>                                                                                   | Chip Enable Low Pulse Width     | 200  |      | ns   |  |  |  |

| 18  | toes                                                                                              | Output Enable HIGH Setup Time   | 10   |      | ns   |  |  |  |

| 19  | t <sub>OEH</sub>                                                                                  | Output Enable HIGH Hold Time    | 10   |      | ns   |  |  |  |

| 20  | t <sub>WP</sub>                                                                                   | Write Enable Low Pulse Width    | 200  |      | ns   |  |  |  |

| 21  | t <sub>WPH</sub>                                                                                  | Write Enable High Recovery Time | 200  |      | ns   |  |  |  |

| 22  | t <sub>DV</sub>                                                                                   | Data Valid                      |      | 1    | S    |  |  |  |

| 22  | t <sub>DS</sub>                                                                                   | Data Setup                      | 100  |      | ns   |  |  |  |

| 22  | t <sub>DH</sub>                                                                                   | Data Hold                       | 25   |      | ns   |  |  |  |

| 22  | t <sub>DW</sub>                                                                                   | Delay to Next Write             | 10   |      | S    |  |  |  |

| 22  | t <sub>BLC</sub>                                                                                  | Byte Load Cycle                 | 0.4  |      | S    |  |  |  |

Notes: (4)  $t_{wc}$  is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is

## TT Semiconductor, Inc

## TTE128HT8F/G/K/N

## TT Semiconductor, Inc

## TTE128HT8 F/G/K/N

TT Semiconductor, Inc. 325 North Shepard Street, Anaheim, California 92806 ♦ (714) 257-2257 ♦ FAX: (714) 257-2252 ♦ http://www.ttsemiconductor.com