## Introduction

The EV1201A provides an evaluation and development platform for the AL1201 Digital-to-Analog Converter IC. With the EV1201A, users may evaluate the sonic qualities of the DAC, as well as test the responses of the chip to various configurations and operating conditions.

The EV1201A accepts inputs in the ADAT® Optical format or S/PDIF format.

To assist with engineering design, an area on the board is set aside for additional circuitry the user may want to add, while expansion connectors are provided for system expansion.

# **Table of Contents**

| Introduction                               | 1  |

|--------------------------------------------|----|

| Table of Contents                          | 1  |

| Using the EV1201A                          | 2  |

| Power and Gnd Connections                  | 2  |

| Audio Input Connections                    | 2  |

| Audio Output Connections                   | 2  |

| Audio Input Format Selection               | 2  |

| EV1201A Circuit Layout                     | 3  |

| External Devices                           | 3  |

| ADAT® Optical Devices                      | 3  |

| EV1201A THD+N Vs. Frequency                | 4  |

| EV1201A Frequency Response                 | 4  |

| EV1201A Crosstalk Vs. Frequency            | 5  |

| EV1201A THD+N Vs. Input Level              | 5  |

| Notice and Contact Information             | 6  |

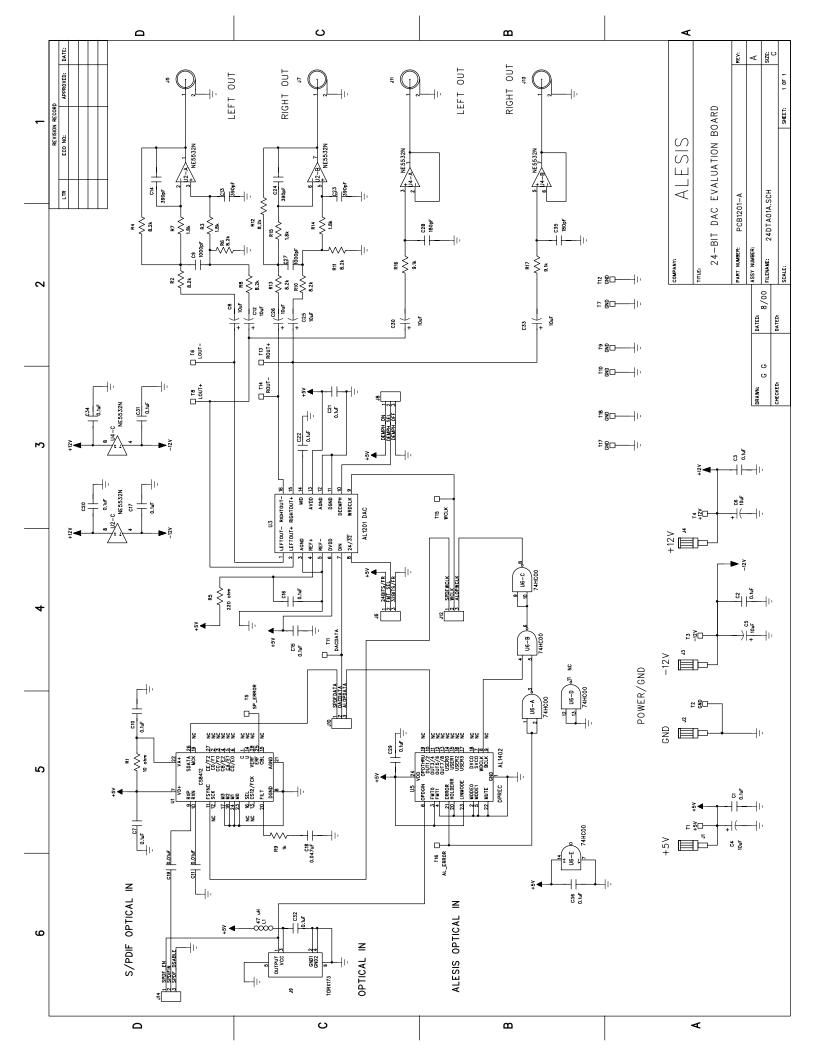

| Evaluation Board Schematic                 | 7  |

| Evaluation Board Top Layer Silkscreen      | 8  |

| Evaluation Board Top Layer Copper Trace    | 9  |

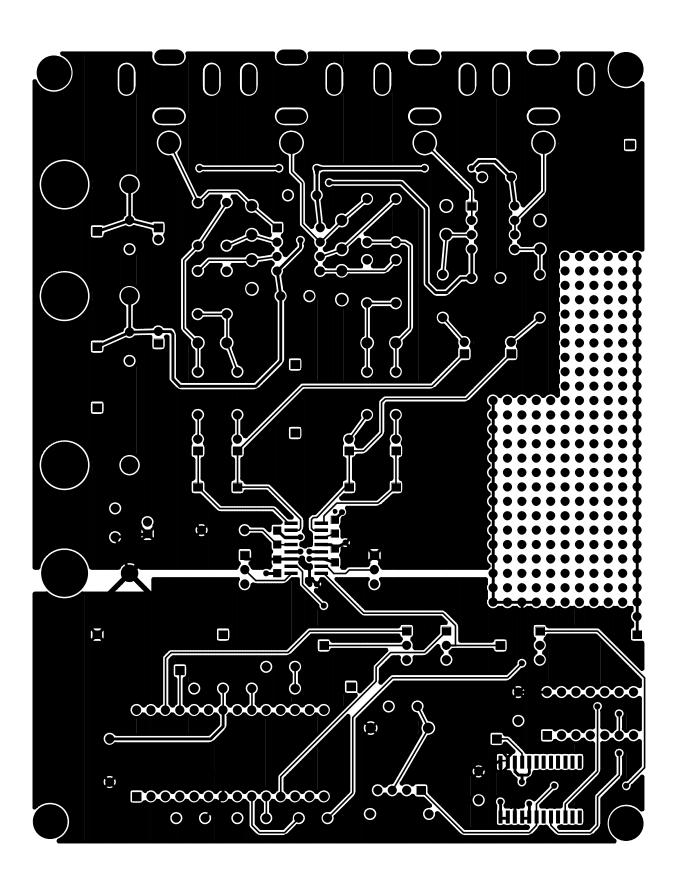

| Evaluation Board Bottom Layer Copper Trace | 10 |

## Using the EV1201A

#### **Power and Gnd Connections**

There are four power/ground inputs to the board. The required voltages are  $V_{DD}$  at connector **J1** (typically +5V, can be monitored at test point **T1**), ground at connector **J2** (can be monitored at **T2**), -V<sub>OPAMP</sub> at connector **J3** (typically -12V to -15V, can be monitored at **T3**), and +V<sub>OPAMP</sub> at connector **J4** (typically +12V to +15V, can be monitored at **T4**).

Test points **T7**, **T9**, **T10**, **T12**, **T17**, and **T18** are Gnd test points and may be used for oscilloscope or other test equipment ground connections. There is only one ground plane on the board (see PCB layout section).

### **Audio Input Connections**

There is one TOSLINK optical digital input at connector **J9**. This input can be set to either ADAT® Optical or S/PDIF via jumpers **J10**, **J12**, and **J15**, as shown on the following table.

| Input         | J10 Setting | J12 Setting | J15 Setting |

|---------------|-------------|-------------|-------------|

| ADAT® Optical | ALOPDATA    | ALOPWCLK    | SPDF_DSABLE |

| S/PDIF        | SPDIFDATA   | SPDIFWCLK   | SPDF_EN     |

The jumpers are oriented such that if all three are on the side closest to the optical connector, then ADAT® Optical has been selected, and if all three are on the side farther away, then S/PDIF has been selected.

In addition, a test point for monitoring the ADAT® Optical error pin is available at **T16**, and a test point for monitoring the S/PDIF error pin is available at **T5**. A high on the error pin in use indicates an error receiving data and the validity of the connection should be checked before proceeding with AL1201 evaluation.

#### **Audio Output Connections**

Test points **T8** and **T6** are the OUTL+ and OUTL- test pins for the AL1201 respectively. Test points **T13** and **T148** are the OUTR+ and OUTR- test pins for the AL1201 respectively. These four test points are the balanced outputs to the AL1201 DAC, and can be used to interface to a balanced output cable if desired.

The Left and Right analog outputs are provided by way of unbalanced BNC jacks – connector **J5** for the Left channel and **J7** for the Right channel. The two-pole filters convert the balanced signals into single-ended signals available at the BNC output. **J11** and **J13** are provided as BNC outputs for any added circuitry that the user may add to the board.

#### **Audio Input Format Selection**

The AL1201 DAC input format may be selected through jumper **J6** for either 32-bits-per-frame or 24-bits-per-frame. The first selection corresponds to a 256X system where the MCLK is 256 times the WDCLK; the second selection corresponds to a 384X system where the MCLK is 384 times the WDCLK. The 32-bits-per-frame mode is more commonly encountered.

The CS8412 S/PDIF receiver (**U1**) and the AL1402 OptoGen ADAT® Optical receiver (**U5**) output data in 32-bits-per-frame mode, so J6 must be set for this mode if the optical input jack is to be used to evaluate the part.

If a 24-bits-per-frame input is desired, then the jumpers on J10 andJ12 must be removed, the input data signal applied to test point **T11**, DACDATA, and the input wordclock signal applied to test point **T15**, WCLK. In addition, a ground connection from the external board needs to be connected to the EV1201A board ground to T7 or T12 (ground pins close to the digital section) and J6 should be set for 24-bits-per-frame.

Jumper **J8** is for either De-emphasis On or De-emphasis Off for the AL1201 DAC. The De-emphasis Off selection is suggested unless reading in data that has had emphasis applied to it.

## **EV1201A Circuit Layout**

The EV1201A uses a two-layer PCB with the ground plane as a continuous copper pour on the bottom of the PCB, a practice we recommend for new designs. A ground plane directly under the chip reduces any EMI emissions emanating from the chip. The PCB traces and components are split into a digital side and an analog side to keep high frequency digital traces away from sensitive analog traces. The AL1201 straddles this border with pins 1-5 and 12-16 on the analog side, and pins 6-11 on the digital side. The EV1201A has a power plane as a continuous copper pour on the top of the PCB. Two +V<sub>DD</sub> planes are used with the PCB, +AV<sub>DD</sub> and +DV<sub>DD</sub>, which are connected together at the one +V<sub>DD</sub> power jack. +V<sub>REF</sub> is derived from the +AV<sub>DD</sub> through a 220 $\Omega$  resistor.

Analog signals of the left channel are kept away from the analog signals of the right channel to avoid crosstalk between the two.

All  $0.1\mu F$  bypass capacitors are placed as close as possible to the pins they are filtering. Surface mount  $0.1\mu F$  ceramic capacitors (type X7R) are used for bypassing, allowing close placement. Bypass pins on the AL1201 are REF+, VA, MID and VD. Electrolytic capacitors (10 $\mu F$ ) are connected to the power lines. The differential-to-single-ended two-pole 48kHz lowpass filter uses film capacitors, 5% tolerance or less. Distortion results will vary if lesser quality capacitors are used. Resistors are 5% throughout.

The AL1402 WCLK can become unstable if a valid input is not presented to it. Through the use of a mute circuit the WCLK to the AL1201 will be muted if an error (non-valid input) is present at the AL1402, accomplished with **U6**. Two blue jumpers near U6 are standard on bottom of board to complete circuit. This is done to match schematic shown with this document.

For information on circuit layout for the Wavefront AL1401A, please see the AL1401A datasheet.

### **External Devices**

#### **ADAT® Optical Devices**

The AL1401A OptoGen provides digital output for the EV1201A board using the industry-standard ADAT® Optical protocol. This device is capable of transporting up to 8 channels (four stereo pairs) of digital audio over a single optical fiber at a 48kHz sample rate.

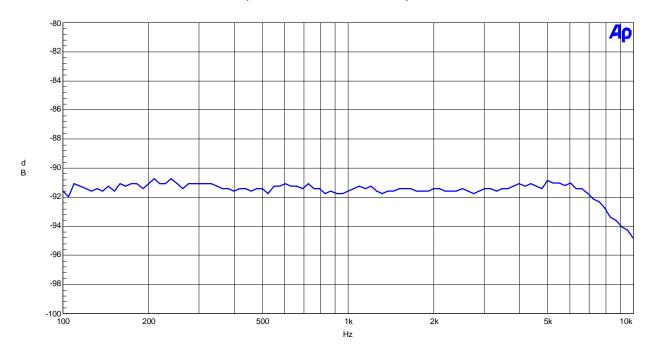

### EV1201 THD+N(REL TO FULL SCALE INPUT) VS FREQUENCY

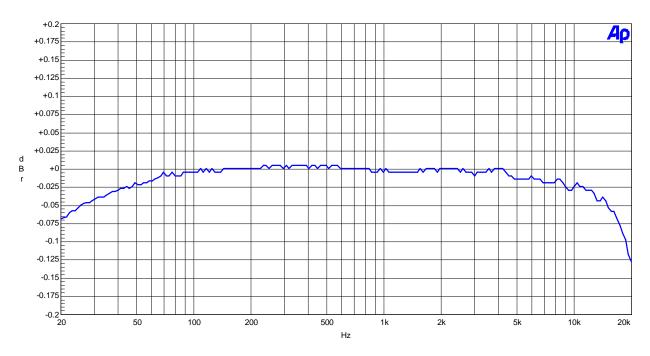

#### EV1201 FREQUENCY RESPONSE WITH FULL SCALE INPUT

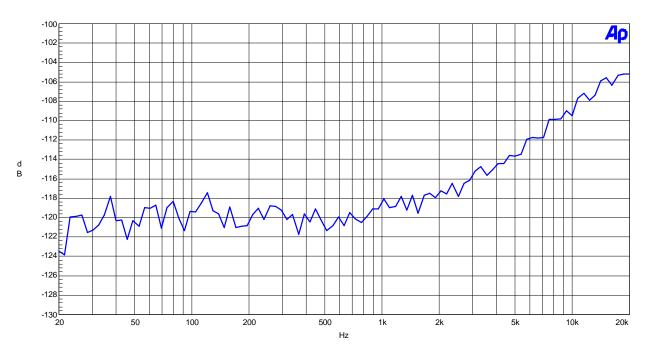

### **EV1201 XTALK VS FREQ**

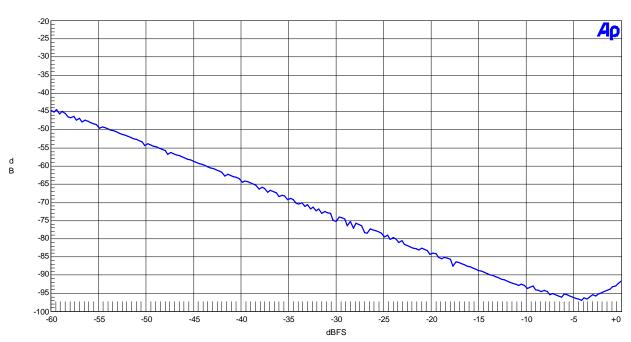

# EV1201 THD+N(REL TO OUTPUT) VS INPUT LEVEL

Walluation

EV1201/

#### NOTICE

Wavefront Semiconductor reserves the right to make changes to their products or to discontinue any product or service without notice. All products are sold subject to terms and conditions of sale supplied at the time of order acknowledgement. Wavefront Semiconductor assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Information contained herein is only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, no responsibility is assumed for inaccuracies.

Wavefront Semiconductor products are not designed for use in applications which involve potential risks of death, personal injury, or severe property or environmental damage or life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness.

All trademarks and registered trademarks are property of their respective owners.

#### **Contact Information:**

Wavefront Semiconductor 200 Scenic View Drive Cumberland, RI 02864 U.S.A. Tel: +1 401 658-3670 Fax: +1 401 658-3680

On the web at www.wavefrontsemi.com Email: info@wavefrontsemi.com

Copyright © 2005 Wavefront Semiconductor

Application note revised March, 2005

Reproduction, in part or in whole, without the prior written consent of Wavefront Semiconductor is prohibited.

ALESIS-SEMI EV1201-A "TOPSILK" LAYER

ALESIS-SEMI EV1201-A "TOPTRACE" LAYER