# Key Design Features

- Synthesizable, technology independent IP Core for FPGA and ASIC

- Supplied as human readable VHDL (or Verilog) source code

- Separate Encoder/Decoder pair that implements the standard IBM® 8b/10b line code for a DC-balanced serial data stream

- Fully synchronous design with data input and output valid flags

- Encoder and Decoder have a latency of 1 clock cycle

- Generic parallel input and output data widths (specified in whole numbers of input and output bytes)

- Supports all standard control bytes K.28.0 to K.30.7

- Error flags indicate control byte errors and general decoding errors

- Running disparity calculations handled internally

- Fully scalable architecture

- Suitable for use in serial data links of 6 GHz+ on basic FPGA devices¹

# **Applications**

- High speed serial interfaces with embedded clocking

- Transmission of DC-balanced, AC-coupled serial data

- Prerequisite for the transmission of serial data over large distances

- Ideal for use in serial links such as LVDS, sub-LVDS, mini-LVDS etc. over cheap twisted pair cable

- Encoding scheme used in a wide range of communication standards such as Ethernet, PCI Express, DVB-ASI etc.

#### Generic Parameters

| Generic name | Description                                        | Туре    | Valid range |

|--------------|----------------------------------------------------|---------|-------------|

| nb (encoder) | Number of bytes to encode in parallel              | integer | ≥ 1         |

| nw (decoder) | Number of 10-bit<br>words to decode in<br>parallel | integer | ≥ 1         |

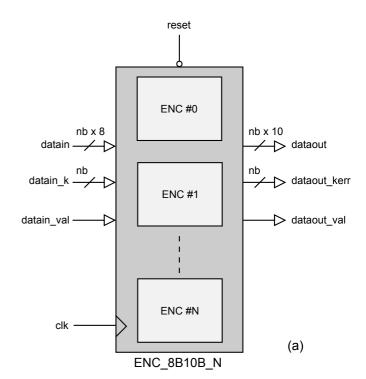

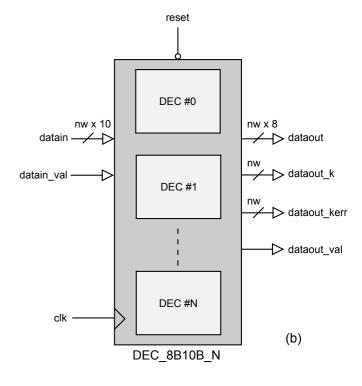

# **Block Diagram**

Figure 1: Simplified architectures for the (a) 8b/10b Encoder and (b) 8b/10b Decoder modules

Xilinx® Artix-7 used as a reference

### Pin-out Description

#### 8B10B ENCODER

| Pin name                   | I/O | Description                                                                         | Active state |

|----------------------------|-----|-------------------------------------------------------------------------------------|--------------|

| clk                        | in  | System clock<br>(Synchronous with parallel<br>input data)                           | rising edge  |

| reset                      | in  | Asynchronous reset                                                                  | low          |

| datain<br>[nb * 8 - 1:0]   | in  | N x input data bytes                                                                | data         |

| datain_k<br>[nb - 1:0]     | in  | N x control byte enables<br>(Indicates that byte is a<br>control symbol)            | high         |

| datain_val                 | in  | Input data valid                                                                    | high         |

| dataout<br>[nb * 10 - 1:0] | out | N x 10-bit output data words                                                        | data         |

| dataout_kerr<br>[nb - 1:0] | out | N x control byte error flags<br>(Indicates an unrecognised<br>control symbol input) | high         |

| dataout_val                | out | Output data valid                                                                   | high         |

#### 8B10B DECODER

| Pin name                   | <i>I/</i> O | Description                                                                    | Active state |

|----------------------------|-------------|--------------------------------------------------------------------------------|--------------|

| clk                        | in          | System clock<br>(Synchronous with parallel<br>input data)                      | rising edge  |

| reset                      | in          | Asynchronous reset                                                             | low          |

| datain<br>[nw * 10 - 1:0]  | in          | N x 10-bit input data words                                                    | data         |

| datain_val                 | in          | Input data valid                                                               | high         |

| dataout<br>[nw * 8 - 1:0]  | out         | N x output data bytes                                                          | data         |

| dataout_k<br>[nw -1:0]     | out         | N x control byte flags<br>(Indicates that byte is a<br>control symbol)         | high         |

| dataout_kerr<br>[nw - 1:0] | out         | N x decoding error flags<br>(Indicates an error in the<br>decoded output byte) | high         |

| dataout_val                | out         | Output data valid                                                              | high         |

# **General Description**

The CODEC\_8B10B IP Core is a scalable 8B/10B Encoder/Decoder pair suitable for a wide range of serial data transmission applications. The design is optimized for very high-speed operation and is suitable for use in serial data links of 6 GHz+ on basic FPGA devices.

The design is comprised of an independent encoder and decoder module (Figure 1) that may be used separately or together as a combined CODEC unit.

The architecture is fully scalable allowing any number of bytes or words to be encoded or decoded in parallel. The number of bytes and words are specified by the *nb* and *nw* generic parameters.

The encoder and decoder feature a simple synchronous user interface. Data inputs and flags are sampled on the rising-edge of *clk* when the *datain\_val* signal is active high. Likewise, data outputs and flags are valid on the rising-edge of *clk* when *dataout\_val* is active high.

As well as regular 8-bit data, the encoder can accept one of the special control characters or symbols. These symbols are labelled K.28.0 to K.30.7 and, by convention, are used to insert 'commas' and control characters in a transmitted bitstream. The table below shows the standard symbols supported:

| Input  | HGFEDCBA | Current RD -ve<br>abcdeifghj | Current RD +ve<br>abcdeifghj |

|--------|----------|------------------------------|------------------------------|

| K.28.0 | 00011100 | 0011110100                   | 1100001011                   |

| K.28.1 | 00111100 | 0011111001                   | 1100000110                   |

| K.28.2 | 01011100 | 0011110101                   | 1100001010                   |

| K.28.3 | 01111100 | 0011110011                   | 1100001100                   |

| K.28.4 | 10011100 | 0011110010                   | 1100001101                   |

| K.28.5 | 10111100 | 0011111010                   | 1100000101                   |

| K.28.6 | 11011100 | 0011110110                   | 1100001001                   |

| K.28.7 | 11111100 | 0011111000                   | 1100000111                   |

| K.23.7 | 11110111 | 1110101000                   | 0001010111                   |

| K.27.7 | 11111011 | 1101101000                   | 0010010111                   |

| K.29.7 | 11111101 | 1011101000                   | 0100010111                   |

| K.30.7 | 11111110 | 0111101000                   | 1000010111                   |

In order to specify that the data input to the encoder is a control symbol then the signal  $datain\_k$  should be set appropriately. Setting this bit high in the respective byte position will make the encoder interpret the input as a control symbol. If the control symbol is not recognized then the encoder will assert the  $dataout\_kerr$  signal with the respective output data.

The decoder has a reciprocal operation to the encoder and decodes the N x 10-bit data back to the original N x bytes. If the decoder detects a decoding error in the stream then the  $dataout\_kerr$  flag will be asserted high for the respective byte.

All Running Disparity (RD) calculations are handled internally in the encoder core. Resetting the encoder will initialize the current running disparity to zero by default.

Both the encoder and decoder have a latency of 1 clock cycle from input valid to output valid.

#### **Functional Timing**

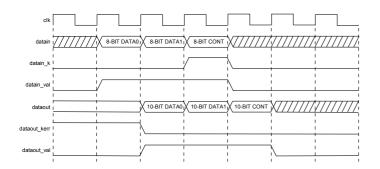

Figure 2 below shows an example series of three consecutive bytes being encoded. The third byte in the sequence is specified as a control symbol by asserting the *datain\_k* flag high.

Inputs are sampled on the rising edge of *clk* when *datain\_val* is high. Inputs are ignored otherwise. The encoder has a latency of 1 clock cycle from input to output.

Figure 2: Example 8b/10b encoder timing waveform for a sequence of bytes

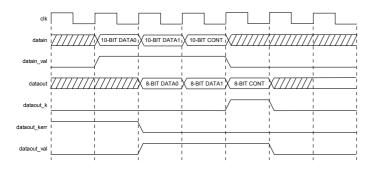

A similar waveform is shown in Figure 3 for the decoding process. Again the third word in the sequence is identified as a control symbol with the *dataout\_k* flag asserted high. The latency is 1 clock cycle.

Figure 3: Example 8b/10b decoder timing waveform for a sequence of 10-bit words

## Source File Description

All source files are provided as text files coded in VHDL. Equivalent Verilog versions of the code may be provided on request.

| Source file           | Description                         |

|-----------------------|-------------------------------------|

| enc_8b10b_lut.vhd     | 8b/10b encoding table               |

| enc_8b10b_code.vhd    | 8b/10b encoding table (symbols)     |

| enc_8b10b.vhd         | Core encoder component              |

| enc_8b10b_n.vhd       | Top-level encoder component         |

| dec_8b10b_code.vhd    | 8b/10b decoding table               |

| dec_8b10b_lut.vhd     | 8b/10b decoding table (symbols)     |

| dec_8b10b.vhd         | Core decoder component              |

| dec_8b10b_n.vhd       | Top-level decoder component         |

| codec_8b10b_bench.vhd | Top-level encoder/decoder testbench |

## Functional Testing

An example testbench is provided for use in a suitable VHDL simulator. The compilation order of the source code is as follows:

- 1. enc\_8b10b\_lut.vhd

- 2. enc 8b10b code.vhd

- 3. enc\_8b10b.vhd

- 4. enc\_8b10b\_n.vhd

- 5. dec 8b10b code.vhd

- 6. dec\_8b10b\_lut.vhd

- 7. dec\_8b10b.vhd

- 8. dec\_8b10b\_n.vhd

- 9. codec\_8b10b\_bench.vhd

The testbench instantiates the encoder and decoder IP Core components in series such that a sequence of random 32-bit words are encoded into a a sequence of 40-bit words and vice-versa.

The generic parameters *nb* and *nw* have been set to 4 to correspond to 4 bytes/words in parallel. The user is free to modify the input and output data widths as required.

The simulation must be run for at least 2 ms during which time the encoder is fed a random sequence of 32-bit data and control symbols. Two output text files are generated during the course of the simulation. These files are 'data\_in.txt' and 'data\_out.txt' and contain a list of data words captured at the inputs and outputs of the encoder and decoder components. The equivalence of these files proves the correct operation of the test.

#### Synthesis and Implementation

The files required for synthesis and the design hierarchy is shown below:

- enc\_8b10b\_n.vhd

- O enc\_8b10b.vhd

- enc\_8b10b\_lut.vhd

- enc\_8b10b\_code.vhd

- dec\_8b10b\_n.vhd

- O dec\_8b10b.vhd

- dec\_8b10b\_lut.vhd

- dec\_8b10b\_code.vhd

The VHDL core is designed to be technology independent. However, as a benchmark, synthesis results have been provided for the Xilinx® 7-series FPGA devices. Synthesis results for other FPGAs and technologies can be provided on request.

There are no special constraints required for synthesis although reducing the number of parallel encoders and/or decoders in the design will obviously impact the total resource use. The IP core is completely technology independent.

Trial synthesis results are shown with the generic parameters nb = 4 and nw = 4. The resource usage is specified after place and route of the design.

ENC\_8B10B\_N

| Resource type        | Artix-7 | Kintex-7 | Virtex-7 |

|----------------------|---------|----------|----------|

| Slice Register       | 46      | 46       | 46       |

| Slice LUTs           | 278     | 281      | 281      |

| Block RAM            | 0       | 0        | 0        |

| DSP48                | 0       | 0        | 0        |

| Occupied Slices      | 107     | 113      | 107      |

| Clock freq. (approx) | 600 MHz | 700 MHz  | 800 MHz  |

# DEC\_8B10B\_N

| Resource type        | Artix-7 | Kintex-7 | Virtex-7 |

|----------------------|---------|----------|----------|

| Slice Register       | 41      | 41       | 41       |

| Slice LUTs           | 1155    | 1158     | 1158     |

| Block RAM            | 0       | 0        | 0        |

| DSP48                | 0       | 0        | 0        |

| Occupied Slices      | 496     | 324      | 498      |

| Clock freq. (approx) | 600 MHz | 700 MHz  | 800 MHz  |

# Revision History

| Revision | Change description                                     | Date       |

|----------|--------------------------------------------------------|------------|

| 1.0      | Initial revision                                       | 01/12/2014 |

| 1.1      | Updated synthesis results for Xilinx® 7 series devices | 18/03/2015 |

|          |                                                        |            |

|          |                                                        |            |

|          |                                                        |            |