#### [1] General

The  $C^2MOS$  voice synthesizing LSI systems T6721A, T6772 and T6684 are the easy-to-control voice synthesizing LOW POWER LSI systems with the following features.

T6721A C2MOS Voice Synthesizing LSI

T6772 C2MOS Mask ROM dedicated for Voice Data (64K bit)

T6684 C2MOS Mask ROM dedicated for Voice Data (128K bit)

- (1) The voce synthesizing system is of PARCOR type\*. 8 kHz sampling voice output.

- (2)  $C^2MOS + 5V$  single power supply with low power consumption. (T6721A 2.5mW TYP, T6772 0.2mW TYP, T6684 0.3mW TYP.)

- (3) Easy connection to a microcomputer. 12 kinds of command write, 4 kinds of synthesizing system status read, voice data ROM data read, and genration of BUSY signal and END OF SPEECH signal are possible.

- (4) It is possible to make power down of the entire synthesizing system and to output signals for power down of the externally mounted audio circuit by means of commands from a microcomputer. The latter only is also possible.

- (5) The manual use without a microcomputer connected is also possible. In this case, the sequential speech for every phrase (HALT/START) or ENDLESS LOOP speech is possible.

- (6) Synthesizing conditions can be selected and speed of speech is changeable. (bit rate: 2.4, 4.8 and 9.6 kbps; sound source: 2; number of filter stages: 8 or 10; speed of speech: 10 stages)

- (7) It is possible to store data other than voice data in the voice data ROM and use them by CPU.

- (8) Max. capacity of voice data is 8M bit Max. at time of Mask ROM.

- (9) The ceramic oscillator used for oscillation provides stable speech.

- (10) The built-in voltage type DA converter (9 bits) improves accuracy of voice output.

- \* PARCOR is the voice analyzing and synthesizing method developed by Nippon Telegraph and Telephone Public Corporation, and our voice synthesizing LSIs have been developed under the guidance of Nippon Telegraph and Telephone Public Corporation.

#### [2] Configuration of Voice Synthesizing System LSI

When a voice synthesizing system is composed using the voice synthesizing LSI systems.

T6721A

Voice Synthesizing LSI

T6772, T6684

Dedicated Mask ROM

there are tow types of configuration: CPU control type by means of a microcomputer and other CPU and manual control type using no CPU.

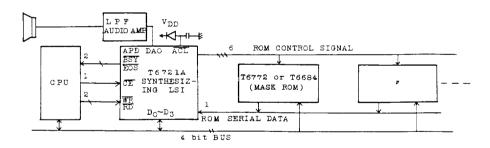

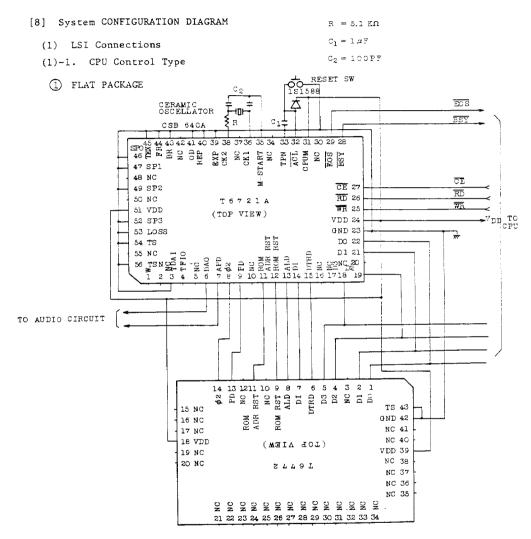

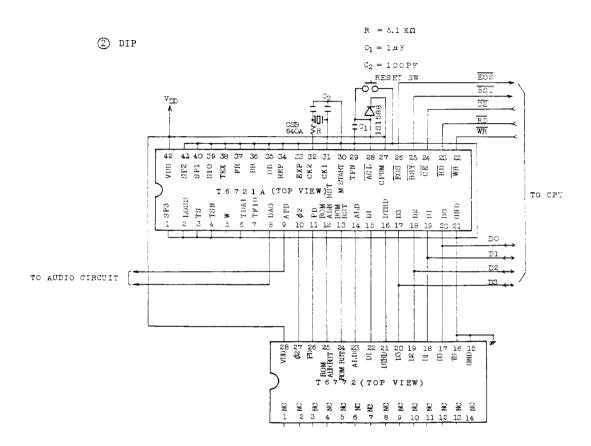

#### (1) CPU control type

The basic configuration of the system of this type is the 3 chip configuration composed of CPU, T6721A and (a) dedicated mask ROM (s). If ROM capacity is insufficient, multiple ROMs can be parallelly connected. (Refer to P29.)

DAO : DA Converter Output APD : Audio Power Down

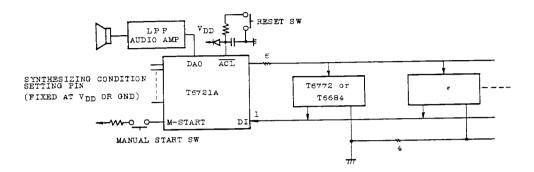

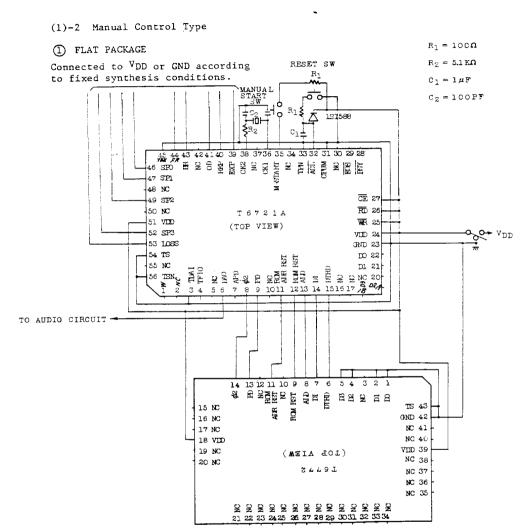

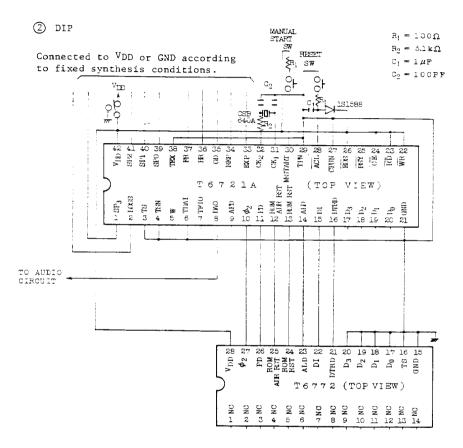

#### (2) Manual control type

As T6721A LSI has a built-in voltage type DA converter, it is necessary to externally provide LPF (low-pass filter) and AUDIO AMP as shown in the above diagram.

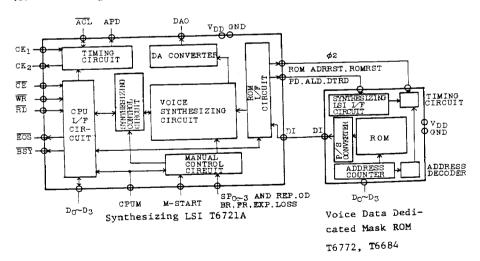

## (3) Block diagram of each LSI

# TOSHIBA INTEGRATED CIRCUIT

[3] Specifications for Voice Synthesizing Section

(1) Operation unit

Type PARCOR type

No. of operation bits 15 bits

No. of digital filter stages 8 and 10 states are selectable

Clock frequency 160 kHz Sampling frequency 8 kHz

Loss effect in digital Available and non-available are

filter selectable

Interpolating calculation Available

(2) Others

Sound source One of 2 voice sources is selectable.

Unvoice source : white noise

Non-linear conversion Available for 48 bits/frame

Total speech time Systematically, possible to expand the voice

ROM capacity up to 8 M bits. In the case of 2.4 kbps, the total speech time is about 1  $\,$

hour.

Repeat bit Available and non-available are selectable.

(3) Changeability of synthesizing conditions and speech length

Selection shown in the following table is possible for 6 synthesizing

conditions. This selection, however, is made at time of voice analysis

and selected conditions are set through the dedicated PINs when the

manual control mode is used or by the CPU when the CPU is used.

| Type of source   | Loss<br>effect | Bit/<br>frame | Frame<br>length | Repeat    | Number of filter stages |  |

|------------------|----------------|---------------|-----------------|-----------|-------------------------|--|

| Pitch            | None           | 48            | 20mS            | Available | 10                      |  |

| Triangle<br>wave | Available      | 96            | 10mS            | None      | 8                       |  |

Selection of magnifications shown in the following table is possible for speech length assuming that length of original sound is  $\kappa$  1.0.

| CODE (HEX) | 1    | 2    | 3    | 4    | 5    | 6            | 7    | 8    | 9    | A     |

|------------|------|------|------|------|------|--------------|------|------|------|-------|

| (*)        | x0.7 | x0.8 | x0.9 | x1.0 | x1.1 | <b>x</b> 1.2 | x1.3 | x1.4 | x1.5 | x1.55 |

# (\*): Magnification of speech length

This selection can be made by a command from CPU or through the decicated PIN when the manual control system is used. Differing from the above selection of synthesizing conditions, however, this selection is independent of the voice analysis.

#### [4] Operation under CPU Control

Any control concerning synthesizing operation itself of the synthesizing system is not required for CPU. Controls required for CPU are (1) instruction for speech start and stop, (2) assignment of phrases to be spoken, and (3) others.

Flows of control signals and data between CPU and the voice synthesizing system may be classified into the follow 4 flows. Further, CPU M PIN of T6721A must be connected to  $V_{\rm DD}$  when the CPU control.

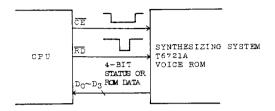

#### (1) General

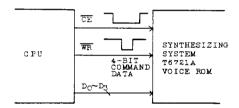

① Write operation from CPU to voice synthesizer system

The synthesizing system is selected by  $\overline{\text{CE}}$  and a 4 bit code on  $\text{D}0^{\circ}$  D<sub>3</sub> is written by  $\overline{\text{WR}}$ . This 4 bit code coresponds to 12 types of commands which specify operation of the synthesizing system, and to parameter data for incidental synthesizing conditions and speech length or to the start address data specifying the phrases in the voice ROM.

② Read operation from voice synthesizing system to CPU

The synthesizing system is selected by  $\overline{\text{CE}}$  and a 4 bit data is read on  $D_0 \sim D_3$  from the synthesizing system by  $\overline{\text{RD}}$ . Content of this 4 bit data is 4 types of internal status of the synthesizing system or data in the voice ROM.

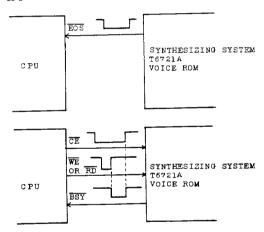

③ EOS (END OF SPEECH) and BSY (BUSY) signals from voice synthesizing system to CPU

$\overline{\text{EOS}}$  is the signal that is generated from the synthesizing system for about 20ms when the speech ended to inform CPU of the end of speech.  $\overline{\text{BSY}}$  is generated for a period during which control by CPU is undesirable for the synthesizing system. That is, this is the period of data transfer in T6721A during power on Auto Clear or immediately after  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  are accepted.

However, no output is provided as long as  $\overline{\text{CE}}$  is at "H" as output is resulted from AND with  $\overline{\text{CE}}$  in T6721A. (Refer to Page 23)

Generation of code data showing end of selected pharase from voice ROM to T6721A.

The synthesizing system stops speech by this END code (END 1) and generates the above-mentioned  $\overleftarrow{EOS}$ . When the synthesizing system is forced to stop speech by STOP command or power down command.  $\overleftarrow{EOS}$  is not generated.

END ① code is added at time of voice analysis and ROM data preparation.

- (2) Types of commands and operation of the synthesizing system

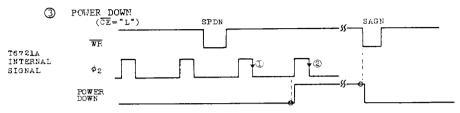

- SPDN (SYSTEM POWER DOWN)

- o Stops oscillation of T6721A and reduces power to the entire synthesizing system.

- o Places AUTIO POWER DOWN OUTPUT APD at "H" level.

- o Places ACL at "L" level and fixes the synthesizing system at the reset status. (Synthesizing conditions and speech length are also cleared, accordingly and reset is required when power is ON.)

- (2) SAGN (SYSTEM ASGIN)

- o Releases SYSTEM POWER DOWN status.

- o After the release, there is the power on transient status for about average 30ms. BSY is generated during this transient status.

- o APD is kept at "H" level. Therefore, prior to starting speech, it is necessary to make AAGN shown below.

- o It is necessary to take a time of more than 30ms before SAGN is made after SPDN.

# TOSHIBA INTEGRATED CIRCUIT

- 3 APDN (AUDIO POWER DOWN)

- o Places AUDIO POWER DOWN OUTPUT APD at "H" level.

- (4) AAGN (AUDIO ASGIN)

- o Places APD at "L" level.

- \* APDN and AAGN are available during speech, so suited to the speaker ON/OFF key (SW) by use of the touch key provided to CPU.

- SPLD (SPEED LOAD)

- o Speed of speech (slow, fast) is set by this command and I nibble (4 bits) data that successively writes.

- 6 CNDT(CONDITION (1))

- o Type of sound source and availability of loss effect calculation are set by this command and succeeding 1 nibble data.

- (CONDITION (2)

- o Similar to CNDT 1, this command sets bit/frame, frame length, availability of repeat and number of filter states.

- \* Parameters that are set in  $\bigcirc$ ,  $\bigcirc$  and  $\bigcirc$ , above, are kept till they are reset or cleared by SPDN.

- ADLD (ADDRESS LOAD)

- o The start address of the voice data ROM corresponding to the phrase to be spoken or to the data in the voice data ROM to be read is set by this command and succeeding 5 nibbles (20 bits) data.

- (9) RRDM (ROM READ MODE)

- o This is a command for setting a mode to read data in the voice data ROM. Under the normal mode other than this mode, the status is read by  $\overline{\text{RD}}$ .

- o This mode is released when another command is written.

- o The low order 4 bits of 8 bits of ROM data coresponding to the ROM address that have been set by ADLD in 8 are taken into T6721A by this command. These 4 bits are output to the bus lines  $D_0 \sim D_3$  by next RD and at the same time, the high order 4 bits are taken into T6721A. Address is advanced in order by the succeeding read and data is read every 4 bits.

- o This function makes it possible to take other data than voice analysis data into the voice data ROM and use it (particularly effective for phrase start address labelling that is described later).

### (O) STRT (START)

- o This command starts the speech.

- o Releases the status "ROM DATA ERROR".

## (STOP (STOP)

- o This command forces the speech to stop and resets the synthesizing system.

- Synthesizing conditions, speech length and APD status are held by this command.

#### NOP (NO OPERATION)

o No OPERATION. ROM READ MODE is, however, released by this command.

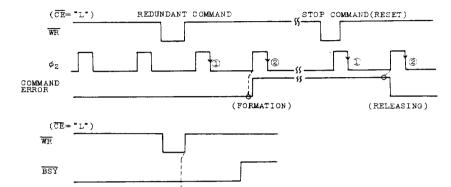

#### (13) Redundant Command

o 4 types of redundant codes are available. Although there is no effect even when these redundant codes are read, the status "COMMAND ERROR" becomes "H" level.

# LIST OF COMMANDS, RD

|              | Name, code<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | BSY generat-<br>ing length (Tø<br>=6.25µs TYP) | Cautions fo                                                                                          |                                         |                  |                    |   | Operation                                                                                                       |                                                             |

|--------------|---------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|--------------------|---|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|              | SPDN<br>1001                                                              | 4 Tø<br>MAX.                                   |                                                                                                      |                                         |                  | ="1,")             |   | Power down of the en-<br>tire synthesizing system<br>Reset                                                      | READ MODE<br>he mode<br>AD MODE.                            |

|              | SAGN<br>1011                                                              | 11                                             | APD remains at "H" level                                                                             |                                         |                  | d (BSY=            | 0 | Release of power cown                                                                                           | eases ROM READ MOI<br>changes the mode<br>STATUS READ MODE. |

|              | APDN<br>1010                                                              | "                                              |                                                                                                      |                                         |                  | ate                | 0 | Brings APD to "H" level                                                                                         | Releases<br>and chang<br>to STATUS                          |

|              | AAGN<br>0100                                                              | ,,                                             |                                                                                                      |                                         |                  | being gener        | 0 | Brings APD to "L" level                                                                                         | Rele<br>and<br>to S                                         |

| struction    | RRDM<br>1000<br>Note 1                                                    | 11 T¢<br>MAX.                                  | ROM start ad-<br>ress must<br>have been set                                                          | performed<br>ech                        | DOWN             | is.                | 0 | Sets ROM READ MODE                                                                                              |                                                             |

| 1 Nibble Ins | STRT<br>0001                                                              | 4 Tø<br>MAX.                                   | ROM start ad-<br>ress must<br>have been set.<br>Synthesizing<br>conditions<br>must have been<br>set. | Should not be perf<br>during the speech | 11d during POWER | performed when BSY | 1 | Starts the speech  If the succeeding RCM data is not at "H" level for 1 frame, status ROM DATA Err is released. | MODE and changes<br>US READ MODE.                           |

|              | STOP<br>0010                                                              | 11                                             |                                                                                                      | <u> </u>                                | Invalid          | not be p           | 0 | Speech stop and reset<br>(synthesizing condi-<br>tions and APD are held)                                        | ROM READ MC<br>to STATUS                                    |

|              | N O P<br>0000                                                             | "1                                             |                                                                                                      |                                         |                  | Should             | 0 | NO OPERATION                                                                                                    | Release<br>the mode                                         |

|              | REDUNDANT<br>COMMAND                                                      | 11                                             |                                                                                                      |                                         |                  | s                  | 0 | Status COMMAND Err be-<br>comes 1.                                                                              | Reth                                                        |

\*: (BSY="L")

|                      | Name, code $D_3 D_2 D_1 D_0$                                                                                                                                                                                                                                                                                                               | BSY generat-<br>ing length (Tø<br>=6.25µs TYP) | Cautior<br>gene                                | ns fo                               |              |                   |   | Operation                          |                             |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|-------------------------------------|--------------|-------------------|---|------------------------------------|-----------------------------|

| ction                | SPLD<br>0101<br>XXXX                                                                                                                                                                                                                                                                                                                       | 4 T¢<br>MAX.<br>"                              |                                                | speech                              |              | being             | 0 | Sets speech length (speed)         | 9 č                         |

| le Instruction       | CNDT ①<br>0110<br>XX00                                                                                                                                                                                                                                                                                                                     | 11                                             | D <sub>0</sub> ,D <sub>1</sub> must<br>be "0". | ring the s                          | DOWN         | BSY 1s            | 0 | Sets synthesizing conditions ①     | DE and change<br>READ MODE. |

| 2 Mbble              | CNDT ② 0111 XXXX                                                                                                                                                                                                                                                                                                                           | ti<br>H                                        |                                                | rformed du                          | during POWER | performed when    | 0 | Sets synthesizing conditions ②     | READ MO<br>STATUS           |

| 6 Nibble Instruction | A D L D 0 0 1 1 X <sub>1</sub> X <sub>1</sub> X <sub>1</sub> X <sub>1</sub> X <sub>2</sub> X <sub>2</sub> X <sub>2</sub> Y <sub>2</sub> X <sub>3</sub> X <sub>3</sub> X <sub>3</sub> X <sub>3</sub> X <sub>4</sub> X <sub>4</sub> X <sub>4</sub> X <sub>4</sub> X <sub>4</sub> X <sub>5</sub> X <sub>5</sub> X <sub>5</sub> X <sub>5</sub> | 11<br>11<br>11<br>11                           | Data of<br>all 20<br>bits must<br>be set.      | Should not be per (status EOS = 0). | Invalid du   | Should not be per | 0 | Sets ROM start address<br>20 bits. | Release ROM<br>the mode to  |

|    | BSY generating length (Tø = 6.25µs TYP)          | Cautions for generating                                                   | Operations other than principal operations                                    |

|----|--------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| RD | Status read  4 Tø MAX. ROM Data read  11 Tø MAX. | Should not be per-<br>formed when BSY is be-<br>ing generated.<br>Note 1. | o Status or ROM data<br>read:<br>o Release of 2 nibble<br>and 6 nibble modes. |

Note 1. 120 $\mu$ s TYP, is required for a period from setting of ROM address by 6 nibble instruction to RRDM or STRT command write. Similarly, 120 $\mu$ s TYP, is also required for a period from RRDM to  $\overline{\text{RD}}$  and succeeding each  $\overline{\text{RD}}$ .

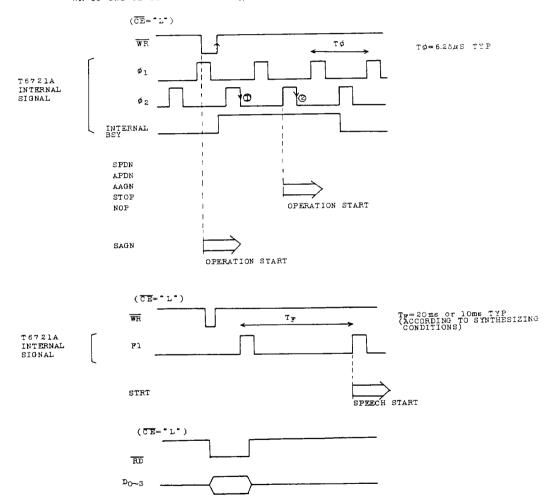

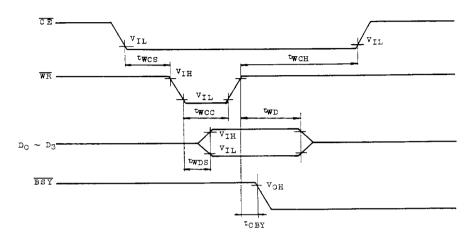

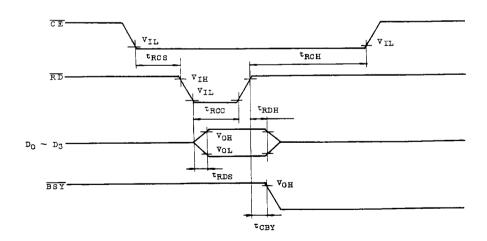

The timing that the operation of each command starts after each WR is in some point of time in a period from the edge of  $\overline{\text{WR}}$  to end of ESY. The timing chart is shown below.

(3) Setting of parameters for synthesizing conditions and speech length Parameters for synthesizing conditions will be determined separately upon consultation with customers at the initial stage of the development on the basis of their requirements for speech quality, ROM capacity, etc. These parameters are set by the above-mentioned commands CNDT 1, CNDT 2 and SPLD and the succeeding 1 nibble data on the bus lines  $D_0 \sim D_3$ . These parameters must have been properly set prior to the speech and also, must not be reset during the speech.

Synthesizing Conditions and Bus Line Data

| Bus (Line      | Condi-<br>tion | Synthesizing conditions ①  CNDT ① | Synthesizing conditions ②  CNDT ② |

|----------------|----------------|-----------------------------------|-----------------------------------|

| Data           |                |                                   | CLIDI (2)                         |

| D3             | 0              | Sound source shape pitch          | 48 bits/frame                     |

|                | 1              | Sound source shape triangle wave  | 96 bits/frame                     |

| D <sub>2</sub> | 0              | Loss effect<br>calculation None   | 20 ms/frame                       |

|                | 1              | " Available                       | 10 ms/frame                       |

| Dl             | О              | Muse be seen as 0                 | Repeat avail-<br>able             |

|                | 1              | Must be set at 0                  | Repeat None                       |

| D <sub>O</sub> | 0              | Must be set at 0                  | Filter 10 stages                  |

|                | 1              | and the set at t                  | Filter 8 stages                   |

Magnification of Speech Length and Bus Line Data Bus line data 1 2 3 5 7 9 A Magnification of x0.7 8.0xx0.9 x1.0 x1.1x1.2x1.3 x1.4 x1.5 x1.55 speech length

When the redundant codes O, E, C, D, E and F are set, the magnification becomes x1.0.

# TOSHIBA INTEGRATED CIRCUIT

Voice synthesizing bit rate is selected through the combination of  $D_3$  and  $D_2$  of the synthesizing conditions ② in the above table.

2.4 kbps 48 bits/frame and 20 ms/frame 4.8 kbps 48 bits/frame and 10 ms/frame 9.6 kbps 96 bits/frame and 10 ms/frame

# (4) Symthesizing system status output (status)

Unless the system has been placed in POM READ MODE by Coomand RRDM, when the read is performed from CPU, a 4 bit status is read out and the status of the synthesizing system can be known. To release this mode, execute commands (NOP, etc.) other than RRDM. Names of status and corresponding bus lines, and conditions for formation and releasing are shown in the following table.

| Correspond-<br>ing bus line | Status<br>name            | Conditions for formation ("H")                                                                                                                                                                                       | Conditions for releasing                                             |

|-----------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| D <sub>3</sub>              | COMMAND<br>ERROR          | <ul> <li>(1) When a redundant command is written.</li> <li>(2) When write/read is made during BSY is being generated.</li> </ul>                                                                                     | STOP<br>When POWER ON<br>CLEAR.<br>During POWER<br>DOWN              |

| D <sub>2</sub>              | ROM DATA                  | When the speech has started and all voice data in the first frame are at "H" level. That is, when ROM CHIP that did not exist has been selected or when it has started from address in which any data did not exist. | Same as above, and when normal data has been obtained by next start. |

| DI                          | POWER<br>DOWN             | When the synthesizing system is in POWER DOWN status.                                                                                                                                                                | At time of POWER ON.                                                 |

| D <sub>O</sub>              | EOS<br>(END OF<br>SPEECH) | When no voice is synthesized.                                                                                                                                                                                        | During voice is be-<br>ing synthesized.                              |

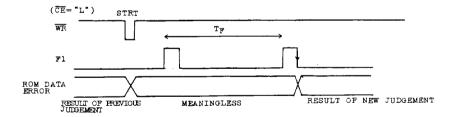

The timing chart for formation and releasing of each status is shown below.

#### COMMAND ERROR

② ROM DATA ERROR

COMMAND ERROR

T672lA INTERNAL SIGNAL

T6721A INTERNAL

SIGNAL

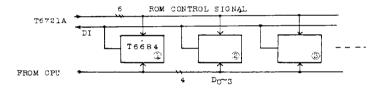

- (5) Setting of ROM start address

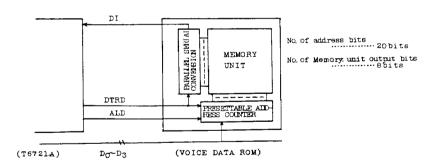

- ① Voice data ROM structure and ROM data output

The structure of Voice Data ROM and principal interface signals with T6721A are shown above.

The voice data output operation is executed as shown below:

(i) Selection of phrase to be spoken ROM start address 20 bits for the phrase are set from CPU by ADLD command and succeeding 5 nibble (20 bits) data to be output to the bus lines. At this time, load pulse ALD is once generated from T6721A to the presettable address counter every 1 nibble.

#### (ii) Start of speech

When STRT command is written from CPU, the address counter starts to count from the start address, and counted data are converted to serial data DI through the parallel serial conversion and transfered to T6721A. The transfer timing of this parallel serial conversion and this address count are controlled by DTRD pulse. At this time, a waiting time of TYP 120  $\mu s$  is required for the systematic reason from completion of address setting in (i) to STRT command write.

### (iii) Stop of speech

Unless the speech is forced to stop by STOP command, SPDN command, etc., the count in (ii) is continued until END ① code comes appear in voice data.

Definite setting method of ROM start address

The setting sequence of the above  $\bigcirc$  - (i) is as follows.

| CPU<br>Operation | to              | bu   | s 1     | m CF<br>ine<br>Do | U<br>EAM) | 3)  |      |      | A 15            |      |                  | RON              | fac<br>An |      | ess  |    | Ал |      |       | Аз               | C                | LSB)           | <b>)</b>         |

|------------------|-----------------|------|---------|-------------------|-----------|-----|------|------|-----------------|------|------------------|------------------|-----------|------|------|----|----|------|-------|------------------|------------------|----------------|------------------|

| Command          | 0               |      | LD<br>1 | 1                 | Y19       | Y18 | Y17  | Y16  | Y <sub>15</sub> | Y1 4 | Y <sub>1 3</sub> | Y <sub>1 2</sub> | Y11       | Y1 0 | Y9 . | Y8 | Y7 | Y6 \ | 6 Y.  | Y3 Y             | 2 Y1             | Yo             | (01d<br>address) |

| lst data         | Хз              | X 2  | Х 1     | Χο                | *         | *   | *    | *    | *               | *    | *                | *                | *         | *    | *    | *  | *  | *    | * *   | Х3 Х             | Z2 X1            | Хо             |                  |

| 2nd data         | X 7             | Х 6  | X 5     | X 4               | *         | *   | *    | *    | *               | *    | *                | *                | *         | *    | *    | *  | Х7 | Х6 2 | X5 X4 | Хэ Х             | ۷ X              | Χo             | i                |

| 3rd data         | X11             | Х1 0 | Хэ      | Хв                | *         | *   | *    | *    | *               | *    | *                | *                | Xıı       | X10  | X9   | Хв | Х7 | Х. 5 | K5 X4 | Хз Х             | ۷2 X             | ι Xο           | ı                |

| 4th data         | X <sub>15</sub> | X14  | Х13     | X, 2              | *         | *   | *    | *    | X,5             | X, 4 | Х, з             | Х, 2             | Х, ,      | X10  | х,   | X, | X, | Х,   | X, X, | Х <sub>3</sub> У | ۲ <sub>2</sub> X | X <sub>o</sub> |                  |

| 5th data         | X19             | Х1в  | X17     | X16               | X1 9      | Х18 | X1 7 | X1 6 | X15             | X14  | Х13              | X <sub>12</sub>  | X11       | Х10  | eX   | Хв | Х7 | Х6   | X5 X4 | XεX              | ζ <sub>2</sub> Χ | ı Xo           |                  |

<sup>\*</sup> denotes indefinite values.

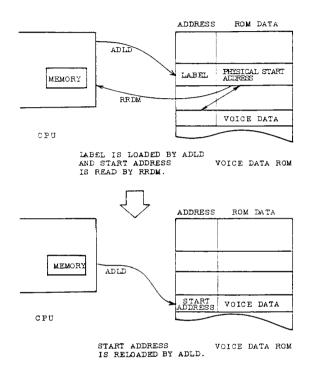

#### \* Use of Labeled Start Address

When the above start address  $X_0 \sim X_{19}$  is generated each time a phrase is assigned by CPU, load applied on CPU software will increase in proportion to increase in kinds of phrases. In addition, if it becomes necessary to change contents of phrases, not only the voice data ROM but also CPU side software must be changed.

Therefore, when serial numbers (labels) are assigned to phrases and labels are generated at CPU software side without generating physical addresses of these phrases, load at CPU side can be reduced.

For this purpose it is possible to use a method in which physical address of each phrase is stored in a part of the voice data ROM address space, that ROM address is used as a lable, which is then address loaded (ADLD) by CPU, and physical start address is read by RRDM and reloaded to select a phrase.

#### (6) BSY Output

The period in which  $\overline{BSY}$  signal is generated from T6721A is that period during which  $\overline{WR}$  and  $\overline{RD}$  from CPU must not be accepted by the synthesizing system. If  $\overline{WR}$  or  $\overline{RD}$  is performed disregarding this period, the synthesizing system does not accept  $\overline{WR}$  or  $\overline{RD}$  at all or operates uncertainly and the internal status may possibly becomes uncertain. In this case, however, status COMMAND ERROR is formed to give a warming.

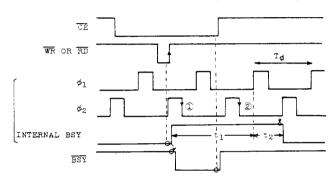

When  $\overline{BSY}$  signal is generated, length of the period of  $\overline{BSY}$  signal generation is either ① or ②, below.

Period from rise of WR or RD pulse from CPU to completion of command data transfer process in the synthesizing system.

T6721A INTERNAL SIGNAL

- \* BSY = CE.internal BSY

- \* TØ = 6.25us TYP.

- \* When rise of  $\overline{WR}$  or  $\overline{RD}$  and 1 of  $\phi_2$  fall in the diagram are close together,  $t_1+t_2$  may be further lengthened 1 T $\phi$  length in some cases due to delay of signal transmission in LSI.

|                                                                                    | Internal BSY generating period (t <sub>1</sub> + t <sub>2</sub> )                   | during internal BSY                                                                                                                    | operation by WR or RD<br>generating period<br>WR or RD in t2 term     |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Command RRDM and succeeding RD  WR or RD other than above (excluding command STOP) | From rise of WR to rise of next \$\phi_2\$ after 9 falls of \$\phi_2\$ are counted. | WR or RD is inhibited and COMMAND ERROR of the status is formed.                                                                       | WR or RD is accepted uncertainly, and un-                             |

| Command WR or RD during BSY by command STOP.                                       |                                                                                     | Ditto. However,<br>previously written<br>STOP command (RESET)<br>may be executed and<br>ERROR released imme-<br>diately in some cases. |                                                                       |

| WR or RD of<br>command STOP                                                        | 4 To Max. including characteristic consideration.                                   | WR or RD is inhibited<br>and COMMAND ERROR is<br>formed                                                                                | Ditto. However,<br>COMMAND ERROR may<br>be released in some<br>cases. |

Therefore, it is necessary for CPU to perform write or read after checking  $\overline{BSY}$  signal or to take a sufficient interval between each write or read.

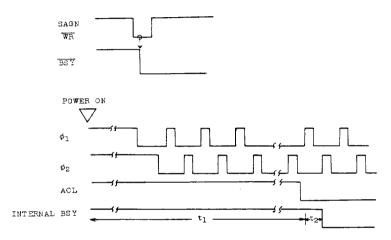

#### 2 Power ON transient status period

When the synthesizing system is placed in On status by turning the power switch ON or by SAGN command, AUTO CLEAR (ACL) is generated for a fixed time (about 30 ms) by the capacitor which has been externally mounted on T6721A  $\overline{\text{ACL}}$  terminal and the synthesizing system is initialized. This period is power ON transient status and  $\overline{\text{BSY}}$  will generate during its length.

When the power on is made by SAGN command, differing from the normal case, fall of  $\overline{BSY}$  signal begins to generate during  $\overline{WR}$  is at low level, not from rise of  $\overline{WR}$ .

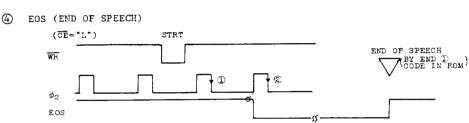

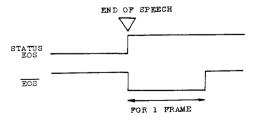

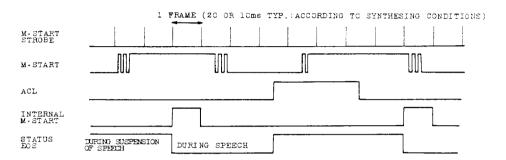

#### (7) EOS Output

AT the end of speech, the speech is stopped by END 1 code that has been set at the end of a phrase in the voice data ROM and the  $\overleftarrow{\text{EOS}}$  output is placed at low level for about 1 frame (20 or 10ms TYP). When the speech is forced to stop by STOP or SPDN command, no  $\overleftarrow{\text{EOS}}$  output is generated. Further, if the speech is restarted when  $\overleftarrow{\text{EOS}}$  is at LOW level, the  $\overleftarrow{\text{EOS}}$  output is placed at high level.

The relationship with status EOS is shown below.

- (8) Summary of principal precautions under CPU control

- ① Connect T6721A CPUM PIN to "H". (Page 8.)

- ② BSY output is the output from AND of T6721A internal BSY signal and CE. Therefore, when CE is at "H" level, there is no BSY output.

(Page 23.)

- ③ In [4]-(2) "Types of commands and operation of synthesizing system" (Pages 10 to 15), the following instructions should be particularly observed:

- (i) WR or RD must not be performed when internal BSY signal is being generated. (Pages 13, 14, 22, 23 and 24.)

- (ii) APD output is placed at "H" level by command SPDN and is also placed at "H" by next command SAGN. It should be made ot "L" level by AAGN command. (Page 10, 11.)

- (iii) In RD operation, the status is normally read out. (Pages 11 and 17.) To read ROM data, it is necessary to set mode by command RRDM.

- (iv) It is necessary to take 120 μs TYP for a period from ROM data start address setting to next RRDM or START command write. In the similar manner, 120 μs TYP is also required from read after RRDM to RRDM and each interval of subsequent reads. (Pages 13, 14 and 20.)

- (v) RRDM, STRT, 2 nibble and 6 nibble commands must not be executed during the speech. (Pages 13, 14.)

- (vi) It is necessary to take a time more than 30 ms before command SAGN is executed after SPDN command. (Page 10.)

- (vii) Time required for each command to start to operate after write. (Page 15.)

- 4 Timing for formation and release of each status. (Pages 17 to 19.)

# TOSHIBA INTEGRATED CIRCUIT

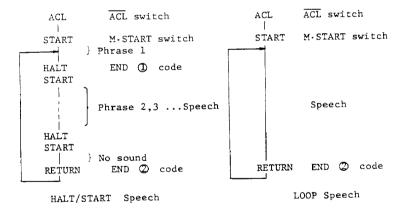

### [5] Operation under Manual Control

The operation under manual control is performed by M·START PIN, the switch externally mounted on  $\overline{ACL}$  PIN and control code END ① and END ② generated from the voice data ROM of T6721. Connect CPUM PIN of T6721A to "L".

#### (1) General

$\bigcirc$  Reset of synthesizing system  $\overline{\text{ACL}}$  SW ON

② Speech start M·START SW ON

③ Stop by end of speech END ① Code

4 Repeat of a series of speeches END 2 Code

Set of synthesizing conditions Set of T6721 dedicated PIN level and speech length

#### (2) Reset operation

- o After ACL switch is turned from ON to OFF, AUTO CLEAR (ACL) is generated for a fixed time (about 30ms) by the capacitor externally mounted on PIN, and the synthesizing system is initialized.

During this period, the M·START switch is not accepted. This reset operation is used when the speech is forced to stop or the system is initialized.

- o When the power switch (Pages  $41{\sim}40$ ) in the configuration circuit is turned from the OFF position to the ON position, ACL is generated as in the above case. If the power ON status is once turned to the OFF status and then, to the ON status again, a time of more than 100ms is required for turning OFF the power supply.

## (3) Start operation

The start operation is initiated by the M.START switch.

When  $M \cdot START$  switch is normally depressed, T6721A will start the speech after the chattering preventive time (about 20ms) has passed.

$M\!\cdot\!\text{START}$  switch must have been steadily depressed for more than 2 frame length.

Chattering of M·START switch must be less than  $20\,\mathrm{ms}$  at both ON and OFF sides.

(4) Setting of parameters for synthesizing conditions and speech length These parameters are set by connecting the T672lA synthesizing condition setting pins (6 pins) for the manual control to "H" or "L". These synthesizing conditions have been already selected at time of the analysis.

| Pin<br>Level | EXP                         | LOSS                              | BR            | FR         |

|--------------|-----------------------------|-----------------------------------|---------------|------------|

| L            | Sound source<br>shape pitch | Loss effect<br>calculation - None | 48 bits/frame | 20ms/frame |

| Н            | " triangle wave             | "<br>Available                    | 96 bits/frame | 10ms/frame |

| Pin<br>Level | REP                         | OD                                |               |            |

| L            | Repeat -<br>Available       | Filter - 10 stages                |               |            |

| н            | Repeat - None               | Filter - 8 stages                 | ]             |            |

Set the T6721A speech length setting pins(SP $_3 \sim$  SP $_0$ ) for the manual control to the codes shown in the following table.

| SP3, SP2, SP1<br>and SP0 Code  | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | А     |

|--------------------------------|------|------|------|------|------|------|------|------|------|-------|

| Magnification of speech length | x0.7 | x0.8 | x0.9 | x1.0 | xl.l | x1.2 | x1.3 | x1.4 | x1.5 | x1.55 |

When O, B, C, D, E and F are set, the magnification becomes x1.0.

## (5) HALT/START and ENDLESS LOOP speech

2 types of speeches are possible by the stop code END 1 and the ROM address initialize code END 2 arranged in the voice data ROM. Select either one of these codes.

#### [6] Dedicated Mask ROM

(1) Use of multiple dedicated mask ROMs

On T6684 128K ROM, the speechable times without using repeat bits are as follows:

2.4 kbps53 sec.4.8 kbps26 sec.9.6 kbps13 sec.

If time is insufficient, multiple mask ROMs can be used when they are parallelly connected. The connection in this case is as shown below:

All address counters that have been built in ROMs always perform the same count and each ROM selects itself by its built-in chip selecter according to address. Therefore, the individual chip select signal to each ROM from CPU or T6721A is not required as shown in the figure. In this case, current consumption of unselected ROM is TYP.  $20\mu A/ROM$ . (Refer to electrical characteristics.)

Max. Connectable ROMs

Total speech time (sec.)

|       |           | No.of con-<br>nectable ROMs |      |     |     |     |

|-------|-----------|-----------------------------|------|-----|-----|-----|

| T6772 | 64 kbits  | 8                           | 512K | 210 | 105 | 50  |

| T6684 | 128 kbits | 16                          | 2M   | 850 | 425 | 210 |

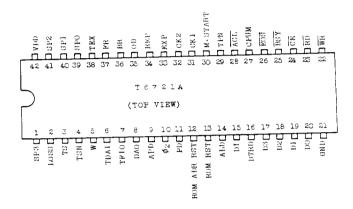

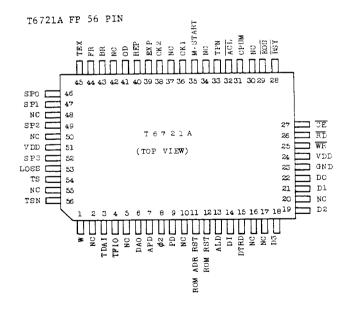

- [7] PIN DESCRIPTION & PIN CONNECTIONS

- (1) PIN Description

(1)-1 T6721A(Voice synthesizing LSI)

| DIN N          | PIN NO. | S                   | tructure         | Functional Explanation                                |

|----------------|---------|---------------------|------------------|-------------------------------------------------------|

| PIN Name       | ():DIP  | I/O                 | Pull-up/down     | runetional Explanation                                |

| พ              | 1 (5)   | Output              | -                | Output for test.                                      |

| TDAI           | 3 (6)   | Input               | Pull-down        | Input for test. To be con-<br>nected to GND.          |

| TFIO           | 4 (7)   | Output              | -                | Output for test.                                      |

| DAO            | 6 (8)   | DAC<br>Output       | -                | DA CONVERTER Output. Output of VSS during power down. |

| APD            | 7 (9)   | -                   |                  | Power down output for external audio circuit.         |

| Ø <sub>2</sub> | 8 (10)  |                     |                  | Clock pulse to ROM or P-ROM I/F LSI.                  |

| PD             | 9 (11)  |                     |                  | Power down to ROM or P-ROM I/F LSI.                   |

| ROM ADR<br>RST | 11 (12) | Output              | <del>-</del>     | Address reset to ROM or P-ROM I/F LSI.                |

| ROM RST        | 12 (13) |                     |                  | Initialize to ROM or P-ROM I/F LSI.                   |

| ALD            | 13 (14) |                     |                  | Sart address set pulse to ROM or P-ROM I/F LSI.       |

| DI             | 14 (15) | Input               | 500kΩ<br>Pull-up | Data input from ROM or P-ROM I/F LSI.                 |

| DTRD           | 15 (16) | Output              | -                | Data read pulse to ROM or P-ROM I/F LSI.              |

| D3             | 18 (17) |                     |                  |                                                       |

| D2             | 19 (18) | 3-state<br>bi-direc |                  | 4-bit bus line Input during WR is "L".                |

| D1             | 21 (19) | -tional -<br>bus    |                  | Output during RD is "L".<br>Hi-Z at other occasions   |

| DO             | 22 (20) |                     |                  |                                                       |

| PIN Name | PIN NO.         | S      | tructure                |                                                                                                    |

|----------|-----------------|--------|-------------------------|----------------------------------------------------------------------------------------------------|

| PIN Name | FP ( ):DIP      | 1/0    | Pull-up/down            | Functional Explanation                                                                             |

| GND      | 23 (21)         | Power  |                         | ov                                                                                                 |

| VDD      | 24<br>51 (42)   | supply |                         | +5V                                                                                                |

| WR       | 25 (22)         | Input  | 500kΩ                   | Write pulse input of command, data, etc. under CPU control.                                        |

| RD       | <b>2</b> 6 (23) | Input  | Pull-up                 | Read pulse input of status,ROM data, etc. under CPU control.                                       |

| CE       | 27 (24)         |        |                         | Chip enable pulse input under CPU control.                                                         |

| BSY      | 28 (25)         | Output | <u>_</u>                | BSY Output                                                                                         |

| EOS      | 29 (26)         | *      | - <del>-</del>          | Output at end of speech                                                                            |

| CPUM     | 31 (27)         | Input  | None                    | Fixed to high level under CPU control. Fixed to low level under CPU control.                       |

| ACL      | 32 (28)         | 1/0    | -                       | Power ON auto clear pin.<br>Schmitt input                                                          |

| TPN      | 33 (29)         |        | Pull-down               | Input for test. To be con-<br>nected to GND.                                                       |

| M·START  | 35 (30)         | Input  | 10mΩ ∿50mΩ<br>Pull-down | Start switch under manual control.                                                                 |

| CK1      | 36 (31)         | _      | None                    | Connection pin for ceramic oscillator (Murata Ceralock)                                            |

| CK2      | 38 (32)         | Output | -                       | Connection pin for ceramic oscillator (Murata Ceralock)                                            |

| EXP      | 39 (33)         | Input  | None                    | Connected to high or low level under of manual control according to fixed synthesizing conditions. |

| PIN Name | PIN NO.    |                  | ructure       | Functional Explanation                                      |  |  |

|----------|------------|------------------|---------------|-------------------------------------------------------------|--|--|

| rin name | FP ( ):DIP | I/O Pull-up/down |               | I directional Baptanacton                                   |  |  |

| REP      | 40 (34)    |                  |               |                                                             |  |  |

| OD       | 41 (35)    |                  |               | Connected to high or low                                    |  |  |

| BR       | 43 (36):   | i                | •             | level under of manual control according to fixed synthesiz- |  |  |

| FR       | 44 (37)    |                  |               | ing conditions.                                             |  |  |

| TEM      | 45 (38)    |                  |               | Input for test. To be con-<br>nected to GND.                |  |  |

| SP0      | 46 (39)    | Input            | None          |                                                             |  |  |

| SPl      | 47 (40)    | Impac            | none          | Speech length can be set up<br>by connecting this input pin |  |  |

| SP2      | 49 (41)    |                  |               | to high or low level under manual control.                  |  |  |

| SP3      | 52 (1)     |                  |               |                                                             |  |  |

| LOSS     | 53 (2)     |                  |               | Same as EXP ∿ FR.                                           |  |  |

| TS       | 54 (3)     |                  | Pull-down     | Input for test. To be con-                                  |  |  |

| TSN      | 56 (4)     |                  | r di i - down | nected to GND                                               |  |  |

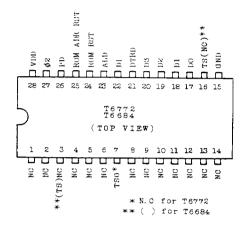

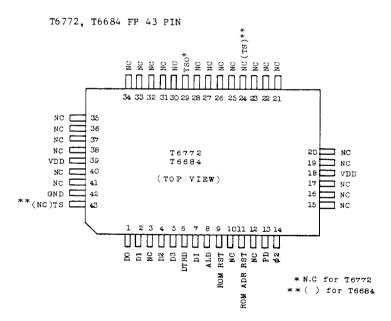

(1)-2 T6772, T6684 (Mask ROM)

|                 | PIN NO.       | S              | tructure           |                                                                                |  |  |  |  |

|-----------------|---------------|----------------|--------------------|--------------------------------------------------------------------------------|--|--|--|--|

| PIN Name        | FP ():DIP     | I/O            | Pull-up/down       | Functional Explanation                                                         |  |  |  |  |

| DO              | 1 (17)        |                |                    |                                                                                |  |  |  |  |

| D1              | 2 (18)        |                |                    | 4-bit bus line                                                                 |  |  |  |  |

| D2              | 4 (19)        | Input          | None               | Address data input at sett-<br>ing of start address.                           |  |  |  |  |

| D3              | 5 (20)        |                |                    |                                                                                |  |  |  |  |

| DTRD            | 6 (21)        |                |                    | Data read pulse from synthe-<br>sizing LSI.                                    |  |  |  |  |

| DI              | 7 (22)        | 3-state output | -                  | Serial data output to synthesizing LSI. Hz during nonselection and power down. |  |  |  |  |

| ALD             | 8 (23)        |                |                    | Start address set pulse from synthesizing LSI.                                 |  |  |  |  |

| ROM RST         | 9 (24)        |                |                    | Initialize from synthesizing LSI.                                              |  |  |  |  |

| ROM ADR<br>RST  | 11 (25)       | Input None     |                    | Address reset from synthe-<br>sizing LSI.                                      |  |  |  |  |

| PD              | 13 (26)       |                |                    | Power down from synthesizing LSI.                                              |  |  |  |  |

| Ø <sub>2</sub>  | 14 (27)       |                | 2                  | Clock pulse from synthesizing LSI.                                             |  |  |  |  |

| V <sub>DD</sub> | 18<br>39 (28) | Power          | _                  | +5V                                                                            |  |  |  |  |

| GND             | 42 (15)       | supply         |                    | 0V                                                                             |  |  |  |  |

| TS              | 43 (16)       | Input          | 500kΩ<br>Pull-down | Input for test.                                                                |  |  |  |  |

| TSO             | 29 (17)       | Output         | _                  | Output for test.<br>(N.C. for T6772)                                           |  |  |  |  |

<sup>\*</sup> T6684

#### (2) PIN CONNECTIONS

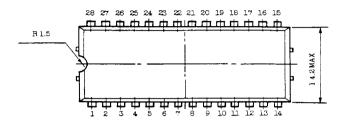

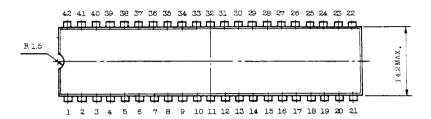

(2)-1. T6721A DIP 42PIN

(2)-2. T6772, T6684 DIP 28 PIN

Notes: 1. The ceramic oscillator and capacitor connected to  ${\tt CK}_1$ , and  ${\tt CK}_2$  of the T6721A should be arranged close to  ${\tt CK}_1$  and  ${\tt CK}_2$ .

2. Other than NC terminal should not be used as relay terminals.

- Notes: 1. The ceramic oscillator and capacitor connected to  ${\tt CK}_1$  and  ${\tt CK}_2$  of the T6721A should be arranged close to  ${\tt CK}_1$  and  ${\tt CK}_2$ .

- 2. Other than NC terminal should not be used as relay terminals.

Notes: 1. The ceramic oscillator and capacitor connected  ${\rm CK}_1$  and  ${\rm CK}_2$  of the T6721A should be arranged close to  ${\rm CK}_1$  and  ${\rm CK}_2$ .

2. Other than NC terminal should not be used as relay terminals.

- Notes: 1. The ceramic oscillator and capacitor connected  ${\rm CK}_1$  and  ${\rm CK}_2$  of the T6721A should be arranged close to  ${\rm CK}_1$  and  ${\rm CK}_2$

- 2. Other than NC terminal should not be used as relay terminals.

### [9] ELECTRICAL CHARACTERISITCS

ABSOLUTE MAXIMUM RATING (Applicable to the T6721A, T6772 and T6684.)

| SYMBOL | ITEM                  | RATING                      | UNIT |

|--------|-----------------------|-----------------------------|------|

| VDD    | Supply Voltage        | -0.3 ~ 6.0                  |      |

| VIN    | Input Voltage         | -0.3 ∿ V <sub>DD</sub> +0.3 | V    |

| Tstg   | Storage Temperature   | <b>-</b> 55 ∿ 125           | °C   |

| Topr   | Operating Temperature | -10 ∿ 55                    | °C   |

T6721A AC CHARACTERISTICS (Ta =  $-10 \sim 55$ °C, C<sub>L</sub> = 15pF)

|                  |                                                                               | THE GOVERNMENT       | STANDARD |          |      | UNIT |

|------------------|-------------------------------------------------------------------------------|----------------------|----------|----------|------|------|

| SYMBOL           | PARAMETER                                                                     | TEST CONDITION       | MIN.     | TYP.     | MAX. | UNII |

| twcs             | CE Fall → WR Fall time                                                        | V <sub>DD</sub> = 5V | 200      |          |      | ns   |

| twcc             | WR Pulse width                                                                | п                    | 4        |          |      | μs   |

| twch             | $\overline{\mathrm{WR}}$ Rise $	o$ $\overline{\mathrm{CE}}$ Rise time         | "                    | 200      | -        | -    | ns   |

| twDS             | WR Fall Time → Effective data time                                            | "                    | 2        | -        | -    | μѕ   |

| tWD              | WR Rise → Data hold time                                                      | 11                   | 10       |          |      | μs   |

| tCBY             | $\overline{WR}$ , $\overline{RD}$ Rise $\rightarrow \overline{BSY}$ Fall time | 11                   | _        | -        | 2    | μs   |

| tRCS             | $\overline{CE}$ Fall $\rightarrow \overline{RD}$ Fall time                    | **                   | 200      | _        | -    | ns   |

| tRCC             | RD Pulse width                                                                | **                   | 4        | -        |      | μs   |

| tRCH             | $\overline{\text{RD}}$ Rise $\rightarrow$ $\overline{\text{CE}}$ Rise Time    | "                    | 200      | <u> </u> | -    | ns   |

| tRDS             | RD Fall → Effective data time                                                 | 11                   |          | -        | 2    | μs   |

| t <sub>RDH</sub> | $\overline{\text{RD}}$ Rise $\rightarrow$ Effective data hold time            | 11                   |          | _        | 2    | μs   |

Definition of T6721A AC Characteristics

# TOSHIBA INTEGRATED CIRCUIT

|                    |                                      | APPLICATION                          |                                             | ST                   | ANDARI     | D               | UNIT |

|--------------------|--------------------------------------|--------------------------------------|---------------------------------------------|----------------------|------------|-----------------|------|

| SYMBOL             | PARAMETER                            | PIN                                  | CONDITIONS                                  | MIN.                 | TYP.       | MAX.            | UNII |

| v <sub>DD</sub>    | Supply Voltage                       | $v_{ m DD}$                          | _                                           | 3.5                  | 5          | 5.7             | V    |

| IDD(1)             | Current dissipation during operation | v <sub>DD</sub>                      | V <sub>DD</sub> =5V, Output<br>with no load | _                    | 0.5        | 1.2             | mA   |

| IDD(2)             | Current during power down            | VDD                                  | 11                                          | -                    | 0.2        | 3               | μA   |

| fø                 | Clock operation frequency            | -                                    | VDD=3.5∿5.7V,<br>Recommended<br>circuit     | 144                  | 160        | 176             | kHz  |

| fosc               | " oscillation "                      | CK2                                  | 77 91                                       | 608                  | 640        | 672             | kHz  |

| VIH                | "l" input voltage                    | Except ACL                           | V <sub>DD</sub> =3.5 ∿5.7V                  | V <sub>DD</sub> -0.8 | _          | ADD             | Ą    |

| VIL                | "0" "                                | 11                                   | 11                                          | 0                    | -          | 0.8             | V    |

| v <sub>ОН</sub>    | "1" output voltage                   | Except ACL,<br>DAO, CK2              | Output no<br>load                           | V <sub>DD</sub> -0.4 | -          | VDD             | V    |

| VOL                | "0" "                                | 31                                   | 11                                          | 0                    | -          | 0.4             | v    |

| RINP(1)            | Input pull-down resistor             | M-START                              | -                                           | _                    | 30         | -               | kΩ   |

| RINP(2)            | " pul-up "                           | DI, WR, RD, CE                       |                                             | -                    | 500        | -               | kΩ   |

| IIH                | "1" input current                    | Except TPN,<br>MSTART, TS, TSN       | VIN≠VDD                                     | -                    | -          | 5               | υA   |

| IIL                | "0" "                                | Except DI,<br>WR, RD, CE             | v <sub>IN</sub> =0v                         | _                    | -          | <b>-</b> 5      | μА   |

| I <sub>OH(1)</sub> | 'l' Output current(1)                | EOS, BSY                             | VOUT=VDD/2                                  | -0.4                 |            | -               | mA   |

| IOH(2)             | (2)                                  | D <sub>0</sub> ∿ D <sub>3</sub>      | VOUT=VDD-0.4V                               | -0.2                 | -          |                 | mA   |

| IOH(3)             | " (3)                                | Ø <sub>2</sub> ,W,APD,TFIO           | 11                                          | -0.2                 |            |                 | mA   |

| IOH(4)             | " (4)                                | Except (1), (2),(3), CK2 DAO and ACL | 11                                          | -0.2                 | -          | _               | mA   |

| IOL(1)             | "0" " (1)                            | EOS, BSY                             | V <sub>OUT</sub> = 0.4V                     | 0.8                  | <u></u> _  |                 | mA   |

| IOL(2)             | " (2)                                | D <sub>0</sub> ∿ D <sub>3</sub>      | н                                           | 0.8                  |            | <u> </u>        | mA   |

| IOL(3)             | " (3)                                | Ø <sub>2</sub> ,W,APD,TFIO           | "                                           | 0.5                  | <u> </u>   | <del>-</del> -  | mA   |

| IOL(4)             | (4)                                  | Same as IOH(4)                       | "                                           | 0.2                  | ļ <u> </u> | ļ -             | mA   |

| VouT               | D/A converter out-<br>put voltage    | DAO                                  | At time of output with no load              | 0                    | -          | V <sub>DD</sub> | V    |

| ROUT               | " " impedance                        | DAO                                  |                                             | -                    | 50         |                 | kΩ   |

| SYMBOL              | PARAMETER                                              | APPLICATION     | CONDITIONS                              | STANDARD                |      |                | UNIT              |

|---------------------|--------------------------------------------------------|-----------------|-----------------------------------------|-------------------------|------|----------------|-------------------|

| SIMBUL              | PARAMETER                                              | PIN             | CONDITIONS                              | MIN.                    | TYP. | MAX.           | UNII              |

| $v_{\mathrm{DD}}$   | Supply Voltage                                         | Δ <sup>DD</sup> |                                         | 3.5                     | 5    | 5.7            | V                 |

| IDD(1)              | Current dissipation during operation (at selection)    | V <sub>DD</sub> | VDD=5V, output with no load             | -                       | 40   | 80             | μА                |

| I <sub>DD</sub> (2) | Current dissipation during operation (at nonselection) | V <sub>DD</sub> | 11                                      | _                       | 20   | 40             | Αц                |

| IDD(3)              | Current during power down                              | V <sub>DD</sub> | 11                                      | - Tylumomic consequence | 0.2  | 3              | :<br>· μ <b>Α</b> |

| fØ                  | Clock operation frequency                              | -               | V <sub>DD</sub> =3.5 ~5.7V              | 144                     | 160  | 176            | kHz               |

| VIH                 | "l" input voltage                                      | All-inputPIN    | 11                                      | v <sub>DD</sub> -0.8    | -    | $v_{DD}$       | V                 |

| AIL                 | "0" "                                                  | 11              | 11                                      | 0                       | -    | 0.8            | v                 |

| VOH                 | "l" output voltage                                     | DI              | Output no load                          | V <sub>DD</sub> -0.4    | _    | $v_{DD}$       | V                 |

| VOL                 | "0" "                                                  | 11              | , , , , ,                               | 0                       | -    | 0.4            | v                 |

| I <sub>IH</sub>     | "1" input current                                      | All-inputPIN    | VIN = VDD                               | -                       | -    | 5              | μА                |

| IIL                 | "0" "                                                  | 11              | VIN = OV                                | -                       | -    | <del>-</del> 5 | μА                |

| IOLK                | 3-state output OFF<br>leak                             | DI              | 0 ≤ VIN≤ VDD                            | -                       | -    | <b>±</b> 5     | μА                |

| IOH                 | "1" output current                                     | T1              | V <sub>OUT</sub> =V <sub>DD</sub> -0.4V | -0.2                    | -    | -              | mA                |

| IOL                 | "0" "                                                  | 11              | V <sub>OUT</sub> = 0.4V                 | 0.2                     | _    | -              | mA                |

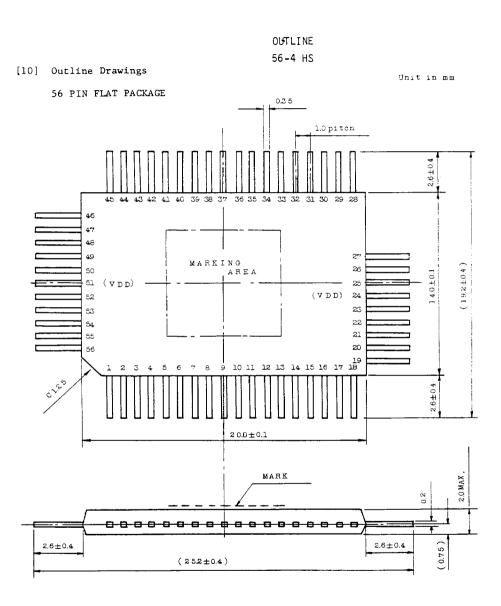

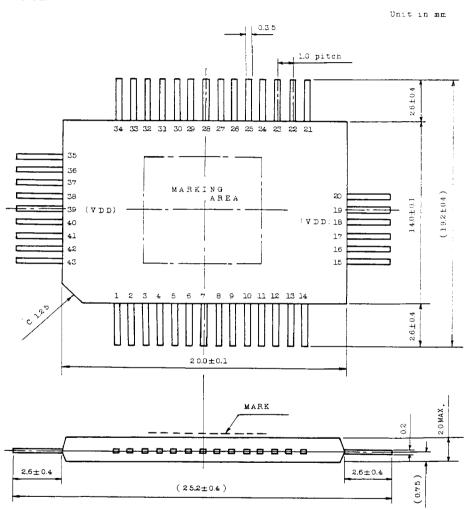

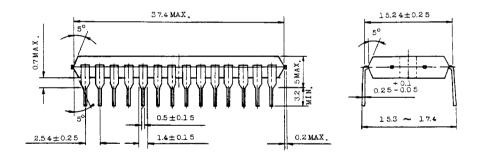

OUTLINE 43-4HS

43 PIN FLAT PACKAGE

Unit in mm

Note: The lead pitch is  $2.54\,\mathrm{mm}$  and the tolerance is  $\pm 0.25\,\mathrm{mm}$  against the theoretical center of each lead that is obtained on the basis of No.1 and No. 28 leads.

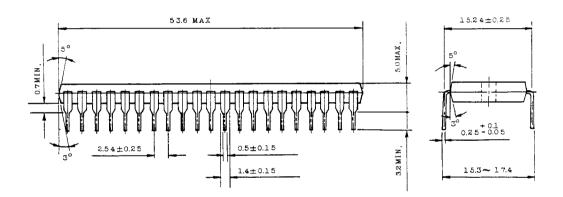

Unit in mm

Note: The lead pitch is  $2.54\,\mathrm{mm}$  and the tolerance is  $\pm 0.25\,\mathrm{mm}$  against the theoretical center of each lead that is obtained on the basis of