## CMOS 10- & 12-Bit Monolithic Multiplying D/A Converters

AD7520, AD7521

#### **FEATURES**

AD7520: 10-Bit Resolution AD7521: 12-Bit Resolution

End Point Linearity: 8-, 9- and 10-Bit Nonlinearity Tempco: 2ppm of FSR/°C

Low Power Dissipation: 20mW **Current Settling Time: 500ns**

Feedthrough Error: 1/2LSB @ 100kHz

TTL/DTL/CMOS Compatible

Note: AD7533 is recommended for new 10-bit designs. AD7541A or AD7545 is recommended for new

12-bit designs.

#### GENERAL DESCRIPTION

The AD7520 (AD7521) is a low cost, monolithic 10-bit (12-bit) multiplying digital-to-analog converter packaged in a 16-pin (18-pin) DIP. The devices use advanced CMOS and thin film technologies providing up to 10-bit accuracy with TTL/ DTL/CMOS compatibility.

The AD7520 (AD7521) operates from +5V to +15V supply and dissipates only 20mW, including the ladder network.

Typical AD7520 (AD7521) applications include: digital/ analog multiplication, CRT character generation, programmable power supplies, digitally controlled gain circuits, etc.

#### ORDERING INFORMATION

| Nonlinearity   | Temperature Range |                |                 |  |

|----------------|-------------------|----------------|-----------------|--|

|                | 0 to +70°C        | -25°C to +85°C | -55°C to +125°C |  |

| 0.2% (8-Bit)   | AD7520JN          | AD7520JD       | AD7520SD        |  |

|                | AD7521JN          | AD7521JD       | AD7521SD        |  |

| 0.1% (9-Bit)   | AD7520KN          | AD7520KD       | AD7520TD        |  |

|                | AD7521KN          | AD7521KD       | AD7521TD        |  |

| 0.05% (10-Bit) | AD7520LN          | AD7520LD       | AD7520UD        |  |

|                | AD7521LN          | AD7521LD       | AD7521UD        |  |

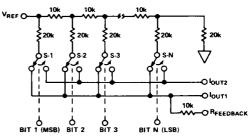

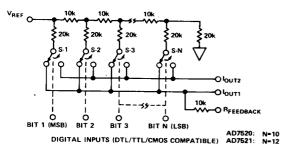

### AD7520, AD7521 FUNCTIONAL BLOCK DIAGRAM

#### DIGITAL INPUTS (DTL/TTL/CMOS COMPATIBLE)

AD7520: N=10AD7521: N=12

Logic:

A switch is closed to l<sub>OUT1</sub> for its digital input in a "HIGH" state.

#### PIN CONFIGURATIONS

|                          | _                      |                        | _                      |

|--------------------------|------------------------|------------------------|------------------------|

| <b>1</b> 0υτ1 <b>1</b> • | 16 RFEEDBACK           | louт1                  | 18 RFEEDBACK           |

| ουτ2 2                   | 15 VREF IN             | fουτ2 2                | 17 VREF IN             |

| GND 3 AD7520             | 14 V <sub>DD</sub> (+) | GND 3 AD7521           | 16 V <sub>DO</sub> (+) |

| BIT 1 (MSB) 4 TOP VIEW   | 13 BIT 10 (LSB)        | BIT 1 (MSB) 4 TOP VIEW | 15 BIT 12 (LSB)        |

| BIT 2 5 (Not To Seal     | 12 BIT 9               | BIT 2 5 (Not To Scale  | 14 BIT 11              |

| BIT 3 6                  | 11 BIT 8               | BIT 3 6                | 13 BIT 10              |

| BIT 4 7                  | 10 BIT 7               | BIT 4 🔼                | 12 BIT 9               |

| BIT 5 B                  | 9 BIT 6                | ВІТ 5 📳                | 11 BIT 8               |

| <del></del>              | _                      | BIT 6 9                | 10 BIT 7               |

#### 16-PIN DIP

18-PIN DIP

#### PACKAGE IDENTIFICATION<sup>1</sup>

Suffix D: Ceramic DIP Package

AD7520: (D16B) AD7521: (D18B)

Suffix N: Plastic DIP Package

AD7520 (N16B) AD7521 (N18B)

<sup>&</sup>lt;sup>1</sup> See Section 19 for package outline information.

# **SPECIFICATIONS** (V<sub>DD</sub> = +15, V<sub>REF</sub> = +10V, T<sub>A</sub> = +25°C unless otherwise noted)

| PARAMETER                                     | AD7520                                  | AD7521  | TEST CONDITIONS                            |

|-----------------------------------------------|-----------------------------------------|---------|--------------------------------------------|

| DC ACCURACY <sup>1</sup>                      |                                         |         |                                            |

| Resolution                                    | 10 Bits                                 | 12 Bits |                                            |

| Relative Accuracy (See Figure 5)              |                                         | 12 2115 |                                            |

| , , , , , , , , , , , , , , , , , , , ,       | J, 0.2% of FSR max (8 Bit)              | •       | S,T,U: over -55°C to +125°C                |

|                                               | S, 0.2% of FSR max (8 Bit)              |         | -10V≤V <sub>REF</sub> ≤+10V                |

|                                               | K, 0.1% of FSR max (9 Bit)              | •       | KEF                                        |

|                                               | T, 0.1% of FSR max (9 Bit)              | •       |                                            |

|                                               | L, 0.05% of FSR max (10 Bit)            | •       |                                            |

|                                               | U, 0.05% of FSR max (10 Bit)            |         |                                            |

| Nonlinearity Tempco                           | 2ppm of FSR/°C max                      | *       | -10V≤V <sub>REF</sub> ≤+10V                |

| Gain Error <sup>2</sup>                       | 0.3% of FSR typ                         | •       | -10V≤V <sub>REF</sub> ≤+10V                |

| Gain Error Tempco <sup>2</sup>                | 10ppm of F\$R/bC max                    |         | -10V≤V <sub>REF</sub> ≤+10V                |

| Output Leakage Current                        | , , , , , , , , , , , , , , , , , , , , |         | KEF                                        |

| (either output)                               | 200nA max                               | •       | Over specified temperature range           |

| Power Supply Rejection                        | 50ppm of FSR/% typ                      | •       | •                                          |

| (See Figure 6)                                | ,,                                      |         | ,                                          |

| AC ACCURACY                                   | 710.5.000                               |         | To 0.05% of FSR                            |

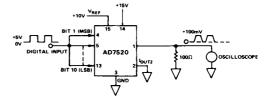

| Output Current Settling Time                  | 500ns typ                               |         | All digital inputs low to high             |

| (See Figure 10)                               | 5 00 115 typ                            |         | and high to low                            |

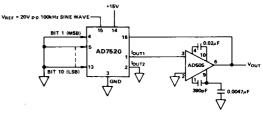

| Feedthrough Error (See Figure 9) <sup>4</sup> | 10mV p-p max                            |         | $V_{RFF} = 20V \text{ p-p}, 100\text{kHz}$ |

| 1 00 miles B. 1 mer (6 00 1 1 B 1 10 7 7      | P P                                     | •       | All digital inputs low                     |

| REFERENCE INPUT                               |                                         |         |                                            |

| Input Resistance <sup>3</sup>                 | 5kΩ min                                 | •       |                                            |

| •                                             | 10kΩ typ                                |         |                                            |

|                                               | 20kΩ max                                | •       |                                            |

| ANALOG OUTPUT                                 |                                         |         |                                            |

| Output Capacitance IOUT1                      | 120pF typ                               | •       | All digital inputs high                    |

| (See Figure 8) IOUT2                          | 37pF typ                                | •       | All digital inputs high                    |

| оот2<br><sup>І</sup> оот1                     | 37pF typ                                | •       | All digital inputs low                     |

| l <sub>our2</sub>                             | 120pF typ                               | •       | All digital inputs low                     |

| Output Noise (both outputs)                   | Equivalent to 10kΩ typ                  | •       | <b>B</b>                                   |

| (See Figure 7)                                | Johnson noise                           |         |                                            |

| DIGITAL INPUTS <sup>5</sup>                   |                                         |         |                                            |

| Low State Threshold                           | 0.8V max                                |         | Over specified temperature range           |

| High State Threshold                          | 2.4V min                                | *       | Over specified temperature range           |

| Input Current (low to high state)             | 1μA typ                                 |         | Over specified temperature range           |

| Input Coding                                  | Binary                                  | *       | See Tables I & II under Applications       |

| POWER REQUIREMENTS                            |                                         |         |                                            |

| Power Supply Voltage Range                    | +5V to +15V                             |         |                                            |

|                                               | 5nA typ                                 |         | All digital inputs at GND                  |

| $I_{\mathrm{DD}}$                             | 2mA max                                 | *       | All digital inputs high or low             |

| Total Dissipation (Including ladder)          |                                         |         | An digital inputs ingit of fow             |

| Total Dissipation (Including ladder)          | 20mW typ                                | -       |                                            |

Specifications subject to change without notice.

#### VOL. I, 9-154 DIGITAL-TO-ANALOG CONVERTERS

<sup>&</sup>lt;sup>1</sup> Full scale range (FSR) is 10V for unipolar mode and ±10V for bipolar mode.

<sup>&</sup>lt;sup>3</sup> Using the internal R<sub>FEEDBACK</sub>

<sup>3</sup> Ladder and feedback resistor tempco is approximately -150ppm/°C.

<sup>4</sup> C. <sup>4</sup>To minimize feedthrough with the ceramic package, the user must ground the metal lid. If the lid is not

grounded, then the feedthrough is 10mV typical and 30mV maximum.

Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

#### ABSOLUTE MAXIMUM RATINGS

- 1. Do not apply voltages higher than  $V_{DD}$  or less than GND potential on any terminal except  $V_{REF}$ .

- The digital control inputs are zener protected; however, permanent damage may occur on unconnected units under high energy electrostatic fields. Keep unused units in conductive foam at all times.

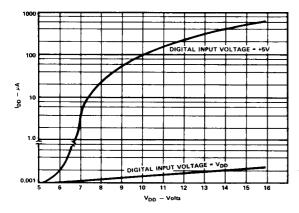

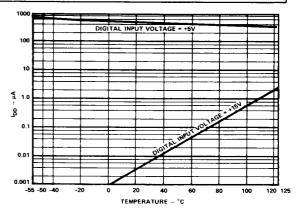

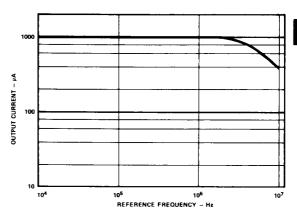

## TYPICAL PERFORMANCE CURVES $T_A = +25^{\circ}C$ , $V_{DD} = +15V$ unless otherwise noted

Figure 1. Supply Current vs. Supply Voltage

Figure 2. Supply Current vs. Temperature

Figure 3. Output Current Bandwidth

Figure 4. Output Current Settling Time vs. Digital Input Voltage

#### **TEST CIRCUITS**

Note: The following test circuits apply for the AD7520. Similar circuits can be used for the AD7521.

#### DC PARAMETERS

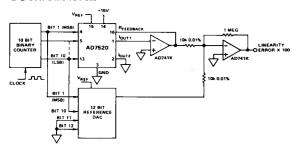

Figure 5. Relative Accuracy

Figure 6. Power Supply Rejection

#### AC PARAMETERS

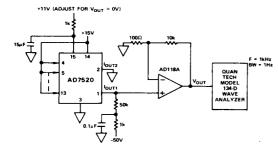

Figure 7. Noise

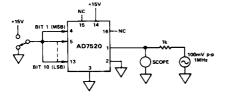

Figure 8. Output Capacitance

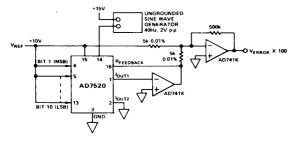

Figure 9. Feedthrough Error

Figure 10. Output Current Settling Time

#### **TERMINOLOGY**

RELATIVE ACCURACY: Relative accuracy or end-point nonlinearity is a measure of the maximum deviation from a straight line passing through the end-points of the DAC transfer function. It is measured after adjusting for ideal zero and full scale and is expressed in % or ppm of full scale range or (sub) multiples of 1LSB.

**RESOLUTION:** Value of the LSB. For example, a unipolar converter with n bits has a resolution of  $(2^{-n})$  ( $V_{REF}$ ). A bipolar converter of n bits has a resolution of  $[2^{-(n-1)}]$  [ $V_{REF}$ ]. Resolution in no way implies linearity.

SETTLING TIME: Time required for the output function of the DAC to settle to within 1/2 LSB for a given digital input stimulus, i.e., 0 to Full Scale.

GAIN: Ratio of the DAC's operational amplifier output voltage to the input voltage.

FEEDTHROUGH ERROR: Error caused by capacitive coupling from V<sub>REF</sub> to output with all switches OFF.

OUTPUT CAPACITANCE: Capacity from  $I_{OUT1}$  and  $I_{OUT2}$  terminals to ground.

OUTPUT LEAKAGE CURRENT: Current which appears on I<sub>OUT1</sub> terminal with all digital inputs LOW or on I<sub>OUT2</sub> terminal when all inputs are HIGH.

#### VOL. I, 9-156 DIGITAL-TO-ANALOG CONVERTERS

### CIRCUIT DESCRIPTION

#### GENERAL CIRCUIT INFORMATION

The AD7520 (AD7521), a 10-bit (12-bit) multiplying D/A converter, consists of a highly stable thin film R-2R ladder and ten (twelve) CMOS current switches on a monolithic chip. Most applications require the addition of only an output operational amplifier and a voltage or current reference.

The simplified D/A circuit is shown in Figure 11. An inverted R-2R ladder structure is used – that is, the binarily weighted currents are switched between the l<sub>OUT1</sub> and l<sub>OUT2</sub> bus lines, thus maintaining a constant current in each ladder leg independent of the switch state.

(Switches shown for Inputs "High")

Figure 11. AD7520 (AD7521) Functional Diagram

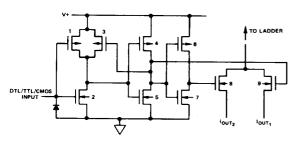

One of the CMOS current switches is shown in Figure 12. The geometries of devices 1, 2 and 3 are optimized to make the digital control inputs DTL/TTL/CMOS compatible over the full military temperature range. The input stage drives two inverters (devices 4, 5, 6 and 7) which in turn drive the two output N-channels. The "ON" resistances of the first six switches are binarily scaled so the voltage drop across each switch is the same. For example, switch-1 of Figure 12 was designed for an "ON" resistance of 20 ohms, switch-2 of 40 ohms and so on. For a 10V reference input, the current through switch 1 is 0.5mA, the current through switch 2 is 0.25mA, and so on, thus maintaining a constant 10mV drop across each switch. It is essential that each switch voltage drop be equal if the binarily weighted current division property of the ladder is to be maintained.

Figure 12. CMOS Switch

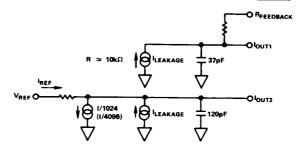

Figure 13. AD7520 (AD7521) Equivalent Circuit— All Digital Inputs Low

#### **EQUIVALENT CIRCUIT ANALYSIS**

The equivalent circuits for all digital inputs high and all digital inputs low are shown in Figures 13 and 14. In Figure 13 with all digital inputs low, the reference current is switched to I<sub>OUT2</sub>. The current source I<sub>LEAKAGE</sub> is composed of surface and

junction leakages to the substrate while the  $\frac{1}{1024} \left( \frac{1}{4096} \right)$

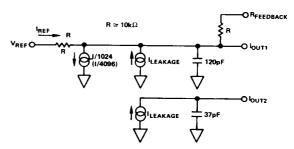

current source represents a constant 1-bit current drain through the termination resistor on the R-2R ladder. The "ON" capacitance of the output N channel switch is 120pF, as shown on the  $I_{OUT2}$  terminal. The "OFF" switch capacitance is 37pF, as shown on the  $I_{OUT1}$  terminal. Analysis of the circuit for all digital inputs high, as shown in Figure 14 is similar to Figure 13; however, the "ON" switches are now on terminal  $I_{OUT1}$ , hence the 120pF at that terminal.

Figure 14. AD7520 (AD7521) Equivalent Circuit— All Digital Inputs High

#### APPLICATIONS

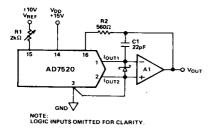

## UNIPOLAR BINARY OPERATION (2-QUADRANT MULTIPLICATION)

Figure 15 shows the analog circuit connections required for unipolar binary (2-quadrant multiplication) operation. The logic inputs are omitted for clarity. With a dc reference voltage or current (positive or negative polarity) applied at pin 15, the circuit is a unipolar D/A converter. With an ac reference voltage or current the circuit provides 2-quadrant multiplication (digitally controlled attenuation). The input/output relationship is shown in Table I. Protection Schottky shown in Figure 15 is not required when using TRIFET output amplifiers such as the AD542 or AD544.

R1 provides full scale trim capability [i.e.—load the DAC register to 11 1111 1111, adjsut R1 for  $V_{OUT} = -V_{REF}$  (1 –  $2^{-10}$ )]. Alternatively, Full Scale can be adjusted by omitting R1 and R2 and trimming the reference voltage magnitude.

C1 phase compensation (10 to 25pF) may be required for stability when using high speed amplifiers. (C1 is used to cancel the pole formed by the DAC internal feedback resistance and output capacitance at  $I_{\rm OUT1}$ ).

Amplifier A1 should be selected or trimmed to provide  $V_{OS} \le 10\%$  of the voltage resolution at  $V_{OUT}$ . Additionally, the amplifier should exhibit a bias current which is low over the temperature range of interest (bias current causes output offset at  $V_{OUT}$  equal to  $I_B$  times the DAC feedback resistance, nominally 15k $\Omega$ ).

Figure 15. Unipolar Binary Operation (2-Quadrant Multiplication)

| DIGITAL INPUT | ANALOG OUTPUT                               |

|---------------|---------------------------------------------|

| 111111111     | -V <sub>REF</sub> (1 - 2 <sup>-10</sup> )   |

| 1000000001    | $-V_{REF} (1/2 + 2^{-10})$                  |

| 1000000000    | -V <sub>REF</sub> 2                         |

| 0111111111    | -V <sub>REF</sub> (1/2 - 2 <sup>-10</sup> ) |

| 0000000001    | -V <sub>REF</sub> (2 <sup>-10</sup> )       |

| 0000000000    | 0                                           |

Table I. Code Table -- Unipolar Binary Operation

NOTE: 1 LSB = 2<sup>-10</sup> V<sub>REE</sub>

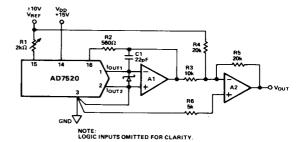

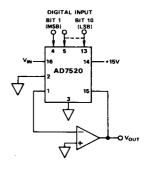

## BIPOLAR OPERATION (4-QUADRANT MULTIPLICATION)

Figure 16 and Table II illustrate the circuitry and code relationship for bipolar operation. With a dc reference (positive or negative polarity) or an ac reference the circuit provides offset binary operation. Protection Schottky shown in Figure 16 is not required when using TRIFET output amplifiers such as the AD542 or AD544.

With the DAC register loaded to 10 0000 0000, adjust R1 for  $V_{OUT}$  = 0V (alternatively, one can omit R1 and R2 and adjust the ratio of R3 to R4 for  $V_{OUT}$  = 0V). Full scale trimming can be accomplished by adjusting the amplitude of  $V_{REF}$  or by varying the value of R5.

As in unipolar operation, A1 must be chosen for low  $V_{OS}$  and low  $I_B$ . R3, R4 and R5 must be selected for matching and tracking. Mismatch of 2R3 to R4 causes both offset and Full Scale error. Mismatch of R5 to R4 or 2R3 causes Full Scale error. C1 phase compensation (10pF to 25pF) may be required for stability.

#### Offset Adjustment

- 1. Make V<sub>REF</sub> approximately +10V.

- 2. Tie all digital inputs to +15V (Logic "1").

- Adjust amplifier #2 offset trimpot for 0V ±1mV at amplifier #2 output.

- 4. Tie MSB (Bit 1) to +15V, all other bits to ground.

- Adjust amplifier #1 offset trimpot for 0V ±1mV at V<sub>OUT</sub>.

| DIGITAL INPUT | ANALOG OUTPUT                            |

|---------------|------------------------------------------|

| 1111111111    | -V <sub>REF</sub> (1 - 2 <sup>-9</sup> ) |

| 1000000001    | -V <sub>REF</sub> (2 <sup>-9</sup> )     |

| 1000000000    | 0                                        |

| 0111111111    | V <sub>REF</sub> (2 <sup>-9</sup> )      |

| 0000000001    | $V_{REF} (1 - 2^{-9})$                   |

| 0000000000    | V <sub>REF</sub>                         |

NOTE: 1 LSB = 2" VREF

Table II. Code Table - Bipolar (Offset Binary) Operation

Figure 16. Bipolar Operation (4-Quadrant Multiplication)

### VOL. I, 9-158 DIGITAL-TO-ANALOG CONVERTERS

### **Applications**

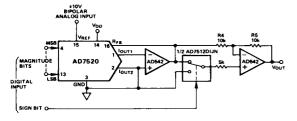

#### 10-BIT AND SIGN MULTIPLYING DAC

Figure 17 shows an alternative method of achieving bipolar output. The circuit operates with sign plus magnitude code and has the advantage that it gives 10-bit resolution in each quadrant. The 10 magnitude bits provide digitally controlled

Figure 17. 10-Bit and Sign Multiplying DAC

attenuation of the reference while the sign bit provides polarity control. The AD7512 is a fully protected CMOS change-over switch. Mismatch between R4 and R5 introduces a gain error. Table III shows the Code Table for the circuit of Figure 17.

| Sign Bit | Binary Numbers in<br>DAC Register | Analog Output                           |

|----------|-----------------------------------|-----------------------------------------|

| 0        | 11 1111 1111                      | +V <sub>IN</sub> · 1 - 2 <sup>-10</sup> |

| 0        | 00 0000 0000                      | 0 Volts                                 |

| 1        | 00 0000 0000                      | 0 Volts                                 |

| 1        | 11 1111 1111                      | $V_{IN} \cdot 1 - 2^{-10}$              |

Table III. 10-Bit Plus Sign Magnitude Table

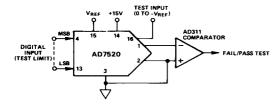

#### DIGITALLY PROGRAMMABLE LIMIT DETECTOR

Figure 18. Programmable Limit Detector

The circuit of Figure 18 shows how the AD7520 is used to implement a programmable limit detector. If the test input does not meet the test limit set by the digital input, then the pass/fail output will indicate a fail.

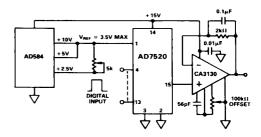

#### **VOLTAGE MODE OPERATION**

The AD7520 can also be used in the voltage-switching mode and the circuit of Figure 19 shows how the DAC can be connected for voltage switching by reversing the roles of the reference input and I<sub>OUT1</sub>. It is a single supply application with the DAC and the CMOS operational amplifier both powered from a single +15V supply. With a single supply operational amplifier, offset is difficult to remove completely; therefore, some offset may have to be tolerated usually amounting to less than one-half LSB at 3.5V reference. The voltage switching mode permits only a single polarity of input (positive with respect to common).

Figure 19. Single Supply Voltage Mode Operation

#### ANALOG/DIGITAL DIVISION

With the AD7520 connected in its normal multiplying configuration as shown in Figure 15, the transfer function is

$$V_0 = -V_{1N} \left( \frac{A_1}{2^1} + \frac{A_2}{2^2} + \frac{A_3}{2^3} + \cdots + \frac{A_n}{2^n} \right)$$

where the coefficients A<sub>X</sub> assume a value of 1 for an ON bit and 0 for an OFF bit.

By connecting the DAC in the feedback of an operational amplifier, as shown in Figure 20, the transfer function becomes

$$V_0 = \left(\frac{-V_{IN}}{\frac{A_1}{2^1} + \frac{A_2}{2^2} + \frac{A_3}{2^3} + \cdots + \frac{A_n}{2^n}}\right)$$

This is division of an analog variable  $(V_{1N})$  by a digital word. With all bits off, the amplifier saturates to its bound, since division by zero isn't defined. With the LSB (Bit 10) ON, the gain is 1024. With all bits ON, the gain is 1 ( $\pm$ 1 LSB).

Figure 20. Analog/Digital Divider

#### VOL. I, 9-160 DIGITAL-TO-ANALOG CONVERTERS