# Hybrid Video Low Glitch D/A Converter

# **HDD Series**

# **FEATURES**

Ultra Fast 10ns Settling Time to 0.2% (HDD-0810) 15ns Settling Time to 0.1% (HDD-1015)

Internal Monolithic Reference

Low 200pV-sec Glitch Energy

Single -5.2V Power Supply

Available Screened to MIL-STD-883

Designed for General Output Compatibility with EIA

Standards RS-170 and RS-343, including 10% Brightness

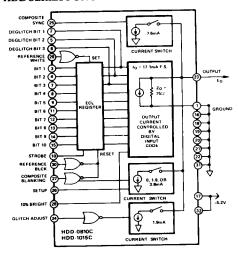

Complete Composite Inputs (HDD-0810C, HDD-1015C)

# **APPLICATIONS**

Raster Scan and Vector Graphic Displays

TV Video Reconstruction

Ultra Fast Current or Voltage Output DAC for Use in

Analytical Instrumentation

Digital VCOs

# GENERAL DESCRIPTION

The HDD-0810 and HDD-1015 combine state-of-the-art technology with the latest active laser trimming techniques to achieve the world's fastest 8- and 10-bit voltage output digital-to-analog converters of their type.

Containing input registers and an ultra stable monolithic internal reference, the HDD-0810 8-bit D/A converter settles to within 0.2% in 10ns, while the 10-bit version HDD-1015 settles to within 0.1% in only 15ns. They are compatible with standard ECL logic levels. The  $75\Omega$  output impedance allows them to drive  $75\Omega$  cables or filters directly, without costly external output drivers. This feature assures that a full one volt is available at the load, since the D/A output is a minimum of 27mA (HDD-1015). Additionally, these D/As are monotonic over the full operating temperature range of  $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (metal case versions), or 0 to  $+70^{\circ}\text{C}$  for the commercial style glass-ceramic package, and require only a single -5.2V supply for operation.

The HDD-0810C and HDD-1015C combine all of the above features with full composite input capability, which allows operation directly with raster scan/output video display systems. These controls include Composite Sync, Blanking, Setup and a 10% Brightness input which gives the user digital control of the picture's intensity. Further, the HDD Series D/A converters contain provisions for external adjustments to optimize differential phase and gain, critical considerations in composite color video applications.

# HDD SERIES FUNCTIONAL BLOCK DIAGRAM

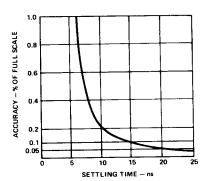

TIME IS MEASURED FROM 50% TRANSITION POINT OF THE STROBE WITH INPUT DATA LINES DESKEWED AND 75 $\Omega$  LOAD. VOLTAGE OUTPUT. IMHERENT DELAY OF INTERNAL REGISTER (3ns) HAS BEEN DISREGARDED.

HDD Series D/A Converters Accuracy vs. Settling Time

DIGITAL-TO-ANALOG CONVERTERS VOL. I, 9-295

SPECIFICATIONS (typical @ +25°C with nominal power supplies and 75Ω output load unless otherwise noted)

| MODEL                               | UNITS        | HDD-0810                                | HDD-0810C                               | HDD-1015     | HDD-1015C                             |

|-------------------------------------|--------------|-----------------------------------------|-----------------------------------------|--------------|---------------------------------------|

| RESOLUTION FS = FULL SCALE          | Bits         | 8                                       | 8                                       | 10           | 10                                    |

| LSB WEIGHT (Current)                | μΑ           | 106                                     | 67                                      | 27           | 17                                    |

| SB WEIGHT (Voltage)                 | mV           | 4                                       | 2.5                                     | 1            | 0.625                                 |

| ACCURACY <sup>1</sup>               | ±% of FS     | 0.1                                     |                                         | 0.05         |                                       |

|                                     | ±% of GS     | 0.1                                     | 0.1                                     | 0.03         | 0.05                                  |

| Linearity                           | ±μΑ          | 26.5                                    | 17                                      | 13           | 8.5                                   |

| Monotonicity                        |              | Guaranteed                              | •                                       | •            | •                                     |

| Zero Offset (Initial)               | mV           | -1.4                                    | •                                       | •            | •                                     |

| TEMPERATURE COEFFICIENTS            |              |                                         | · · · · · · · · · · · · · · · · · · ·   |              |                                       |

| Linearity                           | ppm/°C       | 5                                       | •                                       | •            | •                                     |

| Zero Offset                         | ppm/°C       | 1                                       | •                                       | •            | •                                     |

| Gain                                | ppm/°C       | 80                                      | •                                       | •            | •                                     |

| STROBE INPUT                        | ppi C        |                                         |                                         |              |                                       |

| Logic Compatibility                 |              | ECL                                     | •                                       |              | •                                     |

| Logic Voltage Levels "1" =          | v            | -0.9                                    | •                                       | •            | •                                     |

| (Positive Logic) "0" =              | v            | -1.7                                    | •                                       | •            | •                                     |

| Logic Loading                       | •            | 50pF and 5kΩ                            |                                         |              |                                       |

| But arting                          |              | to -5.2V                                | •                                       | •            | •                                     |

| Set-Up Time (Data)                  | ns           | 2.5 min                                 | •                                       | •            | •                                     |

| Hold Time (Data)                    | ns           | 1.5 min                                 | •                                       | •            | •                                     |

| Propagation Delay                   | ns           | 3                                       | •                                       | •            | •                                     |

|                                     |              | <del></del>                             | <del></del>                             |              | · · · · · · · · · · · · · · · · · · · |

| REFERENCE BLACK AND                 |              | 0 11 6                                  | _                                       | _            |                                       |

| REFERENCE WHITE INPUTS <sup>2</sup> |              | See Note 2                              | •                                       | •            | •                                     |

| Logic Compatibility                 | `            | ECL                                     | •                                       | •            | •                                     |

| Logic Voltage Levels "1" = "0" =    | v            | -0.9                                    |                                         | •            | •                                     |

| -                                   | V            | -1.7                                    | 5.5.1501.0                              | *            |                                       |

| Logic Loading                       |              | 50pF and 5kΩ<br>to -5.2V                | 5pF and 50kΩ                            | 50pF and 5kΩ | 5pF and 50kΩ                          |

|                                     |              | 10 -3 2V                                |                                         |              |                                       |

| DATA INPUTS                         |              |                                         |                                         |              |                                       |

| Logic Compatibility                 |              | ECL                                     | •                                       | •            | •                                     |

| Logic Voltage Levels "1" =          | v            | -0.9                                    | •                                       | •            | •                                     |

| (Positive Logic) "0" =              | v            | -1.7                                    | •                                       | •            | •                                     |

| Logic Loading                       |              | 5pF and 50kΩ                            | •                                       | •            | •                                     |

| (Each Bit)                          |              | to -5.2V                                |                                         |              |                                       |

| Coding (See Table)                  |              | Complementary Binary                    | _                                       |              | _                                     |

|                                     |              | (CBN)                                   |                                         |              |                                       |

| COMPOSITE SYNC INPUT                |              |                                         |                                         |              |                                       |

| Logic Compatibility                 |              | N/A                                     | ECL                                     | N/A          | ECL                                   |

| Logic Voltage Levels "1" =          | V            | N/A                                     | -0.9                                    | N/A          | -0.9                                  |

| "0" =                               | v            | N/A                                     | -1.7                                    | N/A          | -1.7                                  |

| Logic Loading for Logic "1"         |              | N/A                                     | 5pF, +7.6mA                             | N/A          | 5pF, +7.6mA                           |

| Logic "0"                           |              | N/A                                     | 5pF, -50µA                              | N/A          | 5pF, -50μA                            |

| COMPOSITE BLANKING AND              |              |                                         |                                         |              |                                       |

| 10% BRIGHT INPUTS                   |              |                                         |                                         |              |                                       |

| Logic Compatibility                 |              | N/A                                     | ECL                                     | N/A          | ECL                                   |

| Logic Voltage Levels "1"            | v            | N/A                                     | -0.9                                    | N/A          | -0.9                                  |

| "0"                                 | v            | N/A                                     | -1.7                                    | N/A          | -1.7                                  |

| Logic Loading                       |              | NI/A                                    | 5pF and 50kΩ                            | 5114         | 5pF and 50kΩ                          |

| SETUP CONTROL                       |              | N/A                                     | to ~5.2V                                | N/A          | to -5.2V                              |

|                                     |              | 0 (0 IBE II-1-)                         | •                                       |              |                                       |

| Ground<br>Open                      | mV<br>mV     | 0 (0 IRE Units)                         | •                                       | •            | ·                                     |

| -5.2V                               | mV<br>mV     | 71 (10 IRE Units)<br>142 (20 IRE Units) | •                                       | •            | •                                     |

|                                     |              | 142 (20 IRE DING)                       |                                         |              | <del></del>                           |

| DUTPUT <sup>3</sup>                 |              |                                         |                                         |              |                                       |

| Current                             | mA           | 0 to -27.2                              | 0 to -17                                | 0 to -27.3   | 0 to -17.05                           |

| Voltage <sup>4</sup>                | V (±1%)      | 0 to -1.020                             | 0 to -0.6375                            | 0 to -1.023  | 0 to -0.639375                        |

| Compliance                          | V<br>O (+5%) | +1.1 to -1.1                            | •                                       |              | •                                     |

| Internal Impedance                  | Ω (±5%)      | 75                                      | · · · · · · · · · · · · · · · · · · ·   | -            | ·                                     |

| OUTPUT - COMPOSITE SYNC             |              |                                         |                                         |              |                                       |

| Current                             | mA (±5%)     | N/A                                     | 0 or -7.6                               | N/A          | 0 or -7.6                             |

| Voltage                             | mV (±5%)     | N/A                                     | 0 or -286                               | N/A          | 0 or -286                             |

| OUTPUT - 10% BRIGHT                 |              |                                         |                                         |              |                                       |

| Current                             | mA (±5%)     | N/A                                     | 0 or -1.9                               | N/A          | 0 or -1.9                             |

| Voltage                             | mV (±5%)     | N/A                                     | 0 or -71                                | N/A          | 0 or -7.1                             |

| OUTPUT - COMPOSITE                  |              |                                         | *************************************** |              |                                       |

| LANKING <sup>5</sup>                |              |                                         |                                         |              |                                       |

|                                     |              |                                         |                                         |              |                                       |

| Current                             | mA (±1%)     | N/A                                     | 0, -17.0, -18.9, or -20.8               | N/A          | 0, -17.05, -18.95, or -20.85          |

# VOL. I, 9-296 DIGITAL-TO-ANALOG CONVERTERS

| MODEL                                | UNITS        | HDD-0810             | HDD-0810C | HDD-1015 | HDD-1015C     |

|--------------------------------------|--------------|----------------------|-----------|----------|---------------|

| SPEED PERFORMANCE - FULL             |              |                      |           |          |               |

| SCALE OR GRAY SCALE OUTPUT           |              |                      |           |          |               |

| Settling Time (Voltage) <sup>6</sup> | ns (to % FS) | 10 (0.2)             |           | 15 (0.1) | 15 (0.1)      |

| Setting Time ( Totage)               | or (to % GS) |                      | 10 (0.2)  |          | 15 (0.1)      |

| Slew Rate                            | V/μs         | 200                  | •         |          |               |

| Update Rate?                         | MHz          | 100                  | 100       | 67 .     | 67            |

| Rise Time                            | ns           | 4                    | •         | -        | •             |

| Glitch Energy <sup>8</sup>           | pV-s         | 200                  | •         |          |               |

| SPEED PERFORMANCE -                  |              |                      |           |          |               |

| CONTROL INPUTS                       |              |                      |           |          |               |

| Settling Time to 10% of              |              |                      |           |          |               |

| Final Value for:                     |              |                      |           |          |               |

| Composite Sync                       | ns           | N/A                  | 10        | N/A      | 10            |

| Composite Blanking                   | ns           | N/A                  | 10        | N/A      | 10            |

| Reference White                      | ns           | N/A                  | 10        | N/A      | 10            |

| Reference Black                      | ns           | N/A                  | 10        | N/A      | 10            |

| 10% Bright                           | ns           | N/A                  | 10        | N/A      | 10            |

| POWER REQUIREMENTS                   |              |                      |           |          |               |

| -5 2V ±0.25V                         | mA           | 380                  | 390       | 450      | 450           |

| Power Supply Sensitivity             | %/%          | 0.04/1               | •         | •        | •             |

| Reference                            |              | Monolithic, Internal | •         | •        | *             |

| TEMPERATURE RANGE                    |              |                      |           |          |               |

|                                      | °C Casc      | 0 to +70             | •         | •        | •             |

| Operating, Glass Case                | °C Case      | -25 to +85           | •         | •        | •             |

| Operating, Metal Case ("M")          | °C           | -55 to +125          | •         | •        | •             |

| Storage                              |              | <u> </u>             |           |          | <del></del> : |

| MTBF <sup>9</sup>                    | hours        | >300,000             |           |          |               |

| Mean Time Between Failure            | nours        |                      |           | HY32     | c.            |

| PACKAGE OPTIONS <sup>10</sup>        |              | HY32A                |           | 11172    |               |

On models HDD-0810C, 1015C a logic "0" on Pin 30 Reference Black will produce all "1" code 0 volts output; a logic "0" on Pin 29 Reference White will produce all "0" code -1 volt output.

# ORDERING NOTE

1. To order devices with hermetically sealed metal cases, add "M" suffix to part number.

Example: HDD-0810CMB

# PIN DESIGNATIONS

| PIN | FUNCTION           |

|-----|--------------------|

| ,   | GROUND             |

|     | DEGLITCH BIT 1     |

|     | BIT 1 (MSB)        |

| 4   | BIT 2              |

|     | DEGLITCH BIT 2     |

| •   | DEGLITCH BIT 3     |

| 7   | 81T 3              |

|     | BIT 4              |

|     | ert 6              |

| 10  | STROSE             |

| 11  | BIT 6              |

| 12  | SIT 7              |

| 13  | B1T \$             |

| 14  | BIT 9              |

| 15  | BIT 10 (L\$8)      |

| 14  | GROUND             |

| 17  | -5.2V              |

| 18  | GROUND             |

| 19  | GROUND             |

| 20  | GROUND             |

| 21  | GROUND             |

| 22  | GROUND             |

| 23  | OUTPUT             |

| 24  | GLITCH ADJUST      |

| 25  | COMPOSITE SYNC     |

| 25  | SETUP              |

| 27  | COMPOSITE BLANKING |

| 28  | 10% BRIGHT         |

| 29  | REFERENCE WHITE    |

| >0  | REFERENCE BLACK    |

| 31  | GROUND             |

| 32  | -6.2V              |

DIGITAL-TO-ANALOG CONVERTERS VOL. I, 9-297

Accuracy is relative to full scale (FS) for binary versions, or relative to gray scale (GS) for Composite ("C") versions, and includes linearity.

\*Accuracy is relative to full scale (FS) for binary versions, or relative to gray scale (GS) for Composite ("C") versions, and includes linearity.

\*\*Reference White on models HDD-0810, -1015 a logic "1" on Pin 30 Reference Black will produce all "0" code 0 volts output; a logic "1" on Pin 29 Reference White will produce all "1" code -1 volt output.

Reference White will produce all "0" code -1 volt output.

3 The output is shown for full scale (FS) for binary versions, and for full gray scale (GS) for Composite ("C") versions.

4 The difference between the full-scale output of 637.5mV and 643mV shown elsewhere herein is due to the fact that we selected an LSB value of 2.5mV for ease of calibration. These differences are well within the output and EIA standard RS-170 colerances.

5 The three currents and voltages correspond to the three set-up levels of 0, 10, and 20 IRE units as externally selected.

6 Worst case settling time includes FS and most significant bit (MSB) transitions. The inherent 3ns proposition delay through the input registers (50% point of Strobe to 50% point of register output) has been disregarded. Settling time to a percentage of FS is given for straight versions, and settling time to a percentage of maximum gray scale (GS) is given for composite video output ("C") versions. The update rates shown are limited by a full scale settling time that is useable for the number of bits of resolution. Both DACs may be operated up to 125MHz with settling time degradation. This is the limit of the logic switching speed.

8 Reducible to less than 100pV-s with appropriate deskewing of digital inputs. See Applications Section.

9 Calculated for HDD-1015CMB using MIL Handbook 217. Ground: Fixed Temperature Case = 60°C.

<sup>&</sup>lt;sup>9</sup>Calculated for HDD-1015CMB using MIL Handbook 217. Ground: Fixed Temperature Case = 60°C.

<sup>&</sup>lt;sup>10</sup> See Section 19 for package outline information.

<sup>\*</sup>Specifications same as for HDD-0810. Specifications subject to change without notice.

# APPLICATIONS INFORMATION

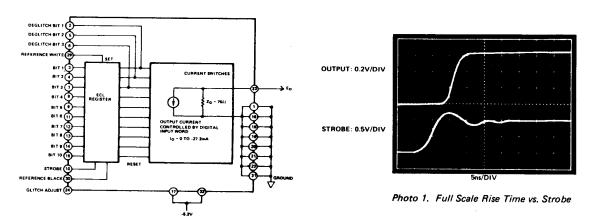

HIGH-SPEED LOW-GLITCH OPERATION SUGGESTIONS

The HDD Series D/As offer the highest available speed. However, with this speed performance, certain precautions and operation conditions should be considered.

- The D/A converter should be provided with a very low impedance grounding system to very high frequencies. A large ground plane is a must.

- Low frequency bypassing should be provided with a 1μF

(or larger) tantalum capacitor mounted between the -5.2V

supply line and ground near the D/A.

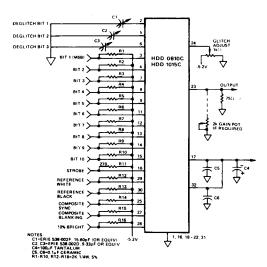

- 3. High frequency bypassing should be provided by ceramic capacitors of 0.1µF or larger mounted within 0.25 inches of Pins 17 and 32 to ground (see Figure 1).

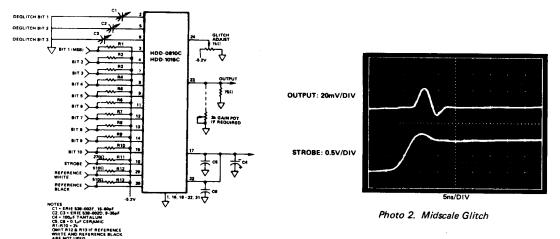

- 4. The threshold of the internal current switches can be optimized for low glitch energy by the addition of an external potentiometer connected to Pin 24 of the D/A (see Figure 1). This potentiometer is adjusted for minimum glitch energy as shown in Photo 2.

If required, variable capacitors can be added to "deskew" the most significant bits for lowest glitch—although this is not usually required in many applications. These capacitors are added as shown in Figure 1 (C1-3). They are adjusted in conjunction with the glitch adjust pot for minimum glitch energy as shown in Photo 2.

In composite television applications, C1-3 are adjusted for best differential phase performance, and the glitch adjust is adjusted for best differential gain performance. These may tend to interact, so going back and forth between adjustments may be required.

5. Standard 32-pin sockets should be avoided. Individual "pin sockets" are most suited for evaluating devices, as lead inductance is reduced. In final designs, the D/As should be soldered directly into the printed circuit board without sockets.

# **GAIN ADJUSTMENT**

The HDD Series D/As are actively laser-trimmed to provide a voltage into exactly  $75\Omega$  which is an even binary multiple; i.e., the HDD-0810 has an LSB of 4mV and the HDD-1015 has an LSB of 1mV. This makes the full-scale output slightly greater than one volt. If an output of exactly one volt is required—such as for TV reconstruction—a 2k potentiometer may be placed across the output of the D/A for gain adjustment. For a one volt output, the adjusted value of this pot will be about  $1500\Omega$  (see Figures 1 and 5).

Figure 1. HDD-0810, HDD-1015C Typical Hook-Up Circuit

# **ULTRA-LOW GLITCH OPERATION**

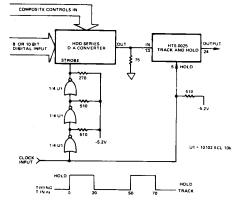

For extremely low glitch requirements (<50 - 100pV-s), an HTS-0025 Track-and-Hold is recommended as a deglitcher (see Figure 2). The duration of the HDD Series D/A glitch is approximately 10ns. The hold time of the HTS-0025 should be at least 15ns to "mask out" the glitch. The minimum acquisition time of the HTS-0025 for 0.1% accuracy is 30ns. This implies that the circuit of Figure 2 can be operated up to 22MHz and still maintain 10-bit accuracy. For 0.2% accuracy, the acquisition time for the T&H can be reduced to 25ns, allowing the circuit to operate to 25MHz. This discussion assumes that the D/A will be required to slew full scale (one volt) between adjacent samples. In practice, the sample-to-sample variation is less than full scale depending on the amount of oversampling. In a practical situation, therefore, 10-bit accuracy should be achievable at 25MHz update rates.

Figure 2. HTS-0025 Track and Hold Used as a Deglitcher (Update  $\approx 20MHz$ )

# HDD-0810C/HDD-1015C

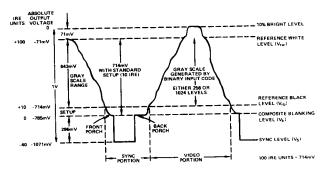

# CHARACTERISTICS OF HDD-1015C [0810C] VIDEO DACS

# COMPOSITE VIDEO SIGNAL

1024 [256] gray levels plus blanking and sync levels

#### STEP SIZE

0.625mV [2.5mV]

# GRAY SCALE RANGE

0.643V Peak to Peak

# SETUP CONTROL

User programmable in three levels

|                   | mV  | IRE Units |

|-------------------|-----|-----------|

| 1. Input Grounded | 0   | 0         |

| 2. Input Open     | 71  | 10        |

| 3. Input @ -5.2V  | 142 | 20        |

# REFERENCE WHITE LEVEL

0V Absolute

100 IRE Units (+0.714V relative to blanking level with standard setup; +0.643V relative to Reference Black)

# DIGITAL INPUT FOR WHITE LEVEL

All ones (1111111111)

# REFERENCE WHITE/BLACK CONTROLS1

Overrides Video Input Word

A logic 0 on Pin 30 (reference Black) will drive the output to reference black level of -643mV.

A logic 0 on Pin 29 (Reference White) will drive the output to reference white level of 0 volts absolute.

# REFERENCE BLACK LEVEL

-0.643V Absolute; +71mV (10 IRE Units) Relative to blanking level with standard setup.

DIGITAL INPUT FOR REFERENCE BLACK All zeroes (0000000000)

# COMPOSITE BLANKING LEVEL

-0.714V Absolute, (0 IRE Units) with standard setup.

# COMPOSITE BLANKING INPUT - PIN 271

Logic 0 on Pin 27 resets input register to 0000000000, and causes output voltage to go negative by the amount of setup voltage with respect to the all "0" output voltage.

# COMPOSITE SYNC LEVEL

-1.0V Absolute with standard setup.

-0.286V (-40 IRE Units) relative to blanking level (Back Porch).

# COMPOSITE SYNC INPUT - PIN 25

Logic 0 resets input register to 0000000000, and the output voltage goes negative by 0.286V.

# 10% BRIGHT - PIN 28

Logic "0" causes output voltage to go positive by 71mV.

# STROBE - PIN 10

Logic "0" to Logic "1" transition clocks input register.

# DEFINITION OF VIDEO TERMS

# BLANKING LEVEL

The level separating the SYNC portion from the Video portion of the waveform. Usually referred to as the Front Porch of Back Porch. At 0 IRE Units, it is the level which will shut off the picture tube, resulting in the blackest possible picture.

# COLOR VIDEO (RGB)

This usually refers to the technique of combining the three primary colors of Red, Green, and Blue to produce color pictures within the usual spectrum. In RGB monitors, three HDD "C" Series DACs would be required, one for each color.

# COMPOSITE SYNC SIGNAL (SYNC)

The position of the composite video signal which synchronizes the scanning process.

# COMPOSITE VIDEO SIGNAL

The video signal with or without setup, plus the composite SYNC signal.

# GRAY SCALE

The discrete levels of video signal between Reference Black and Reference White levels. A 10-bit DAC contains 1,024 different levels, while an 8-bit DAC contains 256.

# RASTER SCAN

The most basic method of sweeping a CRT one line at a time to generate and display images. This method is used in commercial television in the USA.

# REFERENCE BLACK LEVEL

The maximum negative polarity amplitude of the video signal.

# REFERENCE WHITE LEVEL

The maximum positive polarity amplitude of the video

# SETUP

The difference between the Reference Black level and the blanking level. This should not be confused with setup as used with digital logic.

# SYNC LEVEL

The peak level of the composite SYNC signal.

That portion of the composite video signal which varies in gray scale levels between Reference White and Reference Black. Also referred to as the picture signal, this is the portion which may be visually observed.

Reference White (Pin 29) should not be activated at the same time as composite blanking (Pin 27) or Reference Black (Pin 30).

Figure 3. HDD-0810C, HDD-1015C Output Waveforms

DIGITAL-TO-ANALOG CONVERTERS VOL. 1, 9-299

Figure 4. HDD-0810; HDD-1015 Block Diagram

Figure 5. HDD-0810, HDD-1015 Typical Hook-Up Circuit

HDD-0810C, HDD-1015C Output Waveform

| Digital Input | HDD-0810 | HDD-0810C | HDD-1015 | HDD-1015C  |

|---------------|----------|-----------|----------|------------|

| 111 111       | 0        | 0         | 0        | 0          |

| 111 110       | -4mV     | -2.5mV    | -1mV     | -0.625mV   |

| 110 000       | -252mV   | -157.5mV  | -255mV   | -159.375mV |

| 101 111       | -256mV   | -160mV    | -256mV   | -160mV     |

| 100 111       | -508mV   | -317.5mV  | -511mV   | -319.375mV |

| 011 111       | -512mV   | -320mV    | -512mV   | -320mV     |

| 010 000       | -764mV   | -477.5mV  | -767mV   | -479.375mV |

| 001 , 111     | -768mV   | -480mV    | -768mV   | -480mV     |

| 000 , 001     | -1016mV  | -635mV    | -1022mV  | -638.75mV  |

| 000 000       | -1020mV  | -637.5mV  | -1023mV  | -639.375mV |

ANALOG OUTDUT WITH 740 LOAD

Coding Table

# VOL. I, 9-300 DIGITAL-TO-ANALOG CONVERTERS