# CMOS 12-Bit Plus Sign Monolithic A/D Converter

AD7552

FEATURES

12-Bit Binary with Polarity and Overrange

Accuracy ± 1LSB

Microprocessor Compatible

Ratiometric Operation

Low Power Dissipation

#### GENERAL DESCRIPTION

**Low Cost**

The AD7552 is a 12-bit plus sign and overrange monolithic CMOS analog to digital converter. The "Quad Slope" conversion algorithm (Analog Devices patent No. 3872466) converts any offset voltages due to the integrator, comparator etc. to a digital number and subsequently reduces the total system drift error to a second order effect.

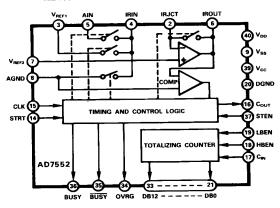

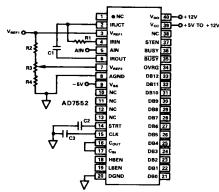

The AD7552 parallel output data lines have three-state logic and are microprocessor compatible. Separate enable lines control the lower eight LSBs (low byte enable) and the five MSBs (high byte enable). An overrange flag is also available which together with the BUSY and BUSY flags can be interrogated through the STATUS ENABLE providing easy microprocessor interface.

#### PACKAGE IDENTIFICATION<sup>1</sup>

Suffix "N" - Plastic DIP (N40A)

<sup>1</sup>See Section 19 for package outline information.

#### AD7552 FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- The output data (12-bits plus sign) may be directly accessed under control of two byte enable signals for a simple parallel bus interface. The overrange and converter busy signals are accessed by a status enable signal.

- The AD7552 conversion time is approximately 160ms with a 250kHz clock.

- Serial count out available for isolated A/D conversion via opto-isolators.

- A conversion start can be controlled by an externally applied signal or, with the addition of a capacitor, the converter can be made to self start.

- For most applications, the AD7552 needs only three resistors, one capacitor, and a reference voltage since the integrating amplifier, comparator, switches and digital logic are all on the CMOS chip.

## **SPECIFICATIONS** $(V_{DD} = +12V, V_{CC} = +5V, V_{SS} = -5V, V_{REF1} = +4.25V \text{ unless otherwise noted})^{\perp}$

| Parameter                                               | $T_A = +25^{\circ}C$                  | $T_A = 0 \text{ to } + 70^{\circ}\text{C}$ | Units                                 | Conditions/Comments                                                                                                      |

|---------------------------------------------------------|---------------------------------------|--------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                                |                                       |                                            |                                       |                                                                                                                          |

| Resolution                                              | 12-bits plus sign                     | 12-bits plus sign                          |                                       | Binary 2's complement coding                                                                                             |

| Accuracy of Reading (Including Noise)                   | ± 1                                   | ± 1                                        | Counts max                            |                                                                                                                          |

| , g(g)                                                  |                                       |                                            | Counts max                            | $f_{CLK} = 250 \text{kHz}, R1 = 1.8 \text{M}\Omega. C1 = 0.01 \mu\text{F}$<br>95% of conversions meet this specification |

| Noise (Flicker)                                         | ±1                                    | ±1                                         | Countra                               |                                                                                                                          |

|                                                         | ± 2                                   | ± 2                                        | Counts max Counts max                 | From nominal reading, not exceeded 95% of time                                                                           |

| ANIAL OC INTRUITO                                       |                                       | <u>- 2</u>                                 | Counts max                            | From nominal reading, not exceeded 99% of time                                                                           |

| ANALOG INPUTS                                           |                                       |                                            |                                       |                                                                                                                          |

| AIN (pin 5) Input Resistance <sup>2</sup>               | <b>R</b> 1                            | R1                                         | $M\Omega$ min                         | R1 is the external integrating resistor                                                                                  |

| V <sub>REF1</sub> (pin 3) Input Resistance <sup>2</sup> | Rl                                    | <b>R</b> 1                                 | $M\Omega$ min                         | connected between IROUT and IRJCT                                                                                        |

| V <sub>REF2</sub> (pin 7) Leakage Current               | 1                                     | 10                                         | nA typ                                | •                                                                                                                        |

| DIGITAL INPUTS                                          |                                       |                                            | · · · · · · · · · · · · · · · · · · · |                                                                                                                          |

| CIN (pin 17), HBEN (pin 18),                            |                                       |                                            |                                       |                                                                                                                          |

| LBEN (pin 19), STEN (pin 37)                            |                                       |                                            |                                       |                                                                                                                          |

| $V_{11}$                                                | +0.8                                  | + 0.8                                      | V max                                 | $V_{CC} = +5V$                                                                                                           |

| V <sub>IH</sub>                                         | + 2.4                                 | + 2.4                                      | V min                                 | V <sub>CC</sub> = +3V                                                                                                    |

| V <sub>II.</sub>                                        | + 1.2                                 | +1.2                                       | V max                                 | V 1331 (31 100) CT                                                                                                       |

| V <sub>IH</sub>                                         | + 10.8                                | + 10.8                                     | V min                                 | $V_{CC} = +12V \qquad (V_{II.} = 10\% \text{ of } V_{CC})$                                                               |

| $I_{IL}$ , $I_{IH}$                                     | 1                                     | + 10.8<br>l                                |                                       | $(V_{IH} = 90\% \text{ of } V_{CC})$                                                                                     |

| START (pin 14)                                          | 1                                     | 1                                          | μA max                                | $V_{CC} = +5V \text{ to } + 12V$                                                                                         |

| V <sub>II.</sub>                                        | +0.8                                  |                                            |                                       |                                                                                                                          |

|                                                         |                                       | + 0.8                                      | V max                                 | $V_{CC} = +5V \text{ to } V_{DD}$                                                                                        |

| V <sub>IH</sub>                                         | + 3.0                                 | + 3.0                                      | V min                                 |                                                                                                                          |

| I <sub>II</sub> .                                       | <b>− 5/ − 50</b>                      | <b>- 5</b> / <b>- 50</b>                   | μA typ/max                            | $V_{CC} = +5V \text{ to } V_{DD}, BUSY (pin 36) = V_{OL}$                                                                |

| I <sub>IH</sub>                                         | +0.5/+2.0                             | + 0.5/ + 2.0                               | mA typ/max                            | $V_{CC} = +5V \text{ to } V_{DD}, BUSY (pin 36) = V_{OH}$                                                                |

| CLOCK (pin 15)                                          |                                       |                                            |                                       | - ,                                                                                                                      |

| $\mathbf{v}_{\mathbf{n}}$                               | +0.8                                  | +0.8                                       | V max                                 | $V_{CC} = +5V$                                                                                                           |

| $\mathbf{v}_{iH}$                                       | + 3.0                                 | + 3.0                                      | V min                                 |                                                                                                                          |

| $V_{II.}$                                               | +1.2                                  | +1.2                                       | V max                                 | $V_{CC} = +12V$ $(V_{IL} = 10\% \text{ of } V_{CC})$                                                                     |

| $V_{IH}$                                                | + 10.8                                | + 10.8                                     | V min                                 | $(V_{IH} = 90\% \text{ of } V_{CC})$                                                                                     |

| $\mathbf{I}_{\mathbf{IL}}$                              | -0.1/-1.0                             | -0.1/-1.0                                  | mA typ/max                            | $V_{IN} = V_{IL}; V_{CC} = +5V \text{ to } +12V$                                                                         |

| I <sub>IH</sub>                                         | +0.1/+1.0                             | +0.1/+1.0                                  | mA typ/max                            | $V_{IN} = V_{IH}, V_{CC} = +5V \text{ to } +12V$                                                                         |

| DIGITAL OUTPUTS                                         | · · · · · · · · · · · · · · · · · · · |                                            |                                       | 11N 11H3 1 CC 1 3 1 CO 1 12 V                                                                                            |

| C <sub>OUT</sub> (pin 16), OVRG (pin 34)                |                                       |                                            |                                       |                                                                                                                          |

| BUSY(pin 35), BUSY (pin 36) and                         |                                       |                                            |                                       |                                                                                                                          |

| DB0-DB12(pins 21-33)                                    |                                       |                                            |                                       |                                                                                                                          |

|                                                         |                                       |                                            |                                       |                                                                                                                          |

| V <sub>OL</sub><br>V <sub>OH</sub>                      | + 0.8                                 | + 0.8                                      | V max                                 | $V_{CC} = +5V, I_{SINK} = 1.6mA$                                                                                         |

|                                                         | +4.0                                  | +4.0                                       | V min                                 | $V_{CC} = +5V$ , $I_{SOURCE} = 40\mu A$                                                                                  |

| Voi.                                                    | + 1.2                                 | + 1.2                                      | V max                                 | $V_{CC} = +12V, I_{SINK} = 1.6mA$                                                                                        |

| V <sub>OH</sub>                                         | + 10.8                                | + 10.8                                     | V min                                 | $V_{CC} = +12V$ , $I_{SOURCE} = 0.6mA$                                                                                   |

| Capacitance per Pin <sup>3</sup>                        | 5                                     | 5                                          | pF typ                                | Outputs in high impedance state                                                                                          |

| Leakage per Pin                                         | 1                                     | 1                                          | μA max                                | Outputs in high impedance state                                                                                          |

| DYNAMIC PERFORMANCE                                     | <del></del>                           |                                            |                                       |                                                                                                                          |

| Conversion Time                                         | 160                                   | 160                                        | me tun                                | P1 - 1 9MO C1 0 01 F 6                                                                                                   |

| Propagation Delays <sup>3</sup>                         | 100                                   | 100                                        | ms typ                                | $R1 = 1.8M\Omega$ , $C1 = 0.01\mu$ F, $f_{CLK} = 250kHz$                                                                 |

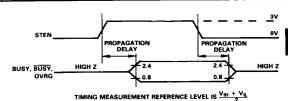

| STEN to BUSY, BUSY, or OVRG                             | 400                                   | 700                                        |                                       | m                                                                                                                        |

| 012/102001,2001,0104Rd                                  | 400                                   | 700                                        | ns max                                | Typically 250ns at +25°C (see next page)                                                                                 |

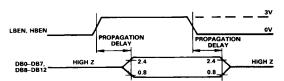

| LBEN to DB0-DB7                                         | 200                                   | £00                                        |                                       | Flag load = 20pF                                                                                                         |

| LBEN (0 DBO-DB/                                         | 300                                   | 500                                        | ns max                                | Typically 160ns at + 25°C (see next page)                                                                                |

| HDEN. DRG DRG                                           |                                       |                                            |                                       | DB0-DB7 load = 20pF                                                                                                      |

| HBEN to DB8-DB12                                        | 300                                   | 500                                        | ns max                                | Typically 160ns at + 25°C (see next page)                                                                                |

| 000000000000000000000000000000000000000                 |                                       |                                            |                                       | DB8-DB12 load = 20pF                                                                                                     |

| STRT Pulse Width                                        | 300                                   | 500                                        | ns min                                | Typically 220ns at + 25°C                                                                                                |

|                                                         |                                       |                                            |                                       | $V_{IN}(STRT) = 0 \text{ to } + 3V$                                                                                      |

| POWER SUPPLIES                                          |                                       |                                            |                                       |                                                                                                                          |

| $V_{DD}$                                                | + 10/ + 12                            | + 10/ + 12                                 | V min/mar                             |                                                                                                                          |

| V <sub>SS</sub>                                         | - 5/ - 12                             | -5/12                                      | V min/max                             |                                                                                                                          |

| V <sub>CC</sub>                                         |                                       |                                            | V min/max                             |                                                                                                                          |

| I <sub>DD</sub>                                         | + 5/V <sub>DD</sub>                   | + 5/V <sub>DD</sub>                        | V min/max                             |                                                                                                                          |

| I <sub>SS</sub>                                         | 0.8/2                                 | 0.8/2                                      | mA typ/max                            | STRT (pin 14) held HIGH,                                                                                                 |

|                                                         | 0.3/2                                 | 0.3/2                                      | mA typ/max                            | digital outputs floating.                                                                                                |

| $I_{CC}$                                                | 0.1/1<br>0.5/2                        | 0.1/1<br>0.5/2                             | mA typ/max                            | $V_{CC} = +5V$                                                                                                           |

|                                                         |                                       |                                            | mA typ/max                            | $V_{CC} = +12V$                                                                                                          |

#### VOL. I, 10-128 ANALOG-TO-DIGITAL CONVERTERS

Full scale voltage =  $\pm V_{REF1} + 2.125$ . For  $V_{REF1} = +4.25V$  FS voltage is  $\pm 2.00V$ . The equivalent input circuit is the integrator resistor R1 in series with a voltage source  $V_{REF2} = V_{REF}/I + 2$ , see Figure 1. Guaranteed but not tested.

Specifications subject to change without notice.

## ABSOLUTE MAXIMUM RATINGS\* (T<sub>A</sub> = + 25°C unless otherwise noted)

| V <sub>DD</sub> to | A  | GN | 1D | )  |   |  |  |  |  |  |  |  |   |  |   | 0V, + 14V           |

|--------------------|----|----|----|----|---|--|--|--|--|--|--|--|---|--|---|---------------------|

| V <sub>DD</sub> to | D  | G١ | ١Ľ | )  |   |  |  |  |  |  |  |  |   |  |   | 0V, +14V            |

| Vss to             | AG | N  | D  |    |   |  |  |  |  |  |  |  |   |  |   | 0V, -14V            |

| V <sub>SS</sub> to | DO | ŝΝ | D  |    |   |  |  |  |  |  |  |  |   |  |   | 0V, -14V            |

| AGND               | to | D  | Gl | NI | O |  |  |  |  |  |  |  |   |  |   | 0V, + 14V           |

| V <sub>CC</sub> to | D  | GN | ID |    |   |  |  |  |  |  |  |  |   |  |   | $V_{DD}$            |

| $V_{REF1}$         |    |    |    |    |   |  |  |  |  |  |  |  |   |  |   | $V_{SS}, V_{DD}$    |

| $V_{REF2}$         |    |    |    |    |   |  |  |  |  |  |  |  | ٠ |  | A | $GND, V_{DD}$       |

| AIN .              |    |    |    |    |   |  |  |  |  |  |  |  |   |  |   | $V_{SS}$ , $V_{DD}$ |

| TTOTAL             |    |    |    |    |   |  |  |  |  |  |  |  |   |  |   | Voc Von             |

| IROUT $V_{SS}$ , $V_{DD}$                     |

|-----------------------------------------------|

| Digital Input Voltage                         |

| HBEN, LBEN, STEN, $C_{IN}$ DGND, (DGND + 27V) |

| CLK, START DGND, V <sub>DD</sub>              |

| Digital Output Voltage                        |

| DB0-DB12, OVRG, BUSY, BUSY, COUT DGND, VCC    |

| Operating Temperature Range 0 to +70°C        |

| Storage Temperature −65°C to +150°C           |

| Power Dissipation (Package)                   |

| Up to +50°C                                   |

| Derates above +50°C by 10mW/°C                |

| Lead Temperature (Soldering, 10secs) + 300°C  |

those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION:-

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The foam should be discharged to the destination socket before devices are removed.

#### ORDERING INFORMATION

| Price<br>Mode | 1 | Temperature Range | Package <sup>1</sup> |

|---------------|---|-------------------|----------------------|

|               |   |                   | Plastic - N40A       |

<sup>&</sup>lt;sup>1</sup>See Section 19 for package outline information.

#### PIN CONFIGURATION

STEN to BUSY, BUSY, or OVRG Propagation Delays

LBEN to DB0-DB7, HBEN to DB8-DB12 Propagation Delays

#### PIN FUNCTION DESCRIPTION

| PIN | MNEMONIC          | DESCRIPTION                                                                                                                                                                                                       |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC                | No Connection                                                                                                                                                                                                     |

| 2   | IRJCT             |                                                                                                                                                                                                                   |

| 3   | V <sub>REF1</sub> | IntegratoR JunCTion. Summing junction (negative input) of integrating amplifier.  Voltage REFerence Input (normally + 4.25 volts).                                                                                |

| 4   | IRIN              | IntegratoR INput. External integrating resistor R1 is connected between IRJCT and IRIN.                                                                                                                           |

| 5   | AIN               | Analog INput. Unknown analog input voltage to be measured. Full scale AIN equals V <sub>REF</sub> /2.125.                                                                                                         |

| 6   | IROUT             | Integrated Oldram Evergelian and input voitage to be measured. Full scale AIN equals V Rest 2.125.                                                                                                                |

| 7   | V <sub>REF2</sub> | IntegratoR OUTput. External integrating capacitor C1 is connected between IROUT and IRJCT. Voltage REFerence $\div$ 2 Input. $V_{REF2}$ is normally obtained by a potential divider circuit as shown in Figure 3. |

| 8   | AGND              | Analog GrouND                                                                                                                                                                                                     |

| 9   | V <sub>SS</sub>   | Negative Supply (-5V to -12V)                                                                                                                                                                                     |

| 10  | NC                | No Connection                                                                                                                                                                                                     |

|     | NC                | No Connection                                                                                                                                                                                                     |

| 12  | NC                | No Connection                                                                                                                                                                                                     |

| 13  | NC                | No Connection                                                                                                                                                                                                     |

| 14  | STRT              | STaRT Conversion. When STRT goes to a Logic "1", the AD7552's digital logic is set up                                                                                                                             |

|     |                   | and BUSY is latched "high". When STRT returns "low", conversion begins in synchronization                                                                                                                         |

|     |                   | with CLK. Reinitiating STRT during conversion causes a conversion restart. STRT can be                                                                                                                            |

|     |                   | driven from an external logic source or can be programmed for continuous conversion by con-                                                                                                                       |

|     |                   | necting an external capacitor between STRT and DGND. An externally applied STRT command                                                                                                                           |

|     |                   | must be a positive pulse of at least 300 nanoseconds to ensure proper set-up of the AD7552 internal logic                                                                                                         |

| 15  | CLK               | CLock Input. The CLK can be driven from external logic, or can be programmed for internal                                                                                                                         |

|     |                   | oscillation by connecting an external capacitor between CLK and DGND.                                                                                                                                             |

| 16  | COUT              | Count OUT provides a number (N) of gated clock pulses given by:                                                                                                                                                   |

|     |                   | $\mathbf{N} = \left[ \frac{\mathbf{AIN}}{\mathbf{V_{REF1}}} 2.125 + 1 \right] 4096$                                                                                                                               |

|     | _                 | <u>-</u>                                                                                                                                                                                                          |

| 17  | $C_{IN}$          | Count IN is the input to the output counter. 2's complement binary data appears on the DB0                                                                                                                        |

|     |                   | through DB12 output lines (if the HBEN and LBEN enable lines are "high") if COUT is                                                                                                                               |

| 10  | HDCM              | connected to C <sub>IN</sub> .                                                                                                                                                                                    |

| 18  | HBEN              | High Byte ENable is the three-state logic enable input for the DB8-DB12 data outputs. When                                                                                                                        |

|     |                   | HBEN is "low", the DB8-DB12 outputs are floating. When HBEN is "high," digital data                                                                                                                               |

| 10  | LBEN              | appears on the data lines.                                                                                                                                                                                        |

| 17  | LBEN              | Low Byte ENable is the three-state logic enable for DB0-DB7. When LBEN is "low,"                                                                                                                                  |

| 20  | DGND              | DB0-DB7 are floating. When "high," digital data appears on the data lines.                                                                                                                                        |

|     | DB0               | Digital GrouND is the ground return for all digital logic and the comparator.  Data Bit 0 (least significant bit)                                                                                                 |

|     | DB1               | Pata Bit O (teast significant bit)                                                                                                                                                                                |

|     | DB2               | <b>↑</b>                                                                                                                                                                                                          |

|     | DB3               |                                                                                                                                                                                                                   |

|     | DB4               |                                                                                                                                                                                                                   |

|     | DB5               |                                                                                                                                                                                                                   |

|     | DB6               | CODE: 2's Complement                                                                                                                                                                                              |

|     | DB7               | 2 - Companies                                                                                                                                                                                                     |

|     | DB8               |                                                                                                                                                                                                                   |

| 30  | DB9               |                                                                                                                                                                                                                   |

| 31  | DB10              | Ţ                                                                                                                                                                                                                 |

| 32  | DB11              | <b>▼</b>                                                                                                                                                                                                          |

| 33  | DB12              | Data Bit 12 (most significant bit)                                                                                                                                                                                |

| 34  | OVRG              | OVerRanGe indicates a Logic "1" if AIN exceeds plus or minus full scale by at least 1/2LSB.                                                                                                                       |

|     |                   | OVRG is a three-state output and floats until STEN is addressed with a Logic "1".                                                                                                                                 |

| 35  | BUSY              | Not BUSY. BUSY indicates whether conversion is complete or in progress. BUSY is a three-                                                                                                                          |

|     |                   | state output which floats until STEN is addressed with a Logic "1." When addressed.                                                                                                                               |

|     |                   | BUSY will indicate either a "1" (conversion complete) or a "0" (conversion in progress).                                                                                                                          |

| 36  | BUSY              | BUSY indicates conversion status. BUSY is three-state output which floats until STEN is                                                                                                                           |

|     |                   | addressed with a Logic "1." When addressed, BUSY indicates a "0" (conversion complete)                                                                                                                            |

|     |                   | or a "1" (conversion in progress).                                                                                                                                                                                |

| 37  | STEN              | STatus ENable is the three-state control input for BUSY, BUSY, and OVRG. When STEN is "high",                                                                                                                     |

|     |                   | the three outputs are enabled.                                                                                                                                                                                    |

|     | NC                | No Connection                                                                                                                                                                                                     |

| 39  | $v_{cc}$          | Logic Supply. Digital inputs and outputs are TTL compatible if $V_{CC} = +5V$ , CMOS                                                                                                                              |

| 40  | <b>T</b> 7        | compatible for $V_{CC} = +10V$ to $V_{DD}$ .                                                                                                                                                                      |

| 40  | $V_{DD}$          | Positive Supply + 10V to + 12V.                                                                                                                                                                                   |

#### VOL. I, 10-130 ANALOG-TO-DIGITAL CONVERTERS

### **Quad Slope Theory of Operation**

Component limitations such as switch leakage, as well as operational amplifier offset voltage and bias current (and the temperature dependency of these errors), are major obstacles when designing high resolution integrating A/D converters. The AD7552 utilizes a patented quad slope conversion technique (Analog Devices Patent No. 3872466) to reduce the effects of such errors to second order effects.

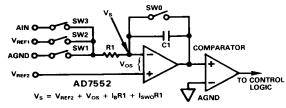

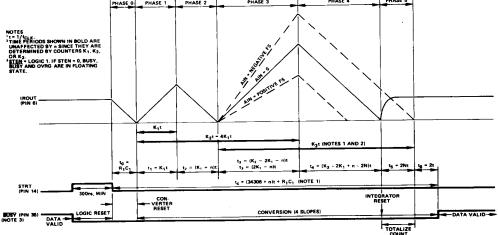

Figure 1 shows a simplified quad slope integrator circuit. The various inputs AGND (Analog Ground),  $V_{REF1}$ , and AIN (Analog Input) are applied in sequence to the integrator via switches 1-3 (see Table I), creating four slopes at the integrator output (phase 1-4 of Figure 2). If the equivalent summing junction voltage  $V_S$  is precisely 0.5 $V_{REF1}$ , the phase 1 and phase 2 integration times are equal, indicating there are no input errors. If  $V_S \neq 0.5V_{REF1}$  (due to amplifier offset voltage, bias current, etc.), an error count "n" is obtained. The analog input integration cycle (phase 3) is subsequently lengthened or shortened by "n" counts, depending on whether the error was positive or negative.

Figure 1. Simplified Quad Slope Integrator Circuit

| Phase            | Input Voltage                                                                                                                              | Integration Time                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4 | $\begin{array}{c} \text{AGND-V}_S \\ \text{V}_{\text{REF1}}\text{-V}_S \\ \text{AIN-V}_S \\ \text{V}_{\text{REF1}}\text{-V}_S \end{array}$ | $t_1 = K_1 t$ $t_2 = (K_1 + n)t$ $t_3 = (2K_1 - n)t$ $t_4 = (K_3 - 2K_1 + n - 2N)t$ |

Table I. Integrator Equivalent Input Voltages and Integration Times

where:

t = The CLK period

n = System error count

$K_1 = A$  fixed count equal to 4352 counts

$K_2 = A$  fixed count equal to 17408 counts ( $K_2 = 4K_1$ )

$K_3 = A$  fixed count equal to 25600 counts

N = Digital output count corresponding to the analog input voltage, AIN

The time  $t_5$  between the phase 4 zero crossing and the termination of counter  $K_3$  is considered equal to 2N counts. N, the number of counts at the  $C_{OUT}$  terminal, is obtained by a divide-by-two counter stage. This reduces "jitter" effect. Barring third (and higher) order effects, it can be proven that:

$$N = \left(\frac{\text{AIN}}{V_{\text{REF1}}} - 1\right) \cdot 2K_1 + \frac{K_3}{2} + \left(\frac{\text{AIN}}{V_{\text{REF1}}} - 1\right) \cdot \left[\frac{\text{AGND}}{V_{\text{REF1}}} (1 + 2\alpha) - \alpha^2\right] \cdot 2K_1$$

ideal term error term

where:

AGND = Voltage at AD7552 pin 8 (AGND) measured with respect to V<sub>REF1</sub> and AIN signal common ground. (Ideally, AGND = 0V)

$$\alpha$$

is an error term equal to  $\frac{2V_S - V_{REF1}}{V_{REF1}}$

Ideally  $\alpha = 0$  when  $V_S = 0.5V_{REF1}$ .

NOTE:

$V_S = V_{REF2} + V_{OS} + I_B R_1 + I_{SWO} R_1$

WHERE

$V_{REF2} = 0.5V_{REF1}$  if no error is present

V<sub>OS</sub> = Offset voltage of integrator amplifier

I<sub>B</sub> R1 = Equivalent integrator amplifier offset voltage due to bias current of integrator amplifier

I<sub>SWO</sub> R1 = Equivalent integrator amplifier offset voltage due to SW0 leakage current.

Figure 2. Quad Slope Timing Diagram

The ideal case assumes:

$$AGND = 0V$$

$$V_S = \frac{V_{REF1}}{2} \text{ , therefore } \alpha = 0$$

Then (EQN 1) simplifies to:

$$N = \frac{AIN}{V_{REF1}} \cdot 8704 + 4096$$

(EQN 2)

$$N = \frac{AIN}{FS} \cdot 4096 + 4096$$

(EQN 3)

FS = full scale input voltage =

$$\frac{V_{REF1}}{2.125}$$

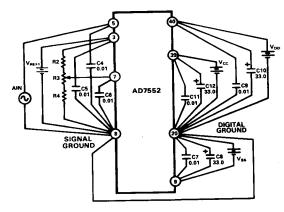

Equation 1 shows that only  $\alpha$  and AGND generate error terms. Errors due to  $\alpha \neq 0$  are strongly reduced because of the  $\alpha^2$  term in equation 1. Errors due to AGND #0 will, however, have a first order effect on the system performance. Great care should be taken in any circuit layout to minimize or eliminate ground loops between AGND and signal ground. A recommended grounding system is shown in Figure 5.

#### **OUTPUT CODING**

The parallel output (DB0-DB12) of the AD7552 represents the number N in binary 2's complement coding when the COUT pin is connected to the C<sub>IN</sub> pin (see Table II).

| Analog Input<br>(Note 1)      | N<br>(Note 2) |      |      | Parallel Digital Outp |      |      |  |  |  |  |

|-------------------------------|---------------|------|------|-----------------------|------|------|--|--|--|--|

|                               |               | OVRG | DB12 | DB11                  |      | DB0  |  |  |  |  |

| + Overrange                   | 8191          | 1    | 0    | 1111                  | 1111 | 1111 |  |  |  |  |

| +(FS-1LSB)                    | 8191          | 0    | 0    | 1111                  | 1111 | 1111 |  |  |  |  |

| + 1LSB                        | 4097          | 0    | 0    | 0000                  | 0000 | 0001 |  |  |  |  |

| 0                             | 4096          | 0    | 0    | 0000                  | 0000 | 0000 |  |  |  |  |

| - ILSB                        | 4095          | 0    | 1    | 1111                  | 1111 | 1111 |  |  |  |  |

| -(FS-1LSB)                    | 1             | 0    | 1    | 0000                  | 0000 | 0001 |  |  |  |  |

| - FS                          | 0             | 0    | 1    | 0000                  | 0000 | 0000 |  |  |  |  |

| <ul> <li>Overrange</li> </ul> | 0             | 1    | 1    | 0000                  | 0000 | 0000 |  |  |  |  |

NOTES:  ${}^{1}FS = \frac{V_{REF1}}{2.125}$ ; 1 Least Significant Bit (LSB) =  $FS(2^{-12})$

<sup>3</sup>C<sub>OUT</sub> strapped to C<sub>IN</sub>; LBEN and HBEN ≈ Logic 1

Table II. Output Coding (Bipolar 2's Complement)

#### ANALOG CIRCUIT SET-UP AND OPERATION

The following steps, in conjunction with the analog circuitry of Figure 3 explain the selection of the various component values required for proper operation.

#### 1. Determination of V<sub>REF1</sub>

The reference voltage V<sub>REF1</sub> and the full scale input voltage FS are related by

$$V_{REF1} = 2.125 (FS)$$

V<sub>REF1</sub> must be positive for proper operation. A typical value of V<sub>REF1</sub> is +4.25V. An AD584 may be used to provide the reference.

#### 2. Selection of Integrator Components R1 and C1

The integrator time constant should be approximately equal to

$$R1C1 \approx \frac{V_{REF1}(9 \times 10^3)}{f_{CLK}(V_{DD}-4V)}$$

The integrating capacitor C1 should be a low leakage, low dielectric absorption type such as Teflon, polystyrene or polypropylene. To minimize noise, the outside foil of C1 should be connected to the output of the integrating amplifier and not to its summing junction.

VOL. I, 10-132 ANALOG-TO-DIGITAL CONVERTERS

Figure 3. AD7552 Operational Diagram

Improper selection of the integrator time constant (time constant = R1 C1) may cause excessive noise due to the integrator output swing being too low, or may cause nonlinear operation if the integrator output attempts to exceed the rated output voltage of the amplifier.

#### 3. Determining Conversion Time

As shown in Figure 2, the conversion time is independent of the analog input voltage AIN, and is given by:

$$t_{CONVERT} = t_{STRT} + \frac{34306}{f_{CLK}} + R1 C1$$

t<sub>STRT</sub> = STRT pulse duration.

$R_1C_1$  = Integrator Time Constant.

f<sub>CLK</sub> = CLK Frequency at pin 15.

#### 4. External or Auto STRT Operation

The STRT pin can be driven externally, or with the addition of C2, made to self-start.

The value of C2 determines the length of time from end of conversion until a new conversion is initiated. This is the "data valid" time and is given by:

$$t_{DAV} \approx (1.17 \times 10^6 \Omega) \text{ C2} + 20 \mu \text{s}$$

When first applying power to the AD7552, a 0V to VDD positive pulse (power up restart) is required at the STRT terminal to initiate auto STRT operation. See APPLICATIONS HINTS No. 5.

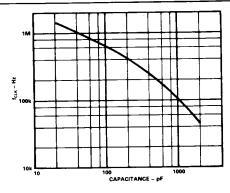

#### 5. Internal Clock Operation

The CLK input, pin 15, should normally be driven from an external crystal frequency source, particularly if operation above 250kHz is required. However, for noncritical applications an internal clock oscillator can be activated when a capacitor is connected from pin 15 to DGND. Figure 4 shows a typical curve of clock frequency versus capacitance, C3. Due to process variations the actual operating frequency for a given value of C3 can vary from device to device by up to 100%. Consequently it may be necessary to "tune" C3 to provide the correct clock frequency for a given V<sub>REF1</sub> and R1C1. For proper operation the clock frequency should be limited to 250kHz. Conversion speeds of up to 80ms can be obtained by increasing the clock frequency to 500kHz. However the flicker due to noise will also increase. See APPLICATIONS HINTS No. 8.

#### 6. Initial Calibration

Trim R3 (Figure 3) so that the voltage on pin 2 (IRICT) equals  $1/2V_{REF1} \pm 0.6\%$ . During this trim and measurement cycle apply a logic HIGH to pin 14 (STRT). This will prevent the AD7552 from executing a conversion.

## **Application Hints**

Figure 4. Internal Clock Frequency vs. C3

Figure 5. Recommended Grounding System

#### APPLICATIONS HINTS

- Decouple AIN (pin 5), V<sub>REF1</sub> (pin 3) and V<sub>REF2</sub> (pin 7) through 0.01µF to signal ground.

- Signal ground must be located as close to pin 8 (AGND) as possible.

- Keep the lead lengths of R1 and C1 toward pin 2 (IRJCT) as short as possible. In addition, both components should lie over the analog ground plane. If C1 has an outside foil, connect it to pin 6 (IROUT), not pin 2.

- 4. Hold the data bit enables (HBEN, LBEN) in the 0 state during conversion. This is easily accomplished by tying STEN to the 1 state and driving HBEN and LBEN with BUSY. This prevents the DB0 through DB12 outputs from coupling noise into the integrator during the phase 1-4 active integration periods.

- To avoid the requirement of providing a positive STRT pulse on power-up to initiate the auto start operation, the following circuit may be used.

The output of the open collector NAND gate is initially high on power-up. When the charging voltage on CS reaches the input threshold level of the NAND gate, the output goes low and remains low to allow the AD7552 to self start.

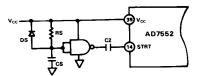

Under no circumstances should V<sub>CC</sub> exceed V<sub>DD</sub> especially during power-up and power-down. In cases where this situation could occur the following diode protection scheme is recommended.

- 7. Some solder fluxes and cleaning materials can form slightly conductive films which cause leakage effects across the integrating capacitor. The user is cautioned to ensure that the manufacturing process for circuits using the AD7552 does not allow such films to remain after assembly. Otherwise the accuracy and noise performance of the device will be affected.

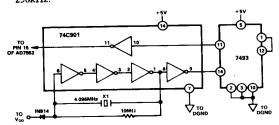

- A suggested crystal oscillator circuit is shown below for use with a V<sub>CC</sub> of +5V. It uses a standard 4.096MHz crystal which is divided down by 16 to produce a clock frequency of 256kHz.

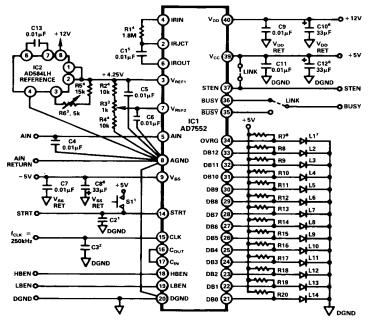

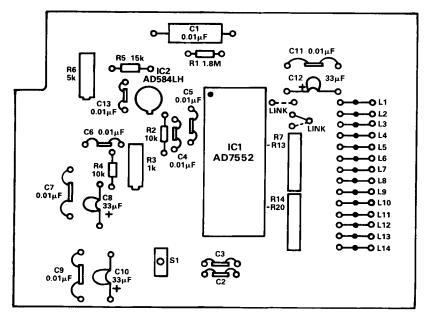

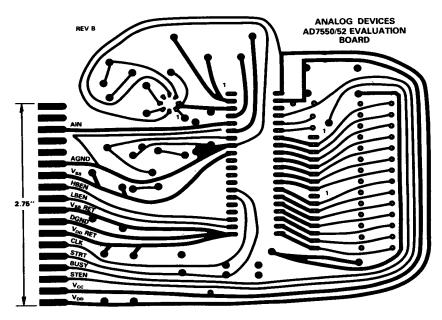

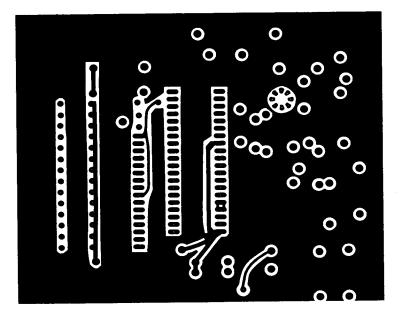

9. A printed circuit layout for an evaluation board is shown in Figure 8a and 8b. Figure 6 shows the circuit diagram for this evaluation board with component values for f<sub>CLK</sub> = 250kHz, V<sub>REF1</sub> = +4.25V operation. Figure 7 shows the component overlay for Figure 8a. Note that either BUSY (pin 35) or BUSY (pin 36) is available at the edge connector via a wire link. Note also that STEN (pin 37) may be tied high via a wire link.

NOTES:

1S1 IS A PUSHBUTTON SWITCH TO INITIATE AUTO-START

OPERATION. S1 AND C2 ARE NOT REQUIRED FOR EXTERNAL.

START OPERATION.

2G1S NOT REQUIRED FOR EXTERNAL CLOCK OPERATION.

2G1S NOT REQUIRED FOR EXTERNAL CLOCK OPERATION.

2G1S NOT REQUIRED FOR EXTERNAL STATISTICS.

2G1S NOT REQUIRED FOR EXTERNAL STATISTICS.

2G1S NOT REQUIRED FOR STATISTICS.

2G1S NOTES NOTE

\*C1 MUST BE A LOW LEAKAGE, LOW DIELECTRIC ABSORPTION

TYPE SUCH AS TEFLON, POLYSTYRENE OR POLYPROPYLENE.

\*C9. C10 AND C12 ARE SOLID ELECTROLYTE TANTULUM CAPACITORS.

\*L1 - L14 ARE LEDS, MONSANTO MVSS OR EQUIVALENT.

\*REPROPERTY OF THE SUCH AND AND PROPERTY OF THE SUCH AND AND PROPERTY OF THE SUCH AND PROPERTY OF THE SUCH AND AND PROPERTY OF THE SUCH AND PROPERTY OF THE

Figure 6. Evaluation Board Circuit with Component Values for  $f_{CLK} = 250kHz$ ,  $V_{REF1} = +4.25V$

Figure 7. Component Overlay for Figure 8a

#### VOL. I, 10-134 ANALOG-TO-DIGITAL CONVERTERS

Figure 8a. Component Side

Figure 8b. Foil Side

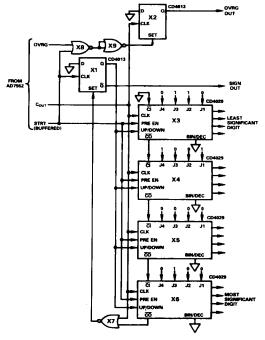

## OBTAINING SIGN-MAGNITUDE 4 DIGIT BCD CODING FROM THE AD7552

Referring to Figure 9 when a convert start pulse is received the four decade presettable up/down counter is loaded with the value 4096. The low level on the up/down count input (Q of X1 = 0) places the CD4029 counters into the count down mode. The contents of the four decade BCD counter are decremented each time a pulse is detected on  $C_{\rm OUT}$ . The number of pulses appearing on  $C_{\rm OUT}$  is related to both the magnitude and the polarity of the input voltage. If the counter reaches the all 0's state, the flip-flop (X1) is set, placing a high level signal on the up/down count input. The counter will now count up on succeeding  $C_{\rm OUT}$  pulses.

Figure 9. Sign-Magnitude BCD Conversion Circuitry

|                           |                | SIGN-MAGNITUDE BCD CODING <sup>1</sup> |      |         |         |         |         |  |  |  |  |  |  |  |

|---------------------------|----------------|----------------------------------------|------|---------|---------|---------|---------|--|--|--|--|--|--|--|

| Analog Input <sup>2</sup> | N <sup>3</sup> | OVRG                                   | Sign | Digit 4 | Digit 3 | Digit 2 | Digit 1 |  |  |  |  |  |  |  |

| + Overrange               | 8191           | 1                                      | 0    | 4       | 0       | 9       | 5       |  |  |  |  |  |  |  |

| +FS - 1LSB                | 8191           | 0                                      | 0    | 4       | 0       | 9       | 5       |  |  |  |  |  |  |  |

| + 1LSB                    | 4097           | 0                                      | 0    | 0       | 0       | 0       | i       |  |  |  |  |  |  |  |

| 0+                        | 4096           | 0                                      | 0    | 0       | 0       | Ô       | ō       |  |  |  |  |  |  |  |

| 0 –                       | 4096           | 0                                      | 1    | 0       | Ó       | 0       | 0       |  |  |  |  |  |  |  |

| - 1LSB                    | 4095           | 0                                      | 1    | 0       | 0       | ō       | i       |  |  |  |  |  |  |  |

| -(FS - 1LSB)              | 1              | 0                                      | 1    | 4       | Ó       | 9       | 5       |  |  |  |  |  |  |  |

| -FS                       | 0              | 1 1                                    | 1    | 4       | 0       | 9       | 6       |  |  |  |  |  |  |  |

| - Overrange               | 0              | 1                                      | 1    | 4       | 0       | 9       | 6       |  |  |  |  |  |  |  |

NOTES

Using circuit of Figure 9.

$^{2}$ FS =  $V_{REP1} \div 2.125$ ; 1 Least Significant Bit (LSB) = FS( $2^{-12}$ ).

<sup>3</sup>N = number of counts at C<sub>OUT</sub> pin.

Table III. Sign-Magnitude BCD Coding

Referring to Table III no counts occur on COUT when the input voltage is either overrange or equal to -FS. Since the most negative value which can be represented in sign-magnitude coding is -(FS - 1LSB) whereas in two's complement coding it is -FS, the X2 flip-flop of Figure 9 ensures that the OVRG output is high if either AIN is overrange or AIN = -FS. Note that there are two codes for zero analog input. This is the result of gating the carry out signal from X6 with the input clock signal C<sub>OUT</sub>. As mentioned previously, the number of counts at the C<sub>OUT</sub> terminal is obtained by an internal divide-by-two counter stage. Depending on whether the number of counts to this divide-by-two was odd or even COUT can remain in either a high or a low state at the end of phase 4. If AIN is negative and less than 1/2LSB (AIN =0-), C<sub>OUT</sub> is high after outputting 4096 counts thus preventing the sign flag from changing. If AIN is positive and less than 1/2LSB, COUT is low after outputting 4096 counts allowing the sign flag to change. If the carry out signal from X6 is directly connected back to X1, then the code for AIN = 0- vanishes leaving one code (the 0+one) for 0V.

This circuit may be used to provide direct readout of analog input voltage with proper scaling of the reference voltage and serial output  $C_{OUT}$ . For instance, dividing  $C_{OUT}$  by two and adjusting  $V_{REF1} = +4.352V$  gives a FS voltage of 2.048V which will be displayed directly.

|                           |      |      | SIGN-MAGNITUDE CODING <sup>1</sup> |      |      |     |     |     |     |     |     |     |     |     |     |

|---------------------------|------|------|------------------------------------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Analog Input <sup>2</sup> | N³   | OVRG | DB12                               | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DBi | DB0 |

| + Overrange               | 8191 | 1    | 0                                  | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |     |

| + FS - 1LSB               | 8191 | 0    | 0                                  | 1    | 1    | 1   | 1   | ı   | 1   | 1   | 1   | i   | 1   | ī   | i   |

| + 1LSB                    | 4097 | 0    | 0                                  | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | ō   | ō   | ō   | ī   |

| 0                         | 4096 | 0    | 0                                  | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | ō   | . 0 | ō   | ō   |

| - 1LSB                    | 4095 | 0    | 1                                  | 0    | 0    | 0   | 0   | 0   | 0   | Ô   | 0   | ō   | 0   | ō   | 1   |

| -(FS - 1LSB)              | 1    | 0    | 1                                  | 1    | 1    | l   | 1   | 1   | 1   | 1   | 1   | 1   | ī   | i   | i   |

| - FS                      | 0    | 1    | 1                                  | 0    | 0    | 0   | 0   | 0   | . 0 | Ô   | 0   | ō   | ō   | Ô   | ó   |

| – Overrange               |      | 1    | 1                                  | 0    | 0    | 0   | 0   | 0   | 0   | 0   | ō   | ō   | ō   | ŏ   | ŏ   |

NOTES

NOTES

Using circuit of Figure 10.

<sup>2</sup>FS = V<sub>REF1</sub> + 2.125; 1 Least Significant Bit (LSB) = FS (2<sup>-12</sup>).

$^3N$  = number of counts at  $C_{OLT}$  pin.

Table IV. Sign-Magnitude Binary Coding

#### VOL. I, 10-136 ANALOG-TO-DIGITAL CONVERTERS

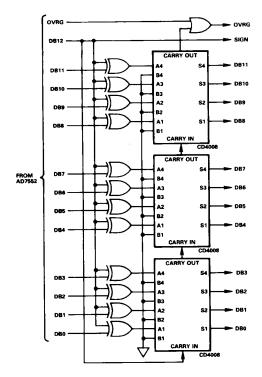

## OBTAINING SIGN-MAGNITUDE BINARY CODING FROM THE AD7552

The circuit of Figure 10 converts the two's complement coding from the AD7552 into sign-magnitude coding. It does this by complementing the AD7552 data and adding 1LSB whenever DB12 is high. In sign-magnitude coding the most negative value that can be represented is -(FS-1LSB); in two's complement coding it is -FS. The OR gate in Figure 10 ensures only valid output codes are produced (see Table IV). Note that there is only one code for zero scale.

Figure 10. Sign-Magnitude Binary Conversion Circuitry

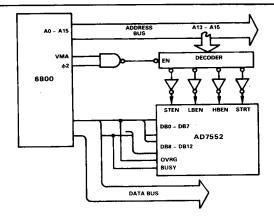

#### MICROPROCESSOR INTERFACING

The three-state output capability of the AD7552 allows the multiplexing of the data and status lines onto a single 8-bit wide bus. Figure 11 shows the AD7552 directly interfaced to the 6800 with convert start, data read, etc., all under program control. Note that the two status lines OVRG and BUSY are connected to the data bus in the MSB and LSB positions so that they can easily be interrogated by reading the status word to the microprocessor accumulator, rotating right or left through carry and then checking the carry flag.

Figure 11. AD7552-6800 Direct Interface

Care should be taken when using fast-access memory or operating at high temperatures to ensure that the AD7552 output drivers relinquish the data bus in time to avoid any possible bus conflict with the following instruction. In any situation where bus conflict is likely, the interfacing technique of Figure 12 is recommended.

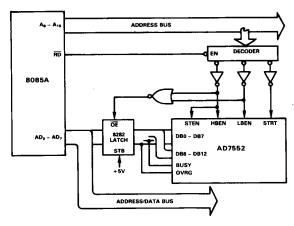

#### AD7552-8085A INTERFACE

Figure 12 shows the AD7552 interfaced to the 8085A. In this application the two status lines share the data bus with the data high byte (DB8-DB12) since the STEN and HBEN inputs are driven simultaneously from a single decoded address. The 8282 data latch which buffers the AD7552 three state drivers from the microprocessor bus ensures that the bus is relinquished promptly at the end of a data read instruction.

Figure 12. AD7552-8085A Direct Interface

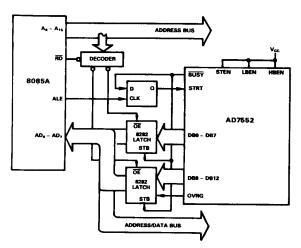

#### **CONTINUOUS CONVERSION MODE**

Figure 13 shows the AD7552 connected for continuous conversion. The conversion STRT signal is synchronized with the ALE signal of the 8085A. The BUSY signal is used to update the 8-bit data latches at a time when the microprocessor is not attempting a read operation. Thus the AD7552 appears to the microprocessor as memory which can be read at any time although scrambled data can result if a data update occurs between reading the high byte and low byte data. One method of avoiding this is to read data only after an update has occurred. The microprocessor can be interrupted to perform a data read by tying the AD7552 STRT input to one of the RST inputs on the 8085A.

#### OPTO-ISOLATED SERIAL INTERFACE

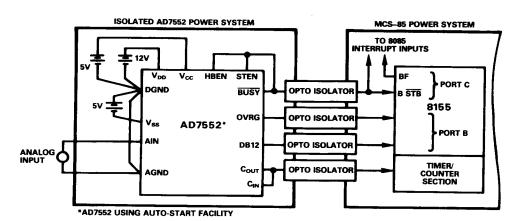

Figure 14 shows a serial interface to the MCS-85 system. This system can accommodate a remote interface where a common-mode voltage is expected to exist between system grounds.

Port C of the 8155 is configured as a control port. Port B is an input port. This port configuration is necessary if sign and/or overrange information is required. Magnitude information is obtained by interrogating the 8155 counter value. The rising edge of  $\overline{BUSY}$  is used to cause an interrupt on the RST 7.5 line. The value  $(2^{14} - C_{OUT})$  in the 8155 timer should now be read. When  $\overline{BUSY}$  returns low, the 8155 counter is reset to FF<sub>H</sub>. The falling edge of  $\overline{BUSY}$  also latches the sign and overrange data into port B. This is indicated by a rising edge on BF (buffer full) which can be used to call the 8085 CPU to read port B data.

Figure 13. AD7552 in Continous Conversion Mode

Figure 14. Optically Isolated Serial AD7552/MCS-85 Interface