# 4½/5½ Digit ADC Subsystem

AD7555

#### PRELIMINARY TECHNICAL DATA

#### **FEATURES**

Resolution: ±4 1/2 Digits BCD or ±20k Count Binary Capability for 5 1/2 Digit Resolution or Custom Data Formats Data Format: Multiplexed BCD (for Display) and Serial Count (for External Linearization, Data Reformatting, or Microprocessor Interface)

Accuracy: ±1 Count in ±20k Counts

Scale Factor Drift: 0.2ppm/°C Using Only Medium-Precision Op Amps

Requires only a Single Positive Reference

Overrange Display

**Auto Calibration Capability** Interfaces to TTL or 5V CMOS

HOLD Input and SCC (System Conversion Complete) **Output for Interface Flexibility**

#### GENERAL DESCRIPTION

The AD7555 is a 4 1/2 digit, monolithic CMOS, quad slope integrating ADC subsystem designed for display or microprocessor interface applications. Use of the high resolution enable input expands the display format to 5 1/2 digits BCD. With SCO (Serial Count Out) connected to SCI (Serial Count In), the output data format is multiplexed BCD suitable for visual display purposes. As an added feature, SCO can also be used with rate multipliers for linearization, or with BCD or binary counters for data reformatting (up to 200k binary counts).

The quad slope conversion algorithm (Analog Devices patent No. 3872466) converts the external amplifier's input drift errors to a digital number and subsequently reduces the total system drift error to a second order effect. Using only inexpensive, medium-precision amplifiers a scale factor drift of 0.2ppm/°C is achieved.

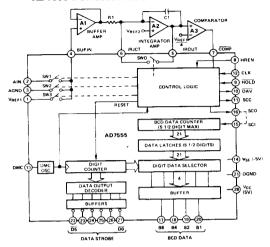

#### AD7555 FUNCTIONAL BLOCK DIAGRAM

#### PIN CONFIGURATION

#### ORDERING INFORMATION

| Model    | Package                             | Operating<br>Temperature Range |

|----------|-------------------------------------|--------------------------------|

| AD7555BD | 28 Pin Side Brazed Ceramic - (D28B) | -25°C to +85°C                 |

| AD7555KN | 28 Pin Molded Plastic — (N28A)      | 0 to +70°C                     |

See Section 20 for package outline information.

# **SPECIFICATIONS** (VCC = +5V, VSS = -5V, VREF1 = +4.0960V, FCLK = 614.4kHz, AGND = 0V)

|                                                | LIMIT AT             | LIMIT AT TA                           |              | , _                                               |

|------------------------------------------------|----------------------|---------------------------------------|--------------|---------------------------------------------------|

| PARAMETER                                      | $T_A = +25^{\circ}C$ | = T <sub>min</sub> , T <sub>max</sub> | UNITS        | CONDITIONS/COMMENTS                               |

| ANALOG SWITCHES                                |                      |                                       |              |                                                   |

| RON (Switch 1-3)                               | 800                  | 1200                                  | $\Omega$ max | -2V ≤ AIN ≤ +2V Refer to Functional Diagram       |

| ΔRON (Switch 1) versus AIN                     | 300                  | 500                                   | Ωtyp         | $-2V \leq AIN \leq +2V$                           |

| Mismatch Between Any Two                       |                      |                                       |              |                                                   |

| Switches (excluding SW0)                       | 300                  | 500                                   | Ωtyp         | $-2V \leq AIN \leq +2V$                           |

| I <sub>LKG</sub> (Switch OFF)                  |                      |                                       |              |                                                   |

| SW0 (pin 6)                                    | 1                    | 70                                    | nA max       | IRJCT (pin 5) = +2.048V                           |

| ,                                              |                      |                                       |              | $0V \leq IROUT (pin 5) \leq +10V$                 |

| SW1 (pin 2)                                    | 1                    | 70                                    | nA typ       | AIN = $+2V$ to $-2V$ , BUFIN = $0V$ and $+4.096V$ |

| SW2 (pin 3)                                    | 1                    | 70                                    | nA typ       | AGND = $0V$ , BUFIN = $-2V$ to $+2V$ , $+4.096V$  |

| SW3 (pin 1)                                    | 1                    | 70                                    | nA typ       | $V_{REF1} = +4.096V$ , BUFIN = -2V to +2V         |

| I <sub>LKG</sub> (BUFIN, pin 4)                | 3                    | 200                                   | nA typ       | Any 1 of SW1, 2, 3 on                             |

| CONTROL INPUTS (pins 7, 8, 9, 15)              |                      |                                       |              |                                                   |

| V <sub>INH</sub>                               | 3.0                  | 3.0                                   | V min        |                                                   |

| VINH<br>VINL                                   | 0.8                  | 0.8                                   | V max        |                                                   |

|                                                | 1                    | 10                                    | μA max       | $V_{IN} = 0V$ or $V_{CC}$                         |

| I <sub>INH</sub> or I <sub>INL</sub>           |                      |                                       |              | 117 CC                                            |

| CLOCK INPUTS (pin 12 and 13)                   |                      |                                       |              |                                                   |

| V <sub>INH</sub> (CLK)                         | 3.5                  | 3.5                                   | V min        |                                                   |

| V <sub>INL</sub> (CLK)                         | 0.8                  | 0.8                                   | V max        |                                                   |

| V <sub>INH</sub> (DMC)                         | 3.0                  | 3.0                                   | V min        |                                                   |

| V <sub>INL</sub> (DMC)                         | 0.8                  | 0.8                                   | V max        |                                                   |

| I <sub>INH</sub> (CLK)                         | 1.0                  | 1.5                                   | mA max       |                                                   |

| I <sub>INL</sub> (CLK)                         | -1.0                 | -1.5                                  | mA max       |                                                   |

| I <sub>INH</sub> (DMC)                         | 200                  | 300                                   | μA max       |                                                   |

| I <sub>INL</sub> (DMC)                         | -100                 | -150                                  | μA max       |                                                   |

| DIGITAL OUTPUTS                                |                      |                                       |              |                                                   |

| $\overline{D0}$ - $\overline{D5}$ (pins 22-27) |                      |                                       |              |                                                   |

| V <sub>OH</sub>                                | 4.5                  | 4.5                                   | V min        | $I_{SOURCE} = 40\mu A$                            |

| Vol.                                           | 4.0                  | 4.0                                   | V max        | I <sub>SINK</sub> = 5mA (Display Driver Load)     |

| V <sub>OL</sub>                                | 0.5                  | 0.8                                   | V max        | I <sub>SINK</sub> = 1.6mA (TTL Load)              |

| B1, B2, B4, B8, DAV, SCC, SCO                  |                      |                                       |              |                                                   |

| (pins 20, 19, 18, 17, 10, 11, 16)              |                      |                                       |              |                                                   |

| V <sub>OH</sub>                                | 4.0                  | 4.0                                   | V min        | $I_{\text{SOURCE}} = 40\mu\text{A}$               |

| Vol                                            | 0.5                  | 0.8                                   | V max        | I <sub>SINK</sub> = 1.6mA                         |

|                                                |                      |                                       |              |                                                   |

| DYNAMIC PERFORMANCE                            | 5                    | 5                                     | μs min       | See Figure 3                                      |

| DMC Pulse Width                                | 100                  | 100                                   | kHz max      | Typical f <sub>DMC</sub> is 1.5kHz with           |

| DMC Frequency                                  | 100                  | 100                                   | KIIZ IIIAA   | $C_{\text{DMC}} = 0.01 \mu\text{F}$               |

| CL K E                                         | 1.5                  | 1.5                                   | MHz max      |                                                   |

| CLK Frequency                                  | 1.5                  | 1.3                                   | MITTE III AX |                                                   |

| Propagation Delays                             | 5                    | 7                                     | μs max       | See Figure 3                                      |

| DMC HIGH to DAV HIGH                           |                      | 7                                     | μs max       | See Ligare V                                      |

| DMC HIGH to DAV LOW                            | 5                    | ′                                     | μειπαλ       |                                                   |

| DMC HIGH to BCD Data on                        | _                    | _                                     | us mar       |                                                   |

| B8, B4, B2, B1                                 | 5                    | 5                                     | μs max       |                                                   |

| DMC LOW to Digit Strobe                        | -                    |                                       | us mar       |                                                   |

| (D0 - D5) LOW                                  | 5                    | 5                                     | μs max       |                                                   |

| POWER SUPPLY                                   |                      |                                       |              |                                                   |

| I <sub>CC</sub>                                | 5                    | 5                                     | mA max       | During Conversion                                 |

| lss                                            | 5                    | 5                                     | mA max       | During Conversion                                 |

| V <sub>CC</sub> Range                          | +5 to +17            | +5 to +17                             | v            | See Absolute Maximum Ratings                      |

| V <sub>SS</sub> Range                          | -5 to -17            | -5 to -17                             | V            |                                                   |

Specifications subject to change without notice.

# **System Electrical Characteristics**

| ABSOLUTE MAXIMUM RATINGS                                     |

|--------------------------------------------------------------|

| V <sub>CC</sub> to DGND                                      |

| V <sub>SS</sub> to DGND17V                                   |

| V <sub>CC</sub> to V <sub>SS</sub>                           |

| Digital Outputs                                              |

| Digital Inputs                                               |

| DMC (Pin 13), CLK (Pin 12) V <sub>SS</sub> , V <sub>CC</sub> |

| All other Logic Inputs DGND, +17V                            |

| Analog Inputs/Outputs                                        |

| AGND to DGND (Positive Limitation) VCC or VIROUT*            |

| AGND to DGND (Negative Limitation). VSS or VIROUT -20V†      |

| AIN (Pin 2), V <sub>REF1</sub> (Pin 1),                      |

| BUFIN (Pin 4)                                                |

| IRJCT (Pin 6), IROUT (Pin 5)+27V, AGND                       |

| Operating Temperature Range                                  |

| AD7555KN (Plastic) 0 to +70° C                               |

| AD7555BD (Ceramic)25°C to +85°C                              |

| Storage Temperature                                          |

| Lead Temperature (Soldering, 10s)+300°C                      |

|                                                              |

| Power Dissipation (package) |         |

|-----------------------------|---------|

| Plastic (AD7555KN)          |         |

| To +50°C                    | .1200mW |

| Derate above +50°C by       | 12mW/°C |

| Ceramic (AD7555BD)          |         |

| To +50°C                    | .1000mW |

| Derate above +50°C by       | 10mW/°C |

|                             |         |

\*Whichever is the least positive. †Whichever is the least negative.

#### NOTE:

Do not apply voltages to any AD7555 digital output, AIN or V<sub>REF1</sub> before V<sub>SS</sub> and V<sub>CC</sub> are applied. Additionally, the voltages at AIN, V<sub>REF1</sub> or any digital output must never exceed V<sub>CC</sub> and V<sub>SS</sub> (if an op amp output is used to drive AIN it must be powered by the AD7555 V<sub>CC</sub> and V<sub>SS</sub> supply voltages). Do not allow any digital input to swing below DGND. V<sub>DD</sub>, the external op-amps positive supply voltage, should be applied before V<sub>CC</sub>.

#### CAUTION:

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The foam should be discharged to the destination socket before devices are removed.

SYSTEM ELECTRICAL CHARACTERISTICS ( $T_A = 0$  to +45°C) Characteristics refer to the system of Figures 6a and 6b.  $V_{CC} = +5V$ ,  $V_{SS} = -5V$ ,  $V_{REF1} = +4.096V$ , error count n calibrated to zero at  $T_A = +25$ °C as described in the calibration section unless otherwise noted. Switch leakages and limitations in temperature performance of auxiliary components (such as the integrating capacitor) cause performance degradations

| CHARACTERISTIC                           | LIMIT                              | CONDITIONS/COMMENTS                                       |

|------------------------------------------|------------------------------------|-----------------------------------------------------------|

| Resolution                               | 4 1/2 Digit BCD<br>5 1/2 Digit BCD | ±20,000 Counts<br>±200,000 Counts<br>(See Note 1)         |

| Relative Accuracy                        | ±1 Count max<br>±10 Count max      | 4 1/2 Digit BCD<br>5 1/2 Digit BCD<br>(See Notes 1 and 2) |

| Count Uncertainty Due to Noise (Flicker) | ±1/2 Count max<br>±2 Counts max    | 4 1/2 Digit BCD<br>5 1/2 Digit BCD<br>(See Note 1)        |

| Conversion Time                          | 610ms max<br>1,760ms max           | 4 1/2 Digit BCD<br>5 1/2 Digit BCD<br>(See Note 1)        |

NOTES:

$^{1}$  4 1/2 digit mode;  $f_{CLK}$  = 614.4kHz, HREN = LOW, R<sub>1</sub> = 360kΩ  $C_{1}$  = 0.22 $\mu$ F

5 1/2 digit mode;  $f_{CLK}$  = 1.024MHz, HREN = HIGH,  $R_1$  = 750k $\Omega$   $C_1$  = 0.22 $\mu$ F

<sup>2</sup> Assumes voltage reference (V<sub>REF1</sub>) TC of 0ppm/°C.

### Applying the AD7555

|                  |                                  |                                  | AD / 333                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                  | AD7555 PIN DESCRIPTION           |                                  |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| ANALOG FUNCTIONS |                                  |                                  |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                  | V <sub>REF1</sub><br>AIN<br>AGND | (Pin 1):<br>(Pin 2):<br>(Pin 3): | +4.096V Reference Input Analog Input Voltage (±2V Full Scale) Analog Signal Common Ground                                                                                                                                                                                                                                  |  |  |  |  |  |

|                  | IROUT                            | (Pin 4):<br>(Pin 5):<br>(Pin 6): | To External Buffer Amplifier Input<br>From Integrator Amplifier Output<br>To Integrator Amplifier Summing                                                                                                                                                                                                                  |  |  |  |  |  |

| İ                | 3                                |                                  | Junction                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| I                | OGIC IN                          |                                  | c d comparator                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                  | COMP                             | (Pin 7):                         | Input from the external comparator.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                  | HREN                             | (Pin 8):                         | High Resolution Enable, determines converter resolution                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                  |                                  |                                  | HREN = LOGIC LOW, Full Scale =<br>±1.9999V (100μV resolution)                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                  |                                  |                                  | HREN = LOGIC HIGH, Full Scale =<br>±1.99999V (10μV resolution)                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                  | HOLD                             | (Pin 9):                         | Hold Input  HOLD = LOGIC HIGH, the ADC converts and updates the displays continuously as per the timing diagram of Figure 3.  HOLD = LOGIC LOW, the ADC is                                                                                                                                                                 |  |  |  |  |  |

|                  |                                  |                                  | reset and conversion is disabled. Data from the last complete conversion continues to be displayed. To ensure most recent data is displayed, HOLD should not be taken LOW when DAV is HIGH. When HOLD returns HIGH, the next leading edge of DMC initiates a new conversion.                                               |  |  |  |  |  |

|                  | DMC                              | (Pin 13):                        | Display Multiplexer Clock, can be driven from an external logic source, or with the addition of an external capacitor, will self oscillate. With an external capacitor of 10,000pF, DMC oscillates at approximately 1.5kHz at a 5% to 10% duty cycle, suitable for display purposes.                                       |  |  |  |  |  |

|                  | CLK                              | (Pin 12):                        | Clock Input for maximum line rejection in the 4 1/2 digit mode;  50Hz: f <sub>CLK</sub> = 512kHz (= 4.096MHz ÷ 8)  60Hz: f <sub>CLK</sub> = 614.4kHz (= 4.915MHz ÷ 8)  50/60Hz: f <sub>CLK</sub> = 409.6kHz  (= 3.2768MHz ÷ 8)  For maximum line rejection in the  5 1/2 digit mode;  50/60Hz, f <sub>CLK</sub> = 1.024MHz |  |  |  |  |  |

|                  | SCI                              | (Pin 15)                         | $(=4.096MHz \div 4)$                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                  | <del>.</del><br> <br>            |                                  | normally connected to SCO for direct count totalization.                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                  | SUPPLY                           | INPUTS                           |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                  | V <sub>CC</sub>                  | (Pin 28)                         | Positive Supply Input (+5V)                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | $V_{SS}$                         | (Pin 14)                         | Negative Supply Input (-5V)                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | DGNI                             | D (Pin 21)                       | : Digital Ground                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| OGIC OUTPUTS                    |                  |                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| B8 - B1                         | (Pins 17 - 20)   | BCD8 - BCD1 output, Active HIGH (See table 1)                                                                                                                                                                                                                                                                   |  |  |  |

| D5                              | (Pin 22):        | 10 <sup>-5</sup> digit output, Active LOW in<br>5 1/2 digit mode, stays HIGH in 4 1/2<br>digit mode                                                                                                                                                                                                             |  |  |  |

| <del>D</del> 4 - <del>D</del> 1 | (Pins 23-<br>27) | 10 <sup>-4</sup> – 10 <sup>-1</sup> digit outputs, Active LOW                                                                                                                                                                                                                                                   |  |  |  |

| DO                              | (Pin 27):        | 10 <sup>0</sup> /overflow/polarity output,<br>Active LOW                                                                                                                                                                                                                                                        |  |  |  |

| SCC                             | (Pin 11):        | System conversion complete, goes HIGH when conversion is complete, returns LOW on comparator crossing at end of phase 0 integration period.                                                                                                                                                                     |  |  |  |

| sco                             | (Pin 16):        | Serial Count Out, a serial output pulse train proportional in length to the magnitude of AIN. SCO can be externally pulled HIGH while DAV = HIGH to display the error count "n" for calibration purposes (see calibration section).                                                                             |  |  |  |

| DAV                             | (Pin 10):        | Data Valid — When low, DAV indicates that the data being presented on the BCD output bus is valid. DAV goes high on the first positive edge of DMC after a conversion is complete and returns low two DMC pulses later. When it returns low, the digit counter is reset to DO. This is termed the MASTER RESET. |  |  |  |

| DATA     | 88 | 84 | B2 | Ві | LED DISPLAY<br>WHEN USING 7447<br>SEGMENT DECODER |

|----------|----|----|----|----|---------------------------------------------------|

|          |    |    |    |    | G                                                 |

| 0        | 0  | 0  | 0  | 0  | 1 - 7                                             |

| 1        | 0  | 0  | O  | 1  | 1 4                                               |

| 2        | 0  | 0  | 1  | 0  | [ <u> </u>                                        |

| 3        | 0  | 0  | 1  | 1  | <u> </u>                                          |

| 4        | 0  | 1  | 0  | 0  | 1 9                                               |

| 5        | 0  | 1  | 0  | 1  | 5                                                 |

| 6        | 0  | 1  | 1  | 0  | ⊵                                                 |

| 7        | 0  | 1  | 1  | 1  | - nwa-ng-nh-cmun                                  |

| 8        | 1  | 0  | 0  | 0  | <u>8</u>                                          |

| 9        | 1  | 0  | 0  | 1  | ) 3                                               |

| OVERFLOW | 1  | 1  | 0  | 0  | <u> </u>                                          |

| (+1      | 0  | 0  | 0  | 0  | +!                                                |

| DIGIT -1 | 0  | 0  | 1  | 0  | -1                                                |

| ONLY +   | 1  | 1  | 0  | 0  | ÷                                                 |

| _        | 0  | 1  | 1  | 1  | -                                                 |

Table 1. Output Coding

### **Quad Slope Theory of Operation**

Component limitations such as switch leakage, as well as operational amplifier offset voltage and bias current (and the temperature dependency of these errors), are major obstacles when designing high resolution integrating A/D converters.

The AD7555 however, utilizes a patented *quad slope* conversion technique (Analog Devices Patent No. 3872466) to reduce the effects of such errors to second order effects.

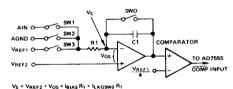

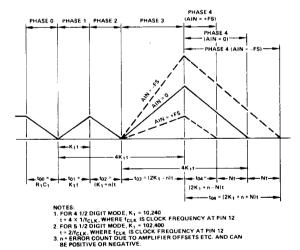

Figure 1 shows a simplified quad slope integrator circuit. The various inputs AGND (Analog Ground),  $V_{REF1}$ , and AIN (Analog Input) are applied in sequence to the integrator via switches 1-3 (see Table 2), creating four slopes at the integrator output (phase 1-4 of Figure 2). If the equivalent summing junction voltage  $V_S$  is precisely  $0.5V_{REF1}$ , the phase 1 and phase 2 integration times are equal, indicating there are no input errors. If  $V_S \neq 0.5V_{REF1}$  (due to amplifier offset voltage, bias current, etc.), an error count "n" is obtained. The analog input integration cycle (phase 3) is subsequently lengthened or shortened by "n" counts, depending on whether the error was positive or negative.

Figure 1. Simplified Quad Slope Integrator Circuit

Figure 2. Quad Slope Integrator Output

The final effect is to reduce the analog input error terms to second order effects. This can be proven by solving the differential equations obtained during the phase 1 through phase 4 integration periods. Barring third (and higher) order effects, the solutions are given in equations 1 and 2.

$$N_{(AIN>0)} = K_T \left[ \frac{AIN}{V_{REF1}} + K_T \left[ \frac{AIN}{V_{REF1}} - 1 \right] \left[ -\alpha^2 + \frac{AGND}{V_{REF1}} (1 + 2\alpha) \right]$$

IDEAL TERM ERROR 1 FRM FQN1

$$N_{(AIN < 0)} = -K_T \left[ \begin{array}{c} AIN \\ V_{REF1} \end{array} \right] - K_T \left[ \begin{array}{c} AIN \\ V_{REF1} \end{array} - 1 \right] \left[ -\alpha^2 + \frac{AGND}{V_{REF1}} \left( 1 + 2 \alpha \right) \right]$$

$$IDEAL TERM \qquad ERROR TERM \qquad EQN2$$

#### WHERE:

N = Number of counts appearing at AD7555 Serial Count Out pin corresponding to the analog input voltage, AIN.

AIN = Analog Input Voltage to be digitized

K<sub>T</sub> = 40960 counts (4 1/2 Digit Mode) 409600 counts (5 1/2 Digit Mode)

AGND = Voltage at AD7555 pin 3 (AGND) measured with respect to V<sub>REF1</sub> and AIN signal common ground. (Ideally, AGND = 0V)

2Ve - V<sub>REF1</sub>

a is an error term equal to  $\frac{2V_S - V_{REF1}}{V_{REF1}}$

Ideally a = 0 when  $V_S = 0.5V_{REF1}$ .

NOTE:

$V_S = V_{REF2} + V_{OS1} + V_{OS2} + I_{B2}R_1 + I_{SW0}R_1$

WHERE

$V_{REF2} = 0.5V_{REF1}$  if no error is present

$V_{OS1}$  = Offset voltage of buffer amplifier A1 (required to buffer the effect of  $\Delta R_{ON}$  of SW1 - SW2)

V<sub>OS2</sub> = Offset voltage of integrator amplifier A2

$l_{B2}R_1$  = Equivalent integrator amplifier offset voltage due to bias current of A2

$I_{SWO}R_1$  = Equivalent integrator amplifier offset voltage due to SW0 leakage current.

If AGND = 0, then the error terms of EQN 1 and 2 contain only second order effects due to  $a \neq 0$ . Thus, the AD7555 is a powerful tool which allows high precision system performance to be obtained when using only moderate precision op amps.

Other advantages of the quad slope technique include bipolar operation using a single positive voltage reference, and the fact that since the comparator propagation delay is constant hysteresis effects are eliminated. (This is because the comparator always approaches the zero crossing from the same direction).

|   | Phase | Switch<br>Closed<br>(Figure 1) | Equivalent<br>Input<br>Voltage     | Integration Time             |  |

|---|-------|--------------------------------|------------------------------------|------------------------------|--|

|   | 0     | SW3                            | V <sub>REF1</sub> - V <sub>S</sub> | $t_{00} = R_1 C_1$           |  |

|   | 1     | SW2                            | AGND - V <sub>S</sub>              | $t_{01} = K_1 t$             |  |

|   | 2     | SW3                            | V <sub>REF1</sub> - V <sub>S</sub> | $t_{02} = (K_1 + n)t$        |  |

|   | 3     | SW1                            | AIN - V <sub>S</sub>               | $t_{03} = (2K_1 - n)t$       |  |

|   | 4     | SW3                            | V <sub>REF1</sub> - V <sub>S</sub> | $t_{04} = (2K_1 + n \pm N)t$ |  |

| - | 5     | SWO                            | RESET INTEGRATOR                   |                              |  |

Table 2. Integrator Equivalent Input Voltages and Integration Times

ANALOG-TO-DIGITAL CONVERTERS VOL. 1, 11-105

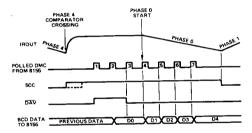

#### TIMING AND CONTROL

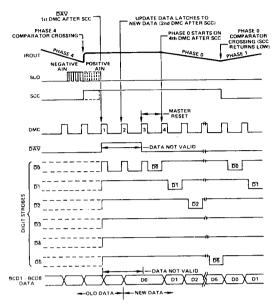

Figure 3 shows the AD7555 timing. SCC goes HIGH at the end of SCO indicating conversion is complete. DAV goes HIGH on the 1st leading edge of DMC after conversion is complete. New data is strobed into the data latches (see functional diagram) on the leading edge of the 2nd DMC. DAV returns low on the leading edge of the 3rd DMC.

BCD data is placed on B1, B2, B4, B8 on the positive edge of DMC while the digit counter is incremented on the negative edges of DMC.

A reset phase (phase 0) is initiated on the 4th DMC after conversion is complete. SCC returns low at the phase 0 comparator crossing indicating a conversion start.

If the DMC oscillator is set up to free run (C8 in Figure 6b causes DMC to run at about 1.5kHz), the AD7555 will continuously convert and update the displays.

Externally controlling the generation of DMC pulses provides a means of controlling data outputting for computer interface applications. Microprocessor Interfacing page illustrates how to use this feature to interface the AD7555 to a microprocessor.

#### DISPLAY

The output data format of the AD7555 is multiplexed BCD as per the Timing Diagram of Figure 3. The output code format is shown in Table 1.

Overflow causes digit 1 through digit 4 (digit 1 through digit 5 in 5 1/2 digit mode) to output a BCD 12 (1100). Overflow does not affect digit 0. Therefore, a positive overflow is displayed as +/, ----- and a negative overflow as -/, ------ when using the 7447 seven-segment decoder.

#### PRINTED CIRCUIT LAYOUT

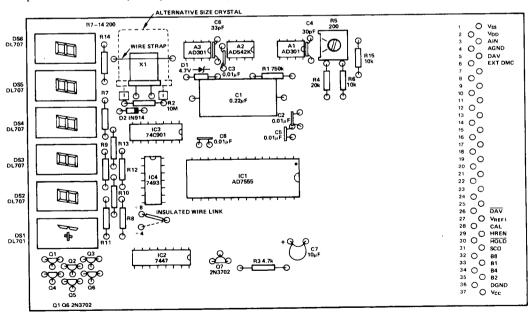

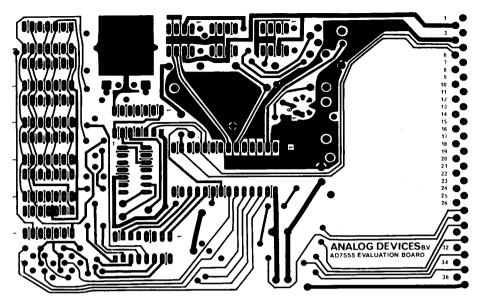

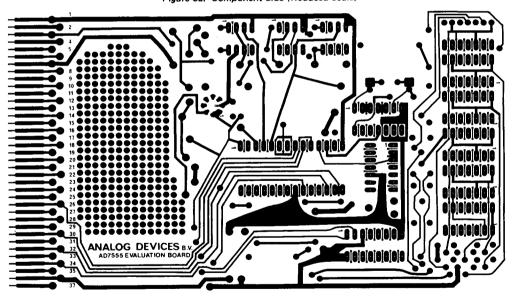

To ensure performance with the system specifications Figures

5a and 5b show the recommended P.C. board layout for the AD7555, Figure 4 shows the component overlay for Figure 5a.

Figure 3. Timing Diagram (Self Start DPM Mode)

Figure 4. Component Overlay for Figure 5a

VOL. I, 11-106 ANALOG-TO-DIGITAL CONVERTERS

Note that a pad already exists on the PCB layout for an AD584LH voltage reference, suitable for 4 1/2 digit operation.

Figure 5a. Component Side (Reduced Scale)

Figure 5b. Foil Side (Reduced Scale)

#### ANALOG CIRCUIT SET-UP AND OPERATION

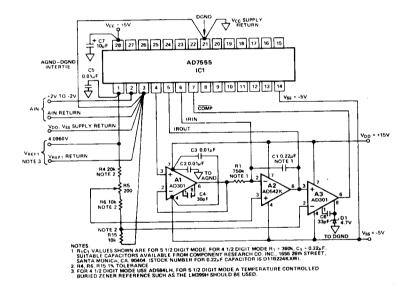

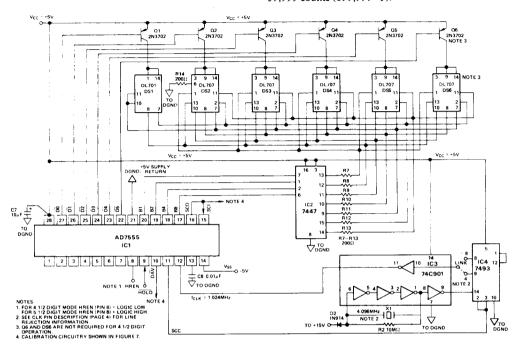

The following steps, in conjunction with the analog circuitry of Figure 6a explain the selection of the various component values required for proper operation.

Selection of Integrator Components R<sub>1</sub> and C<sub>1</sub>

Improper selection of the integrator time constant (time constant = R<sub>1</sub>C<sub>1</sub>) may cause excessive noise due to the integrator output level being too low, or may cause nonlinear operation if the integrator output attempts to exceed the rated output voltage of the amplifier. The integrator time constant R<sub>1</sub>C<sub>1</sub> must be:

$$\frac{(V_{REF1})(K_{\alpha})}{(f_{CLK})(7V)} \geqslant R_1C_1 \geqslant \frac{(V_{REF1})(K_{\alpha})}{(f_{CLK})(V_{DD} - 5V)}$$

Where:

$V_{\rm DD}$  is the integrator amplifier positive supply voltage  $f_{\rm CLK}$  is the clock frequency at pin 12  $K_{\alpha} = 8.2 \times 10^4$  (4 1/2 digit mode) or  $4.0 \times 10^5$  (5 1/2 digit mode)

The integrating capacitor must be a low leakage, low dielectric absorption type such as teflon (5 1/2 digit mode), polystyrene or polypropylene (4 1/2 digit mode). To minimize noise injection, the outside foil of C1 must be con-

nected to the output of the integrating amplifier, not to its summing junction.

The recommended maximum value for R1 in both the 4 1/2 digit and 5 1/2 digit mode is  $750k\Omega$ . Higher values may cause noise injection.

#### 2. Determing Conversion Time

Maximum conversion time occurs when  $A_{IN} = -FS$  and is given by

#### 4 1/2 DIGIT MODE

$t_{CONVERT} = (325,760)(t_{CLK}) + R_1C_1$

#### 5 1/2 DIGIT MODE

$t_{CONVERT} = (1,628,800)(t_{CLK}) + R_1C_1$

#### Where:

t<sub>CLK</sub> = Period of CLK as measured at pin 12 R<sub>1</sub>C<sub>1</sub> = Integrator Time Constant

#### 3. Initial Calibration

- a. Adjust  $V_{REF1}$  so that the voltage at pin 1 ( $V_{REF1}$ ) of the AD7555 is +4.0960V.

- Apply 0V to A1N and adjust R5 (V<sub>REF2</sub> Adjust) for display 0.0000. (See optional calibration procedure on the next page for more precise calibration.)

Figure 6a. Analog Circuit Diagram

#### APPLICATION HINTS

- See Note under Absolute Maximum Ratings for proper power sequencing and input/output voltage ratings.

- For linear operation the absolute magnitude of AIN cannot exceed 1/2 V<sub>REF1</sub>. In no case must AIN be more negative than V<sub>SS</sub>.

- 3. Do not leave unused CMOS inputs floating.

- 4. Check that integrator components R1 and C1 are chosen as per paragraph 1 of the setup and operation section on this page and that initial calibration as per paragraph 3 has been

- accomplished. A resistor value no larger than  $750 \mathrm{k}\Omega$  is recommended to minimize noise pickup.

- For optimum normal mode noise rejection, use the crystal frequencies shown in the applications section.

- In order for the calibrate mode (on the next page) to display the error count properly it can be shown that

$V_{REF2} \ge V_{REF1} \times 0.4883$ Specifically, for  $V_{REF1} = 4.0960V$  $V_{REF2} \ge 2V$

#### VOL. I, 11-108 ANALOG-TO-DIGITAL CONVERTERS

#### LOGIC AND DISPLAY CIRCUITRY

The AD7555 possesses 4 1/2 digit accuracy with potential for 5 1/2 digit resolution. Figure 6b shows the logic and display circuitry when operating the AD7555 with this high resolution.

#### MODIFYING THE FULL SCALE DISPLAY

Availability of the SCO and SCI terminals on the AD7555 provides flexibility for range-switching and modified data-format applications.

For example, in the 5 1/2 digit mode, inserting  $a \div 5$  counter between SCO and SCI provides a full scale count at SCI of 39,999 counts (199,999  $\div 5$ ).

Figure 6b. Logic and Display Circuitry (for 5 1/2 Digit Resolution)

#### **CALIBRATING THE AD7555**

When the AD7555 is placed in the calibrate mode, any resulting error voltage in  $V_S$  (summing junction voltage), due to drift, etc., will be contained in the resulting display. To display the error SC1 and SC0 must be taken HIGH (only allowable when  $\overline{\rm DAV}$  is HIGH). In the calibrate mode the display indicates +8.0480  $\pm \rm n$  (+8.04800  $\pm \rm n$  in 5 1/2 digit mode) where 8 indicates a blanked digit and n is a number representing the reference input errors. This gives the change required in  $V_{REF2}$  ( $\pm\Delta V_{REF2}$ ) for proper calibration (ie., n  $\approx$  0). The exact relationship between n and  $\Delta V_{REF2}$  can be shown to be equal to:

$$\Delta V_{REF2} = \frac{(V_{REF1})n}{40,960 + n}$$

(4 1/2 digit operation)

$$\Delta V_{REF2} = \frac{(V_{REF1})10n}{40,960 + 10n}$$

(5 1/2 digit operation)

For this capability to operate, |V<sub>REF2</sub>| must be 1/2 V<sub>REF1</sub> ±2%.

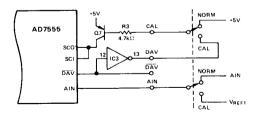

Figure 7 shows the hardware connections for manual calibration. With the switch in the calibrate mode, adjust V<sub>REF2</sub> (potentiometer R5 as shown in Figure 6a) until the display reads +b.0480 (+b0.04800 in 5 1/2 digit mode). The AD7555 is now calibrated to the center of its error correcting range.

Return the switch to normal to resume normal conversion.

Figure 7. Hardware Requirements for Manual Calibration of n = 0

ANALOG-TO-DIGITAL CONVERTERS VOL. 1, 11-109

### **Microprocessor Interfacing**

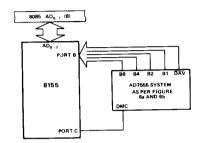

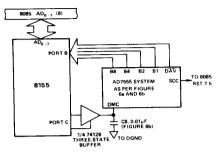

AD7555 AS A POLLED INPUT DEVICE (MCS-85 SYSTEM) Figure 8 shows an AD7555/8085 interface. The DMC clock input of the AD7555 is controlled by the microcomputer via an output port of the 8155.

Typical timing for this interface mode is shown in Figure 9. DAV goes HIGH on the 1st DMC leading edge after SCC goes HIGH. It returns LOW on the rising edge of the 3rd DMC pulse. Digit zero is availabe on B1, B2, B4 and B8 at this time. The leading edge of the 4th DMC pulse initiates a new conversion and places digit 1 on B1, B2, B4 and B8.

Table 3 shows a procedure for polling the AD7555.

Figure 8. AD7555 as a Polled Input Device

Figure 9. Timing Diagram for Operation as a Polled Input Device (8085/AD7555)

Table 3. Procedure for Interfacing the AD7555 as a Polled Input Device

VOL. I, 11-110 ANALOG-TO-DIGITAL CONVERTERS

## AD7555 AS AN INTERRUPTING INPUT DEVICE (MCS-85 SYSTEM)

The AD7555 DMC oscillator provides DMC pulses until SCC (System Conversion Complete) goes high. This causes an interrupt on the RST 7.5 line whereby the three-state buffer is activated and the microprocessor takes control of DMC. Table 4 shows a procedure for using the AD7555 in this mode. Figure 10 shows the basic hookup.

Figure 10. AD7555 as an Interrupting Input Device (MCS-85 System)

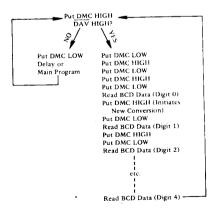

Interrupt Entry (SCC Goes High Causing Interrupt) Enable Three-State Buffer (74126 as Shown in Figure 10) Put DMC HIGH DAV HIGH? Put DMC LOW Put DMC LOW Put DMC HIGH DAV LOW? Put DMC LOW Read BCD Data (Digit 0) Put DMC HIGH Put DMC LOW Read BCD Data (Digit 1) Read BCD Data (Digit 4) Disable Three-State Buffer Return to Main Program

Table 4. Procedure for Interfacing the AD7555 as an Interrupting Input Device

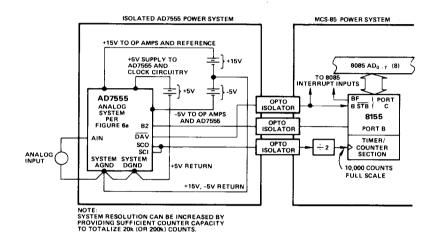

#### OPTO-ISOLATED SERIAL INTERFACE

Figure 11 shows a serial interface to the MCS-85 system. This system can accommodate a remote interface where a common-mode voltage is expected to exist between system grounds. The 8155 counter/timer is only 14 bits long, i.e., it can only count down from 2<sup>14</sup>; therefore SCO output from the AD7555 (20k counts full scale) has to be divided by 2 with consequent reduction in system resolution.

Port C of the 8155 is configured as a control port. Port B is an input port. This port configuration is necessary if sign information is required. Magnitude information is obtained by

interrogating the 8155 counter value. The rising edge of  $\overline{DAV}$  is used to cause an interrupt on the RST 7.5 line. The value  $\left(2^{14} - \frac{|S_Q^C|}{2}\right)$  in the 8155 counter should now be read.

When  $\overline{DAV}$  returns low the 8155 counter is reset to FF<sub>H</sub>. Sign information is checked at this time since  $\overline{D_0}$  BCD data is present and stable on the BCD bus (see Figure 9). The B2 line of the BCD bus is latched into port B by the signal on B STB i.e. the falling edge of DAV. This causes a rising edge signal on BF (buffer full) to call the 8085 CPU to read the B2 bit. B2 bit is HIGH for negative data, LOW for positive data.

Figure 11. Optically Isolated Serial AD7555/MCS-85 Interface (Full Scale = 10,000 Counts)