# Protected Dual SPST Analog Switch

**ADG200**

**FEATURES**

Latch-Proof DI CMOS

Overvoltage-Proof: V<sub>SUPPLY</sub> ±25V Superior DG-200 Replacement Break-Before-Make Switching Action

$R_{ON}$ : 100 $\Omega$  max over Full Temperature Range

Direct TTL/CMOS Interface

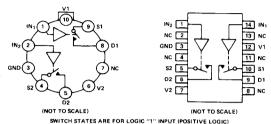

#### ADG200 FUNCTIONAL BLOCK DIAGRAMS

TO-100 TOP VIEW

14-PIN DIP DUAL-IN-LINE PACKAGE TOP VIEW

# GENERAL DESCRIPTION

The ADG200 is a dual single-pole-single-throw analog switch. In the ON condition, the switch conducts current in either direction, maintaining nearly constant ON resistance over the entire analog signal range. In the OFF condition, the switch blocks voltages of peak values equal to the switch V+ and V-supplies. Switch action is break-before-make: The digital inputs interface directly to TTL or CMOS logic over the full operating temperature range.

Fabricated using an advanced monolithic dielectrically-isolated CMOS process, the ADG200 is a superior plug-in replacement for the DG200. The ADG200 provides additional advantages (over the DG200) of: overvoltage protection to ±25V beyond the power supplies, total latch-free operation, much lower power dissipation (30mW max) and faster switching time.

#### ORDERING INFORMATION

| Commercial<br>0 to +70°C | Industrial<br>-25°C to +85°C       | Military<br>-55°C to +125°C<br>Ceramic (D14B) <sup>1</sup> TO-100 |  |  |  |

|--------------------------|------------------------------------|-------------------------------------------------------------------|--|--|--|

| Plastic (N14B)1          | Ceramic (D14B) <sup>1</sup> TO-100 |                                                                   |  |  |  |

| ADG200CJ                 | ADG200BP ADG200BA                  | ADG200AP ADG200AA<br>ADG200AA/883                                 |  |  |  |

Note: "/883" version is 100% screened to MIL-STD-883, class B as per note 3 on Specifications Table, next page.

<sup>1</sup>See Section 20 for package outline information.

16

# **SPECIFICATIONS**

|                                         |                                                      | MAX LIMITS    |             |                            |             |                  |                   |             |       | TEST CONDITIONS                                                  |                                                   |  |

|-----------------------------------------|------------------------------------------------------|---------------|-------------|----------------------------|-------------|------------------|-------------------|-------------|-------|------------------------------------------------------------------|---------------------------------------------------|--|

| CHARACTERISTIC <sup>1</sup>             |                                                      | TYP1<br>+25°C | I           | AA, AP Suffix <sup>3</sup> |             | BA, BP/CJ Suffix |                   | uffix       |       | Unless Noted V <sub>1</sub> = +15V                               |                                                   |  |

|                                         |                                                      |               | -55°C2      | +25°C                      | +125°C      | 5°C -25/0°C2     | +25°C             | +85/70°C2   | UNITS | $V_2 = -15V$ , GND = 0V                                          |                                                   |  |

| SWITCH                                  |                                                      |               |             |                            |             |                  |                   |             |       |                                                                  |                                                   |  |

| rds(on)                                 | ON Resistance                                        | 60<br>40      | 70<br>70    | 70<br>70                   | 100<br>100  | 80<br>80         | 80<br>80          | 100<br>100  | Ω     | $V_D = 10V$<br>$V_D = -10V$                                      | $V_{IN} = 0.8V$ $I_S = +1mA$                      |  |

| I <sub>S(OFF)</sub>                     | Source OFF<br>Leakage Current                        | 0.2<br>-0.2   | 500<br>-500 | 2<br>-2                    | 500<br>-500 | 500<br>-500      | 5<br>5            | 500<br>-500 |       | $V_S = 10V, V_D = -10V$<br>$V_S = -10V, V_D = 10V$               |                                                   |  |

| l <sub>D(OFF)</sub>                     | Drain OFF<br>Leakage Current                         | 0.3<br>-0.3   | 500<br>-500 | 2<br>-2                    | 500<br>-500 | 500<br>-500      | 5<br>-3           | 500<br>-500 | nА    | $V_{\rm IN} = 2.4V$                                              |                                                   |  |

| I <sub>D(ON)</sub> <sup>5</sup>         | Channel ON<br>Leakage Current                        | 0.1<br>-0.1   | 500<br>-500 | 2<br>-2                    | 500<br>-500 | 500<br>-500      | 2<br>-2           | 500<br>-500 |       | $V_D = V_S = 10V$ $V_D = V_S = -10V$                             | V <sub>IN</sub> = 0.8V                            |  |

| INPUT<br>I <sub>INH</sub>               | Input Current<br>Input Voltage High                  |               | -10<br>10   | -1<br>1                    | -10<br>10   | -10<br>10        | -1<br>1           | -10<br>10   | μΑ    | $V_{IN} = 2.4V$ $V_{IN} = 15V$                                   | -                                                 |  |

| I <sub>IN(PEAK)</sub> 6                 | Peak Input Current<br>Required for<br>Transition     |               |             | NOT                        | APPLICA     | BLE <sup>6</sup> |                   |             |       |                                                                  |                                                   |  |

| I <sub>INL</sub>                        | Input Current<br>Input Voltage Low                   |               | -10         | -1                         | -10         | -10 -10 -1 -10   |                   |             | μΑ    | V <sub>IN</sub> = 0V                                             |                                                   |  |

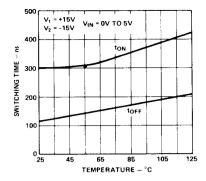

| DYNAMIC<br>TON<br>TOFF                  | Turn-ON Time <sup>7</sup> Turn-OFF Time <sup>7</sup> | 300<br>120    |             | 1000 <sup>2</sup>          |             |                  | 1000 <sup>2</sup> |             | ns    | $V_{1N} = 3.5V \text{ to } 0V$<br>$V_{1N} = 0V \text{ to } 3.5V$ | $R_L = 1k\Omega$ , $C_L = 35pB$<br>$V_S = \pm 5V$ |  |

| C <sub>S(OFF)</sub>                     | Source OFF<br>Capacitance                            | 11            |             |                            |             |                  |                   |             | pF    | $V_S = 0V$ , $V_{IN} = 5V$                                       |                                                   |  |

| C <sub>D(OFF)</sub>                     | Drain OFF<br>Capacitance                             | 11            |             |                            |             |                  |                   |             | pF    | V <sub>D</sub> = 0V, V <sub>IN</sub> = 5V                        | f = 140kHz                                        |  |

| C <sub>D(ON)</sub> + C <sub>S(ON)</sub> | Channel ON<br>Capacitance                            | 28            |             |                            | ***         |                  |                   |             | pF    | $V_D = V_S = 0V$<br>$V_{BN} = 0V$                                |                                                   |  |

| OFF Isolation <sup>B</sup>              |                                                      | 64            |             |                            |             |                  |                   |             | dB    | $V_{1N} = 5V, R_L = 1k\Omega, V_{S} = 7V_{rms}, f = 500kH$       |                                                   |  |

| SUPPLY                                  |                                                      |               |             |                            |             |                  |                   |             |       |                                                                  |                                                   |  |

| I <sub>1</sub> Positive Supply Current  |                                                      | 0.02          | 2           | 1                          | 2           | 2                | 1                 | 2           | mA.   | Both Channels ON; V <sub>IN</sub> = 0V                           |                                                   |  |

| l <sub>2</sub>                          | Negative Supply Current                              | -0.02         | -2          | -1                         | -2          | -2               | -1                | -2          | m A   | Both Chamicis Oiv; V                                             | ų - <del>0 v</del>                                |  |

| 1,                                      | Positive Supply Current                              | 0.1           | 2           | 1                          | 2           | 2                | ı                 | 2           | mA    | Both Channels OFF; V <sub>IN</sub> = 5V                          |                                                   |  |

| l <sub>2</sub>                          | Negative Supply Current                              | -0.02         | -2          | -1                         | -2          | -2               | ~1                | -2          | mA    |                                                                  |                                                   |  |

Specifications subject to change without notice.

#### CAUTION: -

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub> (Digital Input) to Ground0.3V, V <sub>1</sub> |

|---------------------------------------------------------------|

| $V_S$ or $V_D$ to $V_1$ (1 second surge) +25V, -40V           |

| (continuous)                                                  |

| $V_S$ or $V_D$ to $V_2$                                       |

| (1 second surge)25V, +40V                                     |

| (continuous)                                                  |

| V <sub>1</sub> to Ground0.3V, +17V                            |

| $V_2$ to Ground+0.3V, -17V                                    |

| Current, Any Terminal Except S or D 30mA                      |

| Current, S or D                                               |

| Current, S or D Pulsed                                        |

| (1ms, 10% duty cycle max)                                     |

| Operating remperature                       |

|---------------------------------------------|

| AA, AP Suffix55°C to +125°C                 |

| BA, BP Suffix                               |

| CJ Suffix $0^{\circ}$ C to +70 $^{\circ}$ C |

| Storage Temperature                         |

| CJ Suffix65°C to +125°C                     |

| All Others                                  |

| Power Dissipation (Package)*                |

| Metal Can** 450mW                           |

| 14 Pin Ceramic DIP*** 825mW                 |

| 14 Pin Plastic DIP****                      |

|                                             |

- Devices with all leads welded or soldered to printed circuit board Derate 6mW/°C above +75°C

- Derate 11mW/°C above +75°C

- \*\*\*\* Derate 6.5mW/°C above +25°C

Operating Temperature

## VOL. I, 16-30 CMOS SWITCHES & MULTIPLEXERS

NOTES.

17 ypical values for information only, not guaranteed or production tested.

2 Guaranteed, not subject to 100% production test.

3 ADG200AP is available 100% screened to MIL-STD-883, method 5004, para, 3.1.1 through 3.1.12 for a class 8 device. Final electrical tests are: TDS(ON), [S(OFF), DDOFF), IMPL, 1]NL, 1] and 12 at +23°C and +125°C (AA/883 version).

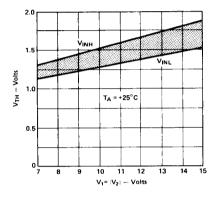

<sup>\*</sup>Functional operation is possible for supply voltages less than ±15V, but the input logic switching threshold will shift:

\*Jig(ON) is leakage from driver gate into ON such is less than 1 nanoamp.

\*Digral inputs are MOS gates. Typical leakage (±25°C) is less than 1 nanoamp. This is in contrast to other designs which require typically 150µA to switch.

\*This is in contrast to other designs which every experience the switch entire the property of the special special

#### CIRCUIT DESCRIPTION

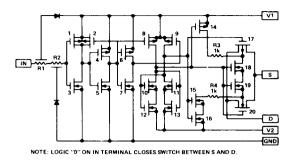

Figure 1. Schematic Diagram (1 of 2 channels)

CMOS devices make excellent analog switches; however, problems with overvoltage and latch-up phenomenon necessitate protection circuitry. However, these protection circuits either cause degradation of important switch parameters such as R<sub>ON</sub> or leakage, or provide only limited protection in the event of overvoltage.

The ADG200 switch utilizes a dielectrically-isolated CMOS fabrication process to eliminate the four-layer structure found in junction-isolated CMOS, thus providing latch-free operation.

A typical switch channel is shown in Figure 1. The output switching element consists of device numbers 17 and 20. Operation is as follows: for an "ON" switch, the gate of device 20 is  $\dot{V}_1$  and the gate of device 17 is  $V_2$  from the driver circuits. Device numbers 14, 15, and 16 are "OFF" and numbers 18 and 19 are "ON". Hence, the back-gates of the P- and N-channel output devices (numbers 17 and 20) are tied together and floating. Floating the output switch back-gates with the signal input provides a flatter  $R_{ON}$  versus  $V_S$  response.

For an "OFF" switch, device numbers 18 and 19 are "OFF", and the back-gates of devices 17 and 20 are tied through  $1k\Omega$  resistors  $R_3$  and  $R_4$  to the respective supply voltages through the "ON" devices 14, 15, and 16.

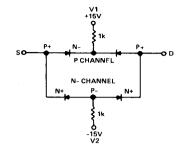

Figure 2. ADG200 Output Switch Diode Equivalent Circuit

If a voltage is applied to the S or D terminals which exceeds  $V_1$  or  $V_2$ , the S- or D-to-back-gate diode is forward biased; however,  $R_3$  and  $R_4$  provide current limiting action (Fig. 2).

Consequently, without external current limiting resistance (or increased R<sub>ON</sub>), the ADG200 series switches provide:

- 1. Latch-proof operation.

- Overvoltage protection 25V beyond the V<sub>1</sub> or V<sub>2</sub> supply voltage.

An equivalent circuit of the output switch element in Figure 2 shows that, indeed, the  $1k\Omega$  limiting resistors are in series with the back-gates of the P- and N-channel output devices — not in series with the signal path between the S & D terminals.

In some applications it is possible to turn on a parasitic NPN (drain to back-gate to source of the N-channel) transistor which causes device destruction under certain conditions. This case will only manifest itself when a negative overvoltage (and not a positive overvoltage) exists with another voltage source on the other side of the switch. Current limitation through external resistors  $(200\Omega)$  or the output of op amps will prevent damage to the device.

Figure 3. Switching Time vs. Temperature

Figure 4. Input Logic Threshold vs. Power Supply Voltage

# VOL. I, 16-32 CMOS SWITCHES & MULTIPLEXERS