# 2147 4096 Bit (4096 x 1) HMOS Static RAM

### **FEATURES**

- High speed-55ns maximum access time (2147-3)

- Low power 880mW maximum active power

- Automatic low-power standby-20mA max (2147L)

- Completely static-no clock required

- Single +5V supply

- TTL compatible inputs and outputs

- Three-state outputs

- HMOS process technology

- Industry standard 2147 pin compatible

### **GENERAL DESCRIPTION**

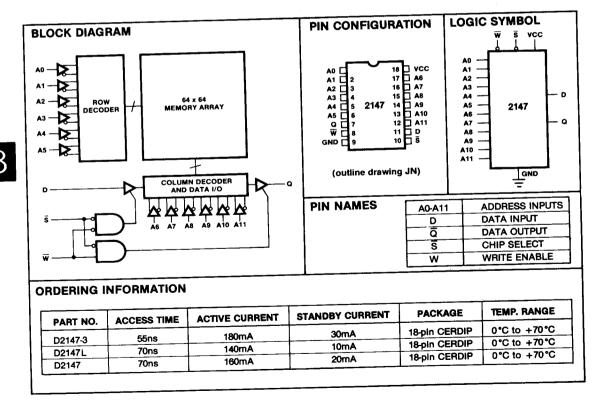

The Intersil 2147 is a low power 4096-bit static RAM organized 4096 words by 1 bit. It is an advanced version of the industry standard 2147, fabricated with Intersil's HMOS single-layer poly selective-oxidation process. Innovative design techniques result in minimum cell area and optimum circuit performance.

Inputs and three-state outputs are TTL compatible and allow for direct interfacing with common system bus structures.

An automatic low-power standby mode is controlled by chip select (\$); less than one cycle time after \$\$ goes high, power dissipation drops from a maximum of 160mA to 20mA (2147).

The basic device operates over the 5V  $\pm 10\%$  range with a worst-case access time of 7pns; a " -3" device offers a worst-case access time 55ns.

The Intersil 2147 is supplied in an 18-pin package with industry standard pin configuration.

### ABSOLUTE MAXIMUM RATINGS 1

| SYMBOL          | DESCRIPTION                        | MIN  | MAX   | UNITS      | NOTES |

|-----------------|------------------------------------|------|-------|------------|-------|

| V <sub>IN</sub> | Voltage on any Pin Relative to GND | -1.5 | +7    | ٧          | 2     |

| los             | D.C. Output Current                |      | 20    | mA         |       |

| tSTORE          | Storage Temperature                | -65  | + 150 | င္         |       |

| †BIAS           | Ambient Temperature Under Bias     | -10  | +85   | <b>°</b> C |       |

| P <sub>D</sub>  | Power Dissipation                  |      | 1     | W          |       |

#### NOTES:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions exceeding those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

- This device contains internal circuitry to protect against damage due to static charge. Conventional precautions should be observed, however, during storage, handling, and use to avoid exposure to excessive voltages.

### **ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V \pm 10\%$ , $T_A = 0$ °C to +70 °C, unless otherwise noted

| SYMBOL          | DESCRIPTION                  | MIN<br>2.0 | <b>MAX</b> 6.0 | UNITS | TEST CONDITONS                                                            |  |  |  |

|-----------------|------------------------------|------------|----------------|-------|---------------------------------------------------------------------------|--|--|--|

| V <sub>IH</sub> | Input HIGH Voltage           |            |                |       |                                                                           |  |  |  |

| VIL             | Input LOW Voltage            | - 1.0      | 0.8            | V     |                                                                           |  |  |  |

| VOH             | Output HIGH Voltage          | 2.4        |                | V     | IOH = -4.0mA                                                              |  |  |  |

| VoL             | Output LOW Voltage           |            | 0.4            | V     | IOL = 8mA                                                                 |  |  |  |

| IIL.            | Input Leakage Current        |            | 10             | μA    | $V_{CC} = 5.5V$ , GND $\leq VIN \leq VCC$                                 |  |  |  |

| JOLK            | Output Leakage Current       |            | 50             | μА    | $V_{CC} = 5.5V$ , $\overline{S} = VIH$ , $\overline{GND} \le VO \le 4.5V$ |  |  |  |

| los             | Output Short Circuit Current | - 200      | 200            | mA    | V <sub>OUT</sub> = GND to V <sub>CC</sub>                                 |  |  |  |

|        |                              | MAXI   | MUM VALU | JES  | UNITS |       |

|--------|------------------------------|--------|----------|------|-------|-------|

| SYMBOL | DESCRIPTION                  | 2147-3 | 2147L    | 2147 |       | NOTES |

| ICCOP1 | Operating Supply Current     | 170    | 135      | 150  | mA    | 1, 2  |

| ICCOP2 | Operating Supply Current     | 180    | 140      | 160  | mA    | 1, 3  |

| ICCSB  | Standby Supply Current       | 30     | 10       | 20   | mA    | 4     |

| ICCPON | Peak Power-On Supply Current | 70     | 30       | 50   | mA    | 5     |

#### NOTES:

1.  $V_{CC} = 5.5V$ ,  $S = V_{1L}$ , IO = 0 mA

2. TA = 25 °C

3. TA = 0°C

**4.**  $V_{CC} = 4.5$  to 5.5V, S =  $V_{IH}$

5.  $V_{CC}=$  GND to 4.5,  $\overline{S}=$  lower of  $V_{CC}$  or  $V_{IH}$  min. A pullup resistor on  $\overline{S}$  is required during power-on in order to keep the device deselected; otherwise ICCPON approaches ICCOp. VCC slew

## TIMING CHARACTERISTICS $V_{CC} = 5V \pm 10\%$ , $T_A = 0$ °C to +70 °C, unless otherwise noted 1,4

| SYMBOL           | DESCRIPTION                         |                   | 2147 |          | 2147-3 |     | 1     | TEST  |

|------------------|-------------------------------------|-------------------|------|----------|--------|-----|-------|-------|

|                  |                                     | JEDEC<br>SYMBOL N | MIN  | MAX      | MIN    | MAX | UNITS | NOTES |

|                  | READ CYCLE                          |                   |      | 1        |        |     |       |       |

| t <sub>rc</sub>  | Read Cycle Time                     |                   | 70   | L        | 55     | L   |       |       |

| laa              | Address Access Time                 | TAVQV             |      | 70       |        | 55  |       |       |

| acs <sub>1</sub> | Chip Select Access Time             | TSLQV             |      | 70       |        | 55  | 1 1   | 2     |

| acs2             | Chip Select Access Time             | TSLQV             |      | 80       |        | 65  | 1 1   | 3     |

| t <sub>oh</sub>  | Output Hold from Address Change     | TAXQX             | 5    |          | 5      | L   | ]     |       |

| t <sub>lz</sub>  | Chip Selection to Output Enabled    | TSLQX             | 10   | Ii       | 10     |     |       |       |

| t <sub>hz</sub>  | Chip Deselection to Output Disabled | TSHQZ             | 0    | 40       | 0      | 40  | 1     |       |

| t <sub>pu</sub>  | Chip Selection to Power Up Time     |                   | 0    |          | 0      |     | 1     |       |

| t <sub>pd</sub>  | Chip Deselection to Power Down Time |                   |      | 30       |        | 30  | ]     |       |

| pu               | WRITE CYCLE                         |                   |      |          |        | 1   | 1     |       |

| twc              | Write Cycle Time                    |                   | 70   | L        | 55     | L   | ns    |       |

| t <sub>cw</sub>  | Chip Selection to End of Write      | TSLWH             | 55   |          | 45     |     |       |       |

| taw              | Address Valid to End of Write       | TAVWH             | 55   |          | 45     |     | _     |       |

| tas              | Address Setup Time                  | TAVWL             | 0    |          | 0      |     | _     |       |

| twp              | Write Pulse Width                   | TWLWH             | 40   | <u> </u> | 35     | J   | _     |       |

| twr              | Write Recovery Time                 | TWHAX             | 15   | 1        | 10     |     | _     |       |

| t <sub>dw</sub>  | Data Valid to End of Write          | TDVWH             | 30   |          | 25     | ļ   | _     |       |

| t <sub>dh</sub>  | Data Hold Time                      | TWHDX             | 10   |          | 10     |     | 1     |       |

| t <sub>wz</sub>  | Write Enabled to Output Disabled    | TWLQZ             | 0    | 35       | 0      | 30  |       |       |

| tow              | Output Active from End of Write     | TWHQX             | 0    | T        | 0      |     | 1     | İ     |

- 1.  $t_f = t_f = 10$ ns. Input and output timing reference level = 1.5V.

- 2. Device deselected for 55ns or more prior to selection.

- 3. Device deselected for a finite time less than 55ns prior to selection.

- 4. Operating temperature range is guaranteed with transverse flow exceeding 400 linear feet per minute.

8-13

ADDRESS VALID

CHIP SELECT

(S)

WRITE ENABLE

(W)

DATA IN

(D)

DATA OUT

(Q)

B-14