### CMOS 4-BIT MICROCONTROLLER

# TMP42C40P, TMP42C60P

The 42C40/60 are compact, high speed 4-bit single chip microcomputers integrating ROM, RAM input/output ports, and interval timer. The 42C40/60 are the standard type devices in the TLCS-42 CMOS series. The 42C40/60 are suitable for control of home appliances (such as fans, air-conditioners, refrigerators), audio equipments, games, toys and so on.

| Г | PART No.  | ROM          | RAM        | PACKAGE | DICCYDACK DOADD |

|---|-----------|--------------|------------|---------|-----------------|

| ŀ | PARTINO.  |              | KAIVI      | PACKAGE | PIGGYBACK BOARD |

| 1 | TMP42C40P | 512 x 8-bit  | 22 4       | DIBAC   | 5443445         |

| ſ | TMP42C60P | 1024 × 8-bit | 32 × 4-bit | DIP16   | BM4211B         |

### **FEATURES**

- ◆4-bit single chip microcomputer

- ◆Instruction execution time: 1.0µs (at 5MHz, 4.5 to 6.0V) 2.5µs (at 2MHz, 4.0 to 6.0V)

- ◆44 basic instructions

- · All instructions are one byte object code

- Table look-up instructions

- ◆Stack for subroutine call: 1 level

- ◆I/O port (11 pins)

- I/O 3ports 11pins (all ports are programmable I/O)

- ♦Interval Timer (14 stages)

- ◆Hold function

Battery/Capacitor back-up

- ◆Clock generator

- Ceramic resonator / RC oscillation (mask option)

- ◆Real Time Emulator: BM4221A

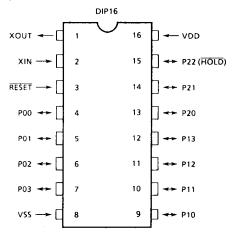

## PIN ASSIGNMENT (TOP VIEW)

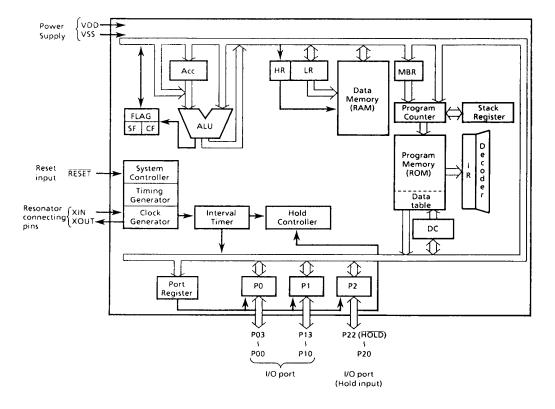

### **BLOCK DIAGRAM**

# PIN FUNCTION

| PIN NAME               | INPUT/OUTPUT | FUNCTION                                                                                |                                  |  |  |  |

|------------------------|--------------|-----------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| P03 - P00              | 40           | 4-bit programmable I/O ports with latch, input/output mode can be specified by          |                                  |  |  |  |

| P13 - P10              | 1/0          | [MOV A, P] instruction.                                                                 |                                  |  |  |  |

| P22 (HOLD) I/O (INPUT) |              | 3-bit programmable I/O port with latch.  Hold request/release signal input              |                                  |  |  |  |

| P21                    |              | The four input/output modes can be selected                                             | suith an I/O anntant instruction |  |  |  |

| P20                    | 1/0          | The four input/output modes can be selected with an I/O control instruction [MOV A, P]. |                                  |  |  |  |

| XIN                    | INPUT        | Resonator connecting pins.                                                              |                                  |  |  |  |

| XOUT                   | OUTPUT       | For inputting external clock, XIN is used and 2                                         | (OUT is opened.                  |  |  |  |

| RESET                  | INPUT        | Reset signal input                                                                      |                                  |  |  |  |

| VDD                    |              | + 5V                                                                                    |                                  |  |  |  |

| vss                    | Power Supply | 0V (GND)                                                                                |                                  |  |  |  |

### **OPERATIONAL DESCRIPTION**

#### 1. SYSTEM CONFIGURATION

- (1) Program Counter (PC)

- (2) Memory Bank Register (MBR)

- (3) Stack Register

- (4) Data Counter (DC)

- (5) Program Memory (ROM)

- (6) H Register(HR), L Register (LR)

- (7) Data Memory (RAM)

- (8) ALU, Accumulator

- (9) Flags

- (10) Clock Generator, Timing Generator

- (11) I/O Ports

- a. Port Register (PR)

- (12) Interval Timer

- (13) Hold Controller

- (14) Reset Circuit

Concerning the above component parts, the configuration and functions of hardwares are described.

#### 2. INTERNAL CPU FUNCTION

### 2.1 Program Counter (PC)

The program counter is a 10-bit binary counter which indicates the address of the program memory storing the next instruction to be executed. Normally, the PC is incremented every time the instruction is fetched. When a branch instruction or a subroutine instruction has been executed the specified values listed in Table 2-1 are set to the PC. The PC is initialized to "0" during reset.

The PC can directly address a 1024-byte address space. However, with the branch and subroutine call instructions, the following points must be considered:

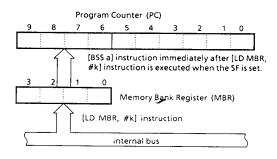

(1) Branch instruction [BSS a], [LD MBR, #k] In executing [BSS a] instruction, when the branch condition is satisfied (SF = 1), the value specified in the instruction is loaded to the lower 6 bits of the after first incrementing the PC. That is, [BSS a] becomes the in-page branch instruction. When [BSS a] is stored at the last address of the page, the upper 4 bits of the PC point the next page, so that branch is made to the next page.

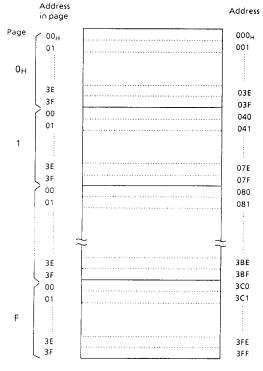

Figure 2-1. Configuration of Program Memory

In addition, branching to the entire program memory space is possible when SF = 1 by executing [BSS a] instruction immediately after [LD MBR, #k] instruction. At that time, the contents of the memory bank register (MBR) are loaded to the upper 4 bits of the PC.

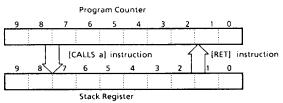

### (2) Subroutine call instruction [CALLS a]

In executing [CALLS a] instruction, the value specified by the instruction is loaded to the PC after the contents of the PC are saved to the stack register. The entry address of the subroutine should be an even number address within the range of  $002_{\rm H}$  through  $01E_{\rm H}$ .

|       | Instruction     |           |                                                            |          | Program Counter (PC) |                 |                            |                                             |                                             |                   |                 |                 |         |   |

|-------|-----------------|-----------|------------------------------------------------------------|----------|----------------------|-----------------|----------------------------|---------------------------------------------|---------------------------------------------|-------------------|-----------------|-----------------|---------|---|

|       | or<br>Operation | Condition |                                                            |          | Page Assignment      |                 | Address assignment in page |                                             |                                             |                   |                 |                 |         |   |

| L     | Operation       |           |                                                            | PC9      | PC <sub>8</sub>      | PC <sub>7</sub> | PC <sub>6</sub>            | PC <sub>5</sub>                             | PC <sub>4</sub>                             | PC <sub>3</sub>   | PC <sub>2</sub> | PC <sub>1</sub> | PCo     |   |

| 0 -   | LD MBR, #k      | SF = 1    | satisfied) contents of MBR immediate data specified by the |          |                      |                 |                            |                                             | the inst                                    | ruction           |                 |                 |         |   |

| u c t | BSS a           | SF = 0    | (Branch cond<br>not satisfied)                             |          |                      |                 |                            | ·                                           |                                             | + 2               |                 |                 |         |   |

| str   | SF = 1          | SF = 1    | Lower 6-bit<br>address                                     | ≠ 111111 | hold                 |                 |                            | immediate data specified by the instruction |                                             |                   |                 | ruction         |         |   |

| -     |                 | 31 = 1    | Lower 6-bit<br>address                                     | = 111111 |                      | + 1             |                            |                                             | immediate data specified by the instruction |                   |                 |                 | ruction |   |

| 0 0   |                 | SF = 0    |                                                            |          | + 1                  |                 |                            |                                             | · · · · · · · · · · · · · · · · · · ·       |                   |                 |                 |         |   |

| t ior | CALLS a         |           |                                                            |          | 0                    | 0               | 0                          | 0                                           | 0                                           | immed<br>instruct |                 | specified       | by the  | 0 |

| D O   | RET             |           |                                                            |          |                      | return addres   |                            |                                             | ess restored from stack register            |                   |                 |                 |         |   |

| E x ( | Others          |           |                                                            |          |                      |                 |                            |                                             |                                             | + 1               | -               |                 |         |   |

|       | Reset           |           |                                                            |          | 0                    | 0               | 0                          | 0                                           | 0                                           | 0                 | 0               | 0               | 0       | 0 |

Table 2-1. Configuration and Status change of Program Counter

## 2.2 Memory Bank Register (MBR)

The memory bank register is a 4-bit register used only for writing to specify pages when branching to the entire program memory space.

Specified values are loaded to the MBR by [LD MBR, #k] instruction. The contents of the MBR are loaded to the upper 4 bits of the PC only when [BSS a] instruction is executed immediately after [LD MBR, #k] instruction. If another instruction is executed after [LD MBR, #k], followed by [BSS a], the contents of the MBR are not loaded to the PC.

Figure 2-2. Operation of Memory Bank Register

## 2.3 Stack Register (STACK)

The stack register is a 10-bit register used to save the contents of the PC (return address) before jumping to a subroutine when the [CALLS a] instruction is executed.

One level subroutine can be used. If there are two calls, the second return address is saved but the first return address is lost.

When returning from a subroutine, contents of the STACK are restored to the PC by [RET] instruction.

Example: When [CALLS a] instruction is stored at address 08EH, "08FH" is saved to the STACK when this instruction is executed. The contents of the STACK (08FH) are restored to the PC by [RET] instruction.

Figure 2-3. Operation of Stack Register

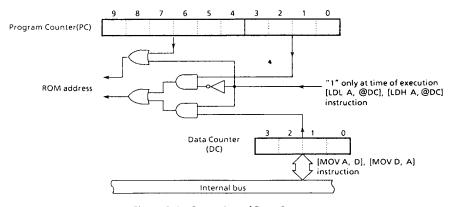

### 2.4 Data Counter (DC)

The data counter is a 4-bit register to specify addresses when fixed data stored in the data table of the program memory (ROM) are read out.

In addition to a function for transferring data from accumulator, the DC also has increment and decrement functions; therefore, it can also be used as a general-purpose register.

The fixed data can be read out using the table look-up instructions.

## (1) Table look-up instructions [LDL A,@DC], [LDH A,@DC]

The table look-up instructions read either the upper 4 bits or the lower 4 bits of the fixed data stored at the address specified by the data counter (DC) and stores them into the accumulator. [LDL A,@DC] instruction reads the lower 4 bits, and [LDH A,@DC] instruction reads the upper 4 bits.

When the table look-up instruction is executed, the lower 4 bits of the ROM address are the contents of the data counter and all of the upper 6 bits become "1".

Consequently, the final 16 bytes ( $1FO_H$ - $1FF_H$  for the 42C40 and  $3FO_H$ - $3FF_H$  for the 42C60) of the program memory are specified by the DC and can also be used as fixed data.

Example: If the contents of the DC is "6" and the contents of program memory address 3F6H is "3EH": "EH" will be stored to the accumulator when [LDL A,@DC] instruction is executed and "3H" is stored to the accumulator when [LDH A,@DC] instruction is executed.

Figure 2-4. Operation of Data Counter

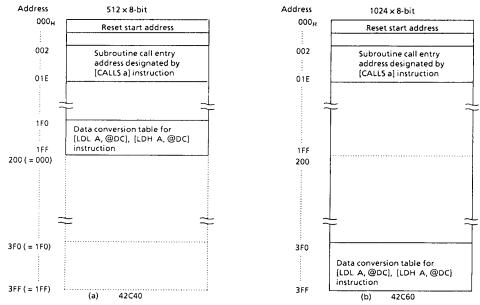

#### 2.5 Program Memory (ROM)

The 42C40 has  $512 \times 8$  bits (addresses  $000_H$  through  $1FF_H$ ) of program memory (mask ROM), the 42C60 has  $1024 \times 8$  bits (addresses  $000_H$  through  $3FF_H$ ).

On the 42C40, no physical program memory exists in the address range 200<sub>H</sub> through 3FF<sub>H</sub>. However, if this space is accessed by program, the most significant bit of each address is always regard as "0" and the contents of the program memory corresponding to the address 000<sub>H</sub> through 1FF<sub>H</sub> are read.

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the contents of the PC. The fixed data can be read by using the table look-up instructions.

### 2.5.1 Program Memory Map

Figure 2-5 shows the program memory map. Address  $000_{\rm H}$  through  $01E_{\rm H}$  and  $3F0_{\rm H}$  through  $3FF_{\rm H}$  ( $1F0_{\rm H}$  through  $1FF_{\rm H}$  for the 42C40) of the program memory are also used for special purposes.

Example : When the data at address  $3F6_H$  are read out and stored to the accumulator with the table look-up instruction, the data at address  $1F6_H$  will actually be stored. That is, the data table for the 42C40 is located at addresses  $1F0_H$  through  $1FF_H$ .

Figure 2-5. Program Memory Map

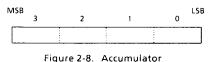

## 2.6 H Register (HR), L Register (LR)

The H register is a 1-bit register and the L register is a 4-bit register. The H and L registers form a pair (HL) and are used as the pointer for specifying data memory (RAM) addresses. The L register can also be used as a general-purpose register.

The data memory is configured in 1-page, 16-word (1 word = 4 bits) units. The H register specifies pages and the L register specifies addresses within the page.

### 2.7 Data Memory (RAM)

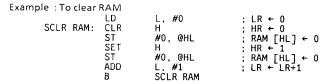

The 42C40/60 have  $32 \times 4$  bits (addresses  $00_H$  through  $1F_H$ ) of the data memory (RAM). Figure 2-6 shows configuration of HR, LR and data memory.

The data memory is addressed in one of the two ways (addressing modes):

(1) Register-indirect addressing mode

In this mode, a page is specified by the H register and an address in the page by L register.

Example: To write immediate data "BH" to address 1EH in the RAM.

SET H ;  $HR \leftarrow 1$ LD L, #0EH ;  $LR \leftarrow E_H$ ST #0BH, QHL ;  $RAM [1E_H] \leftarrow B_H$

(2) Direct addressing mode

The address of 8 words on page 0 of the data memory can be specified directly in the lower 3 bits of the instruction field. The transfer of data to the accumulator with [LD A, x] and [ST A, x] instructions is executed with 1 byte without being affected by the HL register pair.

Example: To load the contents of data memory address 05H into the accumulator.

LD A, 05H ; Acc  $\leftarrow$  RAM [05<sub>H</sub>]

When power-on is performed, the contents of the RAM become unpredictable, so that they must be initialized by the initialization routine.

Figure 2-6. Configuration of HR, LR and Data Memory

### 2.8 ALU and Accumulator

### 2.8.1 Arithmetic / Logic Unit (ALU)

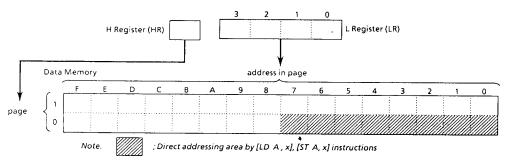

The ALU performs the arithmetic and logic operations specified by instructions on 4-bit binary data and outputs the result of the operation, the carry information (C), and the zero detect information (Z).

(1) Carry information (C)

The carry information indicates a carry-out from the most significant bit in an addition. A subtraction is performed as addition of two's complement, so that, with a subtraction, the carry information indicates that there is no borrow to the most significant bit.

#### (2) Zero detect information (Z)

This information is "1" when the logic operation result or the input data is "0000g".

Example: The carry information (C) and zero detect information (Z) for 4-bit operations.

| Operation |          |       |   | Result                  | C | Z |

|-----------|----------|-------|---|-------------------------|---|---|

| 4         | +        | 2     | = | 6                       | 0 | _ |

| 7         | +        | 9     | = | 0                       | 1 | - |

| 8         | _        | 1     | - | 7                       | 1 | - |

| 5         | -        | 8     | = | -3 (1101 <sub>B</sub> ) | 0 | - |

| 6         | V        | 9     | = | FH                      | - | 0 |

| 2         | $\wedge$ | $C_H$ | = | 0                       | - | 1 |

Note. C<sub>in</sub> indicates the carry input specified by instruction.

Figure 2-7. ALU and Flags

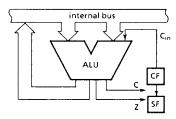

# 2.8.2 Accumulator (Acc)

The accumulator is a 4-bit register used to hold source data or results of the operations and data manipulations.

## 2.9 Flags (FLAG)

There are a carry flags (CF) and a status flags (SF) which can be set and cleared under conditions specified by instructions. During reset, the SF is initialized to "1", the CF is not affected.

#### (1) Carry Flag (CF)

The CF holds the carry information (C) from the ALU when an addition or subtraction instruction involving a carry is executed. Also, CF manipulation instructions can be set to "1" or cleared to "0".

- ① Addition/substruction with carry instructions [ADDC A, @HL], [SUBRC A, @HL]

The CF becomes the input (C<sub>in</sub>) to the ALU to hold the carry information (carry/non-borrow).

- ② Carry flag manipulation instruction [SET CF], [CLR CF]

The CF is set to "1" by [SET CF], and is cleared to "0" by [CLR CF] instruction.

- (3) Carry flag test instructions [TESTP CF] The CF is not affected by this instruction.

#### (2) Status Flag (SF)

The SF provides the branch condition for a branch instruction. Branch is performed when this flag is set to "1". Normally the SF is set to "1", so that any branch instruction can be regarded as an unconditional branch instruction. When a branch instruction is executed upon set or clear of the SF according to the condition specified by an instruction, this instruction becomes a conditional branch instruction.

The SF and Branch instruction Example: ADD A, #1 ; Acc ← Acc + 1 BSS SLAB1 ; Conditional branch (Branches if carry-out occurs by the operation immediately before.) A. @HL ; Acc ← RAM [HL] LD ; Unconditional branch (The SF is set to "1" by BSS SLAB2 the instruction immediately before.)

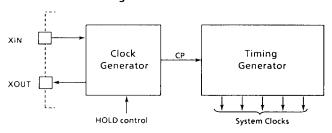

## 2.10 Clock Generator and Timing Generator

Figure 2-9. Clock Generator and Timing Generator

#### 2.10.1 Clock Generator

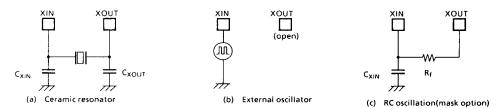

The clock generator is the basic clock (CP) generation circuit used as reference for the system clock supplied to the CPU and peripheral hardware. The basic clock can easily be obtained by connecting an oscillator to the XIN and XOUT pins (RC oscillation is also possible, depending on the mask option). Input from an external clock is also possible.

Figure 2-10. Example of Oscillator Connection

### 2.10.2 Timing Generator

The timing generator produces the system clocks from basic clock pulse which are supplied to the CPU and the peripheral hardware.

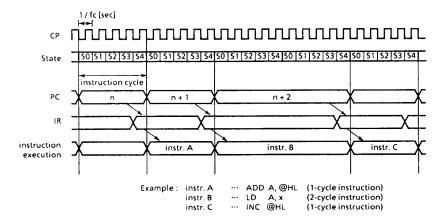

### 2.10.3 Instruction Cycle

The instruction execution and the on-chip peripheral hardware operations are performed in synchronization with the basic clock pulse (CP: fc [Hz]). The smallest unit of instruction execution is called an instruction cycle. The instruction set of the TLCS-42 series consists of 1-cycle instructions and 2-cycle instructions. The former requires 1 cycle for their execution; the latter, 2 cycles. Each instruction cycle consists of 5 states (S0 through S4). Each state consists of one basic clock pulse, and the instruction cycle time is 5/fc [sec]. Figure 2-11 shows CPU basic operation.

Figure 2-11. Instruction Cycle

# 3. PERIPHERAL HARDWARE FUNCTION

#### 3.1 Ports

Input/output instructions (4 types) are used for data transfer to external circuits and for internal circuits control.

(i) I/O port ; Data transfer with external circuit

② Command register ; Control of internal circuit

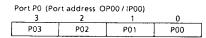

There are two types of ports to which the port addresses  $00_H$ - $05_H$  are assigned. Any of these ports can be selected by specifying the address using an input/output instruction. Input/Output selection of programmable input/output port is controlled by the port register.

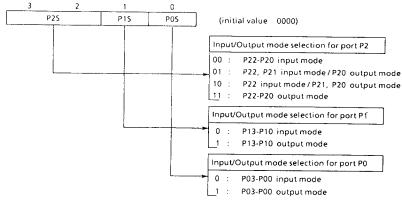

# 3.1.1 Port Register (PR)

The port register is a 4-bit dedicated register for writing and which selects the input/output modes of the programmable input/output ports.

The P0, P1 and P2 ports of the TLCS-42 CMOS series are programmable I/O ports, so data must be loaded to the port register and the I/O mode must be selected by executing the I/O control instruction [MOV A, P]. Also, the port register is initialized to "0" during reset. Consequently, all of the programmable I/O ports are set input mode until the I/O control instruction is executed.

Example: Sets ports P03-P00, P22, P21 to input mode, and P13-P10, P20 to output mode.

LD A, #0110B ;  $PR \leftarrow 0110_B$  MOV A, P

Port Register (PR) 3 2

Figure 3-1. Port Register and Control of programmable I/O ports

#### 3.1.2 I/O Ports

The 42C40/60 have 3 I/O ports (11 pins) each as follows:

(1) P0, P1 ; 4-bit programmable I/O

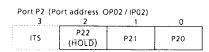

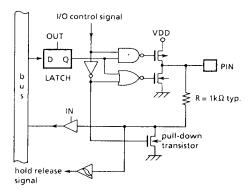

② P2 ; 3-bit programmable I/O ( P22 pin is shared by hold request/release signal input

pin.)

Output data are held by the latch when the output instructions [OUT A, %p] and [OUT @HL, %p] are executed, regardless of the I/O mode of the port. There is no input latch so external input data are either held externally until read, or are read several times before processing, when necessary.

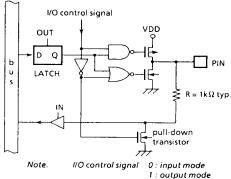

(1) Ports P0 (P03-P00), P1 (P13-P10), P2 (P22-P20)

Ports P0, P1 and P2 are programmable input/output ports. P0 and P1 are 4-bit ports, and P2 is a 3-bit port.

There are 16 I/O modes which can be selected by programs. When an output instruction is executed in one of the input modes, the data are merely held by the latch and are not output to a pin; however, the latched data can be output to a pin by executing the input/output control instruction. The latch is initialized to "1" during reset.

P22 pin is also used as the hold operation release signal input pin (HOLD); therefore, it is necessary to set an input mode before starting a hold operation. Hysteresis input is used for the hold operation release signal.

The highest bit (P23) of port P2 is not included but interval timer output (ITS) is read when an input instruction is executed.

Figure 3-3. Circuitry of programmable I/O port

Port P1 (Port address OP01/IP01)

3 2 1 0

P13 P12 P11 P10

Figure 3-2. Ports P0, P1, P2

Figure 3-4. Circuitry of P22 (HOLD) pin

### 3.1.3 I/O Timing

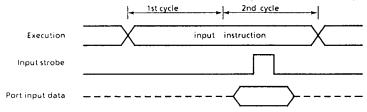

#### (1) Input timing

External data is read from an input port or an I/O port in the S1 state of the second instruction cycle during the input instruction (2-cycle instruction) execution. This timing cannot be recognized from the outside, so that the transient input such as chattering must be processed by program.

Figure 3-5. Input Timing

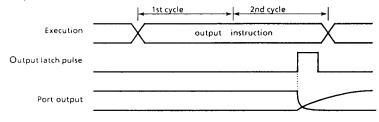

### (2) Output timing

Data is output to an output port or an I/O port in the \$3 state of the second instruction cycle during the output instruction (2-cycle instruction) execution. The port changes at the rise of the output latch pulse.

Figure 3-6. Output Timing

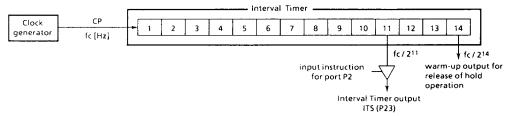

#### 3.2 Interval Timer

The interval timer divides the basic clock (CP) with a 14-stage binary counters and an output constant frequency pulses. The following are interval applications. The intirval timer is cleared to "0" when the hold operation mode is released.

- ① Generation of an interval time with a fixed frequency (the interval timer output)

- ② Generation of warm-up time at release of the hold operating mode

### 3.2.1 Interval Timer Output

Interval timer produces pulse output which is the basic clock (frequency: fc) divided by 2048. These are approximately 1ms pulses when oscillation frequency is fc = 2MHz.

Interval timer output is transferred to the accumulator or data memory as port P2, bit 3 (P23) data by the port P2 input instructions [IN %IP02, A] and [IN %IP02, @HL].

Figure 3-7. Interval Timer

| example: | ro wait un | tii the inter | vai timer output da | ita are changed.                        |

|----------|------------|---------------|---------------------|-----------------------------------------|

|          |            | IN            | %IP02,@HL           | ; RAM [HL] ← IP02                       |

|          | SWAIT :    | IN            | %IP02,A             | ; Acc ← IPO2                            |

|          |            | XOR           | A,@HL               | ; The MSB of the Acc and of the RAM are |

|          |            | ADD           | A,#8                | compared and the results transferred    |

|          |            |               |                     | to the SF.                              |

|          |            | В             | SWAIT               | ; When the results match, there is a    |

branch to SWAIT.

#### 4. POWER SAVING FUNCTION

The 42C40/60 have the hold operating mode intended to save the power.

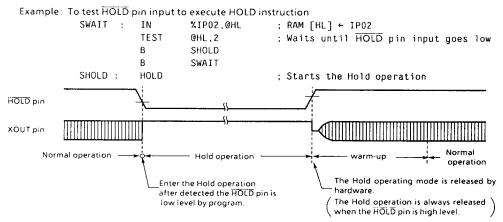

## 4.1 Hold Operating Mode

The hold function stops system operation and holds the internal status active just before stop. Hold operation controlled by the HOLD pin and HOLD instruction. The HOLD pin is also used as the P22 pin.

### 4.1.1 Start of Hold operating Mode

Hold operation is started by executing the HOLD instruction and continues as long as the HOLD pin is at low level. The following statuses are held during hold operation:

- ① Oscillation and all internal operations are stopped.

- ② The interval timer is cleared to "0".

- 3 The status of the data memory, register and port latch are maintained as they were just before the hold operation, except that the SF is set to "1".

- The PC holds two addresses ahead of the HOLD instruction. After hold operation is released, the instruction following the HOLD instruction is executed.

# 4.1.2 Release of Hold Operating Mode

The hold operation can be released to assume to normal operation by inputting the high level to the HOLD pin. Hold operation is released in the following sequence:

- (1) Oscillation is started.

- ② Warming up allows sufficient time for oscillation to stabilize. During warm-up, internal operation stops. The warm-up time is 213/fc [sec].

- 3 When the warm-up time has elapsed, normal operation resumes with the instruction following the HOLD instruction.

Note: The warm-up time is obtained by dividing the basic clock with an interval timer; therefore, when there is fluctuation of the oscillation frequency when a hold operation is released, the warm-up time contains an error. Thus, it is necessary to set an approximate warm-up time value.

In addition, hold operation can also be released by setting the RESET pin to low level. In this case, the normal reset operation is performed immediately and normal operation resumes as soon as the reset mode is released; therefore, it is necessary to keep the RESET pin at low level and continue warm-up until oscillation stabilizes.

Note: The following cautions must be observed when releasing a hold operation with a low hold voltage. Before releasing a hold operation, it is necessary to increase the power supply voltage to the specified voltage range. The RESET pin is at high level at this time and increases together with the power supply voltage. If an external time constant circuit is connected at this time, the RESET pin input voltage will increase at a slower pace than the power supply voltage; therefore, if the RESET pin input voltage drops below the non-inverted high level input voltage of the RESET pin input (hysteresis input), there is danger of a reset occurring.

Hold operation will not start even if the Hold instruction is executed with the  $\overline{\text{HOLD}}$  pin input at high level. Instead, the release (warm-up) sequence will start immediately. The warm-up time in this case is unstable and varies between 0 and 213/fc [sec]. Consequently, when the HOLD instruction is executed, it is necessary to check if the  $\overline{\text{HOLD}}$  pin input is at low level (hold operation request).

Figure 4-1. Hold operating mode

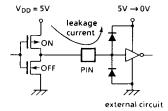

Note: Power consumption by the oscillation circuit and internal hardware is reduced during hold operation but power consumption by external circuit interfaces is not directly related to hold operation hardware operation; therefore, caution must be observed in system design and interface circuit design. For example, if the power supply voltage of an external circuit is dropped to 0V and the output is at high level, as shown in Figure 4-3, current may flow through the parasitic diodes of the external circuit in some cases. The relevant pin must be set to low level

Figure 4-2. External circuit interface during the Hold operating mode

### 5. RESET FUNCTION

The internal status is initialized if a reset action is performed when the power supply voltage is within the operating voltage range and the RESET pin is held at low level for a minimum of 3 instruction cycles (15 basic clocks) while oscillation is stable.

When the  $\overline{\text{RESET}}$  pin input goes high, the reset is released and program execution starts from address  $000_{H}.$

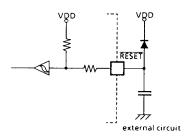

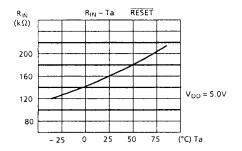

The  $\overline{RESET}$  pin is hysteresis input with a pull-up resistor (typ.160k $\Omega$ ) and simple power-on-reset can be done by

Figure 5-1. Simplified Power-On-Reset circuit

| On-chip h       | ardware | Initial value     | On-chip hardware        | Initial value            |

|-----------------|---------|-------------------|-------------------------|--------------------------|

| Program Counter | r (PC)  | 000н              |                         |                          |

| Status Flag     | (SF)    | 1                 | Output Latch (I/O port) | Refer to "I/O Circuitry" |

| Port Register   | (PR)    | 0000 <sub>B</sub> |                         | "S circuity              |

Table 5-1. Initialization of Internal states by Reset action

# **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0V)$

| PARAMETER                       | SYMBOL           | PIN | RATING                         | UNIT |

|---------------------------------|------------------|-----|--------------------------------|------|

| Supply Voltage                  | V <sub>DD</sub>  |     | - 0.5 to 7                     | V    |

| Input Voltage                   | V <sub>IN</sub>  |     | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output Voltage                  | Vout             |     | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output Current (total)          | Σίουτ            |     | 30                             | mA   |

| Power Dissipation [Topr = 85°C] | PD               |     | 300                            | mW   |

| Soldering Temperature (time)    | Tsid             |     | 260 (10sec)                    | τ    |

| Storage Temperature             | T <sub>stg</sub> |     | - 55 to 125                    | r    |

| Operating Temperature           | Topr             |     | - 40 to 85                     | ď    |

RECOMMENDED OPERATING CONDITIONS

$$(V_{SS} = 0V, T_{opr} = -40 \text{ to } 85^{\circ}C)$$

| PARAMETER       | SYMBOL           | PIN                     | CONDITIONS                    | Min.                  | Max.                  | UNIT            |  |

|-----------------|------------------|-------------------------|-------------------------------|-----------------------|-----------------------|-----------------|--|

| Supply Voltage  | V <sub>DD</sub>  |                         |                               | 4.0                   | 6.0                   | V               |  |

| Input High      | V <sub>IH1</sub> | Except Hysteresis Input |                               | V <sub>DD</sub> × 0.7 |                       |                 |  |

| Voltage         | V <sub>IH2</sub> | Hysteresis Input        |                               | V <sub>DD</sub> × 0.8 | V <sub>DD</sub>       | V               |  |

| Input Low       | V <sub>IL1</sub> | Except Hysteresis Input |                               |                       | V <sub>DD</sub> × 0.3 | V               |  |

| Voltage         | V <sub>IL2</sub> | Hysteresis Input        |                               | 0                     | V <sub>DD</sub> × 0.2 |                 |  |

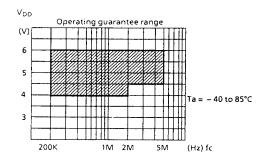

| Clock Frequency | fc               |                         | V <sub>DD</sub> = 4.0 to 6.0V |                       | 2.0                   | · - · · · · · · |  |

|                 |                  |                         | V <sub>DD</sub> = 4.5 to 6.0V | 0.2                   | 5.0                   | MHz             |  |

D.C. CHARACTERISTICS

$(V_{SS} = 0V, T_{opr} = -40 \text{ to } 85^{\circ}C)$

| PARAMETER                                           | SYMBOL          | PIN                | CONDITIONS                                     | Min.  | Тур.  | Max. | UNIT |

|-----------------------------------------------------|-----------------|--------------------|------------------------------------------------|-------|-------|------|------|

| Hysteresis Voltage                                  | V <sub>HS</sub> | Hysteresis Voltage |                                                | -     | 0.3   | _    | V    |

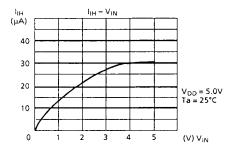

| Input High Current                                  | Чн              | Ports P0, P1, P2   | V <sub>DD</sub> = 5V, V <sub>iN</sub> = 5V     | 15    | 30    | 80   | μА   |

| Input Resistance                                    | R <sub>IN</sub> | RESET              |                                                | 65    | 160   | 340  | ΚΩ   |

| Output High Voltage                                 | V <sub>OH</sub> |                    | V <sub>DD</sub> = 5V, I <sub>OH</sub> = -5μA   | 4.7   | 4.9   | -    | v    |

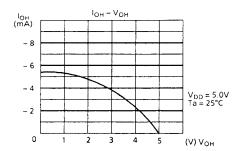

| Output High Current                                 | 10н             | Ports P0, P1, P2   | V <sub>DD</sub> = 4V, V <sub>OH</sub> = 2.4V   | - 1.0 | - 4.5 | -    | mA   |

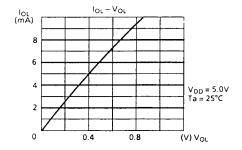

| Output Low Current                                  | lor             | 1                  | V <sub>DD</sub> = 4.5V, V <sub>OL</sub> = 0.4V | 1.6   | 5.0   | _    | mA   |

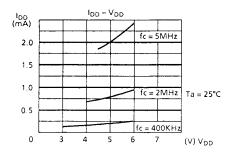

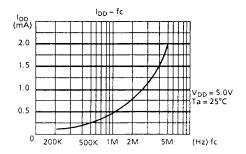

| Supply Current<br>(In the Normal<br>operating mode) | I <sub>DD</sub> |                    | V <sub>DD</sub> = 6V, fc = 2MHz                | _     | 0.8   | 3.0  | mA   |

| Supply Current<br>(In the HOLD<br>operating mode)   | Торн            | ı                  | V <sub>DD</sub> = 6V                           | -     | 0.1   | 5.0  | μΑ   |

Note 1. Typ. values shows those at  $V_{DD}$  = 5V,  $T_{opr}$  = 25°C.

Note 2. Supply Current in the Normal operating mode : RESET pin is OV, and XOUT pin and ports are opened in the external

clock operation.

Note 3. Supply Current in the Hold operating mode

: All pins except the power supply pins (VDD, VSS) are opened.

A.C. CHARACTERISTICS

$(V_{SS} = 0V, T_{opr} = -40 \text{ to } 85^{\circ}C)$

| PARAMETER                    | SYMBOL          | ,                                 | CONDITIONS                    | Min. | Тур. | Max. | UNIT |

|------------------------------|-----------------|-----------------------------------|-------------------------------|------|------|------|------|

| Instruction Cycle Time       |                 | $V_{DD} = 4.0 \text{ to } 6$      | V <sub>DD</sub> = 4.0 to 6.0V |      |      | 25   | μς   |

|                              | t <sub>cy</sub> | V <sub>DD</sub> = 4.5 to 6.0V     |                               | 1.0  | _    |      |      |

| High level Clock pulse Width | twch            | V <sub>IN</sub> = V <sub>IH</sub> | For external                  |      |      |      |      |

| Low level Clock pulse Width  | twcL            | V <sub>IN</sub> = V <sub>IL</sub> | clock operation               | 100  | _    | _    | ns   |

RECOMMENDED

$(V_{SS} = 0V, V_{DD} = 4.0 \text{ to } 6.0 \text{ V}, T_{opt} = -40 \text{ to } 85^{\circ}\text{C})$

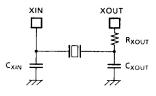

### (1) Ceramic Resonator

5MHz (V<sub>DD</sub> = 4.5 to 6.0V)

CSA5.00MG (MURATA) CXIN = CXOUT = 30pF

2MHz

CSA2.00MG (MURATA)  $C_{XIN} = C_{XOUT} = 100pF$

XOUT : C<sub>XOUT</sub>

1MHz

CSB1000D (MURATA)  $C_{XIN} = C_{XOUT} = 330pF$

455KHz

CSB455E (MURATA)

$C_{XIN} = C_{XOUT} = 220pF$ ,  $R_{XOUT} = 5.6K\Omega$

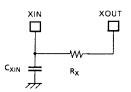

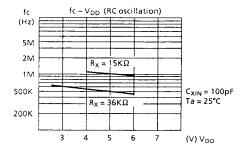

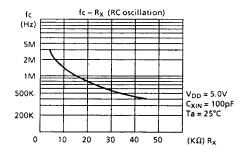

### (2) RC oscillation

1MHz typ.

$R_X = 15K\Omega$ ,  $C_{XIN} = 100pF$

500KHz typ.

$R_X = 36K\Omega$ ,  $C_{XIN} = 100pF$

### TYPICAL CHARACTERISTICS

## INPUT/OUTPUT CIRCUITRY

### (1) Control pins

Input/Output circuitries of the 42C40/60 control pins are shown below.

Oscillation type can be chosen by mask option either a ceramic resonator (external clock input) or an RC oscillator.

| CONTROL PIN | 1/0    | CIRCUITRY                                                                              | REMARKS                                                                                                                                                                             |

|-------------|--------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN         | INPUT  | Option : Ceramic resonator or External clock input  OSC. enable  R  R  R  R  XIN  XOUT | Resonator connecting pins $R = 1K\Omega \ typ.$ $R_f = 1M\Omega \ typ.$                                                                                                             |

| хоит        | OUTPUT | Option: RC oscillation  OSC. enable  R R R R R I XIN XOUT                              | Resonator connecting pins $ \begin{array}{ll} \text{Hysteresis input} \\ \text{R} &= 1 \text{K}\Omega \ \text{typ.} \\ \text{R}_{f} &= 1 \text{M}\Omega \ \text{typ.} \end{array} $ |

| RESET       | INPUT  | QVDD  R <sub>IN</sub> R  R  R                                                          | Hysteresis input $ \begin{array}{ll} \text{Pull-up resistor} \\ \text{Rin} &= 160 \text{K}\Omega \text{ typ.} \\ \text{R} &= 1 \text{K}\Omega \text{ typ.} \end{array} $            |

(2) I/O ports All I/O ports of 42C40/60 are programmable I/O. I/O mode can be specified by [MOV A,P] instruction.

| PORT           | 1/0 | CIRCUITRY                                        | INITIAL<br>STATE | REMARKS                                                                                                  |

|----------------|-----|--------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|

| P0<br>P1<br>P2 | VO  | WO control signal OVDD OVDD Pull-down transistor | INPUT            | Programmable I/O port  Input mode: Input with pull-down transistor  Output mode: push-pull  R = 1KΩ typ. |