# NMB Semiconductor

#### **FEATURES**

- 262,144 words x 1 bit organization

- Ultra high speed, 60, 70, 80, 100 ns RAS access times over full V<sub>CC</sub> (4.5V to 5.5V) and temperature (0°C to 70°C) ranges

- Eliminates traditional DRAM multiplexed address timing constraints

- Advanced field shield isolated

CMOS process optimized for speed

- Inputs and outputs are CMOS and TTL compatible

- Extended RAS active time to facilitate multiple accesses within a row

- Low power (CMOS input levels) Standby: 12.5 mW

- Active: 275 mW at 100ns access time

- 4.4 ms, 256 cycle refresh

- Single 5V ± 10% supply

- JEDEC standard pinout

- CAS-before-RAS refresh as well as RAS-Only refresh

PLASTIC PACKAGE

CERAMIC SIDEBRAZED PACKAGE

PALSTIC LEADED CHIP CARRIER

#### DESCRIPTION

The AAA2800 is a 256K x 1 Dynamic RAM product designed and processed for ultra high performance. The AAA2800 is fabricated with advanced CMOS technology resulting in high speed, low power and extremely wide operating margins.

The AAA2800 features a Static Column Decode mode of operation, its static column-circuitry can keep the row operation dynamic while control the power consumed in the static circuitry and realize the low power dissipation.

The AAA2800 chip design uses asynchronous column address decoding as well as on-chip transparent row address latch which permits an extremely short row address capture time (4ns; 2ns set-up and 2ns hold). This relieves the system designer of the constraint of timing overhead associated with address multiplexing, and makes it possible to achieve system  $\overline{\text{RAS}}$  access times as fast as 60 ns which allows interfacing to the next generation of high speed microprocessors.

The AAA2800 is a cost effective VLSI DRAM for applications that demand high density, reliability, high performance and wide operating margins.

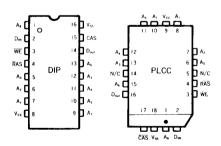

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| A0-A8 | ADDRESS INPUTS        |

|-------|-----------------------|

| CAS   | COLUMN ADDRESS STROBE |

| RAS   | ROW ADDRESS STROBE    |

| Din   | DATA IN               |

| Dout  | DATA OUT              |

| WE    | WRITE ENABLE          |

| Vcc   | + 5V SUPPLY INPUT     |

| Vss   | GROUND                |

#### **LOGIC SYMBOL**

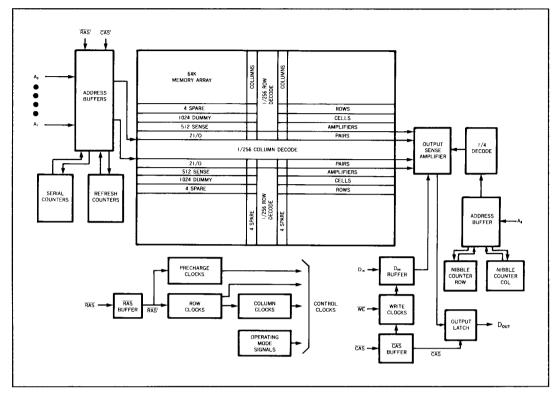

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS\***

| RATING                                                 | SYMBOL                       | VALUE      | UNIT |

|--------------------------------------------------------|------------------------------|------------|------|

| Voltage on V <sub>CC</sub> Relative to V <sub>SS</sub> | V <sub>CC</sub><br>Vin, Vout | - 1 to 7   | V    |

| Storage Temperature (Ceramic)                          | Tstg 1                       | -65 to 150 | °C   |

| Storage temperature (Plastic)                          | Tstg 2                       | -55 to 125 | °C   |

| Power Dissipation                                      | Pd                           | 1.0        | W    |

| Data out Current (Short Circuit)                       | lout                         | 50         | mA   |

\*Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC OPERATING CONDITIONS a.b.

| SYMBOL | PARAMETER                     | MIN   | NOM | MAX | UNITS | NOTES     |

|--------|-------------------------------|-------|-----|-----|-------|-----------|

| Vcc    | Supply Voltage                | 4.5   | 5.0 | 5.5 | V     |           |

| Vss    | Supply Voltage                |       | 0   |     | V     |           |

| VIH    | Logic "1" Voltage             | 2.4   |     | 6.5 | V     |           |

| ViL    | Logic "0" Voltage             | - 1.0 |     | 0.8 | V     |           |

| TA     | Ambient Operating Temperature | 0     |     | 70  | °C    | Still Air |

#### Note:

- a: All voltage values in this data sheet are with respect to V<sub>SS</sub>.

- b: After power-up, a pause of 1 ms followed by eight initialization memory cycles is required to achieve proper device operation.

Any interval greater than 4.4ms with  $\overline{RAS}$  inactivity requires eight reinitialization cycles to achieve proper device operation.

# DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 5.0V $\pm$ 10%)

| SYMBOL           |                                                | PARAMETER                                                                    |                                    | MIN         | MAX    | UNIT | NOTES |  |

|------------------|------------------------------------------------|------------------------------------------------------------------------------|------------------------------------|-------------|--------|------|-------|--|

|                  |                                                |                                                                              | 2800-06                            | _           | 75     | mA   |       |  |

|                  | Average Power Supply Operating Current 2800-07 |                                                                              |                                    |             | - 70 m |      |       |  |

| Icc1             | (RAS, CAS, Addro                               | ess Cycling; $t_{RC} = t_{RCmin}$ )                                          | _                                  | 65          | mA     | a    |       |  |

|                  |                                                |                                                                              | _                                  | 55          | mA     | 1    |       |  |

|                  |                                                | All Inputs Stable at CMOS Levels, RAS                                        | $\overline{S} \ge (V_{CC} - 0.4V)$ | _           | 2.5    | mA   | b     |  |

|                  |                                                | RAS = CAS = VIH, DOUT = HIZ                                                  |                                    |             | 3.0    | mA   |       |  |

|                  |                                                | RAS = VIH, CAS = VIL, DOUT = Enable                                          | е                                  | _           | 3.0    | mA   |       |  |

|                  | 01                                             | All Inputs Stable at TTL Levels, RAS≥                                        | 2.4V                               | _           | 4.5    | mA   |       |  |

| ICC2             | Standby Current                                | All Inputs Toggling Between CMOS Le 6.25 MHZ, RAS ≥ (V <sub>CC</sub> - 0.4V) | vels at                            |             | 4.0    | mA   | b     |  |

|                  |                                                | All Inputs (Except RAS) Toggling<br>Between TTL Levels at 6.25 MHz           |                                    | 5.5         | mA     |      |       |  |

|                  | 2800-06                                        |                                                                              |                                    |             | 65     | mA   |       |  |

|                  |                                                |                                                                              |                                    |             | 60     | mA   |       |  |

| I <sub>CC3</sub> |                                                |                                                                              |                                    |             | 55     | mA   | С     |  |

|                  |                                                |                                                                              | _                                  | 45          | mA     |      |       |  |

|                  |                                                | 2800-06                                                                      |                                    |             |        | mA   |       |  |

| laa.             | Average Power S                                | _                                                                            | 30                                 | mA          | 1      |      |       |  |

| ICC4             | $(t_{RSC} = t_{WSC}, bot)$                     |                                                                              | 27                                 | mA          | a      |      |       |  |

|                  |                                                |                                                                              | _                                  | 25          | mA     |      |       |  |

|                  |                                                | 2800-06                                                                      |                                    | 65          | mA     |      |       |  |

| Icc6             | CAS Before RAS                                 | 2800-07                                                                      | _                                  | 60          | mA     | c    |       |  |

| 1006             | (RAS, CAS Cyclin                               | ig; tac = tacmin)                                                            | _                                  | 55          | mA     |      |       |  |

|                  |                                                |                                                                              | _                                  | 45          | mA     |      |       |  |

| lLi              | Input Leakage Cu                               | irrent (Any Input), $0V \le V_{IN} \le 5.5V$ , other                         | - 10                               | 10          | μΑ     |      |       |  |

| llo              | Output Leakage,                                | $D_{OUT} = HiZ, 0V \le V_{OUT} \le 5.5V$                                     |                                    | <b>- 10</b> | 10     | μΑ   |       |  |

| V <sub>OH</sub>  | Output High Volta                              | $lge, l_O = -5.0 mA$                                                         |                                    | 2.4         |        | ٧    |       |  |

| Vol              | Output Low Volta                               | ge, I <sub>O</sub> = 5.0mA                                                   |                                    |             | 0.4    | V    |       |  |

#### Notes:

- a. I<sub>CC</sub> is dependent on output loading and cycle rates. Specified values are obtained with output open.

- b. CMOS levels are defined as  $V_{IH}$  (min)  $\geq$  ( $V_{CC}$  0.4V) and  $V_{IL}$  (max)  $\leq$  0.4V. TTL levels are defined as  $V_{IH}$  (min)  $\geq$  2.4V and  $V_{IL}$  (max)  $\leq$  0.8V.

- c. I<sub>CC</sub> is dependent on cycle rates.

#### **AC TEST CONDITIONS**

| Input Pulse Levels 0 to 3V                         |  |

|----------------------------------------------------|--|

| Input Rise and Fall Times 3ns between 0.8 and 2.4V |  |

| Input Timing Reference Levels 0.8 and 2.4V         |  |

| Output Timing Reference Levels 0.8 and 2.4V        |  |

| Output Load Equivalent to 2 TTL Loads and 50pF     |  |

#### **CAPACITANCE**

| SYMBOL | PARAMETER            | MAX | UNITS | COND |

|--------|----------------------|-----|-------|------|

| Cin    | RAS, CAS, WE         | 6   | pF    | а    |

| CiN    | Input Cap. Addresses | 5   | ρF    | а    |

| Соит   | Output Cap.          | 7   | pF    | a,b  |

#### Note:

- a: Capacitance measured with Boonton Meter

- b:  $\overline{CAS} = V_{IH}$  to disable  $D_{OUT}$

# AC OPERATING CONDITIONS (0°C $\leq$ $T_{A}$ $\leq$ 70°C, $V_{CC}$ = 5V $\pm$ 10%)

|     |                                            | SYMBOL             |      | 2800-06  |          | 2800-07 |                 | 2800-08 |                 | 8 2800-10 |                 |      |       |  |

|-----|--------------------------------------------|--------------------|------|----------|----------|---------|-----------------|---------|-----------------|-----------|-----------------|------|-------|--|

| NO. | PARAMETER                                  | JEDEC              | STD  | MIN      | MAX      | MIN     | MAX             | MIN     | мах             | MIN       | MAX             | UNIT | NOTES |  |

| 1   | Column Address Set-Up (Early Write)        | tAVCL2             | tASC | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | С     |  |

| 2   | Row Address Set-Up                         | tAVRL2             | tASR | 2        |          | 2       |                 | 2       |                 | 2         |                 | ns   |       |  |

| 3   | Column Address to WE Delay                 | tAVWL2             | tawn | 32       |          | 35      |                 | 40      |                 | 45        |                 | ns   | c.g   |  |

| 4   | Output Turn-Off Delay                      | tCH2QZ             | toff |          | 17       |         | 18              |         | 19              |           | 21              | ns   | a     |  |

| 5   | CAS to RAS Precharge                       | tCH2RL2            | tCRP | 3        |          | 3       |                 | 3       |                 | 3         |                 | ns   |       |  |

| 6   | Read Command Hold Time<br>(Reference CAS)  | tCH2WX             | tRCH | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | b     |  |

| 7   | Column Address Hold (Early Write)          | tCL1AX             | tCAH | 6        |          | 7       |                 | 8       |                 | 9         |                 | ns   | С     |  |

| 8   | CAS Pulse Width (Read)                     | tCL1CH1            | tCAS | 11       |          | 12      |                 | 14      |                 | 16        |                 | ns   |       |  |

| 9   | CAS Pulse Width (Write)                    | tCL1CH1            | tcas | 5        |          | 5       |                 | 5       |                 | 5         |                 | ns   |       |  |

| 10  | Data-In Hold Time from CAS (Early Write)   | tCL1DX             | tDH  | 6        |          | 7       |                 | 8       |                 | 9         |                 | ns   | С     |  |

| 11  | CAS Access                                 | tCL1QV             | tCAC |          | 11       |         | 12              |         | 13              |           | 16              | ns   |       |  |

| 12  | RAS Hold Time                              | tCL1RH1            | trsh | 15       |          | 18      |                 | 20      |                 | 25        |                 | ns   |       |  |

| 13  | CAS Setup Time<br>(CAS Before RAS Refresh) | tCL1RL2            | tcsn | 2        |          | 2       |                 | 2       |                 | 2         |                 | ns   |       |  |

| 14  | CAS Write Hold (Reference CAS)             | tCL1WH1            | twch | 5        |          | 5       |                 | 5       |                 | 5         |                 | ns   |       |  |

| 15  | CAS to WE Delay (Read-Modify-Write)        | tCL1WL2            | tcwD | 11       |          | 12      |                 | 13      |                 | 16        |                 | ns   | d     |  |

| 16  | Data Set-Up (Early Write)                  | tDVCL2             | tos  | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | С     |  |

| 17  | Data Set-Up (Late Write)                   | tDVWL2             | tos  | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | С     |  |

| 18  | RAS to Column Address Hold Time            | tRH2AX             | tAH  | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   |       |  |

| 19  | RAS Precharge                              | tRH2RL2            | tRP  | 55       |          | 65      |                 | 75      |                 | 80        |                 | ns   |       |  |

| 20  | Read Command Hold (Reference RAS)          | tRH2WX             | trrh | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | b     |  |

| 21  | Column Address Hold<br>(Reference RAS)     | t <sub>RL1AX</sub> | tAR  | 40       |          | 43      |                 | 45      |                 | 50        |                 | ns   |       |  |

| 22  | Row Address Hold                           | t <sub>RL1AX</sub> | tRAH | 2        | <u> </u> | 2       |                 | 2       |                 | 2         |                 | ns   |       |  |

| 23  | CAS Hold ( CAS-Before-RAS)                 | tRL1CH1            | tchr | 2        |          | 2       |                 | 2       |                 | 2         |                 | ns   |       |  |

| 24  | CAS Hold Time (Early Write)                | tRL1CH1            | tcsH | 40       |          | 43      |                 | 45      |                 | 50        |                 | ns   |       |  |

| 25  | RAS to CAS Delay                           | tRL1CL1            | tRCD | 4        | 45       | 4       | 55              | 4       | 65              | 4         | 80              | ns   | i     |  |

| 26  | Data in Hold Time from RAS                 | t <sub>RL1DX</sub> | tohr | 40       |          | 43      |                 | 45      |                 | 50        |                 | ns   |       |  |

| 27  | RAS Access                                 | tRL1QV             | tRAC |          | 60       |         | 70              |         | 80              |           | 100             | ns   |       |  |

| 28  | RAS Pulse Width                            | tRL1RH1            | tras | 60       | 105      | 65      | 10 <sup>5</sup> | 70      | 10 <sup>5</sup> | 90        | 10 <sup>5</sup> | ns   |       |  |

| 29  | Write Command Hold<br>(Reference RAS)      | tRL1WH1            | twcr | 40       |          | 43      |                 | 45      |                 | 50        |                 | ns   |       |  |

| 30  | RAS to WE Delay (Read-Modify-Write)        | tRL1WL2            | trwD | 60       |          | 70      |                 | 80      |                 | 100       |                 | ns   | d     |  |

| 31  | Random Read-Write Cycle                    | tRL2RL2            | tRC  | 121      |          | 136     |                 | 151     |                 | 176       |                 | ns   |       |  |

| 32  | Read Command Set-Up                        | twH2CL2            | trcs | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | d     |  |

| 33  | Write Command to CAS Lead                  | tWL1CH1            | tcwL | 5        |          | 5       |                 | 5       |                 | 5         |                 | ns   |       |  |

| 34  | Early Write WE Set-Up                      | tWL1CL2            | twcs | 0        |          | 0       |                 | 0       |                 | 0         |                 | ns   | d     |  |

| 35  | Data-In Hold (Late Write)                  | twL1DX             | tDH  | 5        | <u> </u> | 6       |                 | 7       | ļ               | 8         |                 | ns   | С     |  |

| 36  | Write Command to RAS Lead                  | twL1RH1            | tRWL | 13       |          | 15      | ļ               | 17      | ļ               | 22        |                 | ns   |       |  |

| 37  | Write Pulse                                | tWL1WH1            | twp  | 5        |          | 5       |                 | 5       |                 | 5         | <u> </u>        | ns   |       |  |

| 38  | Refresh Period                             | tREF               | tREF | 1        | 4.4      |         | 4.4             |         | 4.4             |           | 4.4             | ms   |       |  |

| 39  | Transition Time (Rise and Fall)            | tτ                 | t⊤   | 2        | 50       | 2       | 50              | 2       | 50              | 2.        | 50              | ns   | e.f   |  |

| 40  | Output Hold from WE                        | t <sub>WL1QX</sub> | tonw | 5        |          | 5       |                 | 5       |                 | 5         | <u> </u>        | ns   |       |  |

| 41  | Column Address Access                      | tAVQV              | taa  | <u> </u> | 32       |         | 35              |         | 40              |           | 45              | ns   | d     |  |

| 42  | Static Column Mode Read Cycle Time         | tAVAV              | trsc | 35       | _        | 40      |                 | 45      |                 | 50        |                 | ns   |       |  |

| 43  | Output Hold from Address                   | taxqx              | toha | 5        |          | 5       |                 | 5       |                 | 5         |                 | ns   |       |  |

| 44  | CAS Precharge                              | tCH2CL2            | tCP  | 5        | ļ        | 5       |                 | 5       |                 | 5         |                 | ns   |       |  |

| 45  | Write Precharge                            | twH2WL2            | twi  | 5        | <u></u>  | 5       | <u></u>         | 5       |                 | 5         |                 | ns   |       |  |

#### AC OPERATING CONDITIONS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 5V $\pm$ 10%)

|     |                                     | SYM                 | SYMBOL |     | 2800-06 |     | 2800-07 |     | 0-08 | 280 | 0-10 | UNIT | NOTES |

|-----|-------------------------------------|---------------------|--------|-----|---------|-----|---------|-----|------|-----|------|------|-------|

| NO. | PARAMETER                           | JEDEC               | STD    | MIN | мах     | MIN | MAX     | MIN | MAX  | MIN | MAX  |      | NOTES |

| 46  | Column Address to WE Hold Time      | twL1AX              | tawn   | 7   |         | 7   |         | 7   |      | 7   |      | ns   | С     |

| 47  | Static Column Mode Write Cycle Time | tWL1WL1             | twsc   | 35  |         | 38  |         | 40  |      | 45  |      | ns   |       |

| 48  | RAS to Column Address Delay Time    | t <sub>RL1AV</sub>  | tRAD   | 4   | 28      | 4   | 35      | 4   | 40   | 4   | 55   | ns   | h     |

| 49  | RMW Cycle Time                      | t <sub>RL2RL2</sub> | tRWC   | 134 |         | 151 |         | 168 |      | 198 |      | ns   |       |

| 50  | Output Data Hold Time from CAS      | tcH1QX              | tон    | 2   |         | 2   |         | 2   |      | 2   |      | ns   |       |

| 51  | CAS Hold time (Read)                | tRL1CH1             | tcsh   | 60  |         | 70  |         | 80  |      | 100 |      | ns   |       |

| 52  | RAS Precharge · CAS Hold Time       | tRH2CL2             | tRPC   | 0   |         | 0   |         | 0_  |      | 0   |      | ns   |       |

| 53  | Write Read Access Time              | twL1QV              | twra   |     | 55      |     | 65      |     | 74   |     | 92   | ns   |       |

| 54  | Write Precharge Access Time         | twH2QVN             | twpA   |     | 11      |     | 12      |     | 13   |     | 14   | ns   |       |

| 55  | Column Address · WE Set Up Time     | tAVWL2              | taws   | 0   |         | 0   |         | 0   |      | 0   |      | ns   |       |

| 56  | Write Command Hold (Reference CAS)  | tCH2WH1             | twnc   | 0   |         | 0   |         | 0   |      | 0   |      | ns   |       |

#### **Notes**

- a. tope is defined as the time at which the output achieves the open circuit condition.

- b. Either t<sub>CH2WX</sub> or t<sub>RH2WX</sub> must be satisfied for a Read cycle.

- c. Address and data set-up and hold times referenced to  $\overline{\text{CAS}}$  (tAVCL2, tCL1AX, tDVCL2, and tCL1DX) are restrictive parameters for Early-Write operations only. Address and data set-up and hold times referenced to  $\overline{\text{WE}}$  (tAVWL2, tDWCL2, and tWL1DX) are restrictive parameters for Read-Modify-Write cycle operations.

- d. twH2CL2, tcL1wL2, and tRL1wL2 are restrictive operating parameters in Read-Write and Read-Modify-Write cycles only. If twL1CL2 ≥ twL1CL2 (min) the cycle is an Early-Write cycle and data will remain open circuit unless WE goes high while CAS and RAS are both low.

- If  $t_{WH2CL2} \ge t_{WH2CL2}$  (min),  $t_{RL1WL2} \ge t_{RL1WL2}$  (min), and  $t_{AVQV} \ge t_{AVQV}$  (min) the cycle is a Read-Write and the data outut will contain data read from the selected cell.

- If neither of the above conditions is met, the conditions of the data out is indeterminate at access time and remains so until either CAS or WE returns to VIH.

- e. The transition time specification applies for all input signals.

- In addition to meeting the transition rate specification, all input signals must transit between  $V_{IL}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH}$ ) in a monotonic manner.

- Transition time is measured between VIL (max) and VIH (min).

- f. 3ns rise and fall times (t<sub>T</sub>) are used for cycle time specifications.

- g. tAVWL2 is restrictive parameter for Read-Modify write cycles when read access prior to write is required.

- h. Operation within the t<sub>RL1AV</sub> (max) limit insures that t<sub>RL1QV</sub> (max) can be met. t<sub>RL1AV</sub> (max) is specified as a reference point only. If t<sub>RL1AV</sub> is greater than the specified t<sub>RL1AV</sub> (max) limit, then the access time is controlled by t<sub>AVQV</sub> and t<sub>CL1QV</sub>.

- i. t<sub>RL1CL1</sub> (max) is specified for reference only. Operation within t<sub>RL1CL1</sub> (max) and t<sub>RL1AV</sub> (max) limit insure that t<sub>RL1QV</sub> (max), t<sub>AVQV</sub> (max) can be met. If t<sub>RL1CL1</sub> is greater than the specified t<sub>RL1CL1</sub> (max) then the access time is controlled by t<sub>AVQV</sub> and t<sub>CL1QV</sub>.

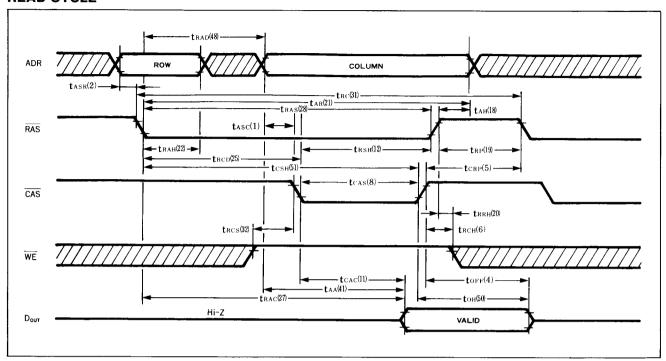

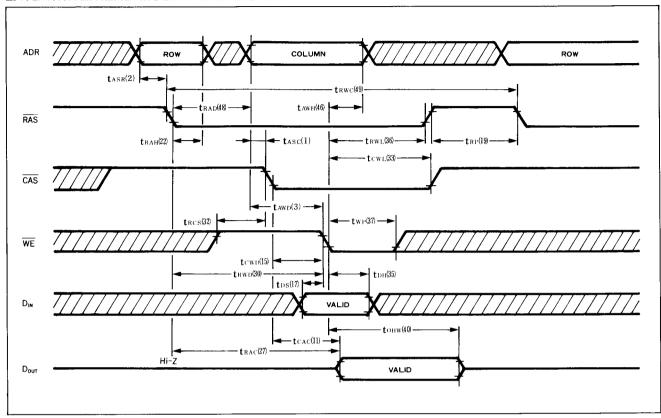

#### **READ CYCLE**

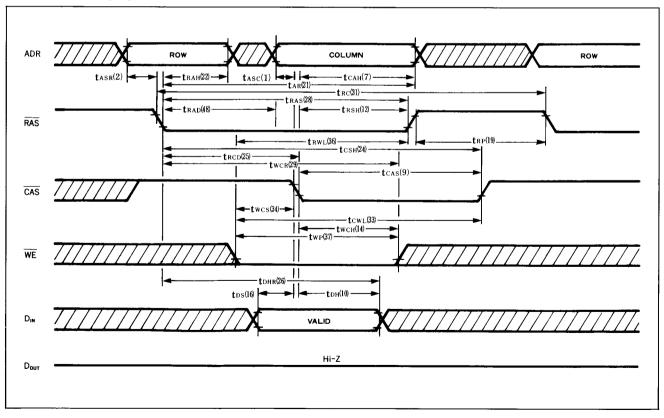

#### **EARLY-WRITE CYCLE**

#### LATE WRITE/READ-MODIFY-WRITE CYCLE

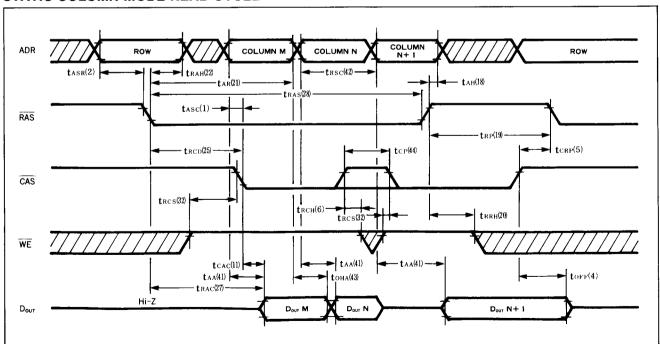

#### STATIC COLUMN MODE READ CYCLE

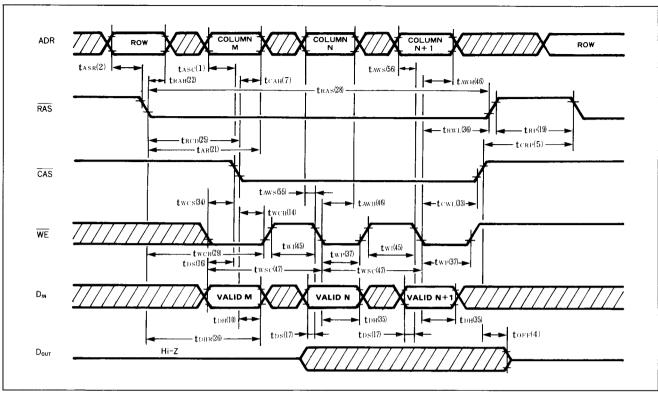

# STATIC COLUMN MODE WRITE CYCLE (WE CONTROL)

# STATIC COLUMN MODE WRITE CYCLE (CAS CONTROL)

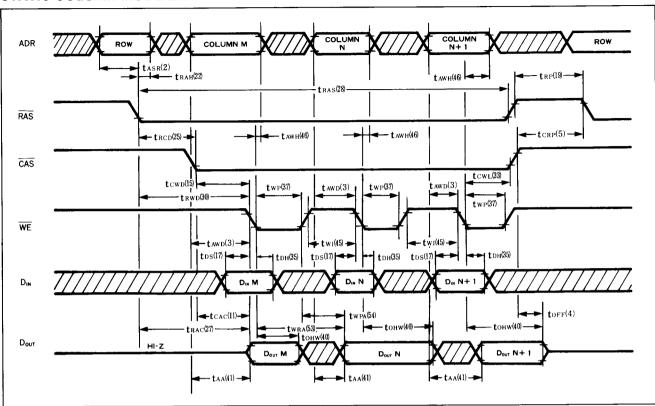

# STATIC COLUMN MODE LATE WRITE/READ-MODIFY-WRITE CYCLE

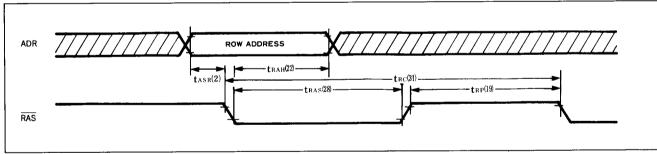

# RAS-ONLY REFRESH [CAS ≥ V<sub>IH</sub> (MIN)]

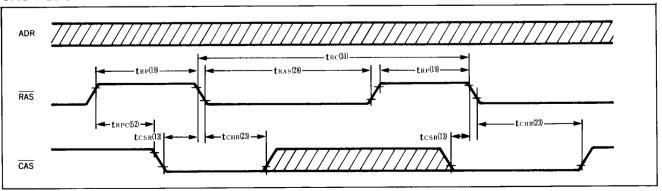

#### **CAS-BEFORE-RAS REFRESH**

#### STATIC COLUMN DECODE MODE TIMING INFORMATION

All cycles of the AAA2800 are initiated by a high-to-low transition of  $\overline{RAS}$ . For Read, Write, Read-Modify-Write, or  $\overline{RAS}$ -Only refresh cycles, the high-to-low transition of  $\overline{RAS}$  causes the state of the 9 external address lines (A<sub>0</sub> through A<sub>8</sub>) to be latched. Eight of the nine address bits are decoded to select one of 256 rows. The ninth row address bit (A<sub>8</sub>) is saved and becomes part of the ten bit column address which selects one of the 1024 column locations. The AAA2800 uses a transparent latch to capture the row addresses which permits an extremely short capture time for the row addresses with only a 2ns set-up and 2ns hold required. After the short row address capture time has been satisfied, the 9 external address lines can be changed to the column address. Since column address decoding on the AAA2800 is static (asynchronous or ripple-through), no address strobes are required to select 1 bit location out of the 512 column locations within the selected row address field. However, after the high-to-low transition  $\overline{RAS}$ , the state of  $\overline{CAS}$  and  $\overline{WE}$  determine whether the cycle is a Read, Wite, Read-Modify-Write, or a  $\overline{RAS}$ -Only refresh cycle.

#### **Read Cycle**

A read cycle is performed on one or more memory locations if  $\overline{\text{WE}}$  is high while both  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  are low. With  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  low while  $\overline{\text{WE}}$  is high, the output will reflect the contents of the cell addressed by the 9 latched row addresses and the current 9 column addresses provided that all read cycle timing conditions have been satisfied. Asynchronous page operations, where more than one location can be accessed during a single  $\overline{\text{RAS}}$  active cycle, can be executed by simply changing the column address whenever a new bit within the present page (defiend by the 9 latched row addresses) is being accessed. It is not necessary to toggle  $\overline{\text{CAS}}$  in order to perform static column decode mode read operations, but  $\overline{\text{CAS}}$  can be toggled, if desired, for the purpose of enabling or disabling the data output buffers.

#### **Write Cycle**

The AAA2800 will perform three types of write cycles: Early-Write, Late-Write, and Read-Modify-Write. A write cycle is initiated when  $\overline{\text{WE}}$ ,  $\overline{\text{CAS}}$  and  $\overline{\text{RAS}}$  are low. If  $\overline{\text{WE}}$  goes low prior to  $\overline{\text{CAS}}$  going low, an Early-Write cycle is executed. Early-Write cycles are initiated by the falling edge of  $\overline{\text{CAS}}$  with set-up and hold times for both data-in and column addresses (Column addresses latched during Write cycles to provide additional noise immunity as well as allow pipelined write operations.) being reference to the falling edge of  $\overline{\text{CAS}}$ . During Early-Write cycles, the data out will remain open (high impedance state) as long as  $\overline{\text{WE}}$  remains low.

If  $\overline{CAS}$  goes low to  $\overline{WE}$  going low, a Late-Write is executed. Late-Write cycles are initiated by the falling edge of  $\overline{WE}$  with the set-up and hold times for both data-in and column addresses being referenced to the falling edge of  $\overline{WE}$ . Prior to the  $\overline{WE}$  control input being asserted for a Late-Write cycle, all the input conditions for a read operation are satisfied ( $\overline{RAS}$  and  $\overline{CAS}$  are both low and  $\overline{WE}$  is high). If  $\overline{WE}$  is asserted after a valid read access occurs, the operation is called a Read-Modify-Write cycle. During a Read-Modify-Write cycle, the data-out will reflect the contents of the addressed cell before it was written until  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  go high. A Late-Write cycle where  $\overline{WE}$  is brought low prior to output data accessing will result an indeterminate data output state, but whatever state was present at the time  $\overline{WE}$  goes low will be latched until  $\overline{RAS}$ ,  $\overline{CAS}$  or  $\overline{WE}$  goes high.

#### **Refresh Cycles**

Dynamic RAMs retain data by storing charge on a capacitor. Since the charge will leak away over a period of time, it is necessary to access the data in the cell (capacitor) periodically in order to fully restore the stored charge while it is still at a sufficiently high level to be properly detected. For the AAA2800, and  $\overline{\text{RAS}}$  sequence will fully refresh all storage cells within the single row addressed. To ensure that all cells remain sufficiently refreshed, all 256 rows (all binary combinations of address bits A<sub>0</sub> through A<sub>7</sub>) must be refreshed every 4.4ms.

The addressing of the rows for refresh may be sourced either externally or internally. If the refresh row addresses are to be provided from an external source,  $\overline{\text{CAS}}$  must be high when  $\overline{\text{RAS}}$  goes low. If  $\overline{\text{CAS}}$  is high when  $\overline{\text{RAS}}$  goes low, and type of cycle (Read, Write, Read-Modify-Write, or  $\overline{\text{RAS}}$ -Only) will cause the externally addressed row to be refreshed.

If  $\overline{\text{CAS}}$  is low when  $\overline{\text{RAS}}$  falls, the AAA2800 will use an internal 8-bit counter as the source of the row addresses and will ignore  $\overline{\text{WE}}$  and the external address inputs.  $\overline{\text{CAS}}$ -Before- $\overline{\text{RAS}}$  refresh mode is a refresh-only mode. Also,  $\overline{\text{CAS}}$ -Before- $\overline{\text{RAS}}$  refresh does not cause device selection and the state of the data-out will remain unchanged as long as  $\overline{\text{CAS}}$  remains low.

#### **APPLICATION**

To ensure proper operation of the AAA2800 in a system environment it is recommended that the following guidelines be followed.

# Power Distribution

Transient currents are required by dynamic RAMs. These transient current spikes can cause significant power supply and ground noise unless adequate power distribution and decoupling is used. The recommended power distribution scheme combines proper trace layout and placement of decoupling capacitors. The impedance in the decoupling path from the power pin (8) through the decoupling capacitor, to the ground pin (16) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line and the decoupling capacitor.

To reduce the power line impedance, it is recommended that the power trace and ground trace be gridded or provided by separate power planes. To prevent loss of signal margins due to differential ground noise, the ground grid of the memory array should be extended to the TTL drivers in the peripheral circuitry. A high-frequency decoupling capacitor with a value of  $0.1\mu F$ , should be placed between the rows of memory devices in the array. A larger tantalum capacitor with a value between  $22\mu F$  and  $47\mu F$  should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These large capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

#### **Termination**

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low-going TTL signals, line termination is recommended. The termination may be either parallel or series but the series termination technique has the advantages of drawing no DC current and using a minimum of components. The recommended technique is to use series termination. A series resistor in the signal line at the output of the TTL driver to match the source impedance of the TTL driver to the signal line will dampen the reflections on the line. The line should be kept short with the driver/termination combination close to the memory array. Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the  $10\Omega$  to  $30\Omega$  range will be required.

Proper power distribution techniques, including adequate use of decoupling capacitors, along with proper termination of TTL driver outputs, are among the most important, yet basic guidelines to be followed. These guidelines are intended to maintain the operation margins of all devices on the memory board by providing a quiet environment relatively free of noise spikes and signal reflections.

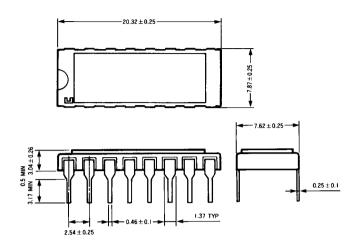

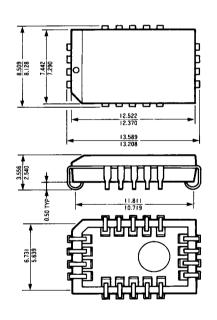

#### 16 PIN SIDEBRAZED (UNIT: mm)

#### 16 PIN PLASTIC DIP (UNIT: mm)

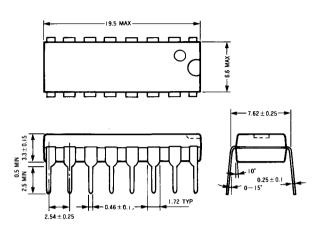

# 18 PIN PLCC (UNIT: MAX mm)

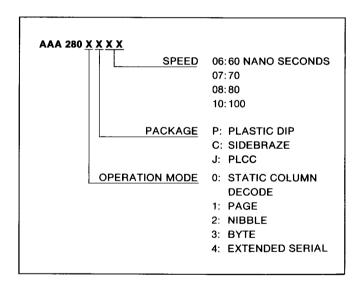

### ORDERING INFORMATION

NMB SEMICONDUCTOR CO., LTD. reserves the right to make changes to the product described herein, and does not assume any liability which may occur due to the use or application of the product described.

#### NMB SEMICONDUCTOR CO., LTD.

Shin-nihon Kaikan Building 7-18, Mita 3-chome, Minato-ku Tokyo 108, Japan

Tel: 03-455-3461 Fax: 03-454-8633 Telex: 2422029

#### NMB SEMICONDUCTOR CORPORATION

11621 Monarch Street, Garden Grove, CA 92641, U.S.A.

Tel: (714) 897-6272 Fax: (714) 891-0895

**JANUARY 1988**