# MULTI MODE MODEM ANALOG FRONT-END

ADVANCE DATA

- 12 BIT A/D AND D/A CONVERTERS WITH PROGRAMMABLE SAMPLING FREQUENCY: 7.2. 8.0. OR 9.6 kHz

- 6 TH ORDER SWITCHED CAPACITOR TRANSMIT FILTER

- TRANSMIT ATTENUATOR PROGRAMMABLE FROM 0 dB TO 22 dB WITH 2 dB STEP

- DUPLEXER OUTPUT AVAILABLE WITH PRO-GRAMMABI F ATTENUATION

- 15 TH ORDER SWITCHED CAPACITOR RX FILTER (PROGRAMMABLE)

- TWO PROGRAMMABLE GAIN Rx AMPLIFIERS: FROM 0 dB TO 9 dB WITH 3 dB STEP BEFORE Rx FILTER AND FROM 0 dB TO 46.5 dB WITH 1.5 dB STEP AFTER Rx FILTER

- PROGRAMMABLE CARRIER LEVEL DETECTOR

- ON CHIP ANTI-ALIASING CELLS (TRANSMIT AND RECEIVE)

- TWO INDEPENDANT TRANSMIT AND RE-CEIVE DIGITAL PHASE LOCKED LOOPS (DPLLS)

- TERMINAL CLOCK INPUT FOR TRANSMIT SYNCHRONIZATION

- THREE AVAILABLE OUTPUT CLOCKS : BIT, BAUD AND CONVERSION CLOCKS

- DSP INTERFACE THROUGH 8 BIT STAN-DARD BUS FOR BOTH SIGNAL SAMPLES AND CONTROL REGISTER ACCESS

- AUTOMATIC RESET ON POWER-ON

- ±5 V POWER SUPPLY

- 250 mW TYPICAL POWER CONSUMPTION

# DIP40 (Plastic Package) PLCC44 (Plastic Package)

#### DESCRIPTION

The TS7542 is a single-chip analog front-end designed to implement high-performance voice-grade MODEMS. Associated with a Digital Signal Processor such as TS68930/31 or ST18930/31, it provides a cost-effective and powerful solution for implementation of multi-mode modems including CCITT V.21, V.22, V.22bis, V.23, V.26, V.27, V.29, V.33 and BELL 103, 202 and 212 A standards.

#### ORDERING INFORMATION

| Part Number | Temperature Range | Package |

|-------------|-------------------|---------|

| TS7542CP    | 0 to 70 °C        | DIP 40  |

| TS7542CFN   | 0 to 70 °C        | PLCC 44 |

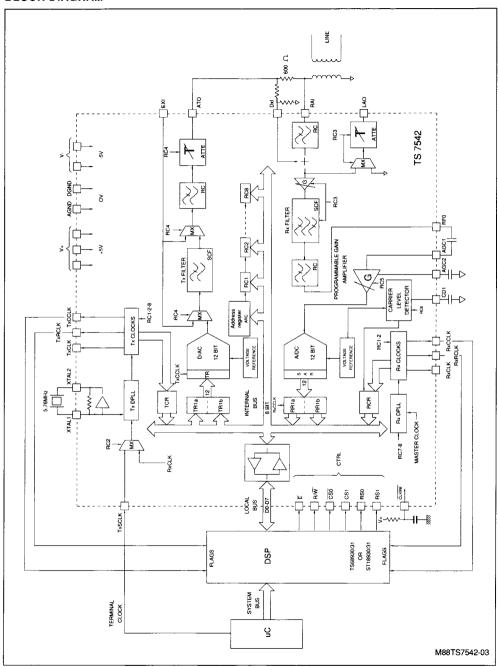

## **BLOCK DIAGRAM**

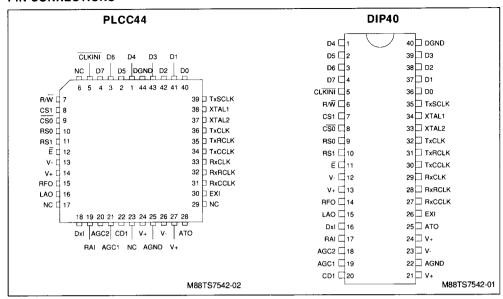

#### PIN CONNECTIONS

#### PIN DESCRIPTION

| N°   | Name    | Description                                                                                                                                        |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-4  | D4-D7   | Bidirectional Data Bus                                                                                                                             |

| 5    | CLKINI  | Clock Initialization Input. Must be tied to V+ during normal operation.                                                                            |

| 6    | R/W     | Read/Write Selection Input. This input indicates whether the current bus cycle is a read (high) or write (low) cycle.                              |

| 7-8  | CS1-CS0 | Chip Select Inputs. The chip is selected when $\overline{\text{CS0}}$ = 0 and $\overline{\text{CS1}}$ = 1.                                         |

| 9-10 | RS0-RS1 | Register Select Inputs. Select the register involved in a read or write operation.                                                                 |

| 11   | Ē       | Enable Input. Enables selection inputs.  Active on a low level for read operation.  Active on a positive-going edge for write operation.           |

| 12   | V -     | Negative Supply Voltage. V = - 5 V ± 5 %                                                                                                           |

| 13   | V +     | Positive Supply Voltage. V <sup>+</sup> = + 5 V ± 5 %                                                                                              |

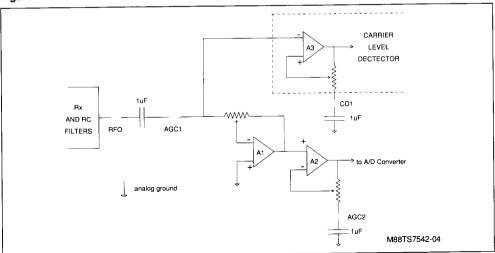

| 14   | RFO     | Receive Filter Analog Output. Designed to be connected to AGC1 input through a 1μF non polarized capacitor.                                        |

| 15   | LAO     | Line Attenuator Output. Duplexer analog output useful for line monitoring during call progress.                                                    |

| 16   | Dxl     | Duplexer Input. Signal on that analog input will be subtracted from the receive anti-aliasing filter output to implement duplexer function.        |

| 17   | RAI     | Receive Analog Input. Analog input tied to the transmission line.                                                                                  |

| 18   | AGC2    | This pin must be connected to the analog ground through a 1µF non polarized capacitor, in order to cancel the offset voltage of the AGC amplifier. |

| 19   | AGC1    | Analog input of the AGC amplifier and of the carrier level detector.                                                                               |

#### PIN DESCRIPTION (continued)

| 20    | CD1    | This pin must be connected to the analog ground through a $1\mu F$ non polarized capacitor, in order to remove the offset voltage of the carrier level detector amplifier.                                                                                          |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21    | V +    | Positive Power Supply Voltage                                                                                                                                                                                                                                       |

| 22    | AGND   | Analog Ground: All analog signals are referenced to this pin.                                                                                                                                                                                                       |

| 23    | V-     | Negative Supply Voltage                                                                                                                                                                                                                                             |

| 24    | V +    | Positive Supply Voltage                                                                                                                                                                                                                                             |

| 25    | ATO    | Analog Transmit Output. Capable of driving 1200 $\Omega$ load with 5 V peak to peak amplitude.                                                                                                                                                                      |

| 26    | EXI    | External Transmit Input. Can be programmed to be connected to the transmit filter or to the transmit attenuator input.                                                                                                                                              |

| 27    | RxCCLK | Receive Conversion Clock Output                                                                                                                                                                                                                                     |

| 28    | RxRCLK | Receive Baud Rate Clock Output                                                                                                                                                                                                                                      |

| 29    | RxCLK  | Receive Bit Rate Clock Output                                                                                                                                                                                                                                       |

| 30    | TxCCLK | Transmit Conversion Clock Output                                                                                                                                                                                                                                    |

| 31    | TxRCLK | Transmit Baud Rate Clock Output                                                                                                                                                                                                                                     |

| 32    | TxCLK  | Transmit Bit Rate Clock Output                                                                                                                                                                                                                                      |

| 33    | XTAL2  | Crystal Oscillator Output. Nominal Frequency = 5.76 MHz.                                                                                                                                                                                                            |

| 34    | XTAL1  | Crystal Oscillator or External Master Clock Input                                                                                                                                                                                                                   |

| 35    | TxSCLK | Transmit Synchronization Clock Input. Can be connected to an external terminal clock to phase lock the internal transmit clocks. When this pin is tied to a permanent logical level the transmit DPLL free-runs or can be phase locked on the receive clock system. |

| 36-39 | D0-D3  | Bidirectional Data Bus                                                                                                                                                                                                                                              |

| 40    | DGND   | Digital Ground. All digital signals are referenced to this pin.                                                                                                                                                                                                     |

#### **FUNCTIONAL DESCRIPTION**

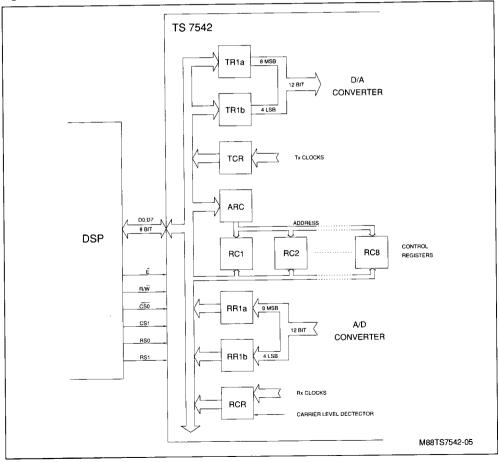

The TS7542 is generally used in conjunction with a DSP to realize the "data-pump" function of a high-speed modem. The circuit communicates with the DSP via an 8-bit bidirectional bus and mainly includes the following functions:

- the transmit analog channel with the D/A Converter, the transmit filter and the transmit attenuator.

- the receive analog channel with the local echo subtractor, the receive filter, the AGC amplifier, the A/D converter and the carrier level detector.

- the two independent transmit and receive clock generators using Digital Phase Locked Loops (DPLL).

- the 15 registers used to store the 12-bit transmit and receive digital samples, digital information for the DSP like the clock and the carrier level detector status, and the data needed to control the programmable functions or to synchronize the DPLLS.

#### TRANSMIT CHANNEL

The transmit channel converts the digital transmit signal coming from the DSP into the analog signal to be transmitted on the phone line. It includes a 12 bit digital to analog converter (DAC) operating at 7200, 8000 or 9600 samples per second according to the supported standard and the signal processing compromises made in the DSP. The maximum analog output signal amplitude is 5 V peak to peak , defined by the internal  $\pm 2.5$  V voltage reference. The DAC is monotonic and provides a guaranteed integral linearity better than 9 bit.

The transmit filter is a 6 th order low-pass switched capacitor filter (SCF) sampled at 288 kHz, whose cut-off frequency is 3.2 kHz. As the Sin x/x correction depends on the DAC sampling frequency, it has not been included in the tansmit filter and must be performed by the DSP. The transmit filter is followed by a second order, continuous time low-pass filter

that removes the residual high frequency parasitic signals.

The transmit attenuator allows the transmit signal gain to be programmed from 0 dB to - 22 dB with 2 dB steps. Infinite attenuation is also programmable. The output amplifier can directly drive a 1200  $\Omega$  load. For special applications, the EXI input can be programmed to give access to the input of the transmit filter or to the input of the attenuator.

#### RECEIVE CHANNEL

The receive channel begins with a second order continuous time anti- aliasing filter followed by a subtractor used to implement the two-wire to fourwire conversion with few external components. The receive signal is then directed to the receive filter input and also, after programmable attenuation, to the LAO output for line monitoring purpose during call progress. Attenuation can be 0 dB, 6 dB, 12 dB or infinite. The receive switched capacitor bandpass filter is composed of three programmable sections: A 5 th order low-pass section, a 4 th order optional 1800 Hz notch section and a 6 th order high-pass section. It also includes an input pre-filtering gain programmable from 0 dB to 9 dB with 3 dB steps. This feature is useful to optimize the dynamic range of the signal by setting the maximum receive level value close to 5 V peak to peak. The transfer function of the receive low-pass and high-pass filter sections can be translated by changing their sampling clock frequencies to support different communication standards. Ten modes are programmable to comply with CCITT V.21, V.22, V.22 bis, V.23, V.26,

V.27, V.29 or V.33 as well as BELL 103, 202 or 212A. The typical curves obtained are given in the TRANSMISSION CHARACTERISTICS section of the data sheet. The receive filter output is smoothed in a continuous time low-pass filter and then directed to the automatic gain control (AGC) amplifier programmable from 0 dB to 46.5 dB with 1.5 dB steps. The same signal is also connected to the carrier level detector input. Three external capacitors are needed to eliminate the offset voltage as indicated in Fig.1. The residual DC level at the analog to digital converter (ADC) input is kept low and independent of the selected gain.

The carrier level detector performs the comparison between the full wave rectified receive signal and programmable threshold voltage nominally equivalent to - 45.5 dBm, - 34.4 dBm or -28.6dBm with a 2.5 dB hysteresis. The binary result of the comparison can be read by the DSP. The nominal response time of the carrier level detector to a signal settlement or removal is 1.78 ms. The receive signal delivered by the AGC amplifier is sampled and converted from analog to digital by a 12-bit monotonic A/D converter whose integral linearity is guaranteed better than 9 bit. The sampling frequency is the same as that programmed for the transmit DAC i.e. 7200, 8000, or 9600 samples per second.

#### **CLOCK GENERATION**

The 5.76 MHz master clock is obtained from either a crystal tied between XTAL1 and XTAL2 pins or an external generator connected to the XTAL1 pin. In the latter case the XTAL2 pin should be left open.

Figure 1: AGC and Carrier Level Detector Amplifier Structure.

To meet the CCITT recommandation, the frequency tolerance requirement of the master clock must be better than  $\pm$  100 ppm. The different transmit (Tx) and receive (Rx) clocks are derived from the master clock via two independent digital phase locked loops (DPLL).

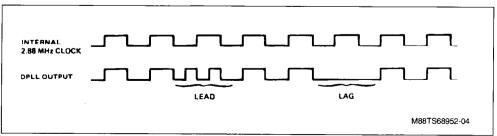

#### TRANSMIT CLOCKS

As shown in Fig.2 the transmit DPLL operates by adding or subtracting pulses to a 2.88 MHz internal clock at a rate of 600 Hz. Consequently the frequency capture range equals  $\pm$  600 Hz/2.88 MHz, i.e.  $\pm$  208 ppm, a value consistent with the worst case synchronization of two independent signals having  $\pm$  100 ppm of frequency accuracy. When V.27 clocks are selected, the DPLL up-dating rate is increased to 800 Hz which is a submultiple of the 1600 baud rate of that particular mode. In this case the frequency capture range is  $\pm$  278 ppm.

The transmit DPLL can be synchronized on an external terminal clock connected to the TxSCLK input or on the receive bit clock R x CLK internally generated from the receive DPLL. It can also free-run without any phase shift.

The TS7542 delivers three synchronous transmit clocks:

- a bit clockT x CLK whose frequency equals the bit rate of the MODEM

- a baud clock T x RCLK whose frequency equals the baud rate of the MODEM

- a conversion clock T x CCLK that gives the samplinfrequency of the transmit D/A converter

The frequencies of these three clocks are programmable to support the different MODEM modes. Their duty cycle is exactly 1:2. These clocks are available on three dedicated pins. Their status can also be read by the DSP from an internal register, TCR. Resetting of all the transmit clock generator counters on the next negative transition of T x SCLK or R x CLK can be controlled from the data bus.

Figure 2: DPLL Lead and Lag.

#### RECEIVE CLOCKS

The receive DPLL phase shifts are performed in two ways:

- a coarse phase lag is obtained by suppressing several 5.76 MHz master clock pulses from the input of the receive clock generator under the control of the DSP. The number of suppressed pulses is programmable from 20 to 4800 with a step value of 20 or 300. That feature will be used to quickly synchronize the receive DPLL on the recovered receive rate.

- a fine phase lead or lag is obtained by adding or suppressing two master clock pulses from the receive clock generator input, like for the transmit DPLL. But in that case the shifts are controlled by the DSP that also implements the phase comparator of the phase locked loop.

The TS7542 delivers three receive clocks with the same nominal frequency values as their transmit counterparts:

- a bit clock R x CCLK

- a baud clock R x RCLK

- a conversion clock R x CCLK

The status of these clocks can also be read from an internal register, RCR.

The receive and transmit clocks are plesiochronous.

#### INTERNAL REGISTERS

The 8-bit bidirectional data bus allows to access 15 internal registers as detailed in Fig.3. The data transfers are controlled by the six following signals:

- two chip select inputs \(\overline{CS0}\) and CS1 that must be put respectively to 0 and 1 to allow a data transfer.

- The read/write input  $R/\overline{W}$  that defines the transfer direction

- Two register select input that address one out of four registers for a read or a write operation.

Actually indirect addressing is used to extend to eight the number of the control registers.

The enable input E that strobes on its positive going transition the data to be written, or that enables on its low level state the output buffers when a data is to be read from a register.

The timing diagram of the data transfers is given in the TIMING SPECIFICATIONS section of the data sheet.

The four registers only accessible in a write operation are :

- TR1a that stores the 8 most significant bit (MSB) of the 12-bit transmit signal digital samples.

- TR1b that stores the 4 least significant bit (LSB) of the transmit signal digital samples.

- ARC that stores the 3-bit address of one out of eight control registers.

Figure 3: Internal Registers Configuration.

The control register whose address is stored in the ARC register. The content of ARC is automatically incremented after each access to a control register. This allows cyclical access to these registers.

The four registers only accessible in a read operation are :

- RR1a that stores the 8 MSB of the 12-bit receive signal digital samples

- RR1b that stores the 4 LSB of the 12-bit receive signal digital samples

- RCR that stores the receive clock and the carrier level detector status

- TCR that stores the transmit clock status

The addresses of the internal registers are given in table 1. Table 2 shows the formats used for the digital signal samples stored in the TR1a/b registers, the RR1a/b registers and for the status data stored

in the TCR and RCR registers. Table 3 summarizes the address and data format of the 8 control registers whose function is detailed in the PROGRAM-MABLE FUNCTIONS section.

Table 1.

| R/W | RS0 | RS1 | AccessedRegister                      | Comment              |

|-----|-----|-----|---------------------------------------|----------------------|

| 0   | 0   | 0   | TR1b                                  |                      |

| 0   | 0   | 1   | TR1a                                  | ]                    |

| 0   | 1   | 0   | ARC                                   | Write Only Registers |

| 0   | 1   | 1   | The Control Register Addressed by ARC | 1                    |

| 1   | 0   | 0   | RR1b                                  |                      |

| 1   | 0   | 1   | RR1a                                  | 1                    |

| 1   | 1   | 0   | RCR                                   | Read Only Registers  |

| 1   | 1   | 1   | TCR                                   |                      |

Table 2.

| Register |      |        | Comment |       |     |     |     |     |                                                            |

|----------|------|--------|---------|-------|-----|-----|-----|-----|------------------------------------------------------------|

| Name     | D7   | D6     | D5      | D4    | D3  | D2  | D1  | D0  |                                                            |

| TR1a     | Tx11 | Tx10   | Tx9     | Tx8   | Tx7 | Tx6 | Tx5 | Tx4 |                                                            |

| TR1b     | Tx3  | Tx2    | Tx1     | Tx0   | X   | Х   | Х   | Х   |                                                            |

| RR1a     | Rx11 | Rx10   | Rx9     | Rx8   | Rx7 | Rx6 | Rx5 | Rx4 |                                                            |

| RR1b     | Rx3  | Rx2    | Rx1     | Rx0   | 0   | 0   | 0   | 0   |                                                            |

| TCR      | Х    | TxRCLK | TxCCLK  | TxCLK | Х   | Х   | Х   | Х   |                                                            |

| RCR      | CDL  | RxRCLK | RxCCLK  | RxCLK | Х   | X   | ×   | Х   | CDL = 1 if Rx signal is greater than the programmed level. |

X = Don't care.

Note 1:D0 to D7 refer to the data bus pins and gives the bit position in the read or written data.

Table 3.

| 0                   | ARC    | Cont     | ent    |      |      |         |        |         |         |      |      |                                                    |

|---------------------|--------|----------|--------|------|------|---------|--------|---------|---------|------|------|----------------------------------------------------|

| Control<br>Register | (addre | ess) (no | ote 1) |      | · ·  | tegiste | er Cor | itent ( | note 2) |      |      | Programmed<br>Function                             |

| Name                | D7     | D6       | D5     | D7   | D6   | D5      | D4     | D3      | D2      | D1   | D0   |                                                    |

| RC1                 | 0      | 0        | 0      | нвз  | нв2  | HB1     | HR2    | HR1     | ×       | x    | x    | Bit/Baud Rate for Tx and Rx Clocks                 |

| RC2                 | 0      | 0        | 1      | x    | х    | Х       | HS2    | HS1     | HTHR    | FCLK | Х    | Conversion Frequency. Tx Synchronization Selection |

| RC3                 | 0      | 1        | 0      | RF3  | RF2  | RF1     | REJ    | RFG2    | RFG1    | LAT2 | LAT1 | Rx Filter and 1800Hz<br>Notch. LAO Attenuation     |

| RC4                 | 0      | 1        | 1      | ATT4 | ATT3 | ATT2    | ATT1   | х       | EM2     | EM1  | ×    | Tx Attenuation. EXI Input.                         |

| RC5                 | 1      | 0        | 0      | RG5  | RG4  | RG3     | RG2    | RG1     | x       | ×    | ×    | AGC Amplifier Gain                                 |

| RC6                 | 1      | 0        | 1      | CDG2 | CDG1 | CDH     | х      | х       | х       | x    | ×    | Carrier Level Detector<br>Gain and Hysteresis      |

| RC7                 | 1      | 1        | 0      | SP5  | SP4  | SP3     | SP2    | SP1     | x       | х    | х    | RxDPLL Coarse Phase<br>Shift                       |

| RC8                 | 1      | 1        | 1      | MPE  | SPR  | AVRE    | VAL    | х       | ×       | х    | x    | TxDPLL Reset. Rx DPLL Fine Phase Shifts.           |

X = Don't care value. Note 2:D0 to D7 refers to the data bus pins and gives the bit position in the loaded address or data.

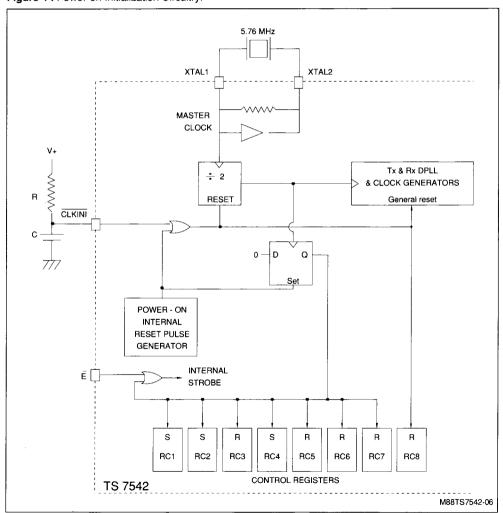

#### POWER-ON INITIALIZATION

Internal power-on circuitry (Fig.4) automatically resets the DPLL and the clock generators counters, and initializes the RC1 to RC8 control registers. The initial status of these registers are given in the PRO-GRAMMABLE FUNCTIONS section. The transmit attenuator is initialized to an infinite attenuation in order to avoid the transmission of indesirable signals on the phone line.

Access to the control registers is desabled during power-on reset until the clock oscillator starting. The

reset time duration can be increased by connecting the CLKINI input to an external RC timer as indicated in Fig.4. That feature will prevent, in particular applications, possible problems due to incontrolled signals coming from the DSP during power-on. In normal operation the CLKINI input can be used to reset the DPLL and clock generator counters and the RC8 control register. When that pin as not used, it must be tied to V\*

Figure 4: Power-on Initialization Circuitry.

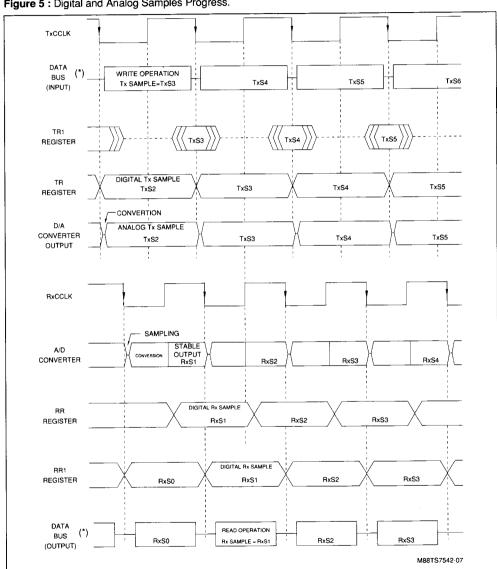

#### PROGRESSION OF SIGNAL SAMPLES

Fig.5 shows the progression in the TS7542 of the digital and analog signal samples. It appears that the transfers of the data representing the transmit and the receive signals have to be synchronized on the TxCCLK or the RxCCLK conversion clock, respectively. This is the reason why the DSP needs to receive these clock signals or to read their status from the dedicated registers.

Figure 5: Digital and Analog Samples Progress.

Txi = ith analog or digital sample of the Tx signal. Notes:

(\*)

Rxi = ith analog or digital sample of the Rx signal.

Data can be written (read) six master clock periods after the T x CCLK (R x CCLK) negative-going transition respectively

#### PROGRAMMABLE FUNCTIONS

Table 4: Bit Clock Frequency Programming (Tx and Rx).

|     |     |     |     | RC1 R | egister | •  |    | TxCLK or RxCLK |                   |                           |

|-----|-----|-----|-----|-------|---------|----|----|----------------|-------------------|---------------------------|

|     | D7  | D6  | D5  | D4    | D3      | D2 | D1 | D0             | Bit Clock Nominal | Communication<br>Standard |

|     | нвз | HB2 | HB1 | HR2   | HR1     | _  | _  | _              | Frequency (Hz)    | Standard                  |

|     | 0   | 0   | 0   |       |         |    |    |                | 9600              | V.29                      |

|     | 0   | 0   | 1   |       |         |    |    |                | 4800              | V.27                      |

|     | 0   | 1   | 0   |       |         |    |    |                | 2400              | V.22 bis, V.26            |

|     | 0   | 1   | 1   |       |         |    |    |                | 1200              | V.22, BELL 212A           |

|     | 1   | 0   | 0 . |       |         |    |    |                | 600               | V.22 Fall-back            |

|     | 1   | 0   | 1   |       |         |    |    |                | 600               | н                         |

|     | 1   | 1   | 0   |       |         |    |    |                | 2400              | V.22 bis, V.26            |

| P/O | 1   | 1   | 1   |       |         |    |    |                | 1200              | V.22, BELL 212A           |

P/O : Power on status.

Table 5: Baud Rate Clock Frequency Programming (Tx and Rx).

|     |     | •   |     | RC1 R | egister |    | TxRCLK or RxBCLK |       |                            |                                    |

|-----|-----|-----|-----|-------|---------|----|------------------|-------|----------------------------|------------------------------------|

|     | D7  | D6  | D5  | D4    | D3      | D2 | D1               | D0    | Baud Rate<br>Clock Nominal | Communication<br>Standard (note 3) |

|     | нвз | HB2 | HB1 | HR2   | HR1     | -  | _                | .   _ | Frequency(Hz)              | Standard (note 5)                  |

|     |     |     |     | 0     | 0       |    | _                |       | 2400                       | V.29, V.33                         |

|     |     |     |     | 0     | 1       |    |                  |       | 1600*                      | V.27*                              |

|     |     |     |     | 1     | 0       |    |                  |       | 1200                       | V.26                               |

| P/O |     |     |     | 1     | 1       |    |                  |       | 600                        | V.22, V.22 Bis,<br>BELL 212A       |

Note 3: The phase shift frequency of the transmit DPLL is 600 Hz, excepted for (\*) 800 Hz.

Table 6: Conversion Clock Frequency Programming (Tx and Rx).

|     |    |    |    | RC2 R | egister | TxCCLK or RxCCLK |          |                          |                                |               |

|-----|----|----|----|-------|---------|------------------|----------|--------------------------|--------------------------------|---------------|

|     | D7 | D6 | D5 | D4    | D3      | D2               | D1       | D0                       | Conversion<br>(sampling) Clock | Communication |

|     | _  | -  | _  | HS2   | HS1     | HTHR             | R FCLK - | Nominal<br>Frequency(Hz) | Standard                       |               |

|     |    |    |    | 0     | 0       |                  |          |                          | 9600                           |               |

|     |    |    |    | 0     | 1       |                  |          |                          | 8000                           | V.27          |

|     |    |    | ĵ. | 1     | 0       |                  |          |                          | 7200                           |               |

| P/O |    |    | ,, | 1     | 1       |                  |          |                          | 7200                           |               |

Table 7: Tx Synchronization Signal Programming.

|     |    |    |    | RC2 R | egiste |      |      |    |                                 |

|-----|----|----|----|-------|--------|------|------|----|---------------------------------|

|     | D7 | D6 | D5 | D4    | D3     | D2   | D1   | D0 | Selected Synchronisation Signal |

|     | _  | -  | -  | HS2   | HS1    | HTHR | FCLK |    | <u> </u>                        |

|     |    |    |    |       |        | 0    | 0    |    | RxCLK                           |

|     |    |    |    |       |        | 1    | 0    |    | TxSCLK (note 4)                 |

| P/O |    |    |    |       |        | Х    | 1    |    | Transmit DPLL free-runs         |

Note 4: The Tx DPLL free runs if there is no transistion on this pin in that case.

X = Don't care value.

Table 8: Tx Clock General Reset.

|     |     | RC   | Regis | ter (note | e 5) |    |    |                                                        |

|-----|-----|------|-------|-----------|------|----|----|--------------------------------------------------------|

| D7  | D6  | D5   | D4    | D3        | D2   | D1 | D0 | ResettingTransition                                    |

| MPE | SPR | AVRE | VAL   | _         | _    |    |    |                                                        |

| 1   | 0   | 0    | 0     |           |      |    |    | Next Negative-going Transition of Synchronizing Signal |

Note 5: RC8 register is cleared after the programmed control operation is completed and on power-on.

Table 9: Rx Clock Phase Shift Programming.

|     |     | RC8 Re | egister( | note 5)  |    |    |                                                 |

|-----|-----|--------|----------|----------|----|----|-------------------------------------------------|

| D7  | D6  | D5     | D4       | D3       | D2 | D1 | Actionon RxDPLL                                 |

| MPE | SPR | AVRE   | VAL      | -        | -  | -  |                                                 |

| 0   | 1   | 0      | 0        |          |    |    | Phase Lag of Programmed Amplitude               |

| 0   | 0   | 0      | 1        |          |    |    | Phase Lag of Two 5.76 MHz Master Clock Periods  |

| 0   | 0   | 1      | 1        | <u> </u> |    |    | Phase Lead of Two 5.76 MHz Master Clock Periods |

Note 5: RC8 register is cleared after the programmed control operation is completed and on power-on.

Table 10: Rx Clock Phase Shift Amplitude Programming.

|     |     |     | RC  | 7 Regis | ster |    |    | Dhase Chill | in Dogrado | Number of Master |  |

|-----|-----|-----|-----|---------|------|----|----|-------------|------------|------------------|--|

|     | D7  | D6  | D5  | D4      | D3   | D2 | D1 | Phase Shim  | in Degrees | Clock Pulses     |  |

|     | SP5 | SP4 | SP3 | SP2     | SP1  | -  | _  | 1200 Bauds* | 1600 Bauds | Suppressed       |  |

|     | 0   | 0   | 0   | 0       | 0    |    |    | 1.5         | 2          | 20               |  |

| 1   | ō   | ŏ   | Ō   | 0       | 1    |    |    | 3           | 4          | 40               |  |

|     | ŏ   | ō   | lo  | 1       | 0    |    |    | 4.5         | 6<br>8     | 60               |  |

|     | Ö   | ō   | Ō   | 1       | 1    |    |    | 6           | 8          | 80               |  |

|     | ١ŏ١ | Ö   | 1 1 | Ó       | 0    |    |    | 7.5         | 10         | 100              |  |

|     | ŏ   | ō   | 1   | ō       | 1    |    |    | 9           | 12         | 120              |  |

|     | Ö   | Ŏ   | 1   | 1 1     | 0    |    |    | 10.5        | 14         | 140              |  |

|     | ٥   | Ö   | 1   | 1 1     | 1    |    |    | 12          | 16         | 160              |  |

|     | ٥   | 1   | Ó   | Ó       | 0    |    |    | 13.5        | 18         | 180              |  |

| 1   | Ŏ   | l i | lo  | 0       | 1    |    |    | 15          | 20         | 200              |  |

|     | Ŏ   | 1 1 | 0   | 1 1     | 0    |    | 1  | 16.5        | 22         | 220              |  |

|     | Ιō  | 1   | 0   | 1 1     | 1    |    |    | 18          | 24         | 240              |  |

|     | ŏ   | 1   | 1   | Ó       | Ó    |    |    | 19.5        | 26         | 260              |  |

|     | Ŏ   | 1   | 1 1 | Ó       | 1    |    |    | 21          | 28         | 280              |  |

|     | ŏ   | i   | l i | l i     | Ó    |    | 1  | 22.5        | 30         | 300              |  |

|     | lŏ  | li  | Ιi  | 1       | l i  |    |    | 24          | 32         | 320              |  |

|     | lĭ  | Ö   | Ó   | 0       | 0    |    |    | 22.5        | 30         | 300              |  |

|     | l i | ١ŏ  | Ō   | ١ŏ      | 1 1  |    |    | 45          | 60         | 600              |  |

|     | Ιi  | ō   | Ō   | 1       | 0    |    |    | 67.5        | 90         | 900              |  |

|     | 1   | lŏ  | Ö   | 1       | 1    | 1  |    | 90          | 120        | 1200             |  |

|     | l i | Ŏ   | 1   | Ó       | 0    |    | ļ  | 112.5       | 150        | 1500             |  |

|     | l i | Ō   | 1   | Ó       | 1    |    |    | 135         | 180        | 1800             |  |

|     | 1 1 | Ō   | 1 1 | 1       | 0    |    |    | 157.5       | 210        | 2100             |  |

|     | l i | ŏ   | 1 1 | 1       | 1    |    |    | 180         | 240        | 2400             |  |

|     | 1   | 1   | lò  | 0       | 0    | ļ  | l  | 202.5       | 270        | 2700             |  |

|     | Ιi  | 1   | ō   | Ιŏ      | 1    |    | i  | 225         | 300        | 3000             |  |

|     | l i | l i | o   | 1       | 0    | 1  |    | 247.5       | 330        | 3300             |  |

|     | i   | 1   | ١ŏ  | 1 1     | 1    |    |    | 270         | 360        | 3600             |  |

|     | l i | l i | 1   | Ó       | 0    |    |    | 292.5       |            | 3900             |  |

|     | l i | 1   | 1   | 0       | 1    |    |    | 315         |            | 4200             |  |

|     | 1   | 1   | 1   | 1       | 0    |    |    | 337.5       |            | 4500             |  |

| P/O | 1   | 1   | 1   | 1       | 1    |    |    | 360         |            | 4800             |  |

(\*) 2400 bauds : multiply by two. 600 bauds : divide by two.

Table 11: Tx Attenuator Programming.

|   |      |      |      | RC4 R | egiste | r   |     |    |                  |

|---|------|------|------|-------|--------|-----|-----|----|------------------|

|   | D7   | D6   | D5   | D4    | D3     | D2  | D1  | D0 | Attenuation (dB) |

|   | ATT4 | ATT3 | ATT2 | ATT1  |        | EM2 | EM1 | _  |                  |

|   | 0    | 0    | 0    | 0     |        |     |     |    | 0                |

|   | 0    | 0    | 0    | 1     |        |     |     |    | 2                |

|   | 0    | 0    | 1    | 0     |        |     |     |    | 4                |

|   | 0    |      |      | 1     |        |     |     |    | 6                |

|   | 0    | 1    | 0    | 0     |        |     |     |    | 8                |

|   | 0    | 1    | 0    | 1     |        |     |     |    | 10               |

|   | 0    | 1    | 1    | 0     |        |     |     |    | 12               |

|   | 0    | 1    | 1    | 1     |        |     |     |    | 14               |

|   | 1    | 0    | 0    | 0     |        |     |     |    | 16               |

|   | 1    | 0    | 0    | 1     |        |     |     |    | 18               |

|   | 1    | 0    | 1    | 0     |        |     |     |    | 20               |

|   | 1    | 0    | 1    | 1     |        |     |     |    | 22               |

| 0 | 1    | 1    | Х    | Х     |        |     |     |    | Infinite         |

X = Don't care value.

Table 12: EXI and AGC1 Inputs Programming.

| _   |      |      | R          | C4 R                        | egist    | er                          |     |    |                         |                    |  |  |

|-----|------|------|------------|-----------------------------|----------|-----------------------------|-----|----|-------------------------|--------------------|--|--|

|     | D7   | D6   | <b>D</b> 5 | D4                          | D3       | D2                          | D1  | D0 | EXI Input Status        | AGC1 Input Status  |  |  |

|     | ATT4 | ATT3 | ATT2       | ATT1                        | _        | EM2                         | EM1 | _  |                         |                    |  |  |

|     | 0 0  |      | 0          |                             | Disabled | Tied to AGC Amplifier Input |     |    |                         |                    |  |  |

|     |      |      |            |                             |          | 0                           | 1   |    | Tied to Tx Filter Input |                    |  |  |

|     | 1 0  |      |            | Tied to Tx Attenuator Input | н        |                             |     |    |                         |                    |  |  |

| P/O |      |      |            |                             |          | 1                           | 1   |    | Disabled                | Tied to A/DC Input |  |  |

Table 13: Rx Filter Programming.

|     | F   | RC3 R | egiste | r   | Sampi    | ing (Fs) a<br>Frequenci | and Cut-of<br>ies (note 6) | ff (Fc)   | Communication                                                        | See       |  |

|-----|-----|-------|--------|-----|----------|-------------------------|----------------------------|-----------|----------------------------------------------------------------------|-----------|--|

|     | D7  | D6    | D5     | D4  | Low Pass | s Section               | High Pas                   | s Section |                                                                      | Figure N° |  |

|     | RF3 | RF2   | RF1    | RF0 | Fs(kHz)  | Fc(Hz)                  | Fs(kHz)                    | Fc(Hz)    |                                                                      |           |  |

| P/O | 0   | 0     | 0      | х   | 288      | 3200                    | 144                        | 1820      | V.22, V.22 bis, BELL<br>212A<br>and BELL 103 High<br>Channels        | 7         |  |

| _   | 0   | 0     | 1      | Х   | 192      | 2133                    | 115.2                      | 1456      | V.21 High Channel                                                    | - 8       |  |

|     | 0   | 1     | 0      | Х   | 288      | 3200                    | 82.3                       | 1040      | V.27 ter 2400 bps                                                    | 9         |  |

|     | 0   | 1     | 1      | х   | 288      | 3200                    | 72                         | 910       | V.27 ter 4800 bps,<br>V.23, V.26<br>and BELL 202                     | 10        |  |

|     | 1   | 0     | . 0    | 0   | 144      | 1600                    | 64                         | 809       | V.22, V.22 bis, ,BELL<br>212A<br>and BELL 103 Low<br>Channels        | 11        |  |

|     | 1   | 0     | 0      | 1   | 144      | 1600                    | 64                         | 809       | V.22, V.22 bis Low<br>Channels<br>with 1800 Hz Tone<br>Rejection (*) | 12        |  |

|     | 1   | 0     | 1      | Х   | 115.2    | 1280                    | 64                         | 809       | V.21 Low Channel                                                     | 13        |  |

|     | 1   | 1     | 0      | Х   | 288      | 3200                    | 36                         | 455       | V.29, V.33                                                           | 14        |  |

|     | 1   | 1     | 1      | Х   | 288      | 3200                    | 18                         | 228       | Full Channel<br>Bandwidth                                            | 15        |  |

|     | 1   | 1     | 1      | Х   | 48       | 533                     | 533 27.4 347               |           | 75 bps Back<br>Channel                                               | 16        |  |

<sup>(\*)</sup> In this mode the 1800 Hz notch filter section is enabled.

#### Table 14.

|     |     |          |     | RC3 R | egister |      |      |      |                     |

|-----|-----|----------|-----|-------|---------|------|------|------|---------------------|

|     | D7  | D6       | D5  | D4    | D3      | D2   | D1   | D0   | Rx Filter Gain (dB) |

|     | RF3 | RF2      | FR1 | RF0   | RFG2    | RFG1 | LAT2 | LAT1 |                     |

| P/O |     |          |     |       | 0       | 0    |      |      | 0                   |

|     |     | _        |     |       | 0       | 1    |      |      | 3                   |

|     |     | <u> </u> |     | -     | 1       | 0    |      |      | 6                   |

|     |     | _        |     |       | 1       | 1    |      |      | 9                   |

Table 15: Line Output Attenuator Programming.

|     |     |     |     | RC3 R | egister | · _  |      |      |                             |  |  |

|-----|-----|-----|-----|-------|---------|------|------|------|-----------------------------|--|--|

|     | D7  | D6  | D5  | D4    | D3      | D2   | D1   | D0   | LAO Output Attenuation (dB) |  |  |

|     | RF3 | RF2 | RF1 | RF0   | RFG2    | RFG1 | LAT2 | LAT1 |                             |  |  |

| P/O |     |     |     |       |         |      | 0    | 0    | Infinite                    |  |  |

|     |     |     |     |       |         |      | 0    | 1    | 0                           |  |  |

|     |     |     |     |       |         |      | 1    | 0    | 6                           |  |  |

|     |     |     |     |       |         |      | 1    | 1    | 12                          |  |  |

X = Don't care values. The notch section is disabled in all these cases.

Note 6: The sampling clocks used by the Rx switched capacitor filters are straightly derived from the crystal oscillator.

The Tx switched capacitor filter is driven from the Tx DPLL.

Table 16: Carrier Level Detector Programming.

|     |      |      |     | RC6 R | egister |    |    |    | Carrier Level Detector  |

|-----|------|------|-----|-------|---------|----|----|----|-------------------------|

|     | D7   | D6   | D5  | D4    | D3      | D2 | D1 | D0 | Threshold(dBm) (note 7) |

|     | CDG2 | CDG1 | CDH | _     | _       | -  | _  | _  |                         |

| P/O | 0    | 0    | 0   |       |         |    |    |    | - 29.85                 |

|     | 0    | 0    | 1   |       |         |    |    |    | - 27.35                 |

|     | 0    | 1    | 0   |       |         |    |    |    | - 36.65                 |

|     | 0    | 1    | 1   |       |         |    |    |    | - 34.15                 |

|     | 1    | 0    | 0   |       |         |    |    |    | - 46.75                 |

| İ   | 1    | 0    | 1   |       |         |    |    |    | - 44.25                 |

|     | 1    | 1    | 0   | ·     |         |    |    |    | - 46.75                 |

|     | 1    | 1    | 1   |       |         |    |    |    | - 44.25                 |

Note 7: These values applies when the total Rx gain from the phone line to the Rx filter output is 0 dB.

Table 17: AGC Amplifier Gain Programming.

|     |        |     | RC5 Registe | r   |     | AGC Amplif | ierGain (dB) |

|-----|--------|-----|-------------|-----|-----|------------|--------------|

|     | D7     | D6  | D5          | D4  | D3  | AGC Ampin  |              |

|     | RG5    | RG4 | RG3         | RG2 | RG1 | AGC1 Input | AGC2 Input   |

| P/O | 0      | 0   | 0           | 0   | 0   | 0          |              |

|     | 0      | 0   | 0           | 0   | 11  |            | 1.5          |

|     | - ∞    | 0   | 0           | 0   | 1   | 0          | 3            |

|     | ∞      | 0   | 0           | 0   | 1   | 11         | 4.5          |

|     | - ∞    | 0   | 0           | 1   | 0   | 0          | 6            |

|     | - ∞    | 0   | 0           | 1   | 0   | 1          | 7.5          |

|     | - ∞    | 0   | 0           | 1   | 1   | 0          | 9            |

|     | - ∞    | 0   | 0           | 1   | 1   | 1          | 10.5         |

|     | - ∞    | 0   | 1           | 0   | 0   | 0          | 12           |

|     | - ∞    | 0   | 1           | 0   | 0   | 1          | 13.5         |

|     | - ∞    | 0   | 1           | 0   | 1   | 0          | 15           |

|     | - ∞    | 0   | 1           | 0   | 1   | 1          | 16.5         |

|     | - ∞    | 0   | 1           | 1   | 0   | 0          | 18           |

|     | - ∞    | 0   | 1           | 1   | 0   | 1          | 19.5         |

|     | - ∞    | 0   | 1           | 1   | 1   | 0          | 21           |

|     | - ∞    | 0   | 1           | 1   | 1   | 1          | 22.5         |

|     | - ∞    | 1   | 0           | 0   | 0   | 0          | 24           |

|     | - 14.5 | 1   | 0           | 0   | 0   | 1          | 25.5         |

|     | - 7.7  | 1   | 0           | 0   | 1   | 0          | 27           |

|     | - 3.4  | 1   | 0           | 0   | 1   | 1          | 28.5         |

|     | 0      | 1   | 0           | 1   | 0   | 0          | 30           |

|     | 2.7    | 1   | 0           | 1   | 0   | 1          | 31.5         |

|     | 5.2    | 1   | 0           | 1   | 1   | 0          | 33           |

|     | 7.4    | 1   | 0           | 1   | 1   | 1          | 34.5         |

|     | 9.5    | 1   | 1           | 0   | 0   | 0          | 36           |

|     | 11.4   | 1   | 1           | 0   | 0   | 1          | 37.5         |

|     | 13.3   | 1   | 1           | 0   | 1   | 0          | 39           |

|     | 15.1   | 1   | 1           | 0   | 1   | 1          | 40.5         |

|     | 16.8   | 1   | 1           | 1   | 0   | 0          | 42           |

|     | 18.5   | 1   | 1           | 1   | 0   | 1          | 43.5         |

|     | 20.2   | 1   | 1           | 1   | 1   | 0          | 45           |

|     | 21.8   | 1   | 1 1         | 1   | 1   | 1          | 46.5         |

#### **ELECTRICAL SPECIFICATIONS**

Unless otherwise noted, electrical characteristics are specified over the operating range. Typical values are given for  $V^+ = +5 \text{ V}$ ,  $V^- = -5 \text{ V}$  and  $t_{amb} = 25 \,^{\circ}\text{C}$ .

#### ABSOLUTE MAXIMUM RATINGS

| Symbol            | Parameter                                            | Value                                        | Unit |

|-------------------|------------------------------------------------------|----------------------------------------------|------|

| -                 | DGND Digital Ground to AGND Analog Ground            | - 0.3 to + 0.3                               | V    |

|                   | V <sup>+</sup> Supply Voltage to DGND or AGND Ground | - 0.3 to + 7                                 | V    |

|                   | V <sup>-</sup> Supply Voltage to DGND or AGND Ground | - 7 to + 0.3                                 | V    |

| Vı                | Voltage at any Digital Input or Output               | DGND - 0.3 to V <sup>+</sup> + 0.3           | V    |

| l <sub>1</sub>    | Digital Output Current                               | - 20 to + 20                                 | mA   |

| V <sub>in</sub>   | Voltage at any Input or Output                       | V <sup>-</sup> - 0.3 to V <sup>+</sup> + 0.3 | V    |

| lout              | Analog Output Current                                | - 10 to + 10                                 | mA   |

| P <sub>tot</sub>  | Power Dissipation                                    | 500                                          | mW   |

| tamb              | Operating Temperature Range                          | 0 to + 70                                    | °C   |

| t <sub>stot</sub> | Storage Temperature Range                            | - 65 to + 150                                | ∘€   |

| t <sub>sold</sub> | Pin Temperature (soldering 10 s.)                    | + 260                                        | ∞C   |

#### POWER SUPPLIES DGND = AGND = 0 V

| Symbol         | Parameter                                            | Min.   | Тур. | Max.   | Unit |

|----------------|------------------------------------------------------|--------|------|--------|------|

| V <sup>+</sup> | Positive Power Supply                                | 4.75   |      | 5.25   | ٧    |

| V-             | Negative Power Supply                                | - 5.25 |      | - 4.75 | V    |

| l+             | Positive Supply Current (receive signal level 0 dBm) |        |      | 35     | mA   |

| I-             | Negative Supply Current (receive signal level 0 dBm) | - 35   |      |        | mA   |

## DIGITAL INTERFACE

Control Inputs, Data Bus and Clock Outputs. Voltages referenced to DGND = 0 V

| Symbol          | Parameter                                                                                  |                                           | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------------------------------------------------------------------|-------------------------------------------|------|------|------|------|

| VıL             | Low Level Input Voltage                                                                    |                                           |      |      | 0.8  | ٧    |

| V <sub>IH</sub> | High Level Input Voltage                                                                   |                                           | 2.2  |      |      | V    |

| I <sub>IL</sub> | Low Level Input Current                                                                    | DGND < V <sub>1</sub> < 0.8 V             | - 10 |      | 10   | μА   |

| Пн              | High Level Input Current                                                                   | 2.2 V < V <sub>1</sub> < V <sup>+</sup>   | - 10 |      | 10   | μА   |

| Vol             | Low Level Output Voltage (I <sub>OL</sub> = 2.5 mA)                                        |                                           |      |      | 0.4  | V    |

| V <sub>OH</sub> | High Level Output Voltage (I <sub>OH</sub> = - 2.5 m                                       | A)                                        | 2.4  |      |      | V    |

| loz             | High Impedance Output Current (when E is high and DGND < V <sub>O</sub> < V <sup>+</sup> ) |                                           | - 50 |      | 50   | μΑ   |

| Crystal         | Oscillator Interface (XTAL1 input)                                                         | "                                         |      |      |      |      |

| V <sub>IL</sub> | Low Level Input Voltage                                                                    | - 44                                      |      |      | 1.5  | V    |

| V <sub>IH</sub> | High Level Input Voltage                                                                   |                                           | 3.5  |      |      | V    |

| I <sub>IL</sub> | Low Level Input current                                                                    | DGND ≤ V <sub>I</sub> ≤V <sub>ILmax</sub> | - 15 |      |      | μА   |

| I <sub>IH</sub> | High Level Input Current                                                                   | $V_{IHmin} \le V_I \le V^+$               |      |      | 15   | μА   |

# **ELECTRICAL SPECIFICATIONS** (continued)

ANALOG INTERFACE All voltages referenced to AGND = 0 V

| Symbol | Paramete                               | r                              | Min.  | Тур. | Max.          | Unit |

|--------|----------------------------------------|--------------------------------|-------|------|---------------|------|

| Vin    | Input Voltage EXI, DxI, RAI            |                                | - 2.5 |      | 2.5           | V    |

| Jin    | Input Current EXI, DxI, RAI (- 2.5 V < | < V <sub>in</sub> < 2.5 V)     | - 1   |      | 1             | μΑ   |

| Rin    | Input Resistance AGC1, AGC2            |                                | 1.5   |      |               | kΩ   |

| Rin    | Input Resistance CD1                   |                                | 0.7   |      |               | kΩ   |

| Vout   | Output Voltage ATO, LAO, RFO           | RL = 1 k $\Omega$ , CL = 50 pF | - 2.5 |      | 2.5           | V    |

| Rout   | Output Resistance                      | ATO<br>LAO<br>RFO              |       |      | 4<br>50<br>15 | Ω    |

| RL     | Load Resistance ATO, RFO               |                                | 1     |      |               | kΩ   |

| CL     | Load Capacitance ATO, RFO              |                                |       |      | 50            | pF   |

| Ri     | Load Resistance LAO                    |                                | 10    |      |               | kΩ   |

| Cı     | Load Capacitance LAO                   |                                |       |      | 20            | pF   |

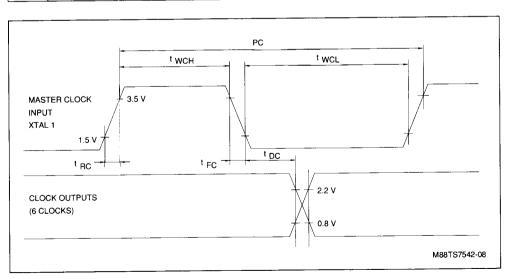

## TIMING SPECIFICATIONS

TIMING SPECIFICATIONS Clock Timing Characteristics (XTAL1 input)

| Symbol          | Parame                        | ter                    | Min. | Тур.  | Max. | Unit |

|-----------------|-------------------------------|------------------------|------|-------|------|------|

| PC              | Master Clock Period           |                        |      | 173.6 |      | ns   |

| twcL            | Master Clock Width Low Level  |                        | 50   |       |      | ns   |

| twch            | Master Clock Width High Level |                        | 50   |       |      | ns   |

| t <sub>RC</sub> | Master Clock Rise Time        |                        |      |       | 50   | ns   |

| tFC             | Master Clock Fall Time        |                        |      |       | 50   | ns   |

| tpc             | Clock Output Delay Time       | C <sub>L</sub> = 50 pF |      |       | 500  | ns   |

| tTC             | Clock Output Transition Time  | C <sub>L</sub> = 50 pF |      |       | 100  | ns   |

## **ELECTRICAL SPECIFICATIONS** (continued)

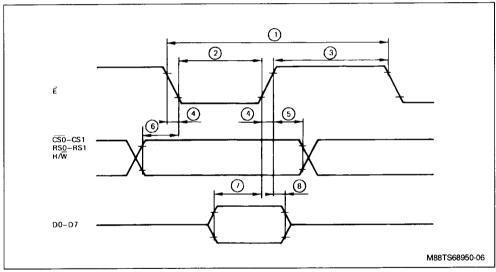

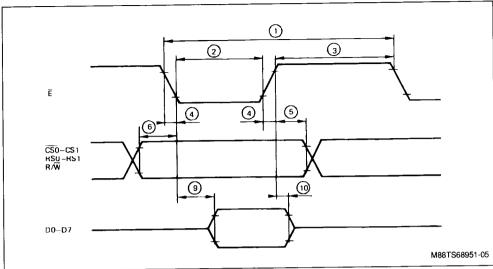

BUS TIMING CHARACTERISTICS (see foot notes 1 and 2 on timing diagrams)

| Symbol                          | Parameter                                                       | -    | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------------------------------------|------|------|------|------|------|

| toyo                            | Cycle Time                                                      | (1)  | 320  |      |      | ns   |

| twel                            | Pulse Width E Low Level                                         | (2)  | 180  |      |      | ns   |

| twen                            | Pulse Width E High Level                                        | (3)  | 100  |      |      | ns   |

| t <sub>r</sub> , t <sub>g</sub> | Clock Rise and Fall Time                                        | (4)  |      |      | 20   | ns   |

| tHCE                            | Control Signal Hold Time                                        | (5)  | 10   |      |      | ns   |

| tsce                            | Control Signal Set-up Time                                      | (6)  | 40   |      |      | ns   |

| t <sub>SDI</sub>                | Input Data Set-up Time                                          | (7)  | 120  |      |      | ns   |

| t <sub>HDI</sub>                | Input Data Hold Time                                            | (8)  | 10   |      |      | ns   |

| tspo                            | Output Data Set-up Time (1 TTL load and CL = 50 pF)             | (9)  |      |      | 150  | ns   |

| t <sub>dz</sub>                 | Output High Impedance Delay Time<br>(1 TTL load and CL = 50 pF) | (10) |      |      | 80   | ns   |

#### WRITE OPERATION

Note 1: Voltage levels shown are VIL < 0.4 V, VIH > 2.4 V, unless otherwise specified.

Note 2: Measurement points shown are 0.8 V and 2.2 V, unless otherwise specified.

#### **READ OPERATION**

Note 1: Voltage levels shown are VIL < 0.4 V, VIH > 2.4 V, unless otherwise specified.

Note 2: Measurement points shown are 0.8 V and 2.2 V, unless otherwise specified.

## TRANSMISSION CHARACTERISTICS

PERFORMANCES OF THE WHOLE TRANSMISSION CHAIN (Input TR1, Output ATO)

| Symbol | Parameter                                                                                    | Min.  | Тур. | Max. | Unit |

|--------|----------------------------------------------------------------------------------------------|-------|------|------|------|

| Gabs   | ATO Absolute Gain at 1 kHz                                                                   | - 0.5 | 0    | 0.5  | dB   |

| N      | ATO Psophometric Noise                                                                       |       |      | 100  | μV   |

| PSRR*  | ATO Positive Power Supply Rejection Ratio $V_{ac} = 200 \text{ mV}_{pp}$ f = 1 kHz           |       | 40   |      | dB   |

| PSRR-  | ATO Negative Power Supply Rejection Ratio $V_{ac} = 200 \text{ mV}_{pp}$ $f = 1 \text{ kHz}$ |       | 40   |      | dB   |

| THD    | Total Harmonic Distortion                                                                    |       |      | - 54 | dB   |

## DAC TRANSFER CHARACTERISTICS

| Symbol                 | Parameter                                          | Min. | Тур. | Max.  | Unit |

|------------------------|----------------------------------------------------|------|------|-------|------|

|                        | Converter Resolution                               |      | 12   |       | Bit  |

| V <sub>out</sub> (max) | Nominal Output Peak to Peak Amplitude              |      | 5.0  |       | ٧    |

| LSB                    | Least Significant Bit Amplitude                    |      | 1.2  |       | mV   |

| Eil                    | Integral Linearity Error Relative to Best Fit Line |      | ± 4  | ± 8   | LSB  |

| Edi                    | Differential Linearity Error                       |      |      | ± 0.7 | LSB  |

#### TRANSMISSION CHARACTERISTICS

TRANSMIT FILTER TRANSFER CHARACTERISTICS (input EXI, output ATO) (see figure 6)

| Symbol           | Parameter                                                                                                                                         | Min.         | Тур. | Max.                        | Unit                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-----------------------------|----------------------------|

| G <sub>abs</sub> | Absolute Gain at 1 kHz                                                                                                                            | - 0.3        | 0    | 0.3                         | dB                         |

| G <sub>re1</sub> | Gain Relative to G <sub>abs</sub> without Sin x/x Correction of DAC Sampling Below 3100 Hz 3200 Hz 4000 Hz 5000 Hz to 12000 Hz 12000 Hz and Above | - 0.4<br>- 3 |      | 0.3<br>- 36<br>- 46<br>- 50 | dB<br>dB<br>dB<br>dB<br>dB |

| Tgp              | Group Propagation Delay Time (f = 1800 Hz)                                                                                                        |              | 250  |                             | μs                         |

| Tgpd             | Group Propagation Delay Time Distortion (600 Hz < f < 3000 Hz)                                                                                    |              | 430  |                             |                            |

#### TX ATTENUATOR TRANSFER CHARACTERISTICS

| Symbol            | Parameter                                  | Min.  | Тур. | Max. | Unit |

|-------------------|--------------------------------------------|-------|------|------|------|

| AT <sub>abs</sub> | Absolute Attenuation at 0 dB Nominal Value | - 0.3 | 0    | 0.3  | dB   |

| ATrel             | Attenuation Relative to Nominal Value      | - 0.5 |      | 0.5  | dB   |

| AT <sub>max</sub> | Maximum Attenuation                        | 50    |      |      | dB   |

#### RECEPTION CHARACTERISTICS

PERFORMANCE OF THE WHOLE RECEPTION CHAIN (input RAI or DxI, output RR1)

| Symbol           | Parameter                                                                                                                                         | Min.  | Тур. | Max. | Unit  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| G <sub>abs</sub> | Absolute Gain<br>(AGC gain = 0 dB, RxCCLK = 9600 Hz, V <sub>in</sub> = 775 mVrms,<br>f = 2000 Hz)                                                 | - 0.5 | 0    | 1.5  | dB    |

| HD⊤              | Total Harmonic Distortion<br>(AGC gain = 0 dB, RxCCLK = 9600 Hz, V <sub>in</sub> = 775 mVrms,<br>f = 2000 Hz, programmed band = 475 Hz - 3200 Hz) |       |      | - 54 | dB    |

| N                | Equivalent RMS Noise (see note) (AGC gain = 0 dB, RAI, DxI tied to AGND, frequency band = 228 Hz - 3200 Hz)                                       |       |      | 800  | μVrms |

Note: Noise depends on AGC gain value.

# **RECEPTION CHARACTERISTICS** (continued)

# RECEIVE BAND-PASS FILTER AND REJECTION FILTER (input RAI or DxI, output RFO)

The characteristics and specifications (templates) of the ten programmable transfer functions are given on figures 7 to 16.

# RECEIVE FILTER INPUT GAIN CHARACTERISTICS

| Symbol | Parameter                        | Min.  | Тур. | Max. | Unit |

|--------|----------------------------------|-------|------|------|------|

| Grei   | Relative Gain to Programmed Gain | - 0.5 |      | 0.5  | dB   |

## LINE MONITORING ATTENUATOR CHARACTERISTICS

| Symbol | Parameter                                                 | Min.  | Typ. | Max. | Unit |

|--------|-----------------------------------------------------------|-------|------|------|------|

| ATabs  | Absolute Attenuation at 0 dB Nominal Value                | - 0.3 | 0    | 0.3  | dB   |

| ATrel  | Attenuation Relative to Nominal Value (2 dB ≤ AT ≤ 22 dB) | - 0.5 |      | 0.5  | dB   |

| ATmax  | Maximum Attenuation (AT = ∞)                              | 50    |      |      | dB   |

# AGC AMPLIFIER AND A/D CONVERTER (input AGC1, output RR1)

| Symbol | Parameter                                                                      | Min. Typ.    | Max.     | Unit     |

|--------|--------------------------------------------------------------------------------|--------------|----------|----------|

| Grei   | Relative Gain to Programmed Gain<br>0 dB ≤ AGC ≤ 24 dB<br>25.5 ≤ AGC ≤ 46.5 dB | - 0.5<br>- 1 | 0.5<br>1 | dB<br>dB |

| Vos    | Offset Voltage                                                                 | <b>– 70</b>  | 70       | LSB      |

# CARRIER LEVEL DETECTOR (input AGC1, output CDR)

| Symbol           | Parameter                                                                                                          | Min.              | Тур. | Max.        | Unit           |

|------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|------|-------------|----------------|

| T <sub>rel</sub> | Relative Threshold to Programmed Value T $-36.65 < T \le -27.35 \text{ dBm}$ $-46.75 \le T \le -36.65 \text{ dBm}$ | 0.5<br>1          |      | 0.5<br>1    | dB<br>dB       |

| H <sub>yst</sub> | Hysteresis                                                                                                         | 2                 |      | 3           | dB             |

| Vos              | Input Offset Voltage<br>1st Threshold Pair (see table 16 and fig. 2)<br>2nd Threshold Pair<br>3rd Threshold Pair   | - 1<br>- 2<br>- 3 |      | 1<br>2<br>3 | mV<br>mV<br>mV |

| T <sub>dd</sub>  | Detection Delay Time<br>0 mVrms to 775 mVrms Transition or 775 mVrms to 0 mVrms<br>Transition                      | 1                 |      | 3           | ms             |

# PERFORMANCE OF THE A/D CONVERTER (input AGC1, output RR1)

| Symbol               | Parameter                                          | Min.  | Тур. | Max.  | Unit |

|----------------------|----------------------------------------------------|-------|------|-------|------|

| V <sub>in(max)</sub> | Input Voltage (peak to peak)                       |       |      | 5     | V    |

| Resh                 | A/D Converter Resolution                           |       |      | 12    | Bit  |

| LSB                  | Analog Increment                                   |       | 1.2  |       | mV   |

| Eil                  | Integral Linearity Error Relative to Best Fit Line |       | ± 4  | ± 8   | LSB  |

| Edl                  | Differential Linearity Error                       |       |      | ± 0.7 | LSB  |

| Vos                  | Offset Voltage                                     | - 100 |      | 100   | LSB  |

Figure 6: Tx Filter Frequency Response.

M88TS7542-09

START O. OOOHz

AMPTD 50. 119mV

STOP 4 000.000Hz

DELAY APER 20. DOHz

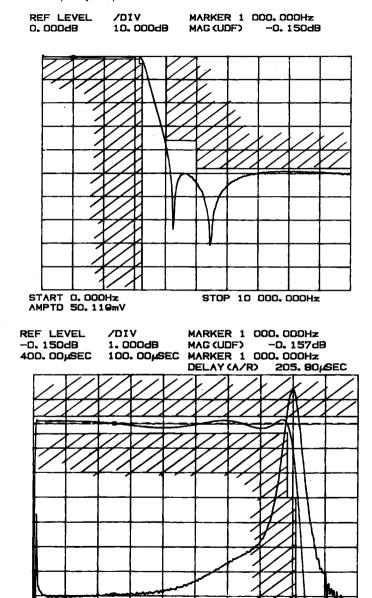

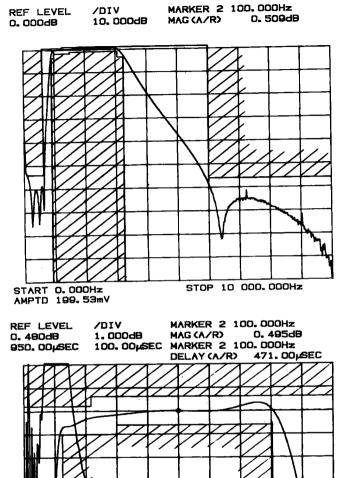

Figure 7: Rx Filter Frequency Response for V.22, V.22bis, BELL212A and BELL103 High Channels (see table 13).

Figure 8: Rx Filter Frequency Response for V.21 High Channel (see table 13).

MARKER 1 800, 000Hz /DIV REF LEVEL 0. 079dB 10.000dB MAG (A/R) O. 000dB STOP 10 000.000Hz START 0.000Hz AMPTD 199.53mV REF LEVEL /DIV MARKER 1 800.000Hz 1.000dB O. 105dB MAG (A/R) 0.100dB 100.00 SEC MARKER 1 800.000Hz 1.6000mSEC 1.1109mSEC DELAY (A/R)

M88TS7542-11

START 1 300.000Hz AMPTD 100.00mV STOP 2 300.000Hz

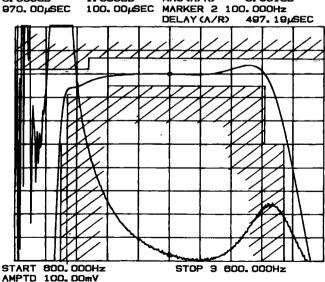

Figure 9: Rx Filter Frequency Response for V.27ter 2400bps (see table 13). /DIV

REF LEVEL

O. 383dB 10.000dB MAG (A/R) O. 000dB STOP 10 000,000Hz START 0.000Hz AMPTD 199.53mV REF LEVEL /DIV MARKER 2 100,000Hz 1.000dB O. 380dB MAG (A/R) 0.381dB 100.00 MARKER 2 100.000Hz DELAY (A/R) 497. 19µSEC

MARKER 2 100.000Hz

Figure 10: Rx Filter Frequency Response for V.27ter 4800bps, V.23, V.26 and BELL202 (see table 13).

START BOO. 000Hz STOP 3 800. 000Hz

AMPTD 100. 00mV

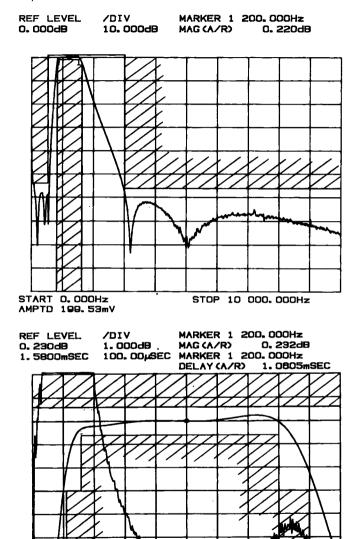

Figure 11: Rx Filter Frequency Response for V.22, V.22bis, BELL212A and BELL103 Low Channel (see table 13).

M88TS7542-14

STOP 1 700.000Hz DELAY APER 5.000Hz

START 700.000Hz AMPTD 100.00mV

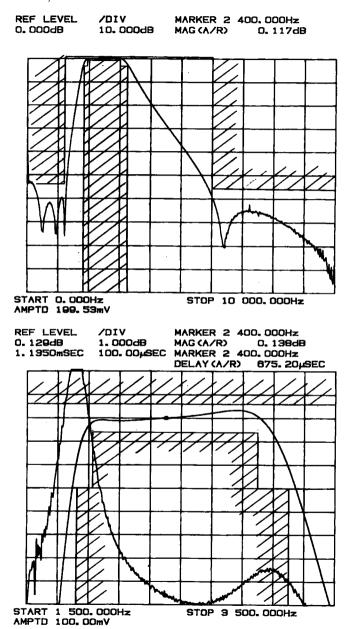

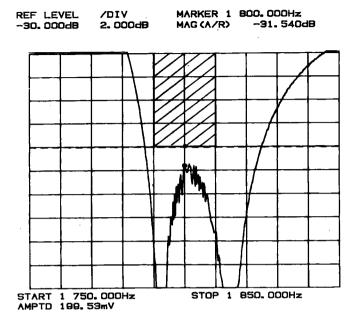

Figure 12: Rx Filter Frequency Response for V.22 and V.22bis Low Channels with 1800Hz Tone Rejection (see table 13).

Figure 12 (continued): Rx Filter Frequency Response for V.22 and V.22bis Low Channels with 1800Hz Tone Rejection (see table 13).

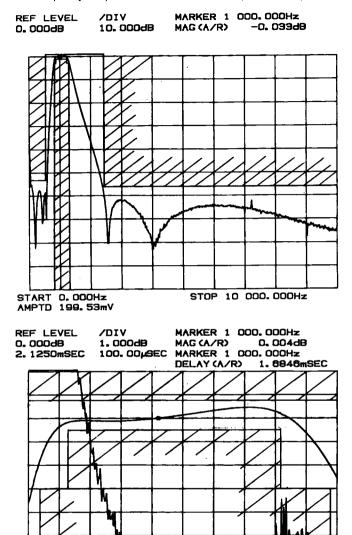

Figure 13: Rx Filter Frequency Response for V.21 Low Channel (see table 13).

START 790.000Hz STOP 1 290.000Hz

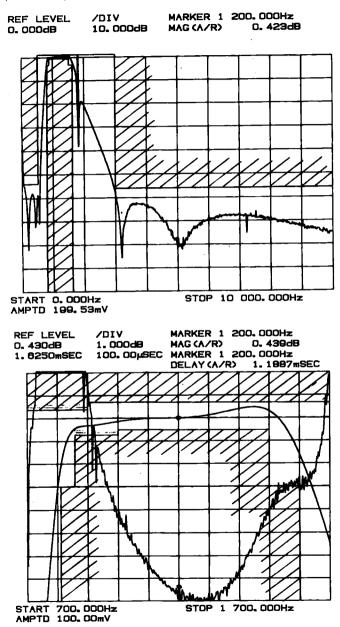

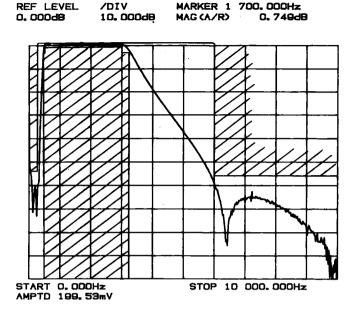

Figure 14: Rx Filter Frequency Response for V.29 and V.33 (see table 13).

REF LEVEL /DIV MARKER 1 705.000Hz

0.725dB 1.000dB MAG (A/R) 0.731dB

995.00µSEC 100.00µSEC MARKER 1 705.000Hz

DELAY (A/R) 418.82µSEC

START 400.000Hz

AMPTD 100.00mV

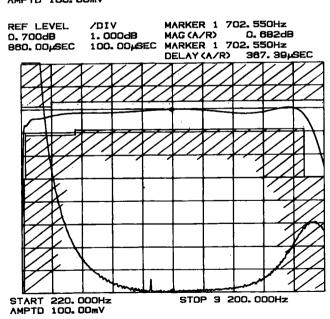

Figure 15: Rx Filter Frequency Response with Full Channel Bandwidth (see table 13).

/DIV

REF LEVEL

10.000dB MAG (A/R) O. 000dB STOP 10 000.000Hz START O. DOOHz AMPTD 100.00mV

MARKER 2 400.000Hz

C. 494dB

Figure 16: Rx Filter Frequency Response for 75bps Back Channel (see table 13).

REF LEVEL /DIV MARKER 450.000Hz 0.000dB 10.000dB MAG (A/R) O. 090dB START O. DOOHz STOP 10 000.000Hz AMPTD 100.00mV REF LEVEL /DIV MARKER 440.000Hz 0. 200dB 1.000dB MAG (A/R) 0.197dB 4. 9450mSEC 200.00 SEC MARKER 440.000Hz DELAY (A/R) 3.9978mSEC START 340. 000Hz STOP 540.000Hz AMPTD 100.00mV